Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении зрительных анализаторов роботов.

Известны устрос ства для распознавания прямого края объекта, содержащие телевизионные датчики и электронные блоки, обеспечивающие выделение полезной информации из совокупности сигHanoBj поступающих с выходов телевизионных датчиков CllНаиболее близким к предлагаемому является устройство для распознавания прямого края объекта, содержащее последовательно соединенные телевизионный датчик, вход которого подключен к выходу синхроимпульсов блока синхронизации, и аналого-цифровой преобразователь, первый блок вычитания, блок элементов И, первый, второй и третий сумматоры 2.

Недостатками известного устройства являются низкая достоверность распознавания в условиях низкой освещенности и воздействии сильных ф.пуктуационных помех, поскольку при воздействии шумов граница мёткду объектом и фоном размывается. Например, уже при отношении сигнал/шум, равных 3, амплитуда шумовых выбросов становится соизмеримой с аииплитудой полезного сигнала от объекта. Это приводит к тому, что уже на этапе локализации контурных точек, вычисление разности амплитуд незалеожанного видеосигнала с выхода телевизионного датчика и задержанного на один р астровый элемент видеосигнала вэлементе задержки и сравнении результата

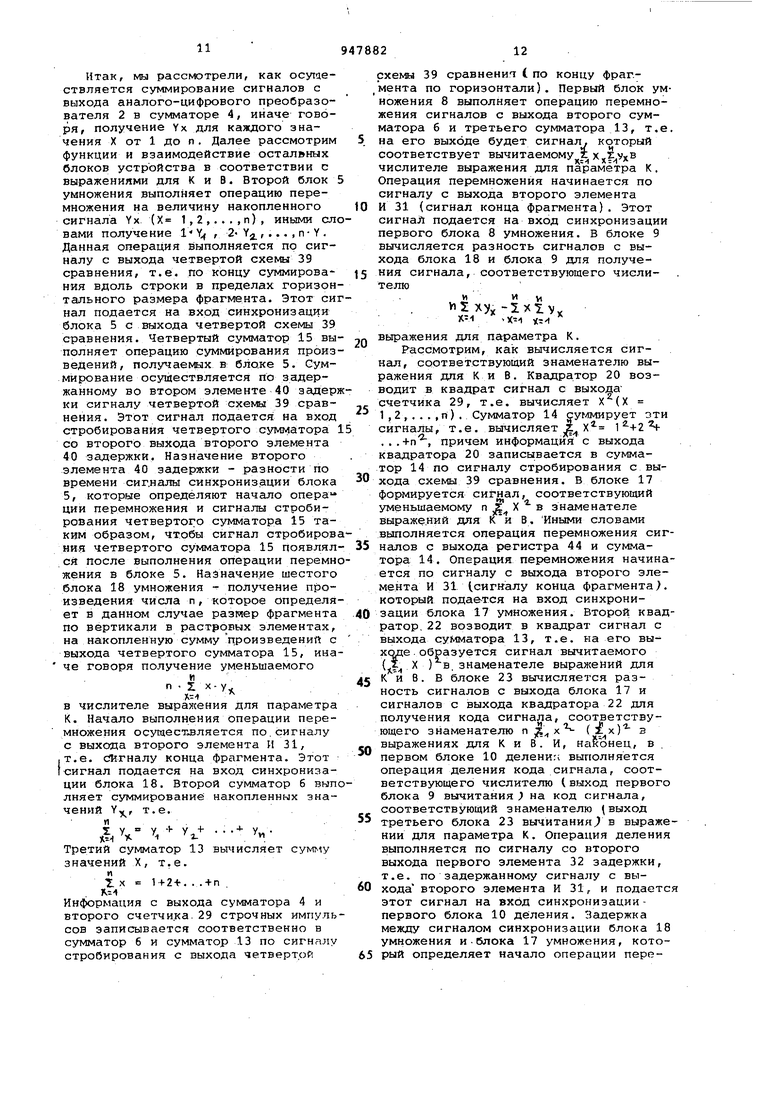

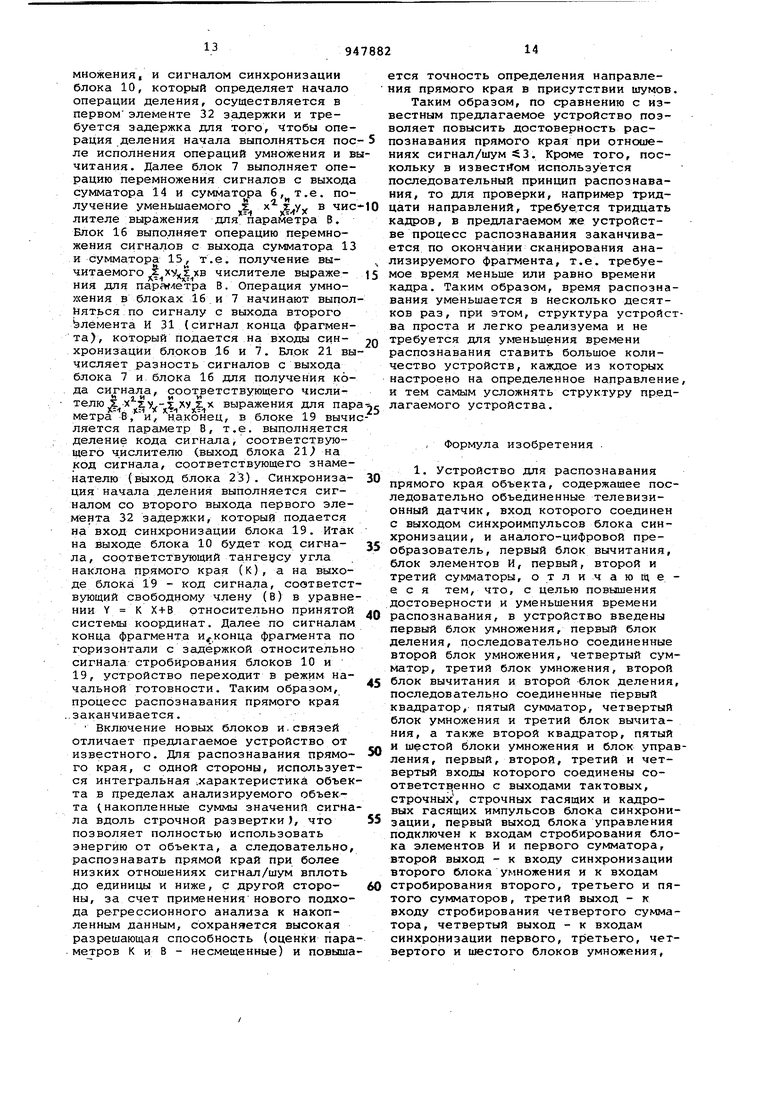

10 с порогом ограничения, предварит§льно установленным в первом пороговом элементе, на его выходе фop wpyютcя импульсы, временное положение которых не соответствует положению ис15тинных контурных точек. Кроме того, возникает большое количество ложных контурных точек от шумовых выбросов, превышающих порог ограничения в первом пороговом элементе, а также зна20чительные разрывы в контурах - в тех местах, где сумма сигнала и шума по абсолютной величине меньше уровня ограничения. Суммирование в первом сумматоре сигналов, не явля25ющихся контурными, приводит к ошибкам ПРИ определении направления прямого края, а также к увеличению вероятности ложного распознавания. При дальнейшем уменьшении отношения сиг30нал-шум, до единицы и меньше, вообще невозможно установить соответствуювдий порог в первом пороговом эле менте и надежно выделить контурный сигнал, а следовательно, распознать прямой край объекта. Здесь, как и в рассмотренных выше аналогах, перво начально выделяется перепад яркости между объектом и фоном, для нахожде ния которого используется только энергия граничных элементов, которой крайне недостаточно для выделения перепада при низких отношениях сигнал/шум (3) . Кроме того, для распознавания, произвольно ориентированных прямолинейных элементов, в устройстве 1осуществляется последоват,ельное изменение направления суммирования, за счет считывания в каждом кадре из блока памяти во второй и третий сумматоры соответствуюцих приращений координат X и У. При сравнении кодов сигналов на выходе счет 1иков тактовых и строчных импульсов соответственно с кодами сигналов: на выходе второго и третьего сумматоров, в схеме сравнения вырабатывается импульс, который открывает элемент И Если в данный момент времени имеется сигнал от контурного элемента на выходе первого порогового элемента, то этот сигнал пройдет через открытый элемент И на вход первого сумматора. Если в данном направлении имеется прямолинейный элемент, то амплитуда сигнала в первом сумматоре увеличивается и вызовет срабатыва ние второго порогового элемента. Пос кольку процесс распознавания последовательный, то требуется значительное время для распознавания, которое линейно увеличивается с увеличением частоты дискретизации по направлениям. Уменьшение же частоты дискретизации по направлениям, приводит к уменьшению достоверности распознавания произвольно ориентированного пря мого Края. Цель изобретения - повышение дос товерности и уменьшение времени рас познавания. . . Указанная цель достигается тем, что в устройство, содержащее последовательно соединенные телевизионный датчик, вход которого соединен с выходом синхроимпульсов блока син хронизации, и аналого-цифровой преобразователь, первый блок вычитания блок элементов И, первый, второй и третий сумматоры, введены первый бл умножения, первый блок деления, пос ледовательно соединенные второй бло умножения, четвертый сумматор, третий блок умножения, второй блок вычитания и второй блок деления, последовательно соединенные первый квад pajrop, пятый сумматор, четвертый бло умножения и третий блок вычитания, также второй квадратор, пятый и шестой блоки умножения и блок управления, первый, второй, третий и четвертый входы которого соединены соответственно с выходами тактовых, строчных, строчных гасящг х и кадровых гасящих импульсов блока синхронизации, первый выход блока управлегния подключен к входам стробирования блока элементов И и первого сумматора, второй выход - к входу синхронизации вто рого блока умножения и к входам стробирования второго, третьего и пятого сумматоров, третий выход - к входу стробирования четвертого сумматора, четвертый выход - к входам синхронизации первого, третьего, четвертого пятого и шестого блоков умножения, пятый выход - к входам синхронизации первого и второго блоков деления, шестой выход - к входу сброса первого сумматора, седьмой выход - -к входам сброса второго, третьего, четвертого и .пятог© сумматоров, восьмой выход - к второму входу четвертого и первому входу шестого блоков умножения, девятый выход к входу первого квадратора, информационному входу третьего сумматора, и к первому входу второго блока умножения, второй вход KOTopoio соединен с выходом первого сумматора, выход аналого-цифрового преобразователя подключен к информационному входу блока элементов И, -выход в:оторого соединен с информационным входом первого сумматора, выход которотро соединен с информационным входом второго сумматора, выход которого подключен к первому входу пятого блока умножения и к первому входу первого блока умножения, выход которого соединен с первым входом первого блока ВЕлчитания, выход которого соединен с первым входом первого блока деления, выход третьего сумматора подсоединен к вторым входам первого и третьего блоков умножения и к входу второго квадратора, выход которого соединен с вторым входом третьего блока вычитания, выход которого подключен к вторым входам первого и второго блоков деления, второй вход пятого блока умножения соединен, с выходом пятого сумматора, а выход - с вторым входом второго блока вычитания, второй вход шестого блока умножения соединен с выходом четвертого сумматора, а выход - со вторым входом первого блока вычитания, кроме того блок управления содержит первый счетчик строчных импульсов, первый счетчик тлкТгувых ИМПУЛЬСОВ, последовательно включенные регистр координаты X, первую схему сравнения, первый триггер, первый элемент И, второй счетчик строчных импульсов, вторую схе- , му сравнения, второй :элемонт И, первый элемент задержки и первый элемент ИЛИ, последовательно соединенные регистр координаты У, третью сх сравнения, второй триггер, третий элемент И, второй счетчик тактовых импульсов, четвертую схему сравнёния, второй элемент задержки и втор ИЛИ, а также регистр и третий элемент ИЛИ, первый и второй входы которого являются соответственно третьим и четвертым входами блока, а выход подключен к второму входу второго, элемента ИЛИ и к входу сброса первого счетчика тактовых импульсов, счетный вход, которого является первым входом блока, а выход подключен к второму входу тре тьей схемы сравнения, выход первого счетчика строчных импульсов подключен к второму входу первой схемы сравнения, а счетный вход и вход сброса соединены соответственно с вторым и четвертым входами блока, второй вход первого элемента ИЛИ соединён с чет ведэтым-входом блока, а выход является седьмым выходом блока и подключен к входу сброса второго счетчика строчных импульсов и к входу установки в нулевое состо ние первого триггера, выход которого соединен с вторым входом третьего элемента И, третий вход которого подключен к первому входу блЬка, а выход является первым выходом блока выход второго элемента ИЛИ соединен с входом установки в нулевое состоя ние второго триггера, с входами сбр са второго счетчика тактовых импуль сов и является.шестым выходом .блока второй вход первого элемента И является вторым входом блока, выход р гистра подключен к вторым входам вт рой и четвертой.схем сравнения и яв ляется восьмым выс{одом блока, выход второго счетчика строчных импульсов является девятым выходом блока, выход четвертой схемы сравнения подключей к второму входу второго элемента И и является вторым выходом блока, выход второго элемента И явл ется четвертым выходом блока, второ выход первого задержки является пятым выходом блока, второй выход второго элемента эадержки является третьим выходом блока. На фиг.1 представлена структурна схема предлагаемого устройства; на фиг. 2 - структурная схема блока уп равления. Устройство содержит телевизионный датчик 1, аналого-цифровой преобразователь 2, блок 3 элементов И первый сумматор 4, второй блок 5 умножения, второй сумматор б, пяты блок 7 умножения, первый блок 8 умн жения, первый блок 9 Вычитания, пер вый блок 10 деления, блок 11 синхронизации, блок 12 управления, третий сумматор 13, пятый сумматор 14, ;четвертый сумматор 15, третий блок 16 умножения, четвертый блок 17 умножения, шестой блок 18 y QIoжeния, второй блок 19 деления, первый квадратор 20, второй блок 21 вычитания, второй квадратор 22, третий блок 23 вычитания Блок 12 управления (фиг.2) содержит регистр 24 координаты X, схему 25 сравнения, первый триггер 26, третий элеме нт И27, первый элемент И 28, второй счетчик 29 строчных импульсов , вторую схему 30 сравнения, второй элемент И 31, первый элемент 32 задержки, первый элемент ИЛИ 33, первый счетчик строчных импульсов 34, регистр 35 координаты У, третью схему 36 сравнения, второй триггер 37, второй счетчик 38 тактовых импульсов четвертую схему 39 сравнения, второй элемент 40 задержки, второй элемент ИЛИ 41, третий элемент ИЛИ 42, первый счётчик 43 тактовых импульсов и регистр 44. Устройстзао работает следующим образом. : Объясним работу устройства укрупненно, а затем покажем детальное взаимодействие входящих в устройство блоков. С помощью блока 12 выбирается некоторый фрагмент из п п растровых элементов в интересующей нас Области телевизионного изображения. Известно, что край,объекта прямой, т.е. координаты точек, принадлежащие прямому краю объекта, связаны между собой линейной зависимостью Y К-Х+8 где К - тангенс угла наклона В - свободный член, но располагаться внутри фрагмента он может под любым произвольным углом. Будем считать, что система координат, связанная с анализ яру eNbiM фрагментом, декартовая, причем начало координат совпадает с левым верхним углом фрагмента, ось ординат направлена вдоль строчной развертки, а ось абцисс - перпендикулярно направлению строчной развертки. Работу устройства будем рассматривать для случая двухградационных изображений, т.е. аналого-цифровой преобразователь 2 квантует сигнал с выхода телевизионного датчика 1 на два уровня, например на 1 и О будем считать, что развертка прогрессивная. Внутри выбранного фрагмента выполняется пространственная суммация значений сигнала с выхода аналого-цифрового преобразователя 2 вдоль строки разложения телевизионного растра. Иначе говоря, для каждого значения X 1, 2,... п, где X - текущий номер строки в пределах анализируемого фрагмента, an- размер фрагмента в растровых элементах по вертикали, имеет некоторое накопленное значение сигнала YX. По этим данным, используя линейный регрессионный анализ, в частности метод наименьших квадратов, легко находятся параметры К и В 5 влинейном уравнении,которое овязывает между собой координаты прямого края, относительно принятой системы координат. Метод основывается на выборе таких значений К и В, которые мини-ю мизируют сумму квадратов вертикальных отклонений от линии регресси. Иными словами минимизируется сумма S

S (Yi - К-Х - В)1C

t-.л

ПО отношению к параметрамК и В. Экстремум находится обычным образом, т.е. берутся производные по К и В, приравниваются к нулю и затем полученные выражения решаются совместно. .После 20 несложных вычислений получаются следукядие выражения для вычисления по накопленным значениям Ух параметров

,;llл. 25

К-г

п о. , и W Z X)

НИ

и о VI - и „1.

1 X Z v - г. ху„ Z -х

в- )-1 У. хVI , VI .12.

VI Z Х - ( 2 X) И-1 1

где Ух - накопленные значения,сигналов с выхода аналого-цифрового преобразователя 2 в пределах горизонтального размера анализируемого фрагмента в направлении строчной развертки (по оси ординат); X - текущий номер строки в пределах вертикального размера анализируемого фрагмента. Принимает значение от 1 до п с частотой раз- , вертки ;

п - размер анализируемого фраг-, мента в растровых элементах как по горизонтали, так и по вертикали.

Для того, что.бы устройство было работоспособным, необходимо обеспечить его синхронизацию, т.е. для правильного взаимодействия входягцих в устройство блоков, необходимо обеспечить требуемые временные соотношения между управляющими импульсами. Эти функции возлагаются на блок 11 синхронизации и на блок 12 управления. Причем блок 11 вырабатывает основные последовательности синхроимпульсов для работы телевизионного датчика 1 и блока 12. В свою очередь, блок 12, испбльзуя данные последовательности, а именно тактовые, строчные гасящие и кадровые гасяшие импульсы. Формирует для блоков устройства имп.льсы стробнрова ния, сброса и сиячооиичацин : требуемыми временными соотношениями. В режим начальной готовности устройство переходит по каждому кадровому гасящему импульсу блока 11, при этом сбрасывается содержимое всех суг/пиаторов, устанавливаются в нулевое состояние все счетчики и триггеры. Кадровые гасящие импульсы блока 11 подаются на вторые входы первого элемента ИЛИ 33 и третьего элемента ИЛИ 42. При этом сигнал с выхода первого элемента ИЛИ

33идет на установку в нулевое состояние первого триггера 26, на вход сброса счетчика 29, на вход сброса содержимого сумматора б, сумматора 13 сумматора 15 и сумматора 14. Сигнал

с выхода третьего элемента ИЛИ 42 на вход .сброса первого счетчика 43 и через второй элемент ИЛИ 41 - на сброс первого сумматора 4, на установку в нулевое состояние второго триггера 37 и на сброс второго счетчика 38. Первый счетчик 34 сбрасывается непосредственно кадровыми гасящими импульсами блока 11.

Итак, рассмотрим, как обеспечивается суммирование сигналов с выхода аналого-цифрового преобразователя 2 вдоль направления строчной развертки, т.е. получение Ух для каждого значения X 1,2,...,п в выражениях для К и В. Координаты Xц и У„а левого верхнего угла фрагмента, относительно системы координат, связанной с телевизионным растром (причем, как и для фрагмента, ось абцисс системы также направлена перпендикулярно, а ось ординат - вдоль направления строчной развертки занесены в регистр координаты X 24 и регистр координаты У 35. Размер фрагмента в растровых элементах занесен в регистр 44 При равенстве кода сигнала с выхода первого, счетчика строчных импульсов

34с кодом сигнала на выходе регистра 24, на выходе первой схемы сравнения 25 вырабатывается сигнал, который переводит триггер 26 в единичное состояние, при этом сигнал с его выхода будет разрешающим для первого элемента И 28 и третьего элемента

И 27. При этом строчные импульсы с., выхода блока 11,. через открытый первый элемент И 28 проходят на первый вход кторого счетчика 29, на выходе которого будет в двоичном виде код сигнала, соответствующий величинам X 1,2,...,п в выражениях К и В и который изменяется последовательно с частотой строчной развертки.

1а первом входе первого элемента И 28 - единица, строчный импульс переводит второй счетчик 29 в состоя(ние X 1. При равенстве кода сигнала на выходе первого счетчика 43 с кодом сигнала на выходе регистра 35, в третьей схеме сравнения 36 выг абаплвается импульс, который перев1-лит в единичное состояние триггер 37 сигнал с выхода которого будет разрешающим для третьего элемента И 27. Третий элемент И 27 выполняет функцию конъюкции трех сигналов. Поскольку первый триггер 26 тоже в единичном состоянии, т.е. на втором входе, третьего элемента И 27 - единица, то тактовые импульсы блока 11 синхронизации через третий элемент И 27 проходят на счетный вход второго счетчика 38 и на входы стробирования блока элементов И 3 и сумматора 4. При этом сигналы с выхода аналого-цифрового преобразователя 2 через блок 3 проходят на вход сумматора 4 ( все используемые, в устройстве сумматоры накапливающего типа). При равенстве кода сигнала с выхода второго счетчика 38 с кодом сигнала на выходе регистра 44, в четвертой схеме 39 сравнения вырабатывается сигнал, который указывает на конец фрагмента по горизонтали. Таким образом, в этот момент времени, для X 1, в первом сумматоре 4 находится накопленный сигнал Y , который затем сбрасывается сигналом с выхода второго элемента ИЛИ 41 (этот сигнал образуется по сигналу с В лхода схемы 39 сравнения 39, задержанному во втором элеме те 40 задержки). Сигналом с выхода второго элемента ИЛИ 41 также сбрасывается второй счетчик 38 и устанавливается в нулевое состояние второй триггер 37. При этом, на первом входе третьего элемента И 27 - нуль, и тактовые импульсы через него не проходят. Назначение задержек будет объяснено позже.

Следующий импульс с выхода блока 11 через открытый элемент И 28 установит на выходе второго счетчика 29 код сигнала, соот)етствующий X 2. Далее накопление происходит аналогичным образом, т.е. при равенстве кода сигнала с выхода первого счетчика 43 с кодом сигнала на выходе регистра 35, в третьей схеме сравнения 36 вырабатывается импульс, который установит второй триггер 37 в единичное состояние, и следовательно, на первом входе третьего элемента И 27 - единица, а поскольку на втором его входе тоже единица (сигнал с выхода первого триггера 26), то тактовые импульсы через открытый третий элемент И 27 проходят на вход второго счетчика 38 и на входы стробирования блока 3 и сумматора 4. Следовательно, сигналы с выхода аналого-цифрового преобразователя 2 через блок 3 проходят на вход первого сумматора 4. При равенстве кода сигнала на выходе второго счетчика 38 с кодом сигнала на выходе регистра 44, в четвертой схеме 39 сравнения вырабат з1вастся сигнал, который указывает на конец суммирования вдоль строки в пределах горизонтального размера анализируемого фрагмента. Таким образом, в этот момент времени для X 2 в первом сумматоре 4 находится накопленный сигнал Yj, который затем сбрасывается сигналом с выхода второго элемента ИЛИ 41.. Этим же сиг налом сбрасывается счетчик 38 и устанавливается в нулевое состояние второй триггер 37. Следовательно, на первом входе третьего элемента И 27 нуль, и тактовые импульсы не проходят на выход. Далее следующий строчный импульс через открытый первый элемент И 28 установит на выходе 29 код сигнала, соответствугадий X 3, накопление сигналов происходит вдоль этой строки. Сигнал на выходе сумматора 4 в конце накопления равен Yj, и так далее, пока код сигнала на выходе счетчика 29 не равняется коду сигнала на выходе регистра 44, т.е. когда X п, в этом случае на выходе схемы 30 вырабатывается сигнал, который указывает на конец фрагмента по вертикали. А при совпадении сигналов с выхода cxeNti 30 с сигнсшом с выхода четвертой схемы 39 сравнения, на выходе второго элемента И 31 появляется сигнал, который указывает на конец фрагмента, т.е. указывает на правый нижний угол анализируемого фрагмента. Этот сигнал после задержки в первом элементе 32 задержки используется для установки устройства в начальное состояние, т.е. он подается на вход первого элемента ИЛ 33, а с его выхода - на входы сброса блоков устройства. При этом второй триггер 37 и счетчик 38 устанавливаются в нулевое состояние сигналом с выхода второго элемента ИЛИ 41 (этот сигнал вырабатывается по сигналу схемы 39 сравнения, задержанному во втором элементе 40 задержки). Следовательно, устройство устанавливается в начальное состояние или по кадровому гасящему импульсу блока 11 или по импульсу конца фрагмента. Эти сигналы собираются по ИЛИ в первом элементе ИЛИ 33. Первый счетчик тактовых импульсов 43 сбрасывается в нулевое состояние или кадровым гасящим импульсом, или строчным гасящим импульсом. Эти сигналы собираются по ИЛИ в третьем элементе ИЛИ 4 Второй триггер 37, второй счетчик 38 тактовых импульсов и первай сумматор 4. устанавливаются в нулевое состояние или кадровым гасящим, или строчным гасящим или импульсом конца фрагмента по горизонтали, задержанным во втором элементе 40 задержки. Эти импульсы собираются по ИЛИ в третьем элементе ИЛИ 42 и втором элементе ИЛИ 41. Итак, мы рассмотрели, как ocytneствляется суммирование сигналов с выхода аналого-цифрового преобразователя 2 в сумматоре 4, иначе говоря, получение Yx для каждого значения X от 1 до п. Далее рассмотрим функции и взаимодействие осталвных блоков устройства в соответствии с выражениями для К и В. Второй блок умножения выполняет операцию перемножения на величину накопленного сигнала Yx (Х 1,2,..,,п), иными сл вами получение 1 Y , 2- Y,, ... , п У . Данная операция выполняется по сигналу с выхода четвертой схемы 39 сравнения, т.е. по концу суммирования вдоль строки в пределах горизон тального размера фрагмента. Этот си нал подается на вход синхронизации блока 5 с выхода четвертой схемы 39 сравнения. Четвертый сумматор 15 вы полняет операцию суммирования произ ведений, получаемых в блоке 5. Суммирование осуществляется По задержанному во втором элементе 40 задер ки сигналу четвертой схемы 39 сравнения. Этот сигнал подается на вход стробирования четвертого сумматора со второго выхода второго элемента 40 задержки. Назначение второго элемента 40 задержки - разности по времени сиг.налы синхронизации блока 5, которые определяют начало опера ции перемножения и сигналы стробирования четвертого сумматора 15 таким образом, чтобы сигнал стробиров ния четвертого сумматора 15 появлял ся после выполнения операции перемн жения в блоке 5. Назначение шестого блока 18 умножения - получение произведения числа п, которое определя ет в данном случае размер фрагмента по вертикали в растровых элементах, на накопленную сумму произведений с выхода четвертого сумматора 15, ина че говоря получение уменьшаемого п . s Л:1 в числителе выражения для параметра К. Начало выполнения операции перемножения осуществляется по.сигналу с выхода второго элемента И 31, .т.е. сигналу конца фрагмента. Этот (сигнал подается на вход синхронизации блока 18. Второй сумматор 6 вып лняет суммирование накопленных значений т.е м X, -t- Д V , V, Третий сумматор 13 вычисляет сумму значений X, т.е. и Т. X 1+2-(-. . . + п K-l Информация с выхода сумматора 4 и второго счетчика.29 строчных импуль сов записывается соответственно в сумматор 6 и сумматор 13 по сигналу стробирования с выхода четвертой схемы 39 сравненияг ( по концу фрагмента по горизонтали). Первый блок умножения 8 выполняет операцию перемножения сигналов с выхода второго сумматора б и третьего сумматора 13, т.е. на его выходе будет сигнал, который соответствует вычитаемому числителе выражения для парамётра К, Операция перемножения начинается по сигналу с выхода второго элемента И 31 (сигнал конца фрагмента). Этот сигнал подается на вход синхронизации первого блока 8 умножения. В блоке 9 вычисляется разность сигналов с выхода блока 18 и блока 9 для получения сигнала, соответствующего числителюи и VI ViJxjIx -IXlVv Х-1 Х-1 KI-I выражения для параметра К. Рассмотрим, как вычисляется сигнал, соответствующий знаменателю выражения дпя К и В. Квадратор 20 возводит в квадрат сигнал с выходасчетчика 29, т.е. вычисляет X (X 1 , 2 , , . . , п) . Сумматор 14 g:y лмиpyeт эти сигналы, т.е. вычисляет х . . ,+п, причем информации с выхода квадратора 20 записывается в сумматор 14 по сигналу стробирования с выхрда схемы 39 сравнения. В блоке 17 формируется сигнал, соответствующий уменьшаемому п X в знаменателе выраже.ний для В. Иными словами выполняется операция перемножения сигналов с выхода регистра 44 и сумматора 14. Операция перемножения начинается по сигналу с выхода второго элемента И 31 (сигналу конца фрагмента. который подается на вход синхронизации блока 17 умножения. Второй квадратор, 22 возводит в квадрат сигнал с выхода сумматора 13, т.е. на его выходе . образуется сигнал ВЕЛЧитаемого { X ) в. знаменателе выражений для К и В. В блоке 23 вычисляется разность сигналов с выхода блока 17 и сигналов с выхода квадратора 22 для получения кода сигнала, соответствующего знаменателю п Д х ( ) з выражениях для К и В. И, на1 :онец, в первом блоке 10 делениг; выполняется операция деления кода сигнала, соответствующего числителю (выход первого блока 9 вычитания на код сигнала, соответствующий знаменателю выход третьего блока 23 вычитания в выражении для параметра К. Операция деления выполняется по сигналу со второго выхода первого элемента 32 задержки, т.е. по задержанному сигналу с выхода второго элемента И 31, и подается этот сигнал на вход синхронизациипервого блока 10 деления. Задержка между сигналом синхронизации блока 18 умножения и блока 17 умнож€;ния, который определяет начало операции перемножения, и сигналом синхронизации блока 10, который определяет начало операции деления, осуществляется в первом элементе 32 задержки и требуется задержка для того, чтобы операция деления начала выполняться пос-5 ле исполнения операций умножения и вычитания. Далее блок 7 выполняет операцию перемножения сигналов с выхода сумматора 14 и сумматора 6, т.е. получение уменьшаемого Е , в лителе выражения дпя параметра 3. Блок 16 выполняет операцию перемножения сигналов с выхода сумматора 13 и сумматора 15, т.е. получение вычитаемого числителе выраже- 15 ния для парс«летра В. Операция умножения в блоках 16 и 7 начинают выполняться по сигналу с выхода второго (элемента И 31 (сигнал конца фрагмента), который подается на входы син- 20 хронизации блоков 16 и 7. Блок 21 вычисляет разность сигналов с выхода блока 7 и блока 16 для получения кода сигнала, соответствующего числиЛоии и J-.

sVy-t xv Z- x выражения для пара- г метраВ,, нЬконед, в блоке 19 вычисляется параметр В, т.е. выполняется деление кода сигнала, соответствующего числителю (выход блока 21 на код сигнала, соответствующего знаменателю (выход блока 23). Синхрониза- 30 ия начала деления выполняется сигалом со второго выхода первого элеента 32 задержки, который подается а вход синхронизации блока 19. Итак а выходе блока 10 будет код сигна- 35 а, соответствующий тангедсу угла наклона прямого края (к), а на выхое блока 19 - код сигнала, соответствующий свободному члену (В) в уравнении Y К Х+В относительно принятой дл системы координат, Далее по сигналам конца фрагмента и конца фрагмента по горизонтали с задержкой относительно сигнала стробирования блоков 10 и 19, устройство переходит в режим начальной готовности. Таким образом, процесс распознавания прямого края заканчивается.

Включение новых блоков и.связей отличает предлагаемое устройство от известного. Для распознавания прямо- 50 го края, с одной стороны, используется интегральная .характеристика объекта в пределах анализируемого объекта (накопленные суммы значений сигнала вдоль строчной развертки ), что 55 позволяет полностью использовать энергию от объекта, а следовательно, распознавать прямой край при более низких отношениях сигнал/шум вплоть до единицы и ниже, с другой сторо- 60 ны, за счет применения нового подхода регрессионного анализа к накопленным данным, сохраняется высокая разрешающая способность (оценки параметров К и В - несмещенные) и повышается точность определения направления прямого края в присутствии шумов Таким образом, по сравнению с известным предлагаемое устройство позволяет повысить достоверность распознавания прямого края при отношениях сигнал/шум 3. Кроме того, поскольку в известном используется последовательный принцип распознавания, то для проверки, например тридцати направлений, требуе.тся тридцать кадров, в предлагаемом же устройстве процесс распознавания заканчивается по окончании сканирования анализируемого фрагмента, т.е. требуемое время меньше или равно времени кадра. Таким образом, время распознавания уменьшается в несколько десятков раз, при этом, структура устройсва проста и легко реализуема и не требуется для уменьшения времени распознавания ставить большое количество устройств, каждое из которых настроено на определенное направлени и тем самым усложнять структуру предлагаемого устройства.

Формула изобретения .

1. Устройство для распознавания прямого края объекта, содержащее последовательно объединенные телевизионный датчик, вход которого соединен с выходом синхроимпульсов блока синхронизации, и аналого-цифровой преобразователь, первый блок вычитания, блок элементов И, первый, второй и третий сумматоры, отличающееся тем, что, с целью повышения достоверности и уменьшения времени распознавания, в устройство введены первый блок умножения, первый блок деления, последовательно соединенные второй блок умножения, четвертый сумматор, третий блок умножения, второй блок вычитания и второй блок деления, последовательно соединенные первый квадратор, пятый сумматор, четвертый блок умножения и третий блок вычитания, а также второй квадратор, пятый и шестой блоки умножения и блок управления, первый, второй, третий и четвертый входы которого соединены соответственно с выходами тактовых, строчных , строчных гасящих и кадровых гасящих импульсов блока синхронизации, первый выход блока управления подключен к входам стробирования блока элементов И и первого сумматора, второй выход - к входу синхронизации второго блока умножения и к входам стробирования второго, третьего и пятого су маторов, третий выход - к входу стробирования четвертого сумматора, четвертый выход - к входам синхронизации первого, третьего, четвертого и шестого блоков умножения.

пятый выход - к входам синхронизации первого и второго блоков деления шестой выход - к входу сброса первого суьчматора, седьмой выход - к входам сброса второго, третьего, четвертого и пятого сумматоров, восьмой выход - к второму входу четвертого и первому входу шестого блоков умножения, девятый выход - к входу первого квадратора, информационному входу третьего сумматора и к первому входу второго блока умножения, второй вход которого соединен с выходом первого сумматора, выход аналого-цифрового преобразователя подключен к информационнс)1у входу блока элементов И, выход которого соединен с информационным входом первого сумглатора, выход которого соединен с информационным входом второго сумматора, выход которого подключен к первому входу пятого блока умножения и к первому входу первого блока умножения, выход которого соединен с первым входом первого блока вычитания, выход которого соединен с первым входом первого блока деления, выход третьего сумматора подсоединен к вторым входам первого и третьего блоков умножения и к входу второго квалратора, выход которого соединен с вторым входом третьего блока вычитания, выход которого подключен к вторым входам первого и второго блоков деления, второй вход пятого блока умножения соединен с выходом пятого сумматора, а выход - с вторым входом второго блока вычитания, второй вход шестого блока умножения соединен с выходом четвертого сумматора, а выход - с вторым входом первого блока вычитания.

2. Устройство по п.1, отличаю щ е е с я тем; что блок управления содержит первый счетчик строчных импульсов, первый счетчик тактовых импульсов, последовательно включенные регистр координаты -Х, первую схему сравнения, первый триггер, первый элемент И, второй счетчик строчных импульсов, вторую схему сравнения, второй элемент И, первый элемент задержки и первый элемент ИЛИ, последовательно соединенные регистр координаты Y, третью схему сравнения, второй триггер, третий элемент И, второй счетчик тактовых

импульсов, четвертую сравнения, второй элемент и второ элемент ИЛИ, а также регистр и третий элемент ИЛИ, первый и второй входы которого являются соответственно третьим и четвертым входами блока, а

выход подключен к второму входу ВТОрого элемента ИЛИ и к входу сброса первого счетчика тактовых импульсов, счетный вход которого является первы входом блока, а выход подключен к второму входу третьей схемы сравнения, выход первого счетчика строчных импульсов подключен к второму входу первой схемы сравнения, а счетный вход и вход сброса соединены соответственно с вторым и четвертым входами блока, второй вход первого элемента ИЛИ соединен с четвертым входом блока, а выход является седьмым выходом блока и подключен к i входу сброса второго счетчика строчных импульсов и к входу установки в нулевое состояние первого триггера, выход которого соединен с вторым входом третьего элемента И, третий вход которого подключен к первому входу блока, а выход является первым выходом блока, выход второго элемента ИЛИ соединен с входом установки в нулевое состояние второго триггера, с входами сброса второго счетчика тактовых импульсов и является шестым выходом блока, второй вход первого элемента И является вторым входом блока, выход регистра подключен к вторым входам второй и четвертой схем сравнения и является восьмым выходом блока, выход второго счетчика строчных импульсов является девятым выходом блока, выход четвертой схемы сравнения подключен к второму входу второго элемента И и является вторым выходом блока, выход второго элемента И явля€ тся четвертым выходом блока, второй выход первого элемента задержки является пятым выходом блока, второй выход второго элемента задержки является третьим выходом блока.

Источники информации, принятые во внимание при экспертизе

1,Авторское свидетельство СССР № 548873, кл. G Об К 9/00, 1975,

2. Авторское свидетельство СССР по заявке 2815580, кл. G 06 к 9/00 1979 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распознавания прямого края объекта | 1984 |

|

SU1179391A2 |

| Устройство для распознавания прямого края объекта | 1988 |

|

SU1587552A1 |

| Устройство для распознавания прямого края объекта | 1987 |

|

SU1439636A1 |

| Устройство для распознавания прямого края объекта | 1988 |

|

SU1716549A1 |

| Устройство для диагностики и прогнозирования отказов | 1989 |

|

SU1629898A1 |

| Устройство для распознавания прямолинейных элементов изображений | 1979 |

|

SU873252A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1257638A1 |

| Генератор случайных чисел | 1986 |

|

SU1417006A1 |

| Устройство для измерения отношения сигнала к помехе в телевизионном канале | 1985 |

|

SU1292206A1 |

| Устройство для выделения прямолинейных элементов контура изображения | 1988 |

|

SU1628069A1 |

Авторы

Даты

1982-07-30—Публикация

1980-12-17—Подача