Изобретение относится к вычислительной технике и предназначено для выполнения операции преобразования кодов прямоугольных координат У и X в коды полярных координат г и ip измеряемой величины и может быть, в частности, использовано при построении специализированного цифрового вычислителя (СЦВ) и генератора окружностей телевизионного устройства отражения информации (УОИ) метеорологической радиолокационной станции (МРЛ). : ,

Цель изобретения - упрощение и повышение быстродействия цифрового преобразователя координат (ЦПК),

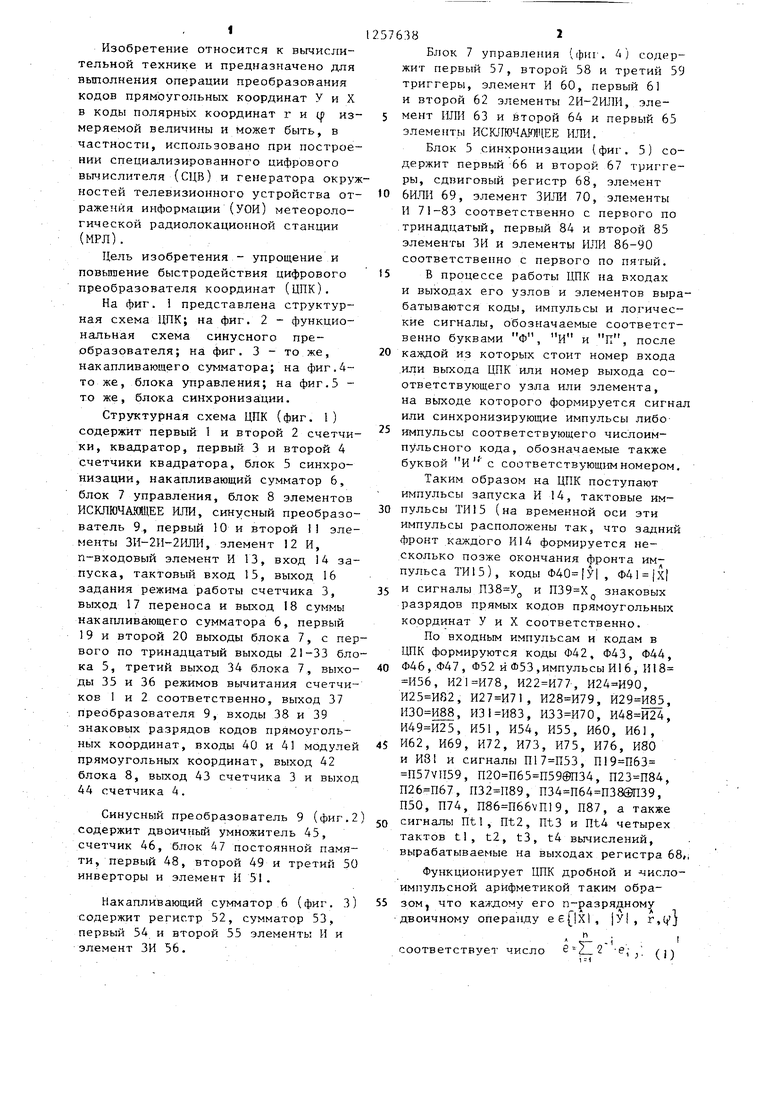

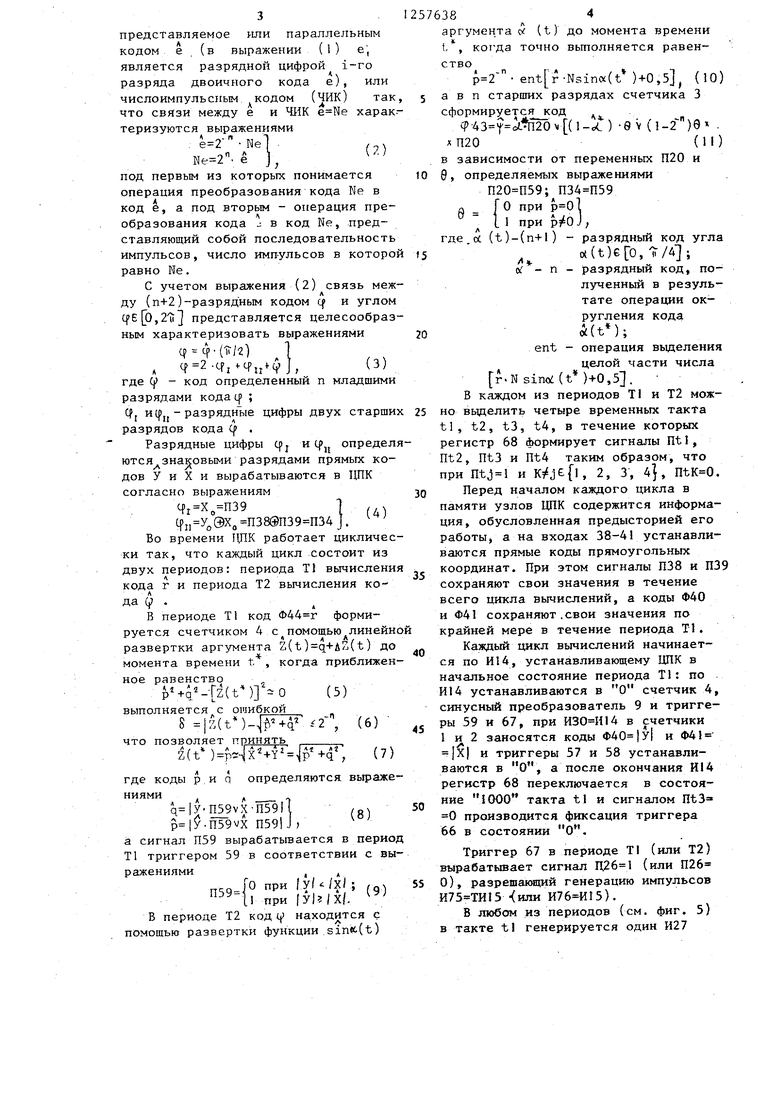

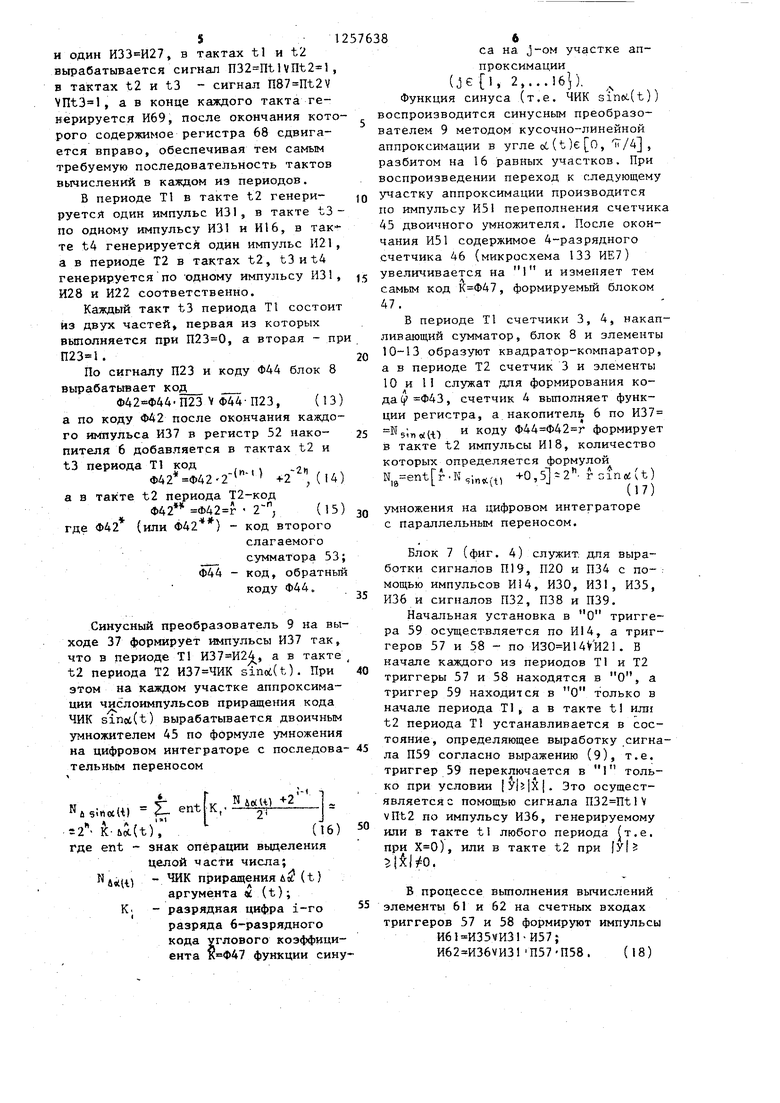

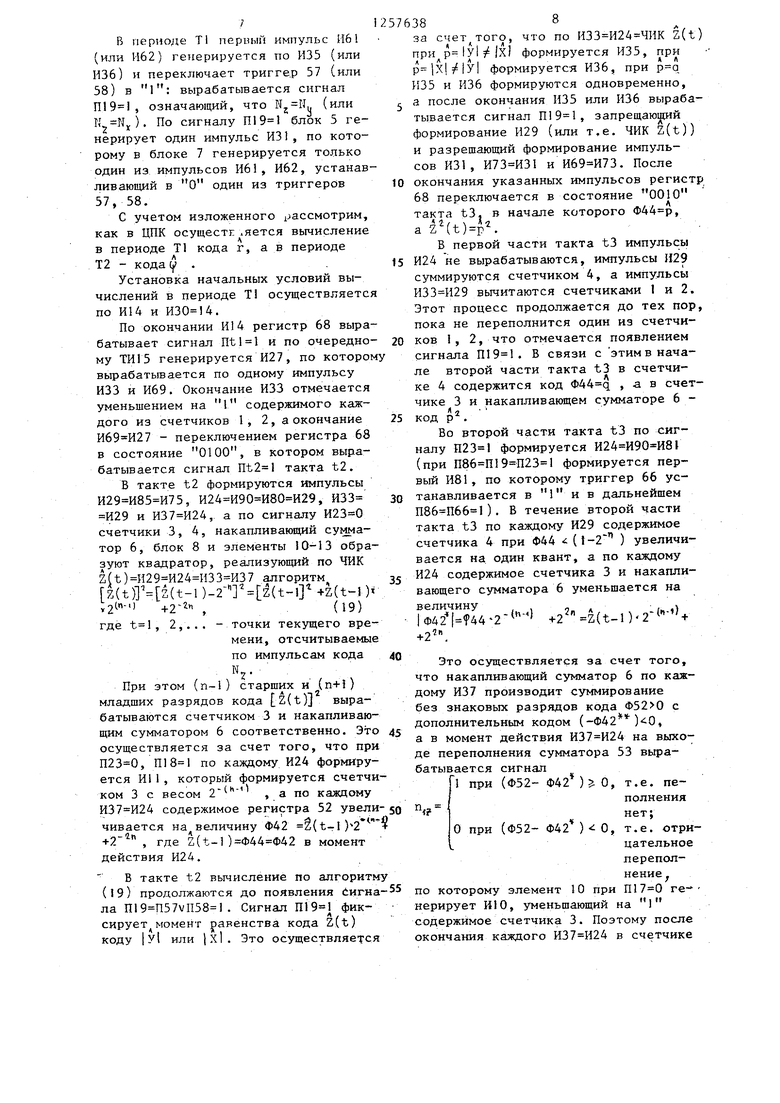

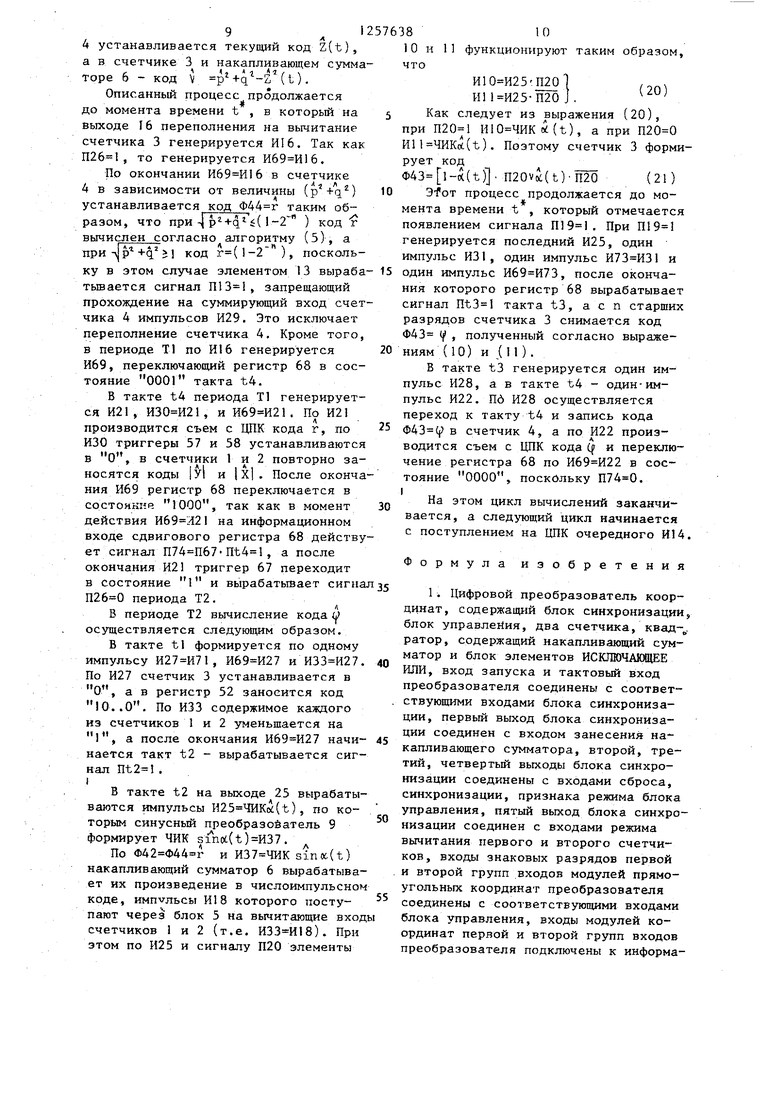

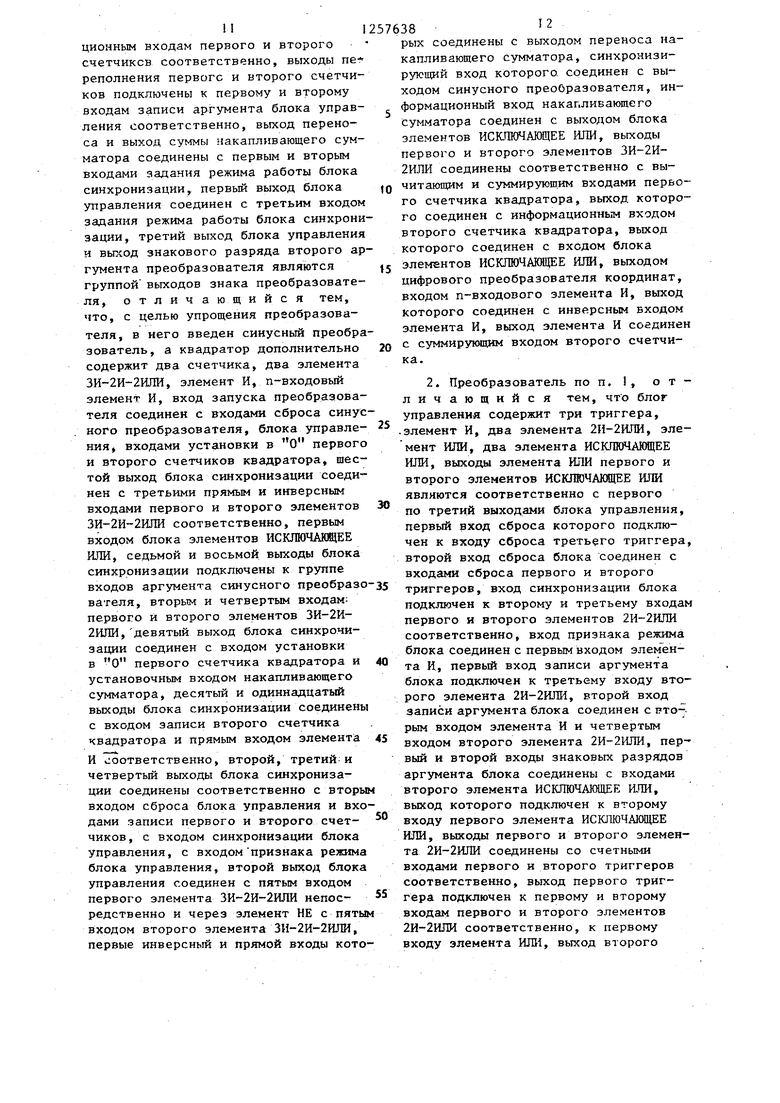

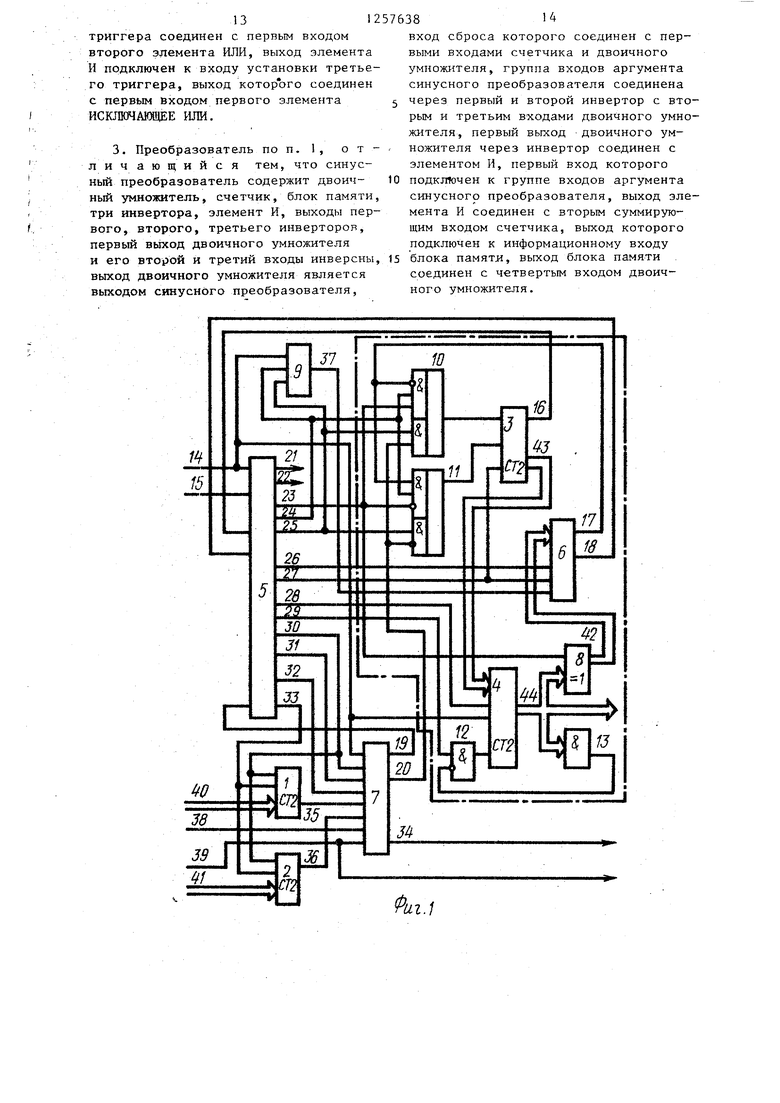

На фиг. 1 представлена структурная схема ЦПК; на фиг. 2 - функциональная схема синусного преобразователя; на фиг. 3 - то же, накапливающего сумматора; на фиг.4- то же, блока управления; на фиг.5 - то же, блока синхронизации.

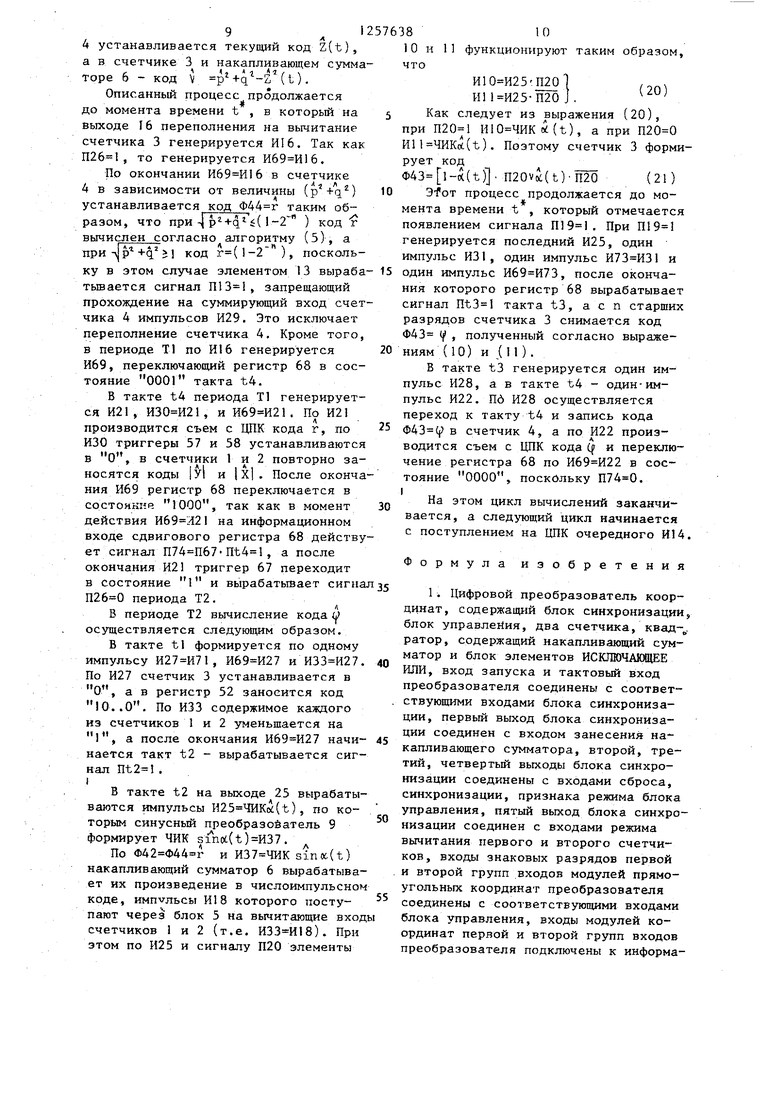

Структурная схема ЦПК (фиг. I) содержит первый 1 и второй 2 счетчики, квадратор, первый 3 и второй 4 счетчики квадратора, блок 5 синхронизации, накапливающий сумматор 6, блок 7 управления, блок 8 элементов ИСКЛЮЧАКЙЦЕЕ ИЛИ, синусный преобразователь 9, первый 10 и второй элементы ЗИ-2И-2ИЛИ, элемент 12 И, п-входовый элемент И 13, вход 4 запуска, тактовый вход 15, выход 16 задания режима работы счетчика 3, выход 17 переноса и выход 18 суммы накапливающего сумматора 6, первый 19 и второй 20 выходы блока 7, с первого по тринадцатый выходы 21-33 блока 5, третий выход 34 блока 7, выходы 35 и 36 режимов вычитания счетчиков 1 и 2 соответственно, выход 37 преобразователя 9, входы 38 и 39 знаковых разрядов кодов прямоугольных координат, входы 40 и 41 модулей прямоугольных координат, выход 42 блока 8, выход 43 счетчика 3 и выход 44 счетчика 4.

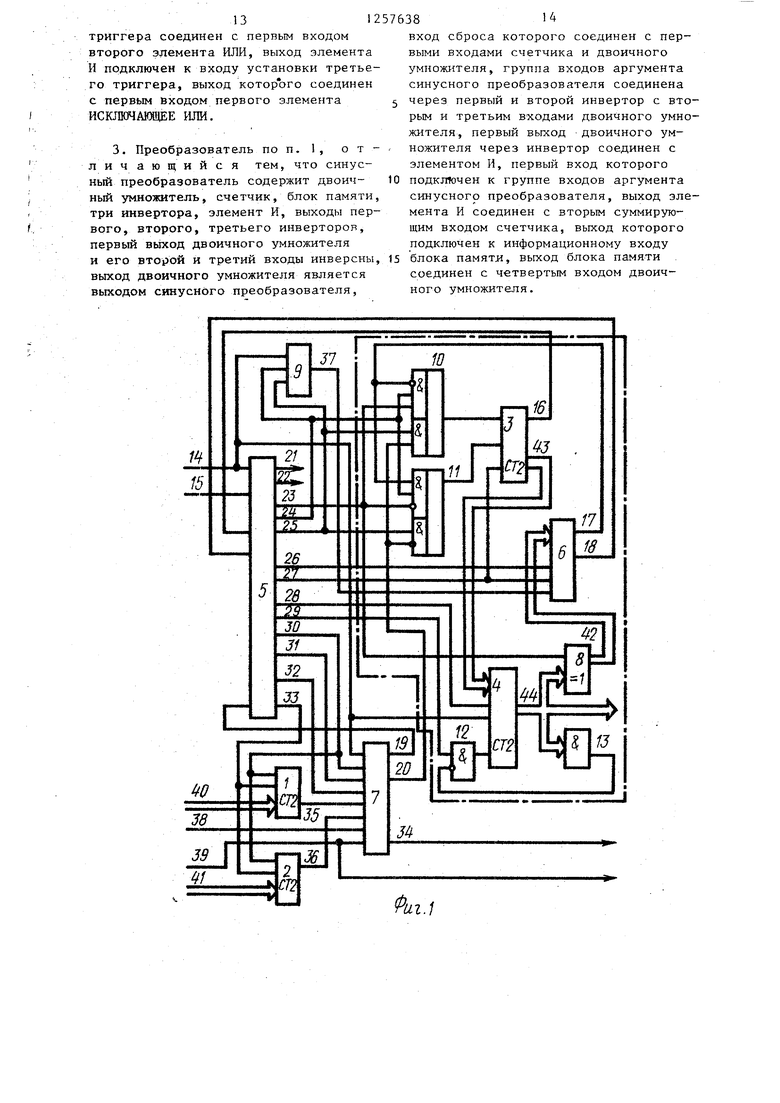

Синусный преобразователь 9 (фиг. содержит двоичный умножитель 45, счетчик 46, блок 47 постоянной памяти, первый 48, второй 49 и третий 5 инверторы и элемент И 51.

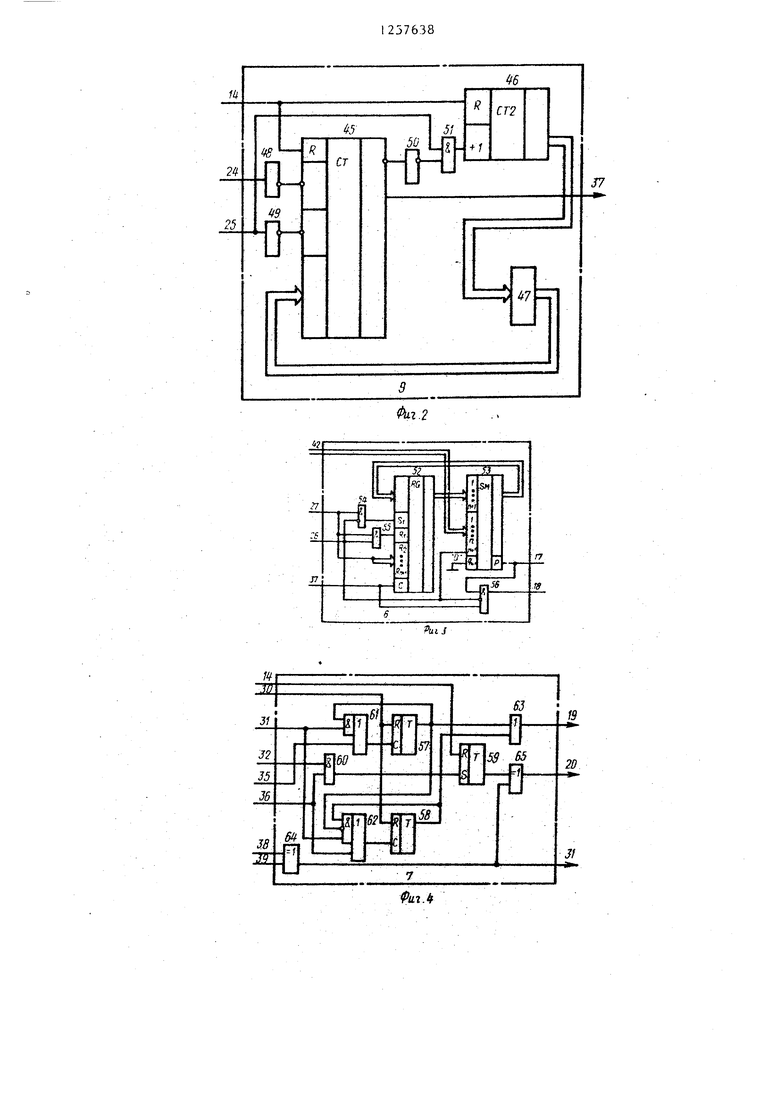

Накапливающий сумматор ,6 (фиг. 3 содержит регистр 52, сумматор 53, первый 54 и второй 55 элементы И и элемент ЗИ 56.

fS

2576382

Блок 7 управления (фиг. 4) содержит первый 57, второй 58 и третий 59 триггеры, элемент И 60, первый 61 и второй 62 элементы 2И-2ИЛИ, эле- 5 мент ИЛИ 63 и второй 64 и первый 65 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ.

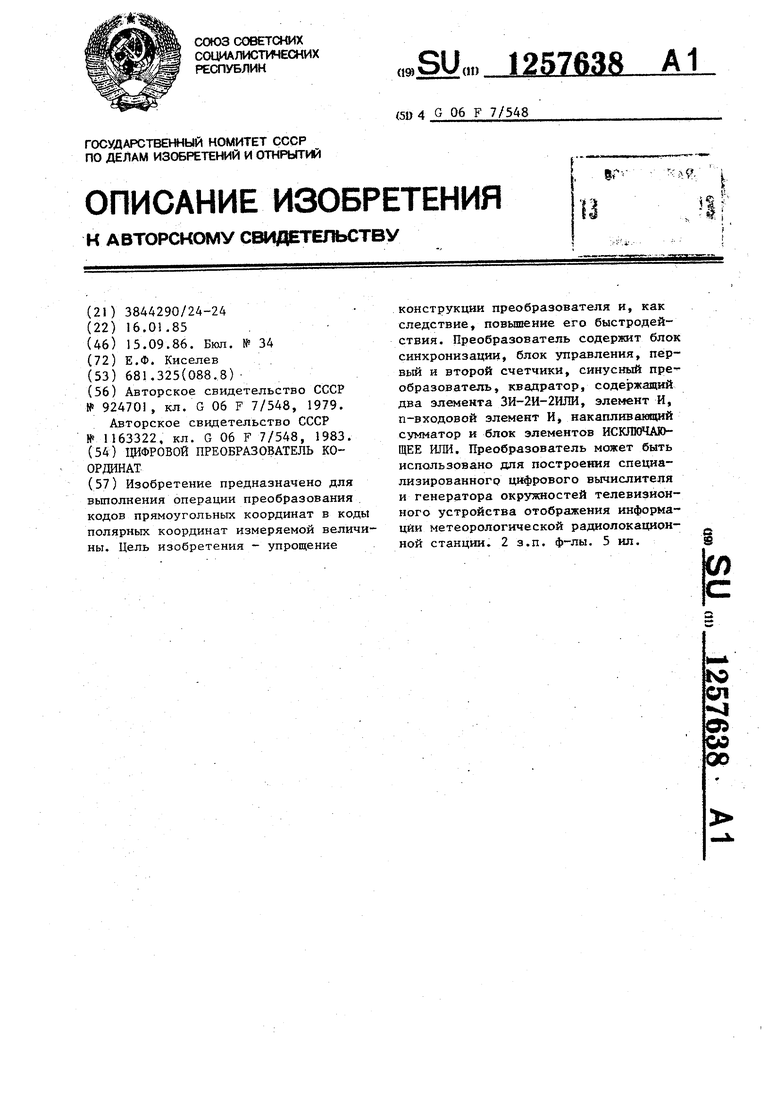

Блок 5 синхронизации (фиг. 5) содержит первый 66 и второй 67 триггеры, сдвиговый регистр 68, элемент 10 били 69, элемент ЗИЛИ 70, элементы И 71-83 соответственно с первого по .тринадцатый, первый 84 и второй 85 элементы ЗИ и элементы ИЛИ 86-90 соответственно с первого по пятый, В процессе работы ЦПК на входах и выходах его узлов и элементов вырабатываются коды, импульсы и логические сигналы, обозначаемые соответственно буквами Ф

И и И

после

каждой из которых стоит номер входа или выхода ЦПК или номер выхода соответствующего узла или элемента, на выходе которого формируется сигнал или синхронизирующие импульсы либо- импульсы соответствующего числоим- пульсного кода, обозначаемые также буквой и с cooтвeтcтвyющIiмномером.

Таким образом на ЦПК поступают импульсы запуска И 14, тактовые им- пульсы ТИ15 (на временной оси эти импульсы расположены так, что задний фронт каждого И14 формируется несколько позже окончания фронта импульса ТИ15), коды , Ф41 )Х|

35

и сигналы и знаковых

разрядов прямых кодов прямоугольных координат У и X соответственно.

По входным импульсам и кодам в ЦПК формируются коды Ф42, Ф43, Ф44,

Ф46,.Ф47, Ф52 и Ф53 ,импульсы И16 , И18 И56, , , , , , , , , , , , , И51, И54, И55, И60, И61,

И62, И69, И72, И73, И75, И76, И80 и И81 и сигналы , , П20 П65 П59Ш34, , П26-П67, , (ЭП39, П50, П74, n86 n66vm9, Ц87, а также сигналы nt1, nt2, nt3 и Ц14 четырех тактов tl, t2, t3, t4 вычислений, вырабатываемые на выходах регистра 68,; Функционирует ЦПК дробной и число- импульсной арифметикой таким образом, что каждому его п-разря ном - двоичному операнду , |У| , г,(

. h . ,

число

а-Ц 2.

е;

J

(1)

или

представляемое

л I кодом е (. в выражении

параллельным

(1) е,

является разрядной цифрой i-го разряда двоичного кода е), или

числоимпульсным кодом

(ЧИК)

так

что связи между е и ЧИК характеризуются выражениями

. Ne

л

е

под первым из которых понимается

операция преобразования кода Ne в

л

код е, а под вторым - операция преобразования кода -: в код Ne, представляющий собой последовательность импульсов, число имп-ульсов в которой равно Ne.

С учетом выражения (2) связь между (п+2)-разрядным кодом с| и углом (,2 u представляется целесообразным характеризовать выражениями

C cf (1t/2) I

д .cf,.cf.(, (3) где (р - код определенный п младшими разрядами кодац) ; Уг и(р„ - разрядною цифры двух старших

1 т IIд

разрядов кода Cj .

Разрядные цифры Cf j и ( определя ются зна1 овыми разрядами прямых кодов У и X и вырабатываются в ЦПК согласно выражениям (|)|,Уд@Хд П38@П39 П34

Во времени ЦПК работает циклически так, что каждый цикл состоит из двух периодов: периода Т1 вычисления кода г и периода Т2 вычисления кода ( .

В периоде Т1 код формируется счетчиком 4

(4)

с помощью линейно развертки аргумента Z(t)q+AS(t) до

когда приближен(5)

момента времени t ное равенство

J,(t)o

выполняется с ошибкой

8 jz(t)-jF+F ,

что позволяет принять

Z(t )(

л Р.и

определяются вьфаже(8)

где коды

ниями

q |y n5 9vX-05911

р |У-П59УХ П59 J а сигнал П59 вырабатывается в период Т1 триггером 59 в соответствии с выражениями,д

П59 РМ,;/|| (9) 1 при I У1 I Х{.

В периоде Т2 код ( находится с помощью развертки функции sin«c.(t)

,

10

й 15

20

25

-

30

35

й

40

45

50

SS

аргумента of (t) до момента времени ,

f, , ко1 да точно выполняется равенство

ent r-Nsin(x(t )+0,5 (Ю) а в п старших разрядах счетчика 3 сформируется код

(,C ) -0 V (1-2)6 . П20(11)

в зависимости от переменных П20 и 9, определяемых выражениями

Q Го при

I 1 при J ,

где ОС (t)-(n+l) - разрядный код угла o{(t),7/Ai; 0 - п - разрядный код, полученный в результате операции округления кода ACtM; ent - операция выделения

целой части числа r.N sinoi (t )+0,5. В каждом из периодов Т1 и Т2 можно вьзделить четыре временных такта tl, t2, t3, t4, в течение которых регистр 68 формирует сигналы nt1, nt2, nt3 и nt4 таким образом, что при ntj I и , 2, 3, 4, .

Перед началом каждого цикла в памяти узлов ЦПК содержится информация, обусловленная предысторией его работы, а на входах 38-41 устанавливаются прямые коды прямоугольных координат. При зтом сигналы П38 и П39 сохраняют свои значения в течение всего цикла вычислений, а коды Ф40 и Ф41 сохраняют.свои значения по крайней мере в течение периода Т1.

Каждый цикл вычислений начинается по И14, устанавливающему ЦПК в начальное состояние периода Т1: по И14 устанавливаются в О счетчик 4, синусный преобразователь 9 и триггеры 59 и 67, при в счетчики 1 и 2 заносятся коды и Ф41- 1х) и триггеры 57 и 58 устанавливаются в О, а после окончания Й14 регистр 68 переключается в состояние 000 такта tl и сигналом ntS 0 производится фиксация триггера 66 в состоянии О.

Триггер 67 в периоде Т1 (или Т2) вырабатывает сигнал (или П26 0), разрешающий генерацию импульсов -(или ).

В любом из периодов (см. фиг. 5) в такте tl генерируется один И27

и один , в тактах tl и t2 вырабатывается сигнал П32 П11vnt2 l, в тактах t2 и t3 - сигнал , а в конце каждого такта ге- керируется И69, после окончания которого содержимое регистра 68 сдвигается вправо, обеспечивая тем самым требуемую последовательность тактов вычислений в каждом иэ периодов.

В периоде Т1 в такте t2 генерируется один импульс И31, в такте t3- по одному импульсу И31 и И16, в такте t4 генерируется один импульс И21, а в периоде Т2 в тактах t2, t3Ht4 генерируется по одному импульсу И31, И28 и И22 соответственно.

Каждый такт t3 периода Т1 состоит из двух частей первая из которых выполняется при , а вторая - при .

По сигналу П23 и коду ФА4 блок В

вырабатывает код

Ф42 Ф44 П23 VФ44-П23, (13) а по коду ФД2 после окончания каждого импульса И37 в регистр 52 накопителя 6 добавляется в тактах t2 и t3 периода Т1 код

Ф42 Ф42 2- - , (14) а в такте t2 периода Т2-код

где Ф42 (или Ф42

) ;

(15)

код второго слагаемого сумматора 53; Ф44 - код, обратный коду Ф44.

Синусный преобразователь 9 на выходе 37 формирует импульсы И37 так, что в периоде Т1 , а в такте t2 периода Т2 sinoi(t). При этом на каждом участке аппроксимации числоимпульсов приращения кода

/ . ,

ЧИК sino6(t) вырабатывается двоичным умножителем 45 по формуле умножения на цифровом интеграторе с последова- тельным переносом

- Г «п-1- Гк ХН) +2 1

rtocU) А- ent К,ji Jk-bSKt), - (16)

ent - знак операции выделения целой части числа; ЧИК приращения АО (t) аргумента 2 (t); К. - разрядная цифра i-ro разряда 6-разрядного кода углового коэффициента функции сину A«tH)

са на J-OM участке аппроксимации(j€{l, 2,...б). , Функция синуса (т.е. ЧИК sinoi.(t)) воспроизводится синусным преобразователем 9 методом кусочно-линейной аппроксимации в угле oi (t )е о, , разбитом на 16 равных участков. При воспроизведении переход к следующему участку аппроксимации производится по импульсу И51 переполнения счетчика 45 двоичного умножителя. После окончания И51 содержимое 4-разрядного счетчика 46 (микросхема 133 ИЕ7) увеличивается на 1 и изменяет тем самым код , формируемый блоком 47.

В периоде Т1 счетчики 3, 4, накапливающий сумматор, блок 8 и элементы 10-13 образуют квадратор-компаратор, а в периоде Т2 счетчик 3 и элементы 10 и П служат для формирования кода (f Ф43, счетчик 4 вьшолняет функции регистра, а накопитель 6 по И37 (.-) и коду формирует в такте t2 импульсы И18, количество которых определяется формулой N,-ent.K,i(,, +0, b.nc(t)

умножения на цифровом интеграторе с параллельным переносом.

0

5

Блок 7 (фиг. 4) служит, для выработки сигналов П19, II20 и 1134 с помощью импульсов И14, ИЗО, И31, И35, И36 и сигналов П32, ПЗВ и П39.

Начальная установка в О триггера 59 осуществляется по И14, а триггеров 57 и 58 - по ИЗО И14У И21 . В начале каждого из периодов Т1 и Т2 триггеры 57 и 58 находятся в О, а триггер 59 находится в О только в начале периода Т1, а в такте tl или t2 периода Т1 устанавливается в состояние, определяющее выработку сигнала П59 согласно выражению (9), т.е. триггер 59 переключается в только при условии yjilXJ. Это осущест- является с помощью сигнала II32 IItlV vnt2 по импульсу И36, генерируемому или в TaiKTe t любого периода (т.е. при ), или в такте t2 при |У|

.

В процессе вьшолнения вычислений элементы 61 и 62 на счетных входах триггеров 57 и 58 формируют импульсы

И61 И35ЧИ31-И57;

И62 И36 И31П57 П5В.(1В)

5

0

5

в периоде Т1 первый импульс 1161 (или И62) генерируется по И35 (или Н36) и переключает триггер 57 (или 58) в вырабатывается сигнал , означающий, что Wj,rJ, (или N N). По сигналу блок 5 генерирует один импульс И31, по которому в блоке 7 генерируется только один из импульсов И61, И62, устанавливающий в О один из триггеров 57, 58.

С учетом изложенного рассмотрим, как в ЦПК в периоде Т1 кода г, а в периоде

10

15

20

осущестЕ яется вычисление периоде Т1 кода г, а в Т2 - кода(|; .

Установка начальных условий вычислений в периоде Т осуществляется по И14 и .

По окончании И14 регистр 68 вырабатывает сигнал и по очередному ТИ15 генерируется И27, по которому вьфабатывается по одному импульсу ИЗЗ и И69. Окончание ИЗЗ отмечается уменьшением на 1 содержимого каждого из счетчиков 1, 2, а окончание 25 - переключением регистра 68 в состояние 0100, в котором вырабатывается сигнал такта t2.

В такте t2 формируются импульсы , , И33 И29 и , а по сигналу счетчики 3, 4, накапливающий сумматор 6, блок 8 и элементы 10-13 образуют квадратор, реализующий по ЧИК

г,(г) алгоритм Гп/л. 1 ,/j- лг .,

z((t- ( +z(t-i )t

+2- ,(19)

где , 2,... - точки текущего времени, отсчитываемые по импульсам кода

, N,

за , что по Z(t при p lyi/lx формируется И35, при формируется И36, при И35 и Pi36 формируются одновременно, J а после окончания И35 или И36 выраба тывается сигнал , запрещающий формирование И29 (или т,е. ЧИК Z(t) и разрешающий формирование импульсов Й31, и . После окончания указанных импульсов регист 68 переключается в состояние 0010 такта t3. в начале которого ,

а 2(t)4.

В первой части такта t3 импульсы И24 не вырабатываются, импульсы Я29 суммируются счетчиком 4, а импульсы вычитаются счетчиками 1 и 2. Этот процесс продолжается до тех пор пока не переполнится один из счетчиков 1, 2, что отмечается появлением сигнала . В связи с этим в начале второй части такта t3 в счетчике 4 содержится код , з. в счет чике 3 и накапливающем сумматоре 6 л л

код р- .

Во второй части такта t3 по сигналу формируется (при формируется первый И81, по которому триггер 66 устанавливается в 1 и в дальнейщем ). В течение второй части такта t3 по каждому И29 содержимое счетчика 4 при Ф44 ; (1-2 ) увеличивается на один квант, а по каждому И24 содержимое счетчика 3 и накапливающего сумматора 6 уменьшается на

30

35

величину

|042 hf44

+2

) (t-l) 2- - 4

40

45

7 При этом (п-1 ) старших и (п+)

младших разрядов кода Z(t) вырабатываются счетчиком 3 и накапливающим сумматором 6 соответственно. Это осуществляется за счет того, что при , по каждому И24 формируется И1 1, который формируется счетчиком 3 с весом , а по каждому содержимое регистра 52 увели-50 чивается на величину Ф42 2(t-l ) , где Z(t-l) в момент действия И24.

В такте t2 вычисление по алгоритму

Это осуществляется за счет того, что накапливающий сумматор 6 по каждому И37 производит суммирование без знаковых разрядов кода с дополнительным кодом ()0, а в момент действия на выходе переполнения сумматора 53 вырабатывается сигнал

1 при (Ф52- Ф42)5.0, т.е. пеполнения

п

if

нет;

О при (Ф52- Ф42)0, т.е. отрицательноепереполнение .

(19) продолжаются до появления Сигна- по которому элемент 10 при гела ni9 n57vn58 l. Сигнал П19 сирует момент равенства кода коду |У1 или 1x1. Это

1 фикZ(t) осуществляется

10

15

20

25

576388

за , что по Z(t) при p lyi/lx формируется И35, при формируется И36, при И35 и Pi36 формируются одновременно, J а после окончания И35 или И36 вырабатывается сигнал , запрещающий формирование И29 (или т,е. ЧИК Z(t)) и разрешающий формирование импульсов Й31, и . После окончания указанных импульсов регистр 68 переключается в состояние 0010 такта t3. в начале которого ,

а 2(t)4.

В первой части такта t3 импульсы И24 не вырабатываются, импульсы Я29 суммируются счетчиком 4, а импульсы вычитаются счетчиками 1 и 2. Этот процесс продолжается до тех пор, пока не переполнится один из счетчиков 1, 2, что отмечается появлением сигнала . В связи с этим в начале второй части такта t3 в счетчике 4 содержится код , з. в счетчике 3 и накапливающем сумматоре 6 л л

код р- .

Во второй части такта t3 по сигналу формируется (при формируется первый И81, по которому триггер 66 устанавливается в 1 и в дальнейщем ). В течение второй части такта t3 по каждому И29 содержимое счетчика 4 при Ф44 ; (1-2 ) увеличивается на один квант, а по каждому И24 содержимое счетчика 3 и накапливающего сумматора 6 уменьшается на

30

35

величину

|042 hf44

+2

) (t-l) 2- - 4

Это осуществляется за счет того, что накапливающий сумматор 6 по каждому И37 производит суммирование без знаковых разрядов кода с дополнительным кодом ()0, а в момент действия на выходе переполнения сумматора 53 вырабатывается сигнал

1 при (Ф52- Ф42)5.0, т.е. пеполнения

п

if

нет;

О при (Ф52- Ф42)0, т.е. отрицательноепереполнение .

нерирует И10, уменьшающий на l содержимое счетчика 3. Поэтому после окончания каждого в счетчике

4 устанавливается текущий код Z(t), а в счетчике 3 и накапливающем сумматоре 6 - код V (t).

Описанный процесс продолжается до момента времени t , в который на выходе Г 6 переполнения на вьиитание счетчика 3 генерируется И16. Так как П26-I, то генерируется .

По окончании в счетчике 4 в зависимости от величины (p +q) устанавливается код таким образом, что при-J ( ) код г

вычислен согласно алгоритму (5), а при -Jp +4 51 код г(1-2), поскольку в этом случае элементом 13 выраба- 15 один импульс , после оконча- тьшается сигнал , запрещающий ния которого регистр 68 вырабатывает

п

25

прохождение на суммирующий вход счетчика 4 импульсов И29, Это исключает переполнение счетчика 4, Кроме того, в периоде Т1 по И16 генерируется И69, переключающий регистр 68 в состояние 0001 такта t4.

В такте t4 периода Т1 генерируется И21, , и . По И21 производится съем с ЦИК кода г, по ИЗО триггеры 57 и 58 устанавливаются в О, в счетчики 1 и 2 повторно заносятся коды |У1 и 1х1. После окончания И69 регистр 68 переключается в состоякир. 1000, так как в момент 30 действия на информационном входе сдвигового регистра 68 действует сигнал П74 П67 nt4 5, а после окончания И2 триггер 67 переходит в состояние 1 и вырабатывает сигнал 35 периода Т2.

В периоде Т2 вычисление кода у осуществляется следунидим образом.

В такте tl формируется по одному импульсу , и . 40 По И27 счетчик 3 устанавливается в О, а в регистр 52 заносится код 10..О. По ИЗЗ содержимое каждого из счетчиков 1 и 2 уменьшается на , а после окончания начи- 45 нается такт t2 - вырабатывается сигнал .

сигнал такта t3, а с п старщих разрядов счетчика 3 снимается код Ф43 (j , полученный согласно выраже- 20 ниям (10) и ,(11).

В такте t3 генерируется один импульс И28, а в такте t4 - один-импульс И22. П6 И28 осуществляется переход к такту t4 и запись кода в счетчик 4, а по И22 производится съем с ЦПК кода Cf и переключение регистра 68 по в состояние 0000, поскольку .

На этом цикл вычислений заканчивается, а следующий цикл начинается с поступлением на ЦПК очередного И14

Формула изобретения

1. Цифровой преобразователь координат, содержащий блок синхронизации блок управления, два счетчика, квадратор, содержащий накапливающий сумматор и блок элементов ИСКШОЧАЩЕЕ ИЛИ, вход запуска и тактовый вход преобразователя соединены с соответствующими входами блока синхронизации, первый выход блока синхронизации соединен с входом занесения накапливающего сумматора, второй, третий, четвертый выходы блока синхронизации соединены с входами сброса, синхронизации, признака режима блока управления, пятый выход блока синхро низации соединен с входами режима вычитания первого и второго счетчиков, входы знаковых разрядов первой и второй групп входов модулей прямоугольных координат преобразователя соединены с соответствующими входами блока управления, входы модулей координат первой и второй групп входов преобразователя подключены к информа

В такте t2 на выходе 25 вырабатываются импульсы H25 4IiKoi(t), по которым синусный преобразоёатель 9 формирует ЧЙК sinot(t)H37.

По и sin«.(t) накапливающий сумматор 6 вырабатывает их произведение в числоимпульсном коде, импульсы И18 которого поступают через блок 5 на вычитающие вход счетчиков 1 и 2 (т.е. ). При этом по И25 и сигналу П20 элементы

5763810

10 и 11 функционируют таким образом, что

И10 И25 П20 ,„„

И11 И25-П20.

5 Как следует из выражения (20), при (t), а при И11 4HKo(.(t). Поэтому счетчик 3 формирует код

(X(t). n20v5;(t)-n20 (21) 10 3foT процесс продолжается до момента времени t , который отмечается появлением сигнала , При генерируется последний И25, один импульс И31, один импульс и

п

сигнал такта t3, а с п старщих разрядов счетчика 3 снимается код Ф43 (j , полученный согласно выраже- ниям (10) и ,(11).

В такте t3 генерируется один импульс И28, а в такте t4 - один-импульс И22. П6 И28 осуществляется переход к такту t4 и запись кода в счетчик 4, а по И22 производится съем с ЦПК кода Cf и переключение регистра 68 по в состояние 0000, поскольку .

На этом цикл вычислений заканчивается, а следующий цикл начинается с поступлением на ЦПК очередного И14.

Формула изобретения

1. Цифровой преобразователь координат, содержащий блок синхронизации, блок управления, два счетчика, квад„. ратор, содержащий накапливающий сумматор и блок элементов ИСКШОЧАЩЕЕ ИЛИ, вход запуска и тактовый вход преобразователя соединены с соответствующими входами блока синхронизации, первый выход блока синхронизации соединен с входом занесения накапливающего сумматора, второй, третий, четвертый выходы блока синхронизации соединены с входами сброса, синхронизации, признака режима блока управления, пятый выход блока синхронизации соединен с входами режима вычитания первого и второго счетчиков, входы знаковых разрядов первой и второй групп входов модулей прямоугольных координат преобразователя соединены с соответствующими входами блока управления, входы модулей координат первой и второй групп входов преобразователя подключены к информаи

ционньм входам первого и второго счетчиков соответственно, выходы пе реполнения первого и второго счетчиков подключены к первому и второму входам записи аргумента блока управления соответственно, выход переноса и выход суммы накапливающего сумматора соединены с первым и вторым входами задания режима работы блока синхронизации, первый выход блока управления соединен с третьим входом задания режима работы блока синхронизации, третий выход блока управления и выход знакового разряда второго аргумента преобразователя являются группой выходов знака преобразователя, отличающийся тем, что, с целью упрощения преобразователя, в него введен синусный преобразователь, а квадратор дополнительно содержит два счетчика, два элемента ЗИ-2И-2ИЛИ, элемент И, п-входовый элемент И, вход запуска преобразователя соединен с входами сброса синусного преобразователя, блока управления, входами установки в О первого и второго счетчиков квадратора, шестой выход блока синхрониза1ции соединен с третьими прямым и инверсным входами первого и второго элементов ЗИ-2И-2ИЛИ соответственно, первым входом блока элементов ИСКЛЮЧАЩЕЕ ИЛИ, седьмой и восьмой выходы блока синхронизации подключены к группе входов аргумента синусного преобразо вателя, вторым и четвертым входам; первого и второго элементов ЗИ-2И- 2ИЛИ, девятый выход блока синхронизации соединен с входом установки в О первого счетчика квадратора и установочным входом накапливающего сумматора, десятый и одиннадцатый выходы блока синхронизации соединены с входом записи второго счетчика квадратора и прямым входом элемента

И соответственно, второй, третий-и четвертый выходы блока синхронизации соединены соответственно с вторым входом сброса блока управления и входами записи первого и второго счетчиков, с входом синхронизации блока управления, с входом признака режима блока управления, второй выход блока управления соединен с пятым входом первого элемента ЗИ-2И-2ИЛИ непосредственно и через элемент НЕ с пятым входом второго элемента ЗИ-2И-2ИЛИ, первые инверсный и прямой входы кото

5

57638 2

рых соединены с выходом переноса накапливающего сумматора, синхронизирующий вход которого соединен с выходом синусного преобразователя, информационный вход накапливакндего сумматора соединен с выходом блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы первого и второго элементов ЗИ-2И- 2ИЛИ соединены соответственно с выJQ читающим и суммирующим входами первого счетчика квадратора, выход которого соединен с информационным входом второго счетчика квадратора, выход которого соединен с входом блока

15 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выходом цифрового преобразователя координат, входом п-входового элемента И, выход которого соединен с инверсным входом элемента И, выход элемента И соединен

20 с суммирукяцим входом второго счетчика.

25

35

30

40

5

0

5

2. Преобразователь по п. 1, отличающийся тем, чт о блог управления содержит три триггера, элемент И, два элемента 2И-2ИЛИ, эле- мент ИЛИ, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы элемента ИЛИ первого и второго элементов ИСКШЧАЩЕЕ ИЛИ являются соответственно с первого по третий выходами блока управления, первый вход сброса которого подключен к входу сброса третьего триггера, второй вход сброса блока соединен с входами сброса первого и второго триггеров, вход синхронизации блока подключен к второму и третьему входам первого и второго элементов 2И-2ИЛИ соответственно, вход признака режима блока соединен с первым входом элемента И, первый вход записи аргумента блока подключен к третьему входу второго элемента 2И-2ИЛИ, второй вход записи аргумента блока соединен с РТО-. рым входом элемента И и четвертым входом второго элемента 2И-2ИЛИ, первый и второй входы знаковых разрядов аргумента блока соединены с входами второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подключен к второму входу первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы первого и второго элемента 2И-2ИЛИ соединены со счетными входами первого и второго триггеров соответственно, выход первого триггера подключен к первому и второму входам первого и второго элементов 2И- 2ИЛИ соответственно, к первому входу элемента ИЛИ, выход второго

триггера соединен с первым входом второго элемента ИЛИ, выход элемента И подключен к входу установки третьего триггера, выход которЪго соединен с nepsfciM Входом первого элемента ИСКЛЮЧАЩЕЕ ИЖ,

3. Преобразователь по п. 1, отличающийся тем, что синусный преобразователь содержит двоичный умнотштель, счетчик, блок памяти три инвертора, элемент И, выходы первого, второго, третьего инверторов, первый выход двоичного умножителя и его второй и третий входы инверсны выход двоичного умножителя является выходом синусного преобразователя,

вход сброса которого соединен с первыми входами счетчика и двоичного умножителя, группа входов аргумента синусного преобразователя соединена

через первый и второй инвертор с вторым и третьим входами двоичного умножителя, первый выход двоичного умножителя через инвертор соединен с элементом И, первый вход которого

подклточен к группе входов аргумента синусного преобразователя, выход элемента И соединен с вторым суммирующим входом счетчика, выход которого подключен к информационному входу

блока памяти, выход блока памяти соединен с четвертым входом двоичного умножителя.

lit

5

2«

CT

25

9

7

J7

/

+ 1

СГ2

37

JT

2L

fi

s«

Pfl

/7

,J5

W

,i.5

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой преобразователь координат | 1983 |

|

SU1163322A1 |

| Цифровой преобразователь координат | 1979 |

|

SU842801A1 |

| Генератор концентрических окружностей для телевизионного индикатора | 1983 |

|

SU1124373A1 |

| Функциональный преобразователь кода угла и дальности | 1981 |

|

SU1008734A1 |

| Цифровой преобразователь координат | 1979 |

|

SU873239A1 |

| Микропроцессорное устройство для цифрового преобразования координат | 1982 |

|

SU1104523A1 |

| Устройство для симметрирования токов трехфазных четырехпроводных сетей | 1990 |

|

SU1758773A1 |

| Цифровой преобразователь координат | 1981 |

|

SU960834A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА | 1996 |

|

RU2115229C1 |

| Функциональный преобразователь | 1986 |

|

SU1352476A1 |

Изобретение предназначено для вьшолнения операции преобразования кодов прямоугольньпс координат в коды полярных координат измеряемой величины. Цель изобретения - упрощение конструкции преобразователя и, как следствие, повышение его быстродействия. Преобразователь содержит блок синхронизации, блок управления, первый и второй счетчики, синусный преобразователь, квадратор, содержащий два элемента ЗИ-2И-2Ш1И, элемент И, п-входовой элемент И, накапливагаций сумматор и блок элементов ИСКШОЧАКЬ ЩЕЕ ИЛИ. Преобразователь может быть использовано для построения специализированного цифрового вычислителя и генератора окружностей телевизионного устройства отображения информации метеорологической радиолокационной станции, 2 з.п. ф-лы. 5 нл. (П с: iC 01 1 Од 00 00

| Универсальный цифровой преобразователь координат | 1980 |

|

SU924701A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Цифровой преобразователь координат | 1983 |

|

SU1163322A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-15—Публикация

1985-01-16—Подача