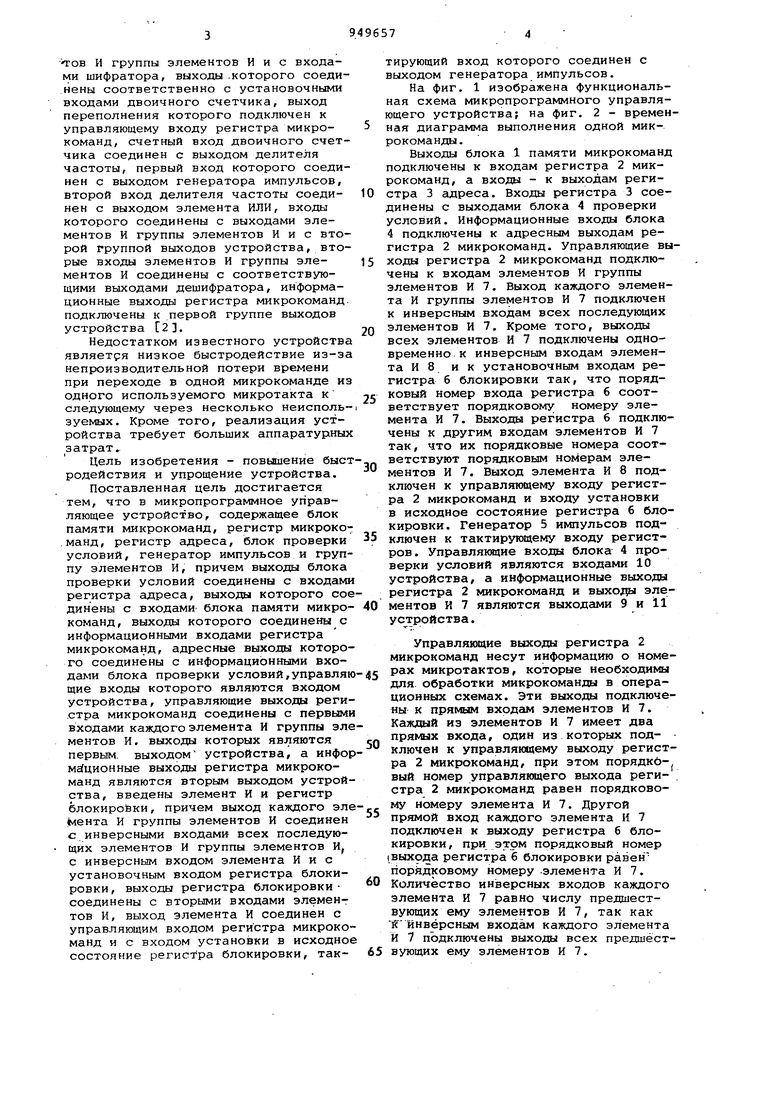

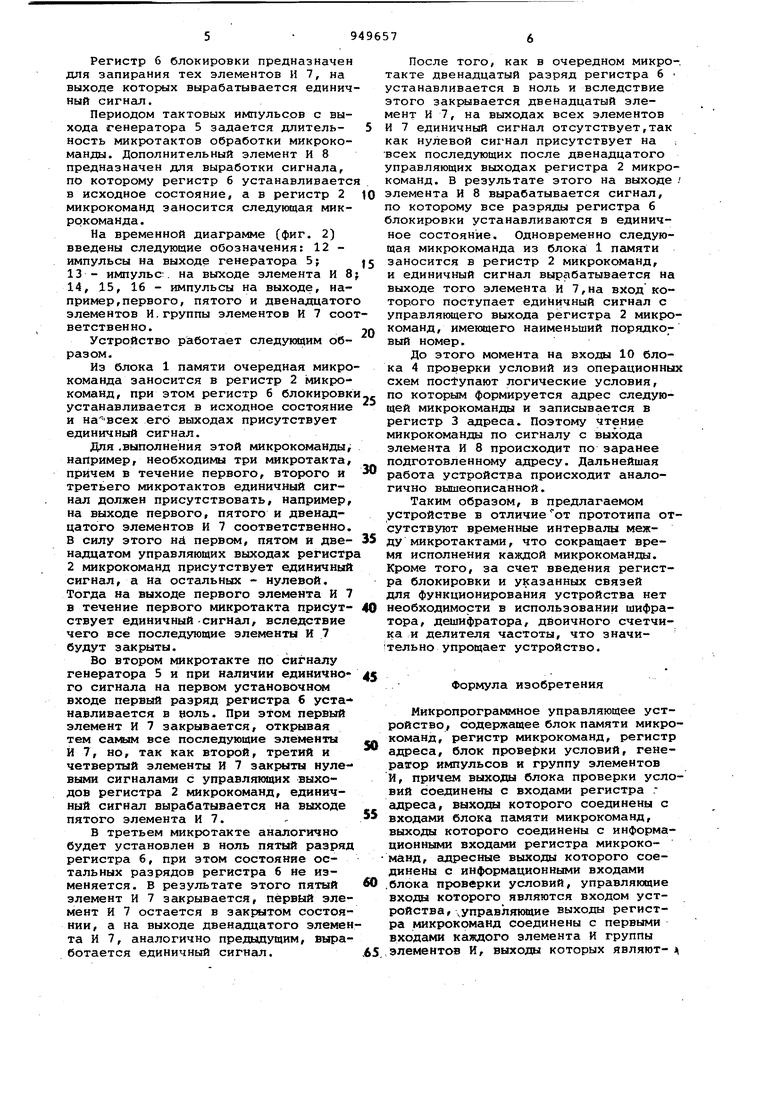

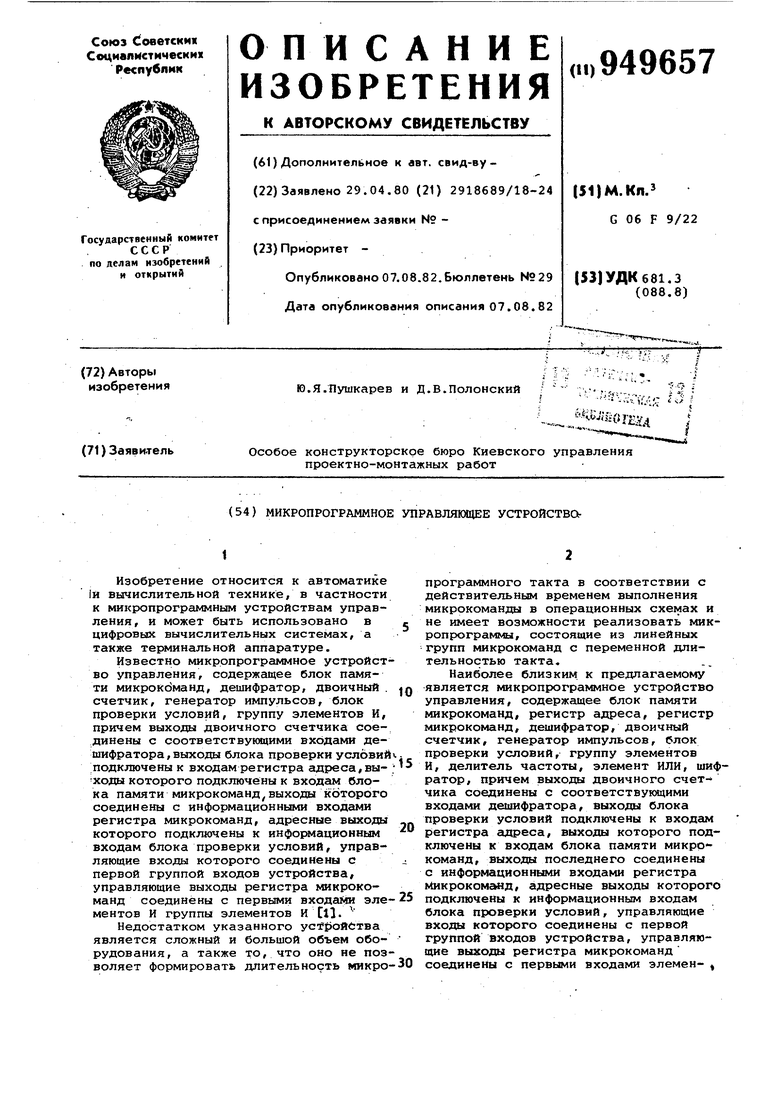

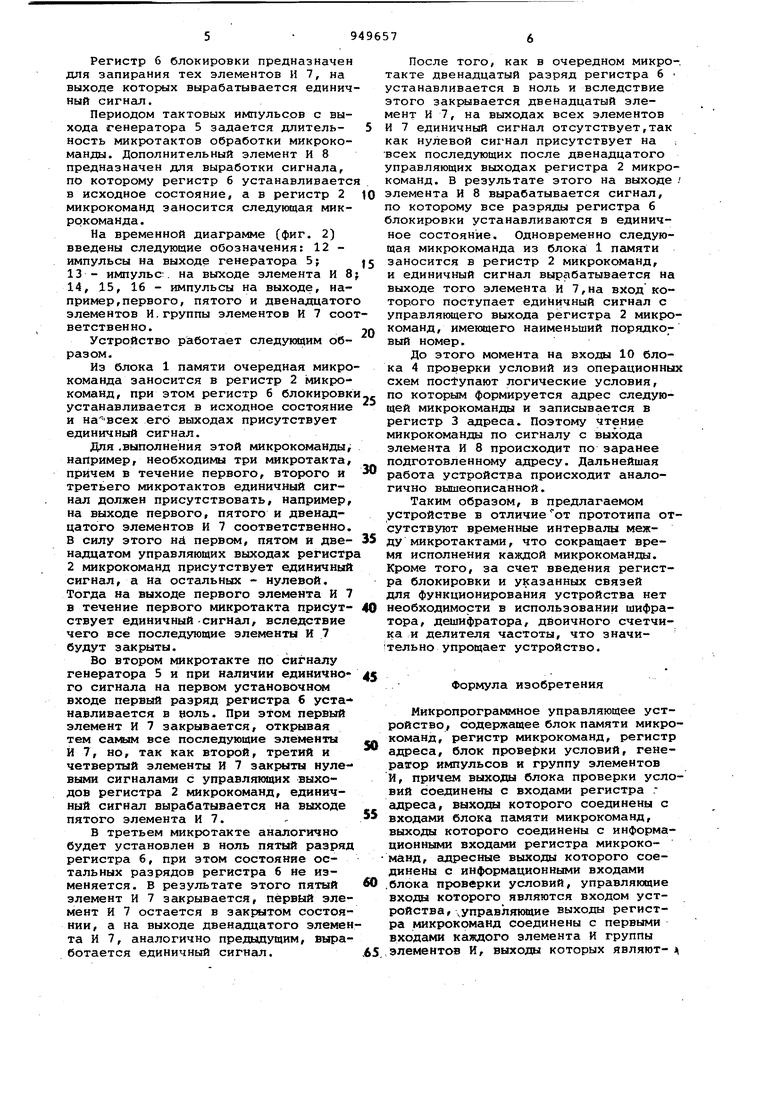

Изобретение относится к автоматике 1й вычислительной технике, в частности к микропрограммным устройствам управления, и может быть использовано в цифровых вычислительных системах, а также терминальной аппаратуре. Известно микропрограммное устройст во управления, содержащее блок памяти микрокбманд, дешифратор, двоичный . счетчик, генератор импульсов, блок проверки условий, группу элементов И, причем выходы двоичного счетчика соединены с соответствующими входами дешифратора , выходы блока проверки условий подключены к входам регистра адреса,выходы которого подключены к входам блока Пс1мяти микрокоманд выходал которого соединены с информационными входами регистра микрокоманд, адресные выходы которого подключены к информационным входам блока проверки условий, управляющие входы которого соединены с первой группой входов устройства, управляющие выходы регистра микрокоманд соединены с первыми входами эле ментов И группы элементов И Ц. Недостатком указанного усгройСтва является сложный и большой объем оборудования, а также то, что оно не поз воляет формировать длительность микро программного такта в соответствии с действительным временем выполнения микрокоманд:ца в операционных схемах и не имеет возможности реализовать микропрограммы, состоящие из линейных групп микрокоманд с переменной длительностью такта. Наиболее близким к предлагаемому является микропрограммное устройство управления, содержащее блок памяти микрокоманд, регистр адреса, регистр микрокоманд, дешифратор, двоичный счетчик, генератор импульсов, блок проверки условий, группу элементов И, делитель частоты, элемент ИЛИ, шифратор, причем выходы двоичного счетчика соединены с соответствующими входами дешифратора, выходы блока проверки условий подключены к входам регистра адреса, выходы которого подключены к входам блока памяти микро команд, выходы последнего соединены с информационными входами регистра Микрокомгжд, адресные выходы которого подключены к информационным входам блока проверки условий, управляющие входы которого соединены с первой группой входов устройства, управляющие выходы регистра микрокоманд соединены с первыми входами элемен- тов И группы элементов И и с входами шифратора, выходы .которого соединены соответственно с установочными входами двоичного счетчика, выход переполнения которого подключен к управляющему входу регистра микрокоманд, счетный вход двоичного счетчика соединен с выходом делителя частоты, первый вход которого соединен с выходом генератора импульсов, второй вход делителя частоты соединен с выходом элемента ИЛИ, входы которого соединены с выходами элементов И группы элементов И и с второй группой выходов устройства, вторые входы элементов И группы элементов И соединены с соответствующими выходами дешифратора, информационные выходы регистра микрокоманд подключены к первой группе выходов устройства Г23, Недостатком известного устройства является низкое быстродействие из-за непроизводительной потери времени при переходе в одной микрокоманде из одного используемого микротакта к следующему через несколько неиспользуемых. Кроме того, реализация устройства требует больших аппаратурных затрат. Цель изобретения - повиаение быст родействия и упрощение устройства. Поставленная цель достигается тем, что в микропрограммное управляющее устройство, содержащее блок памяти микрокоманд, регистр микроко.манд, регистр адреса, блок проверки условий, генератор импульсов и группу элементов И, причем выходал блока проверки условий соединены с входами регистра адреса, выходы которого сое динены с входами блока памяти микрокоманд, выходы которого соединены с информационными входами регистра микрокоманд, адресные выходы которого соединены с информационными входами блока проверки условий,управляю щие входы которого являются входом устройства, управляющие выходы регистра микрокоманд соединены с первыми входами каждого элемента И группы эле ментов И. выходы которых являются первым, выходом устройства, а инфор мйционные выходы регистра микрокоманд являются вторым выходом устройства, введены элемент И и регистр блокиройки, причем выход каждого эле ента И группы элементов И соединен с инверсными входами всех последующих элементов И группы элементов И с инверсным входом элемента И и с установочным входом регистра блокировки, выходы регистра блокировкисоединены с вторыми входами элементов И, выход элемента И соединен с управляющим входом регистра микрокоманд и с входом установки в исходное состояние регистра блокировки, тактирующий вход которого соединен с выходом генератора импульсов. На фиг. 1 изображена функциональная схема микропрограммного управляющего устройства на фиг. 2 - временная диаграмма выполнения одной микрокоманды. Выходы блока 1 памяти микрокоманд подключены к входам регистра 2 микрокоманд, а входы - к выходам регистра 3 адреса. Входы регистра 3 соединены с выходами блока 4 проверки условий. Информационные входы блока 4 подключены к адресным выходам регистра 2 микрокоманд. Управляющие выходы регистра 2 микрокоманд подключены к входам элементов И группы элементов И 7. Выход каждого элемента И группы элементов И 7 подключен к инверсным входам всех последующих элементов И 7, Кроме того, выходы всех элементов И 7 подключены одновременно к инверсным входам элемента И 8 и к установочным входам регистра б блокировки так, что порядковый номер входа регистра 6 соответствует порядковому номеру элемента И 7. Выходы регистра 6 подключены к другим входам элементов И 7 так, что их порядковые номера соответствуют порядковым номерам элементов И 7. Выход элемента И 8 подключен к управляющему входу регистра 2 микрокоманд и входу установки в исходное состояние регистра 6 блокировки. Генератор 5 импульсов подключен к тактирукяцему входу регистров . Управляющие входы блока 4 проверки условий являются входами 10 устройства, а информационные выходы регистра 2 микрокоманд и выходы элементов И 7 являются выходами 9 и 11 устройства. Управляющие выходы регистра 2 микрокоманд несут информацию о номерах микротактов, которые необходимы для. обработки микрокоманды в операционных схемах. Эти выходы подключены к прямым входг1М элементов И 7. Каждый из элементов И 7 имеет два прянмх входа, один из которых подключен к управляющему выходу регистра 2 микрокоманд, при этом порядки-, вый номер управлякядего выхода регистра 2 микрокоманд равен порядковому номеру элемента И 7. Другой прямой вход каждого элемента И 7 подключен к выходу регистра б блокировки, при этом порядковый номер выхрда регистра 6 блокировки равен порядковому номеру .элемента И 7. Количество инверсных входов каждого элемента И 7 равно числу предшествующих ему элементов И 7, так как ffинверсным входам каждого элемента И 7 подключены выходы всех предшествующих ему элементов и 7. Регистр G блокировки предназначен для запирания тех элементов И 7, на выходе которых вырабатывается единич ный сигнал. Периодом тактовых импульсов с выхода генератора 5 задается длительность микротактов обработки микрокоманды. Дополнительный элемент И 8 предназначен для выработки сигнала, по которому регистр б устанавливаетс в исходное состояние, а в регистр 2 микрокоманд заносится следующая микрокоманда. На временной диаграмме (фиг. 2) введены следующие обозначения: 12 импульсы на выходе генератора 5; 13 - импулье. на выходе элемента И 8 14, 15, 16 - импульсы на выходе, например, первого, пятого и двенадцатог элементов И.группы элементов И 7 соо ветственно. Устройство работает следукндим образом. Из блока 1 памяти очередная микро команда заносится в регистр 2 микрокоманд, при этом регистр 6 блокировк устанавливается в исходное состояние и на всех его выходах присутствует единичный сигнал. Для .выполнения этой микрокоманды, например, необходимы три микротакта. причем в течение первого, второго и третьего микротактов единичный сигнал должен присутствовать, например, на выходе первого, пятого и двенадцатого элементов И 7 соответственно. В силу этого на первом, пятом и двенадцатом управляющих выходах регистр 2 микрокоманд присутствует единичный сигнал, а на остальных - нулевой. Тогда на выходе первого элемента И 7 в течение первого микротакта присутствует единичный-сигнал, вследствие чего все последующие элементы И 7 будут закрыты. Во втором микротакте по сигналу генератора 5 и при наличии единично го сигнала на первом установочнс входе первый разряд регистра 6 уста- навливается в ноль. При этом первый элемент И 7 закрывается, открывая тем самым все последующие элементы И 7, но, так как второй, третий и четвертый элементы И 7 закрыты нулевыми сигналами с управляняцих выходов регистра 2 микрокоманд, единичный сигнал вырабатывается на выходе пятого элемента И 7. В третьем микротакте аналогично будет установлен в ноль пятый разряд регистра 6, при этом состояние остальных разрядов регистра 6 не изменяется. В результате этого пятый элемент И 7 закрывается, первый элемент И 7 остается в закрытом состоянии, а на выходе двенадцатого элемен та И 7, аналогично предыдущим, выработается единичный сигнал. После того, как в очередном микро-, такте двенадцатый разряд регистра 6 устанавливается в ноль и вследствие этого закрывается двенадцатый элемент И 7, на выходах всех элементов И 7 единичный сигнал отсутствует,так как нулевой сихнал присутствует на всех последующих после двенадцатого управляющих выходах регистра 2 микрокоманд, в результате этого на выходе / элемента И 8 вырабатывается сигнал, по которому все разряды регистра 6 блокировки устанавливаются в единичное состояние. Одновременно следующая микрокоманда из блока 1 памяти заносится в регистр 2 микрокоманд, и единичный сигнал вырабатывается на выходе того элемента и 7,на вход которого поступает единичный сигнал с управляющего выхода регистра 2 микрокоманд, имеющего наименьший порядковый номер. До этого момента на входы 10 блока 4 проверки условий из операционных схем пос упают логические условия, по которым формируется адрес следующей микрокоманды и записывается в регистр 3 адреса. Поэтому чтение микрокоманды по сигналу с выхода элемента И 8 происходит по заранее подготовленному адресу. Дальнейшая работа устройства происходит аналогично вышеописанной. Таким образом, в предлагаемом устройстве в отличие от прототипа отсутствуют временные интервалы между микротактами, что сокращает время исполнения каждой микрокоманды. Кроме того, за счет введения регистра блокировки и указанных связей для функционирования устройства нет необходимости в использовании шифратора, дешифратора, двоичного счетчика и делителя частоты, что значи тельно упрощает устройство. Формула изобретения Микропрограммное управляющее устройство, содержащее блок памяти микрокоманд, регистр микрокоманд, регистр адреса, блок проверки условий, генератор импульсов и группу элементов И, причем выходы блока проверки условий соединены с входами регистра г адреса, выходы которого соединены с входами блока памяти микрокоманд, выходы которого соединены с информационными входеи да регистра микрокоманд, адресные выходы которого соединены с информационными входами .блока проверки условий, управляющие входвл которого являются входом устройства, управляющие выходы регистра микрокоманд соединены с первыми входами Кс1ждого элемента И группы элементов И, выходы которых являют- J

йя первым выходом устройства, а информационные выходы регистра микрокоманд являются вторым выходом устройства, отличающееся тем, что, с целью повышения быстродействия и упррщеиня устройства, в него введены элемент И и регистр блокировки, причем выход каждого элемента И группы элементов И соединен с инверсными входами всех последующих элементов И группы элементов И, с инверсным входом элемента И и с установочным входом регистра блокировки, соответственно выходы

регистра блокировки соединены с вторыми входами элементов И, выход элемента И соединен с управляющим входом регистра микрокоманд и с входом установки в исходное состояние регистра блокировки, тактирующий вход которого соединен с выходом генератора импульсов.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР

431515, кл. G 06 F 9/12, 26.05.72.

2.Авторское свидетельство СССР

640294, кл. G 06 F 9/16, 30.12.78.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное управляющее устройство | 1981 |

|

SU1005051A1 |

| Микропрограммное управляющее устройство | 1981 |

|

SU970367A1 |

| Микропрограммное управляющее устройство | 1981 |

|

SU1029178A2 |

| Микропрограммное управляющее устройство | 1982 |

|

SU1166109A2 |

| Микропрограммное устройство управления | 1976 |

|

SU640294A1 |

| Микропрограммное управляющее устройство | 1983 |

|

SU1137467A1 |

| Микропрограммное управляющее устройство | 1983 |

|

SU1136161A1 |

| Микропрограммное управляющее устройство | 1982 |

|

SU1084792A2 |

| Микропрограммное устройство управления | 1983 |

|

SU1111161A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1238071A1 |

Авторы

Даты

1982-08-07—Публикация

1980-04-29—Подача