(54) МИКРОПРОГРАММНОЕ УПРАВЛЯЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное управляющее устройство | 1980 |

|

SU949657A1 |

| Микропрограммное управляющее устройство | 1981 |

|

SU1005051A1 |

| Микропрограммное управляющее устройство | 1983 |

|

SU1136161A1 |

| Микропрограммное управляющее устройство | 1983 |

|

SU1137467A1 |

| Микропрограммное управляющее устройство | 1982 |

|

SU1166109A2 |

| Микропрограммное управляющее устройство | 1981 |

|

SU1029178A2 |

| Микропрограммное устройство управления | 1976 |

|

SU640294A1 |

| Микропрограммное управляющее устройство | 1982 |

|

SU1084792A2 |

| Микропрограммное устройство управления | 1984 |

|

SU1238071A1 |

| Многотактное микропрограммное устройство управления | 1983 |

|

SU1151963A1 |

Изобретение относится к автоматике и вычислительной технике, в частности к микропрограммным устройствам управления, и может быть использовано в цифровых вычислительных системах, а также в терминальной аппаратуре.

Известно микропрограммное устройство управления, содержащее блок памяти микрокоманд, регистр адреса, регистр микрокоманд, дешифратор, двоичный счетчик, генератор импульсов, блок проверки условий, группу элементов И, делитель частоты, элемент ИЛИ и шифратор 1 .

Недостатком указанного устройства является низкое быстродействие вследствие непроизводительной потери времени при переходе в одной микрокоманде из одного используемого микротакта к следующему через несколько неиспользуемых .

Наиболее близким к предлагаемому является микропрограммное управляющее устройство, содержащее блок памяти микрокоманд, регистр микрокоманд, регистр адреса, блок проверки условий/ генератор импульсов, группу элементов И, регистр, блокировки и элемент И, причем Bfixojifi блока проверки

условий соедине1||Ь1 с входами регистра адреса, выходы которого соединены с входами блока памяти микрокоманд, выходы которого соединены с информационными входами регистра микрокоманд, адресные выходы которого соединены с информационными входами блока проверки условий, управляющие входы которого являются входом устройст10ва, управляющие выходы регистра микрокоманд соединены с первыми входами каждого элемента И группы элементов И, выходы которых являются первым выходом устройства, а информационные

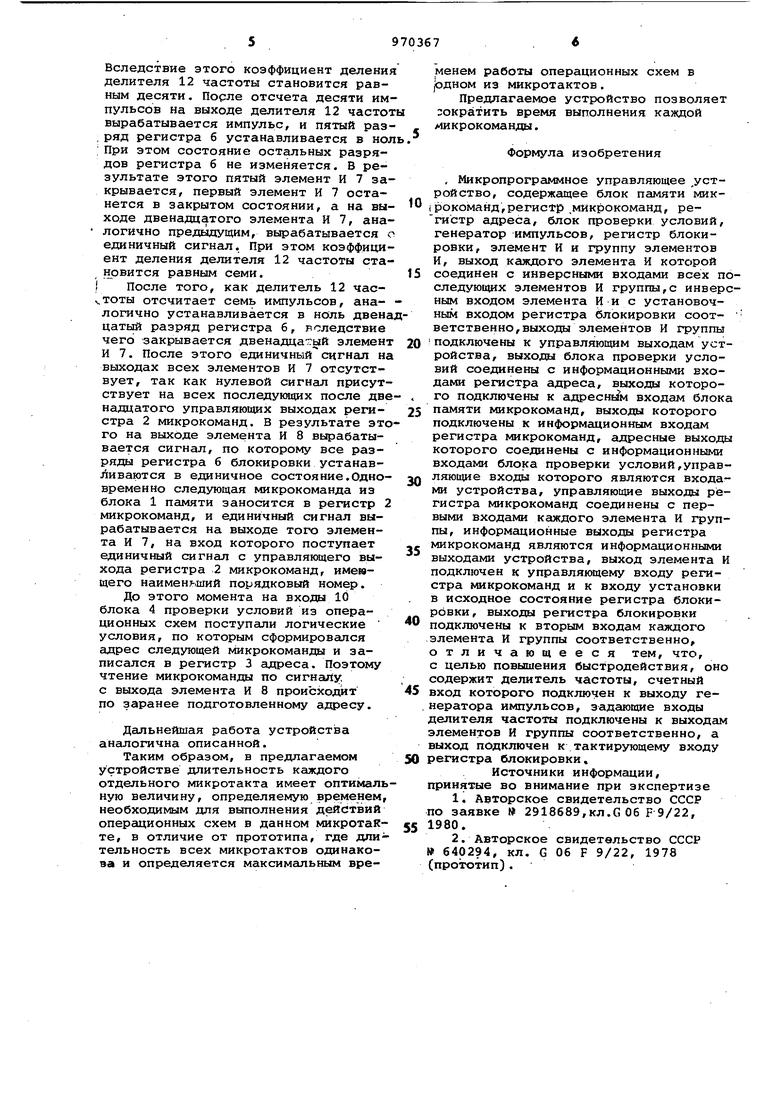

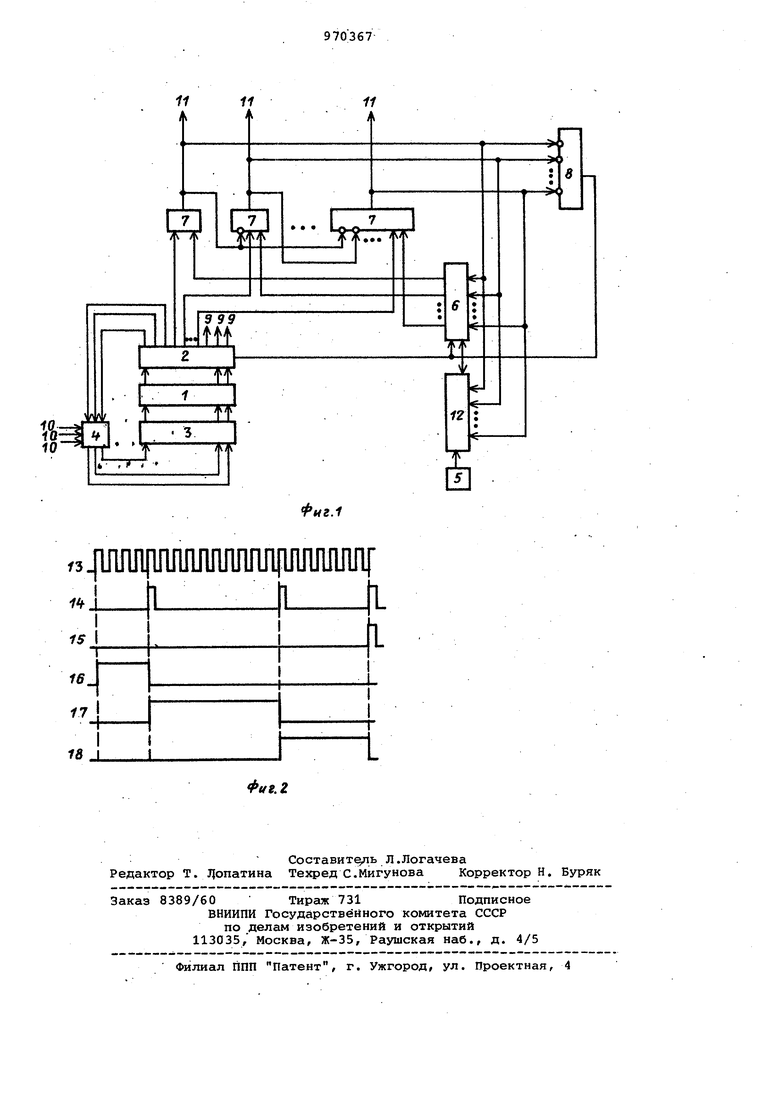

15 выходы регистра микрокоманд являются вторым выходом устройства, выход каждого элемента И группы элементов И соединен с инверсными входами всех последующих элементов И группы элемен20тов И, с инверсным входом элемента И и с установочным входом регистра блокировки соответственно, выходы регистра-блокировки соединены с вторамк входсши элементов И группы эле25ментов И, выход элемента И соединен с управляющим входом регистра микрокоманд и с входом установки в исходное состояние регистра блокировки, тактирующий, вход которого соединен с вы30ходом генератора импульсов Г2. В известном устройстве длительность всех микротактов в каждой микрокоманде постоянна и определяется временем выполнения самой длинной операции, которую инициируют выходные сигналы устройства в операццонных схемах. Разница во времени выполнения коротких и длинных операций может иметь существенное значение, особенно когда выходные сигналы устройства инициируют электронные и механические действия. Поэтому наличие в известном устройстве микротакта с постоянной длительностью, которая определяется вр еменем выполнения самой ДЛИННОЙ операции, значительно сниькает быстродействие устройства и |класс решаемых им задач. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что микропрограммное устройство управления, содержащее блок памяти микрокоманд, регистр микрокоманд, регистр адреса, блок проверки условий, генератор импульсов, регист блокировки, элемент И и группу эле|Ментов И, выход каждого элемента И которой соединен с инверсными вхог дами всех последующих элементов И группы, с инверсным входом элемента И и с установочным входом регистра блокировки соответственно, выхо ды элементов И группы подключены к у равляющим выходам устройства, выходы блока проверки условий соединены с информационными входами регистра адр са, выходы которого подключены к адр ным входам блока памяти микрокоманд, выходы которого подключены к информа ционным входам регистра микрокоманд, адресные выходы которого соединены с информационными входами блока провер ки условий, управляющие входы которо го являются входами устройства, упра ляющие выходы регистра микрокоманд соединены с первыми входами каждого элемента И группы, информационные вы ходы регистра микрокоманд являются информационными выходами устройства, выход элемента И подключен к. управля ющему входу регистра микрокоманд и к входу установки в исходное состояние регистра блокировки/ выходы регистра блокировки подключены к вторым входа каждого элемента И группы соответственно, дополнительно содержит делиаель частоты/счетный вход которого подключен к выходу генератора импуль сов, задающие входы делителя частоты подключены к выходам элементов И гру пы соответственно, а выход подключён к тактирующему входу регистра блокировки. На фиг. 1 изображена (функциональная схема микропрограммного управляю щего уст)ойства; на фиг. 2 - временная диаграмма выполнения одной микрокоманды . Предлагаемое устройство содержит блок 1 памяти микрокоманд, регистр 2 микрокоманд, регистр 3 адреса, блок 4 проверки условий, генератор 5 импульсов, регистр 6 блокировки, группу элементов И 7, элемент И 8, информационные выходы 9 устройства, входы 10 устройства, управляющие выходы 11 устройства, делитель 12 частоты. На временной диаграмме (фиг. 2) введены следующие обозначения: 13 импульсы на выходе генератора 5, 14 - импульсы На выходе делителя 12 частоты, 15 - импульсы на выходе элемента И 8, 16-18 - импульсы на выходе. Например первого, пятого и двенадцатого элементов И группы элементов И 7 соответственно. Устройство работает .следующим образом. Из блока 1 памяти очередная микрокоманда заносится в регистр 2 микрокоманд, при этом регистр 6 блокировки устанавливается в исходное состояние и на всех его выходах присутствует единичный сигнал. Для выполнения микрокоманды необходимы три микротакта, причем в течение первого, второго и третьего микротактов единичный сигнал должен присутствовать, например, на выходе первого, пятого и двенадцатого элементов И 7 соответственно. Длительности микротактов в этом случае должны составлять соответственно че:тыре, десять и семь временныхинтервалов, задаваемых периодом генератора 5 . В силу этого на первом, пятом и двенадцатом управляющих выходах регистра 2 микрокоманд присутствует единичный сигнал, а на остальных нулевой. Тогда на выходе первого эле.мента И 7 вырабатывается единичный сигнал, вследствие чего все последующие элементы И 7 закрыты. При поступлении единичного сигнала с выхода первого элемента И 7 на один из задающих входов делителя 12 частоты коэффициент деления последнего становится равным четырем. После поступления четырех импульсов с выхода генератора 5 на .счетный вход делителя 12 частоты на выхо де последнего вырабатывается импульс, по которому в силу Наличия единичного сигнала на первом установочном входе первый разряд регистра б блокировки устанавливается в ноль. При этом первый элемент И 7 закрывается, открывая тем самым все последующие элементы И 7, но так как второй, третий и четвертый элементы И 7 закрыты нулевыми сигналами с управляющих выходов регистра 2 микрокоманд единичный сигнал вырабатывается на.выходе пятого элемента И 7. Вследствие этого коэффициент делени делителя 12 частоты становится равным десяти. Порле отсчета десяти им пульсов на выходе делителя 12 часто вырабатывается импульс, и пятый раз , ряд регистра б устанавливается в но При этом состояние остальных разрядов регистра 6 не изменяется. В результате этого пятый элемент И 7 за крывается, первый элемент И 7 останется в закрытом состоянии, а на вы ходе двенадцатого элемента И 7, ана логично предьадущим, вырабатывается единичный сигнал. При этом коэффици ент деления делителя 12 частоты ста новится равным семи. После того, как делитель 12 часч,тоты отсчитает семь импульсов, аналогично устанавливается в ноль двен цатый разряд регистра б, вследствие чего закрывается двенадцатый элемен И 7. После этого единичный сигнал н выходах всех элементов И 7 отсутствует, так как нулевой сигнал присут ствует на всех последукнцих после дв надцатого управляющих выходах регистра 2 микрокоманд. В результате эт го на выходе элемента И 8 вырабатывается сигнал, по которому все разряды регистра 6 блокировки устанавливаются в единичное состояние.Одно временно следующая микрокоманда из блока 1 памяти заносится в регистр микрокоманд, и единичный сигнал вырабатывается на выходе того элемента И 7, на вход которого поступает единичный сигнал с управляющего выхода регистра 2 микрокоманд, имеющего наименьший порядковый номер. До этого момента на входы 10 блока 4 проверки условий из операционных схем поступали логические условия, по которым сформировсшся адрес следующей микрокоманды и записался в регистр 3 адреса. Поэтому чтение микрокоманды по сигналу, с выхода элемента И 8 происходит по заранее подготовленному адресу. Дальнейшая работа устройства аналогична описанной. Таким образом, в предлагаемом устройстве длительность каждого отдельного микротакта имеет оптималь ную величину, определяемую временем необходимым для выполнения действий операционных схем в данном микротакте, в отличие от прототипа, где дли тельность всех микротактов одинакова и определяется максимальным временем работы операционных схем в |0дном из микротактов . Предлагаемое устройство позволяет сократить время выполнения каждой /микрокоманды. Формула изобретения , Микропрограммное управляющее устройство, содержащее блок памяти микрокоманд,регистр микрокоманд, регистр адреса, блок проверки условий, генератор импульсов, регистр блокировки, элемент И и группу элементов И, выход каждого элемента И которой соединен с инверсными входами всех последующих элементов И группы,с инверсным входом элемента И и с установочным входом регистра блокировки соответственно,выходы элементов И группы подключены к управляющим выходам устройства, выходы блока проверки условий соединены с информационными входами регистра адреса, выходы которого подключены к адресньйм входам блока памяти микрокоманд, выходы которого подключены к информационным входам регистра микрокоманд, адресные выходы которого соединены с информационными входами блока проверки условий,управляющие входы которого являются входами устройства, управляющие выходы регистра микрокоманд соединены с первыми входами каждого элемента И группы, информационные выходы регистра микрокоманд являются информационными выходами устройства, выход элемента И подключен к управляющему входу регистра микрокоманд и к входу установки в исходное состояние регистра блокировки, выходы регистра блокировки подключены к вторым входам каждого элемента И группы соответственно, отличающееся тем, что, с целью повышения быстродействия, оно содержит делитель частоты, счетный вход которого подключен к выходу генератора импульсов, задающие входы делителя частоты подключены к выходам элементов И группы соответственно, а выход подключен к тактирующему входу регистра блокировки Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР по заявке 2918689,кл.С Об F 9/22, 1980. 2.Авторское свидетельство СССР 640294, кл. G Об F 9/22, 1978 (прототип).

%: 10

Фнг.1

f3j

1t

Авторы

Даты

1982-10-30—Публикация

1981-04-14—Подача