динены с первыми входами элементов И группы элементов.

Недостатком известного устройства является его сложный и большой объем оборудования, за счет того, что оно, во-нервых, не позволяет формировать длительность микропрограммного такта в соответствии с действительным временем выполнения микрокоманды в операционных схемах и не имеет возможности реализовывать микропрограммы, состоящие из линейных групп микрокоманд с переменной длительностью такта.

Цель изобретения - упрощение устройства.

Поставленная цель достигается тем, что в предлагаемое устройство введены делитель частоты, элемент ИЛИ, шифратор, причем входы щифратора соединены с управляющими выходами регистра микрокоманд, информационные выходы которого подключены к первой группе выходов устройства, выходы шифратора соединены соответственно с установленными входами счетчика, выход переполнения которого подключен к управляющему входу регистра микрокоманд, счетный вход счетчика соединен с выходом делителя частоты, первый вход которого соединен с выходом генератора импульсов, второй вход делителя частоты соединен с выходом элемента ИЛИ, входы которого соединены с выходами элементов И группы элементов И и со второй группой выходов устройства, вторые входы элементов И группы элементов И соединены с соответствующими выходами дешифратора.

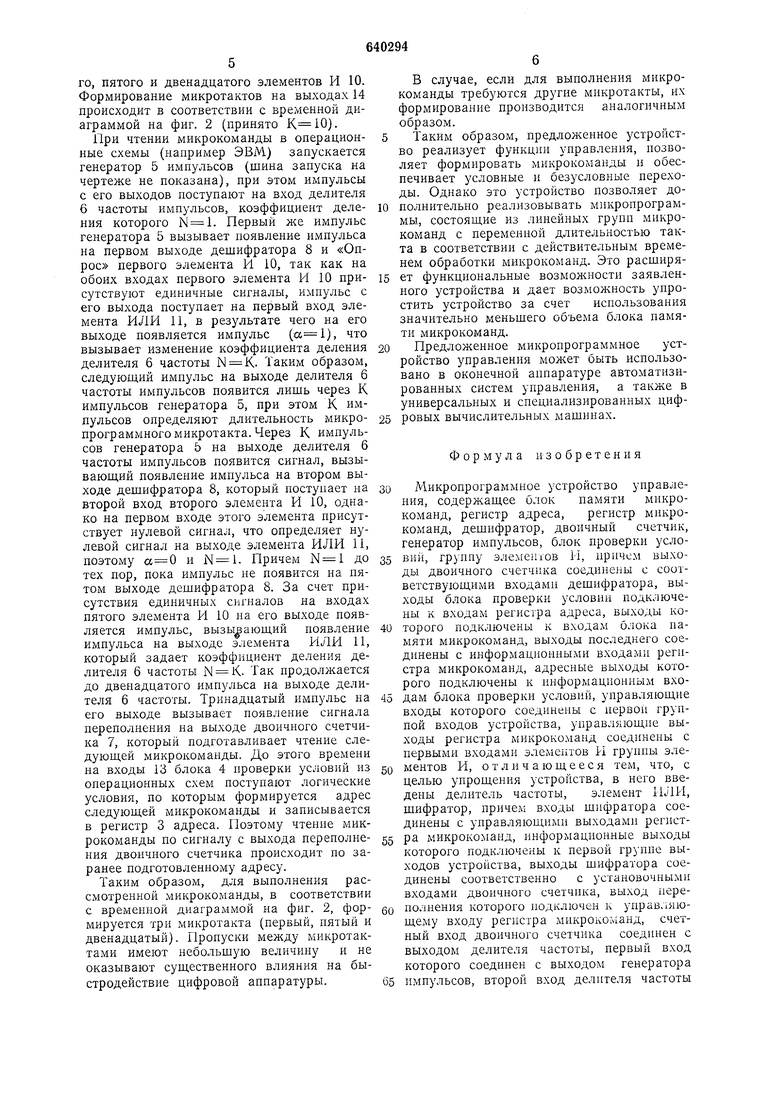

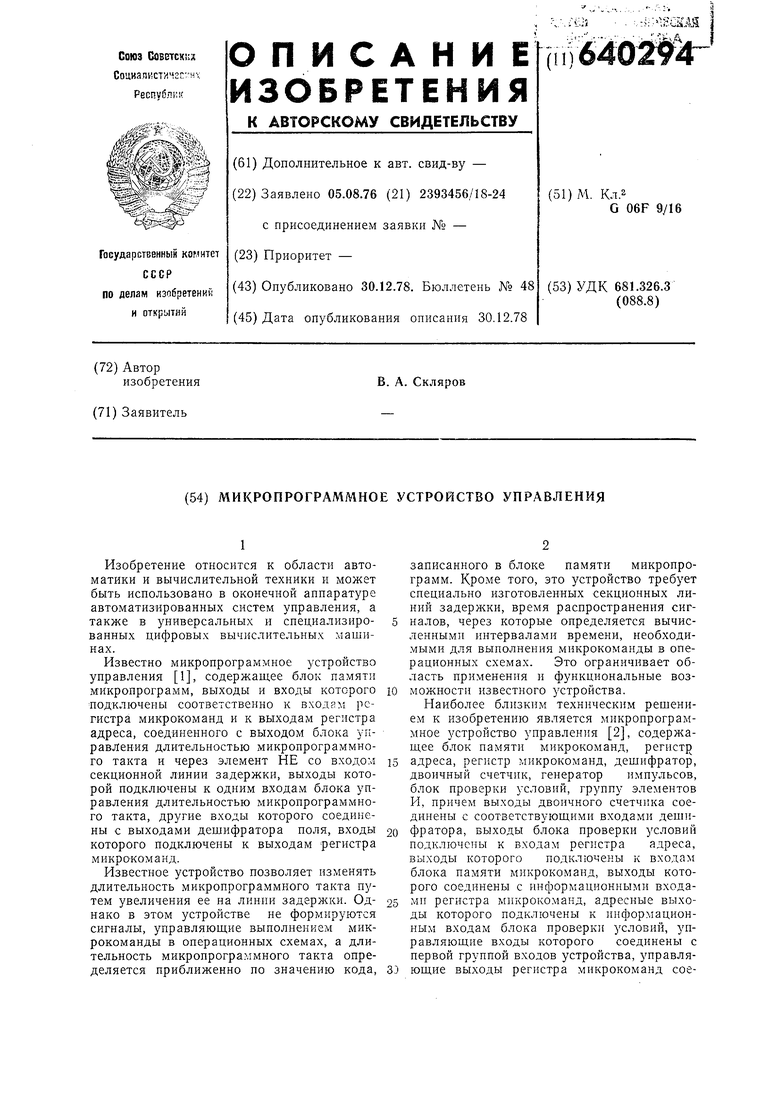

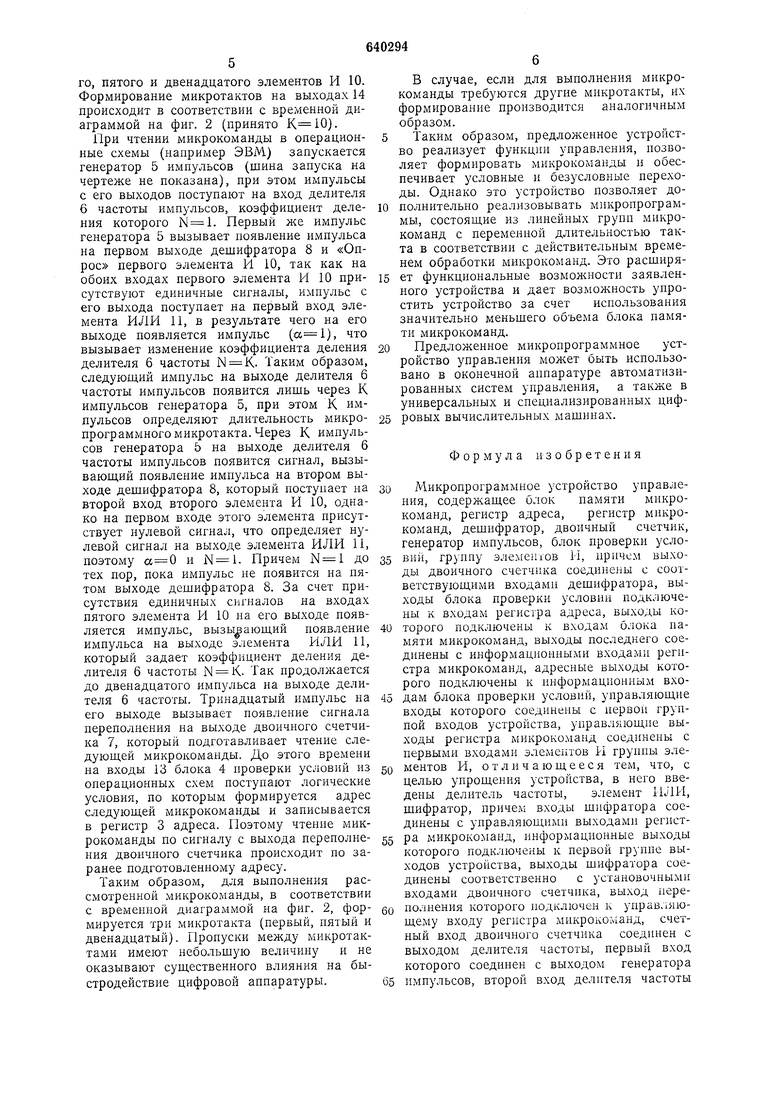

На фиг. 1 изображено нредлагаемое микропрограммное устройство управления; па фиг. 2 - временная диаграмма его работы.

Устройство содержит блок 1 памяти микрокоманд, регистр 2 микрокоманд, регистр 3 адреса, блок 4 нроверки условий, генератор 5 импульсов, делитель 6 частоты, двоичный счетчик 7, дешифратор 8, шифратор 9, элементы И 10, элемент ИЛИ 11, первая группа выходов устройства 12, первая группа 13 входов устройства, вторая группа 14 выходов устройства.

Выходы блока 1 памяти микрокоманд подключены к входам регистра 2 микрокоманд, а входы - к выходам регистра 3 адреса, входы которого соединены с выходами блока 4 проверки условий. Входы блока 4 проверки условий подключены к адресным выходам регистра микрокоманд, на которые подается адресная часть микрокоманды регистра. Управляюидие выходы регистра 2 микрокоманд несут информацию о номерах микрогактов, которые необходимы для обработки микрокоманды в операционных схемах. Эти выходы подключены к первым входам элементов И 10 и ко входам шифратора 9, выходы которого

подключены ко входам двоичного счетчика 7. Выходы разрядов двоичного счетчика 7 подключены ко входам дешифратора 8, выходы которого подключены ко вторым входам элементов И 10. Выходы элементов И 10 подключены ко входам элемента ИЛИ И, выход которого соединен со вторым входом делителя 6 частоты, первый вход которого подключен к выходу генератора 5 импульсов, а выход - к счетному входу двоичного счетчика 7, выход переполнения которого подключен к управляющему входу регистра 2 микрокоманд. Делитель 6 частоты предназначен для

управления подачей тактовых сигналов на вход двоичного счетчика 7. Он имеет два коэффициента деления - N, первый , второй N K (К 10-100). Иричем д, j 1, прн 1 ЛГ, при к 1,

где а - сигнал на выходе элемента ИЛИ 11. Счетчик 7 и дешифратор 8 представляют

собой распределитель импульсов и предназначены для последовательного опроса элементов И 10. Шифратор 9 предназначен для изменения коэффициента пересчета двоичного счетчика 7. Он представляет собой преобразователь номера последнего такта, необходимого для обработки микрокоманды, в двоичный код.

Принцип действия остальных элементов и узлов либо такой же, как и в прототипе,

либо соответствует их функциональному назначению.

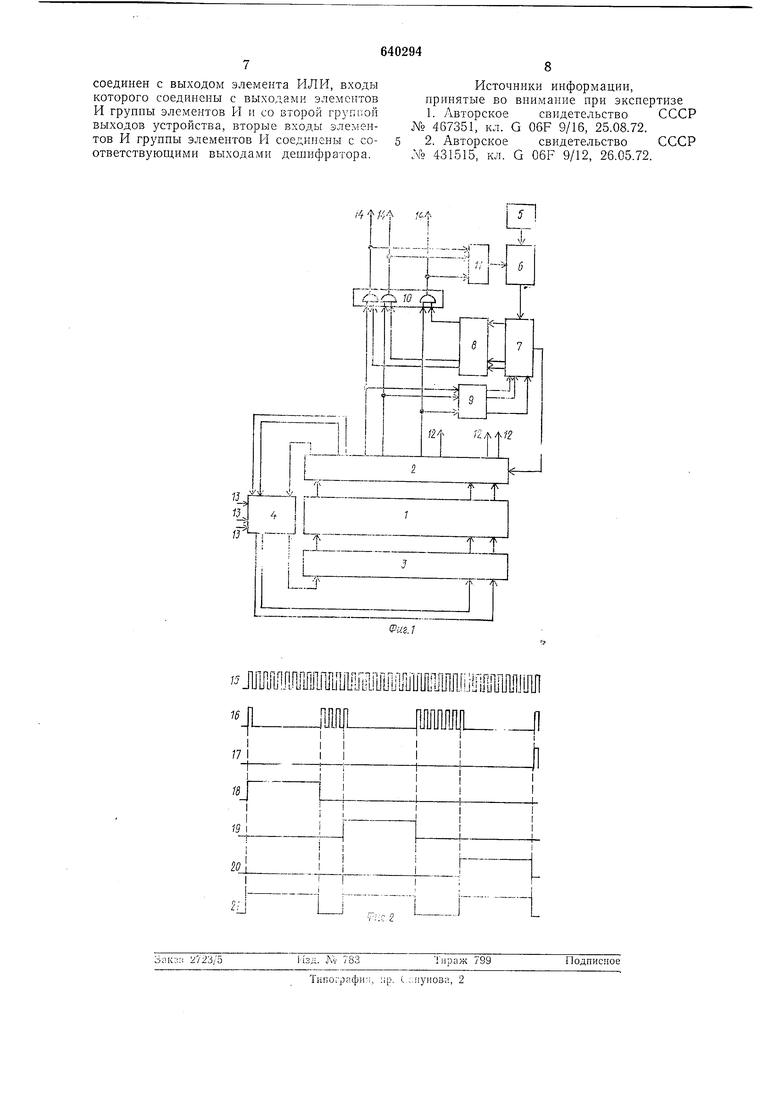

На фиг. 2 цифры обозначают следующие сигналы: 15-импульсы на выходе генератора 5 импульсов, 16 - импульсы на выходе делителя 6 частоты, 17 - импульс на выходе переполнения двоичного счетчика, 18-20 - соответственно имнульсы на выходе первого, пятого и двенадцатого элементов И, 21 - импульсы на выходе элемента ИЛИ 11.

Принцип работы устройства заключается в следующем.

Пусть нз блока 1 памяти микрокоманд читается микрокоманда, для выполнения

которой в операционных схемах необходим первый, пятый и двенадцатый микротакты. При этом с информационных выходов регистра 2 микрокоманд онерационная часть микрокоманды поступает на первую групну выходов устройства, а на выходах унравляющих регистра 2 микрокоманд с порядковыми номерами 1, 5 и 12 будет присутствовать единичный сигнал (на остальных управляющих выходах будет нулевой

сигнал). Единичные сигналы с управляющих выходов поступают на вход щифратора 9, Б результате чего на его выходах формируется код 1100 (число 12 в двоичной системе счисления). Кроме того, эти

сигналы поступают па первые входы нервого, пятого и двенадцатого элементов И 10. Формирование микротактов на выходах 14 происходит в соответствии с временной диаграммой на фиг. 2 (принято ).

При чтении микрокоманды в операционные схемы (например ЭВМ) запускается генератор 5 импульсов (шина запуска на чертеже не показана), при этом импульсы с его выходов поступают на вход делителя 6 частоты импульсов, коэффициент деления которого N 1. Первый же импульс генератора 5 вызывает появление имиульса на первом выходе дешифратора 8 и «Опрос первого элемента П 10, так как на обоих входах первого элемента П 10 присутствуют единичные сигналы, импульс с его выхода поступает на первый вход элемента ИЛИ 11, в результате чего на его выходе появляется импульс (), что вызывает изменение коэффициента деления делителя 6 частоты ,. Таким образом, следуюя1,ий импульс на выходе делителя 6 частоты импульсов появится лишь через К импульсов генератора 5, при этом К импульсов определяют длительность микропрограммного микротакта. Через К импульсов генератора 5 на выходе делителя 6 частоты импульсов появится сигнал, вызывающий появление импульса на втором выходе дешифратора 8, который поступает па второй вход второго элемента И 10, однако на первом входе этого элемента присутствует нулевой сигнал, что определяет нулевой сигнал на выходе элемента ИЛИ 11, поэтому и . Причем до тех пор, пока импульс не появится на пятом выходе дешифратора 8. За счет присутствия единичных сигналов на входах пятого элемента И 10 на его выходе появляется импульс, вызывающий появление импульса на выходе элемента ИЛИ 11, который задает коэффициент деления делителя 6 частоты N К.. Так продолжается до двенадцатого импульса на выходе делителя 6 частоты. Тринадцатый импульс на его выходе вызывает появление сигнала переполнения на выходе двоичного счетчика 7, который подготавливает чтение следующей микрокоманды. До этого времени на входы 13 блока 4 проверки условий из операционных схем поступают логические условия, по которым формируется адрес следующей микрокоманды и записывается в регистр 3 адреса. Поэтому чтение микрокоманды по сигналу с выхода переполнения двоичного счетчика происходит по заранее подготовленному адресу.

Таким образом, для выполнения рассмотренной микрокоманды, в соответствии с временной диагра.ммой на фиг. 2, формируется три микротакта (первый, пятый и двенадцатый). Пропуски между микротактами имеют небольшую величину и не оказывают существенного влияния на быстродействие цифровой аппаратуры.

В случае, если для выполнения микрокоманды требуются другие микротакты, их формирование производится аналогичным образом.

Таким образом, предлол енное устройство реализует функции управления, иозволяет формировать микрокоманды и обеспечивает условные и безусловные переходы. Однако это устройство позволяет дополнительпо реализовывать микропрограммы, состоящие из лииейных групп микрокоманд с переменной длительностью такта в соответствии с действительным временем обработки микрокоманд. Это расширяет функциональные возмон ности заявленного устройства и дает возможность упростить устройство за счет использования значительно меньшего объема блока памяти микрокоманд.

Предложенное микропрограммное устройство управления может быть использовано в оконечной аппаратуре автоматизированных систем управления, а также в универсальных и специализированных цифровых вычислительных машинах.

Формула изобретения

Микропрограммное устройство управления, содержашее блок памяти микрокоманд, регистр адреса, регистр микрокоманд, дешифратор, двоичный счетчик, генератор импульсов, блок проверки услоВИЙ, группу элементов П, причем выходы двоичного счетчика соединены с соответствующими входами дешифратора, выходы блока проверки условии подключены к входам регистра адреса, выходы которого подключены к входам блока памяти микрокоманд, выходы последнего соединены с информационными входами регистра микрокоманд, адресные выходы которого подключены к информационным входам блока проверки условий, управляюшие входы которого соединены с первой группой входов устройства, управляющие выходы регистра микрокоманд соединены с первыми входами элементов И группы элементов И, отличающееся тем, что, с целью упрощения устройства, в него введены делитель частоты, элемент ИЛИ, шифратор, причем входы шифратора соединены с управляющими выходами регистра микрокоманд, информационные выходы которого подключены к первой группе выходов устройства, выходы шифратора соединены соответственно с установочными входами двоичного счетчика, выход переполнения которого подключен к управляюшему входу регистра микрокоманд, счетный вход двоичного счетчика соединен с выходом делителя частоты, первый вход которого соедппен с выходом генератора

импульсов, второй вход делителя частоты

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное управляющее устройство | 1980 |

|

SU949657A1 |

| Микропрограммное управляющее устройство | 1981 |

|

SU970367A1 |

| Микропрограммное устройство управления | 1981 |

|

SU945866A1 |

| Микропрограммное управляющее устройство | 1981 |

|

SU1005051A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1241241A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1111161A1 |

| Микропрограммное управляющее устройство | 1982 |

|

SU1084792A2 |

| Микропрограммное управляющее устройство | 1981 |

|

SU1029178A2 |

| Микропрограммное устройство управления | 1981 |

|

SU1005049A1 |

| Устройство для сопряжения ЭВМ с каналами связи | 1985 |

|

SU1288706A1 |

Авторы

Даты

1978-12-30—Публикация

1976-08-05—Подача