Изобретение относится к аналоговой и аналого-цифровой вычислительной технике и может быть использовано в вычислительных машинах, моделирующих устройствах и других областях измерительной техники. Известно множительно-делительное устройство, содержащее генератор синхроимпульсов, компаратор, элементы И, двухпозиционный ключ, входной вентиль, цифро-аналоговый преобразователь, счетчик, выходной ключ и запоминающее устройство, причем входы реверсивного счетчика подключены через входной вентиль к генератору так товых импульсов, а выход - к первому входу цифро-аналогового преобразователя, выход которого подключен к пер вому входу компаратора, второй вход компаратора соединен с первой входной клеммой устройства, а выход - с управляющим входом входного вентиля, выход генератора синхронизации соеди нен с управляющими входами двухпозиционного я выходного ключей и элемента И, второй вход цифро-аналогово го преобразователя подключен через двухпозиционный ключ к второй и третьей входным клег/1мам устройства, а выход - через входной ключ к запоМйнающему блоку, выход которого соединен с выходной клеммой устройства, выход генератора тактовых импуль сов соединен через элемент И с входным вентилем Г1. Недостатком данного множительноделительного устройства является Ограниченный династический диапазон входных сигналов, так как исходя из принципа работы аналого-цифрового преобразователя.-отношение числителя к знаменателю должно быть всегда меньше 1.. Наиболее близким к предлагаемому по технической сущности является r« oжитeльнo-делительное устройство, содержащее генератор синхроимпульсов, первый блок управления, первый вход которого подключен к выходу генератора синхроимпульсов, последовательно соединенные счетчик, цифро-аналоговый преобразователь и первый компаратор, второй вход которого является первым входом устройства, а выход подключен к второму входу первого блока управления, вход счетчика подключен к первому выходу первого блока управления, последовательно соединенные цифроуправляемый резистор, двухпозиционный переключатель,

первый усилитель с управляемым коэффициентом усиления и второй компаратор, выход которого подключен к третьему входу первого блока управления, информационный вход цифроуправляемого резистору является вторым входом устройства, последовательно соединенные генератор тактовых импульсов и первый сдвиговый регистр вход синхронизации которого подключе к выходу генератора синхроимпульсов, а выход подключен к первому управляющему входу первого усилителя с управляемым коэффициентом усиления, выход генератора тактовых импульсов подключен к четвертому входу первого блока управления, второй информационный вход двухпозиционного переключателя является третьим входом устройства, информационный выход первого усилителя с управляемым коэффициентом усиления подключен к информационному входу цифро-аналогового преобразователя, а группа выходов первого усилителя с управляемым коэффициентом усиления подключена к группе управляющих входов цифроуправляемого резистора 2.

Недостатком известного устройства является невысокая точность вычисления частного при увеличении значения знаменателя. Как известно, точность преобразования аналого-цифрового преобразователя зависит от разрядности выходного кода и величины опорного напряжения. В данном устройстве при постоянной разрядности точность вычисления частного ухудшается при увеличении знаменателя (опорного напряжения). Это ухудшение можно допустить до определенной, наперед заданной величины, что соответствует максимальному значению знаменател при определенной разр5удности.

Цель изобретения - повышение точности путем ограничения максимальной величины кванта преобразования.

Поставленная цель достигается тем, что в множительн о-делительное устройство, содержащее генератор синхроимпульсов, первый блок управления, первый вход которого подключе к выходу генератора синхроимпульсов, последовательно соединенные счетчик, цифро-аналоговый преобразователь и первый компаратор, второй вход которого является первым входом устройства, а выход подключен к второму входу первого блока управления, вход счетчика подключен к первому выходу первого блока управления, последовательно соединенные цифроуправляемый резистор, двухпозиционный переключатель, первый усилитель с управляемым коэффициентом усиления и второй компаратор, выход которого подключен к третьему входу первого блока управления , информационный вход цифроуправляемого резистора является вторым входом устройства, последовательно соединенные генератор тактовых импульсов и первый сдвиговый регистр, вход синхронизации которого подключен к выходу генератора синхроимпульсов, а выход подключен к первому управляющему входу первого усилителя с управляемым коэффициентом усиления, выход генератора тактовых импульсов подключен к четвертому входу первого блока управления, второй информационный вход двухпозиционного переключателя является третьим входом устройства, информационный выход первого усилителя с управляемым коэффициентом усиления подключен к информационному входу цифро-аналогового преобразователя, а группа выходов первого усилителя с управляемым коэффициентом усиления подключена к группе управляющих входов цифроуправляемого резистора, введены третий компаратор, триггер переключения режимов, второй блок управления, второй усилитель с управляемым коэффициентом усиления и второй сдвиговый регистр, информационный вход второго усилителя с управляемым коэффициентом усиления подключен к второму входу первого компаратора, выход подключен к второму входу второго компаратора, а управляющий вход подключен к первому выходу второго сдвигового регистра, второй выход которого подключен к второму управляющему входу первого усилителя с управляемым коэффициентом усиления, третий выход второго сдвигового регистра подключен к первому входу второго блока управления, первый и второй выходы которого подключены к информационным входам соответственно первого и второго сдвиговых регистров, а третий выход подключен к управляющему входу двухпозиционного переключателя, второй вход второго блока управления подключен к выходу цифро-аналогового преобразователя и является выходом устройства, трети вход подключен к выходу генератора тактовых импульсов, а четвертый и пятый входы подключены соответственно к выходам второго и третьего компараторов, выход генератора синхроимпульсов подключен к входу синхронизации второго Сдвигового регистра, первый вход третьего компаратора является четвертым входом устройства, второй ВХОД третьего компаратора подключен к информационному выходу первого усилителя с управляемым коэффициентом усиления, а выход подключен к третьему управляющему входу первого усилителя с управляемым коэффициентом усиления и к пятому входу первого блока управления, шестой вход которого подклк1чен к четвертому управлягащег у входу усилителя с управляемым коэффициентом усиления, выход генератора синхроимпульсов подключен к счетному входу триггера переключения режимов, информационные входы которого объединены и подключены к выходу второго компаратора, первый выход триггера переключения режимов подключен к четвертому управляк1цему входу первого усилителя с управляемым коэффициентом усиления и к шестому входу первого блока управления, второй выход триггера переключения режимов подключен к пятому управляющему входу первого усилителя с управляемым коэффициентом усиления и к шестому входу второго блока управления, седьмой вход которого подключен к второму выходу первого блока управления.

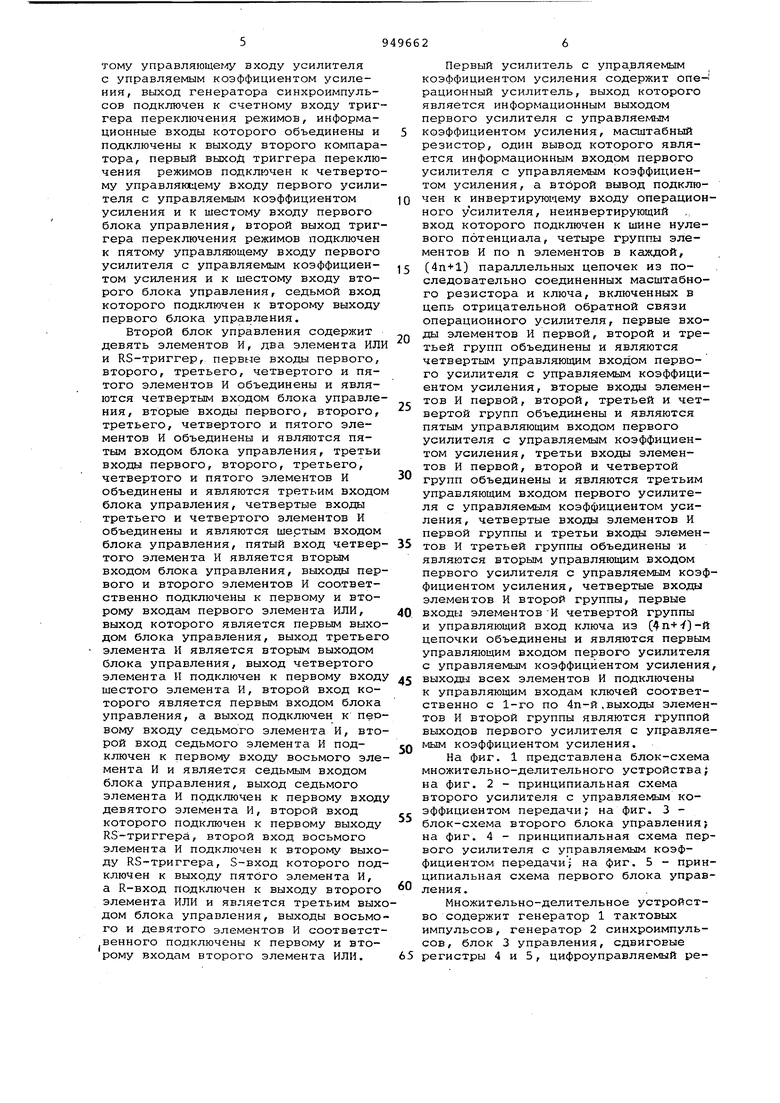

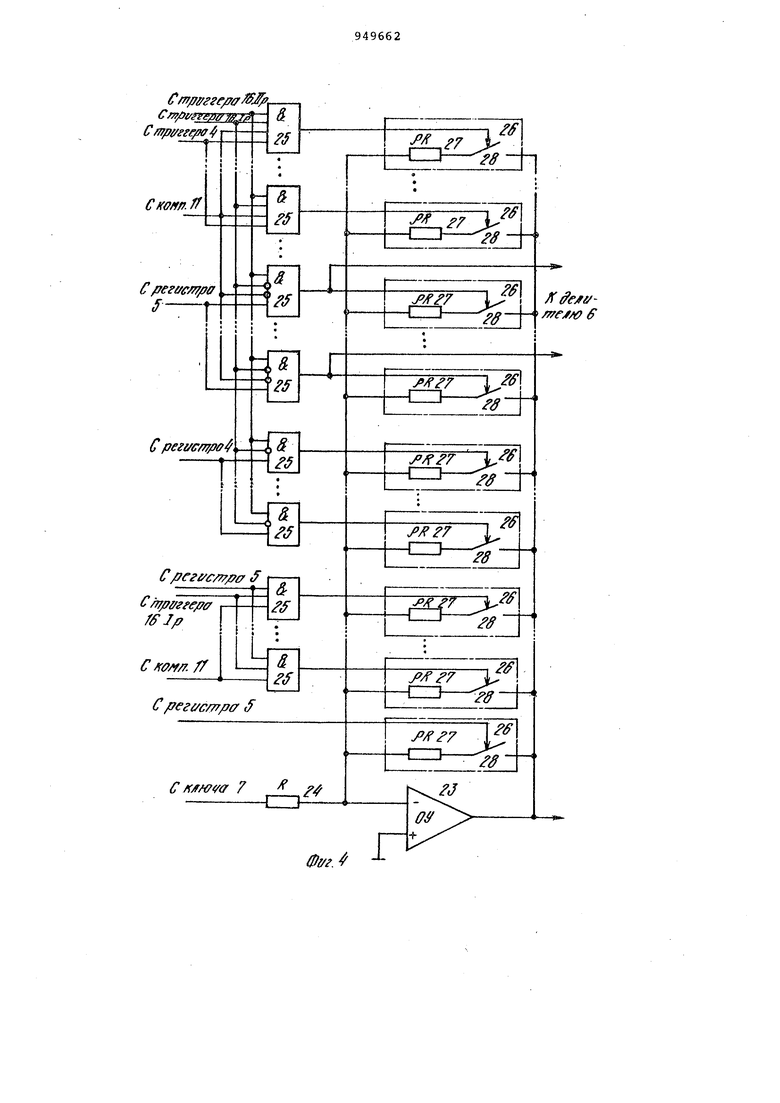

Второй блок управления содержит девять элементов И, два элемента ИЛИ и RS-триггер, первые входы первого, второго, третьего, четвертого и пятого элементов И объединены и являются четвертым входом блока управления, вторые входы первого, второго, третьего, четвертого и пятого элементов И объединены и являются пятым входом блока управления, третьи входы первого, второго, третьего, четвертого и пятого элементов И объединены и являются третьим входом блока управления, четвертые входы третьего и четвертого элементов И объединены и являются шестым входом блока управления, пятый вход четвертого элемента И является вторым входом блока управления, выходы первого и второго элементов И соответственно подключены к первому и второму входам первого элемента ИЛИ, выход которого является первым выходом блока управления, выход третьего элемента И является вторым выходом блока управления, выход четвертого элемента И подключен к первому входу шестого элемента И, второй вход которого является первым входом блока управления, а выход подключен к первому входу седьмого элемента И, второй вход седьмого элемента И подключен к первому входу восьмого элемента И и является седьмым входом блока управления, выход седьмого элемента И подключен к первому входу девятого элемента И, второй вход которого подключен к первому выходу RS-триггера, второй вход восьмого элемента И подключен к второму выходу RS-триггера, S-вход которого подключен к выходу пятого элемента И, а R-вход подключен к выходу второго элемента ИЛИ и является третьим выходом блока управления, выходы восьмого и девятого элементов И соответст|Венного подключены к первому и второму входам второго элемента ИЛИ,

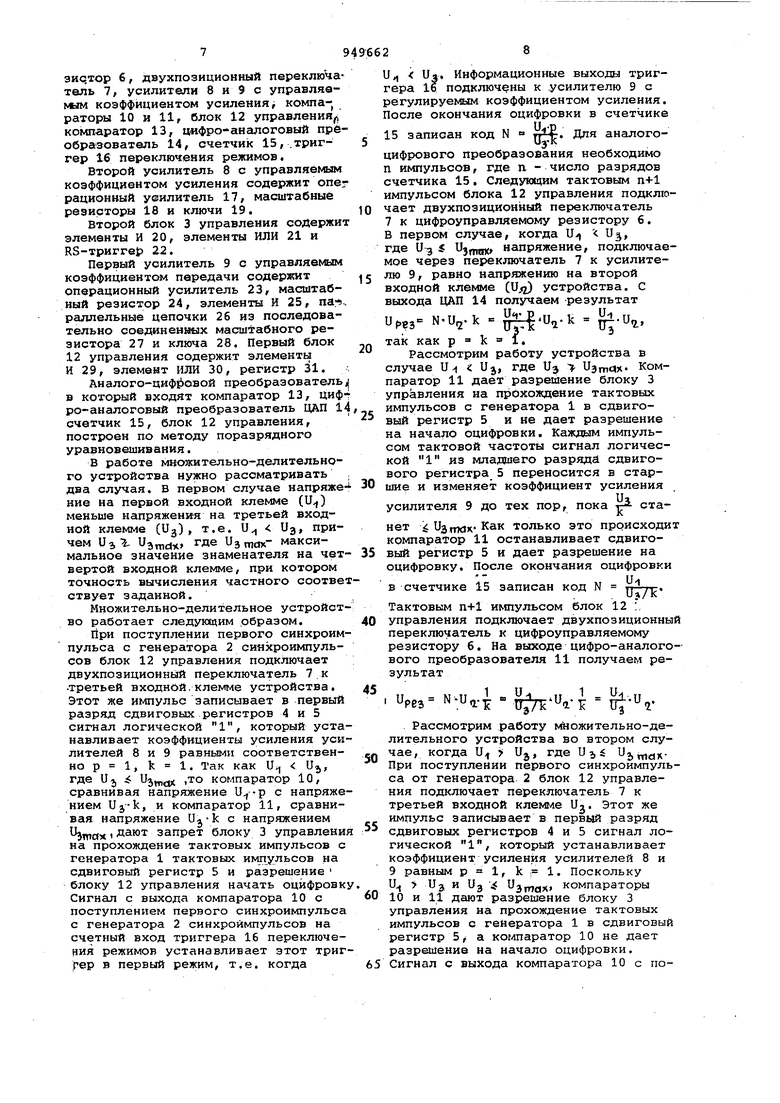

Первый усилитель с управляемым коэффициентом усиления содержит one-i рационный усилитель, выход которого является информационным выходом первого усилителя с управляемым коэффициентом усиления, масштабный резистор, один вывод которого является информационным входом первого усилителя с управляемым коэффициентом усиления, а второй вывод подключен к инвертирую1дему входу операцион0ного усилителя, неинвертирующий вход которого подключен к шине нулевого потенциала, четыре группы элементов И по п элементов в каждой, (4п+1) параллельных цепочек из по5следовательно соединенных масштабного резистора и ключа, включенных в цепь отрицательной обратной связи операционного усилителя, первые входы элементов И первой, второй и тре0тьей групп объединены и являются четвертым управляющим вхоДом первого усилителя с управляемым коэффициентом усиления, вторые входы элементов И первой, второй, третьей и чет5вертой групп объединены и являются пятым управляющим входом первого усилителя с управляемым коэффициентом усиления, третьи входы элементов И первой, второй и четвертой

0 групп объединены и являются третьим управляющим входом первого усилителя с управляемым коэффициентом усиления , четвертые входы элементов И первой группы и третьи входы элемен5тов И третьей группы объединены и являются вторым управляющим входом первого усилителя с управляемым коэффициентом усиления, четвертые входы элементов И второй группы, первые

0 входы элементов И четвертой группы и управляющий вход ключа из ()-й цепочки объединены и являются первым управляющим входом первого усилителя с управляемым коэффициентом усиления, выходы всех элементов И подключены

5 к управляющим входам ключей соответственно с 1-го по 4п-й,выходы элементов И второй группы являются группой выходов первого усилителя с управляемым коэффициентом усиления.

0

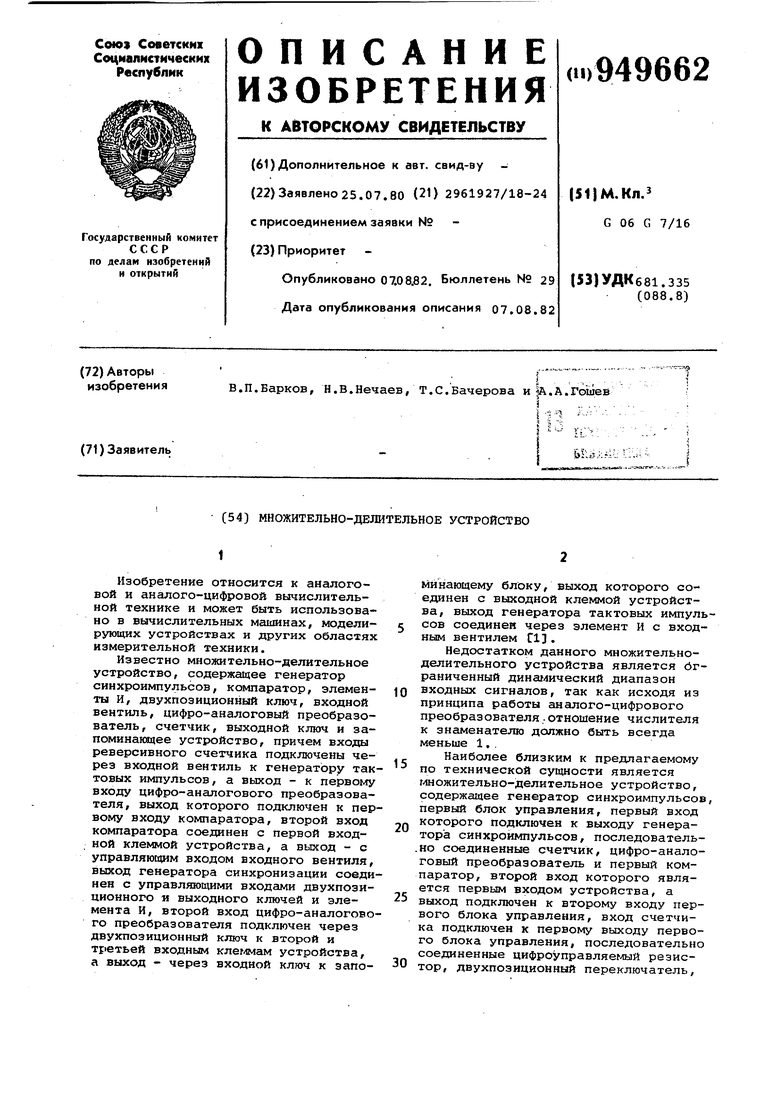

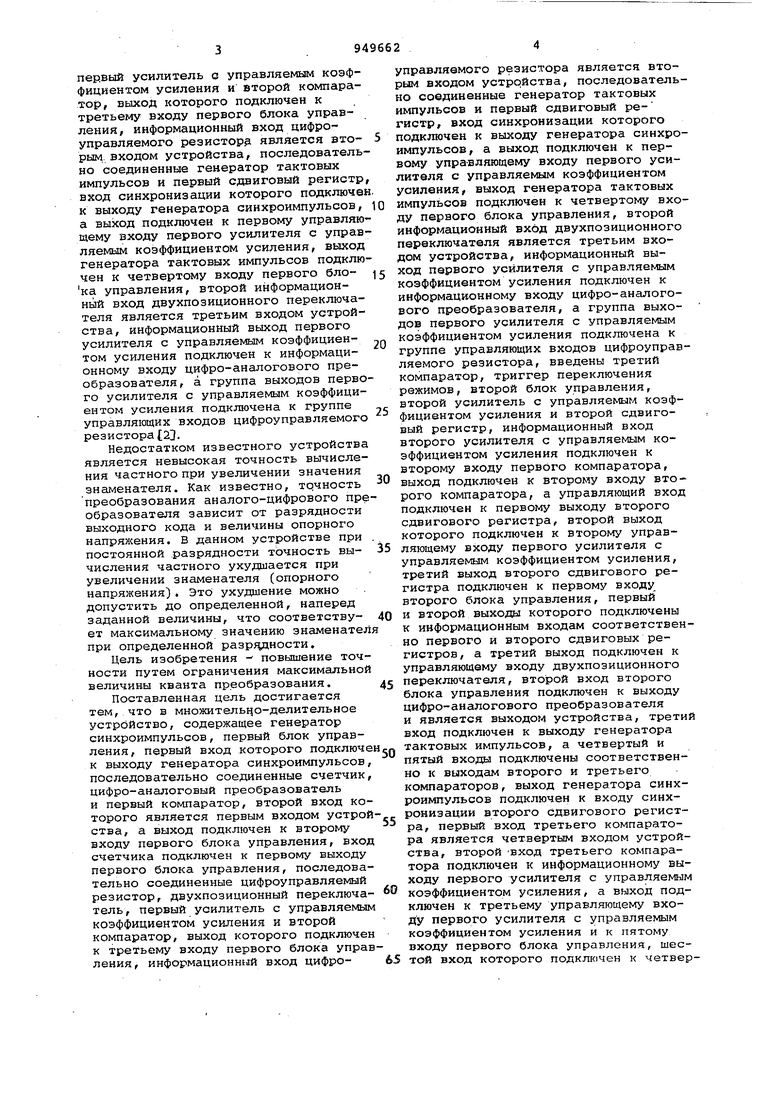

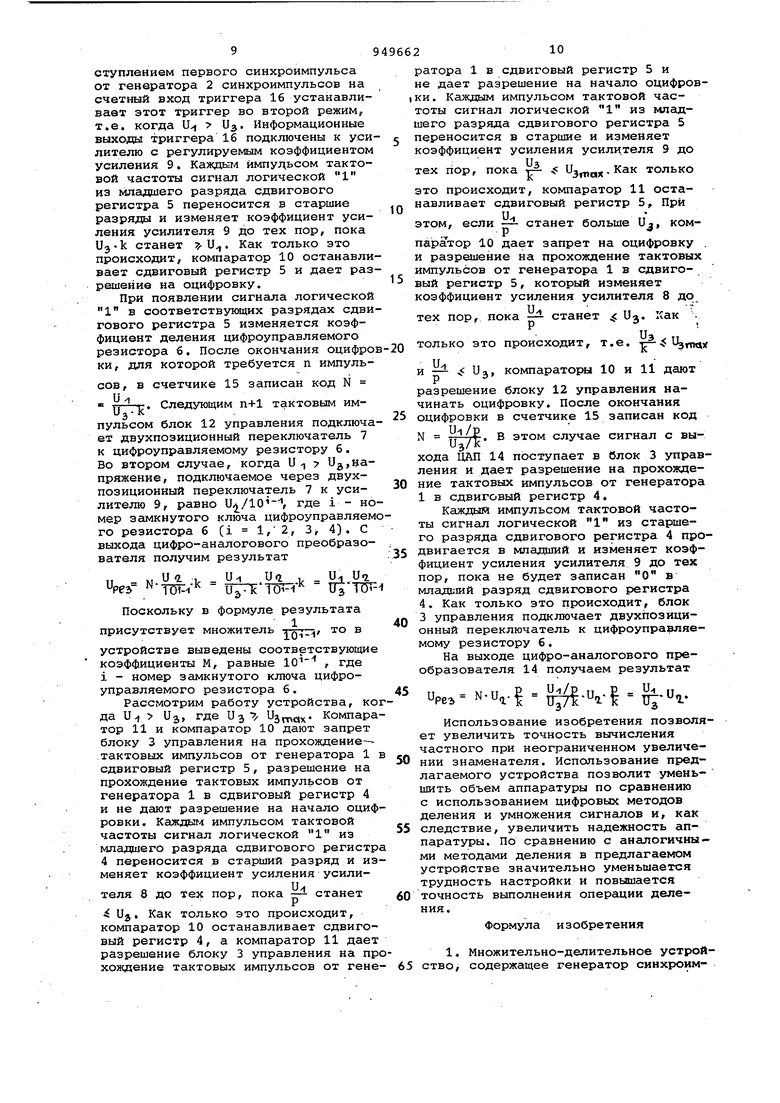

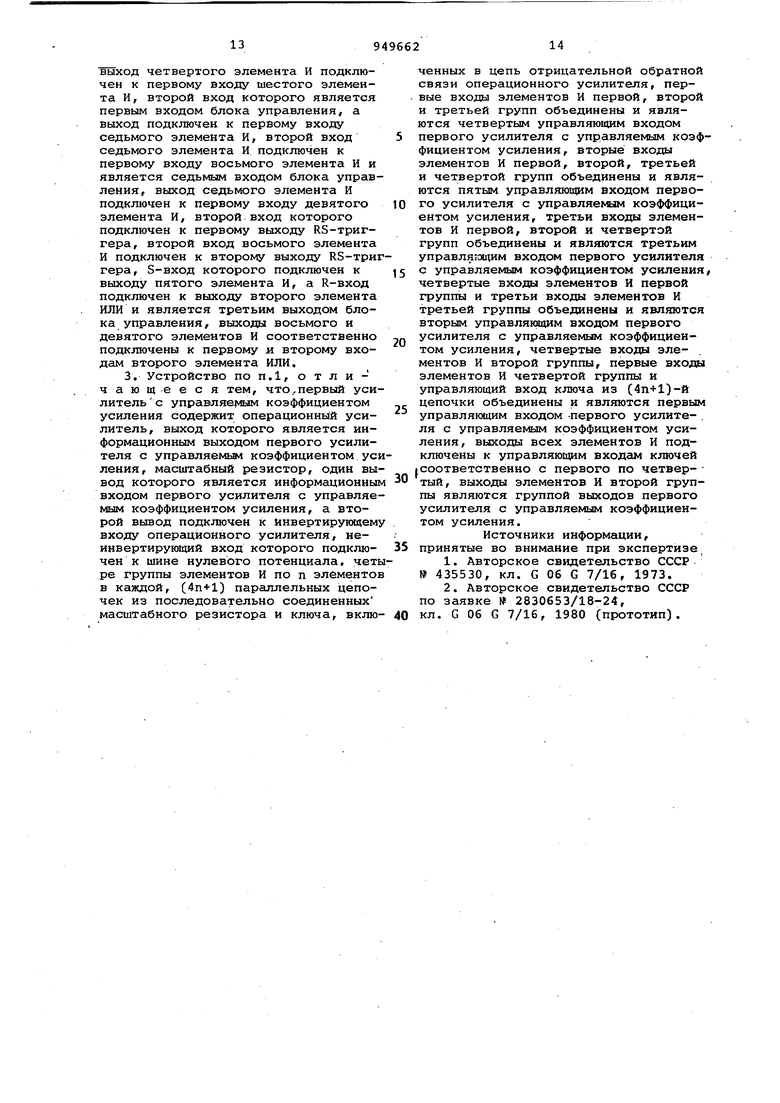

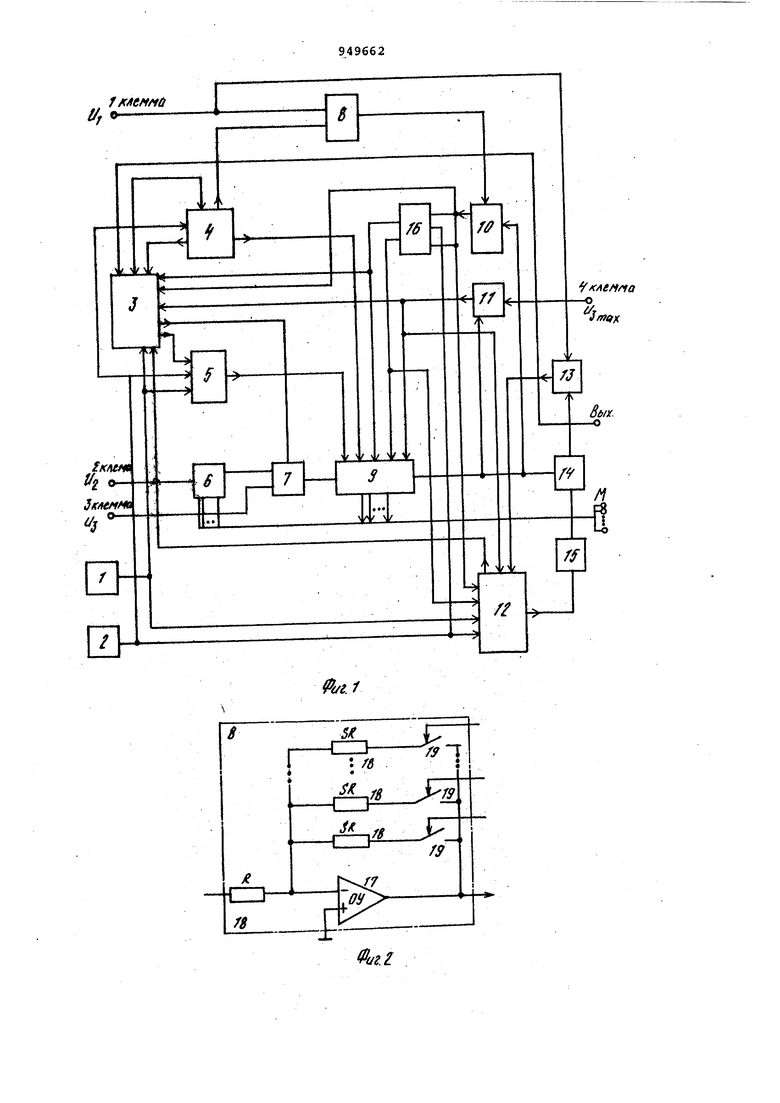

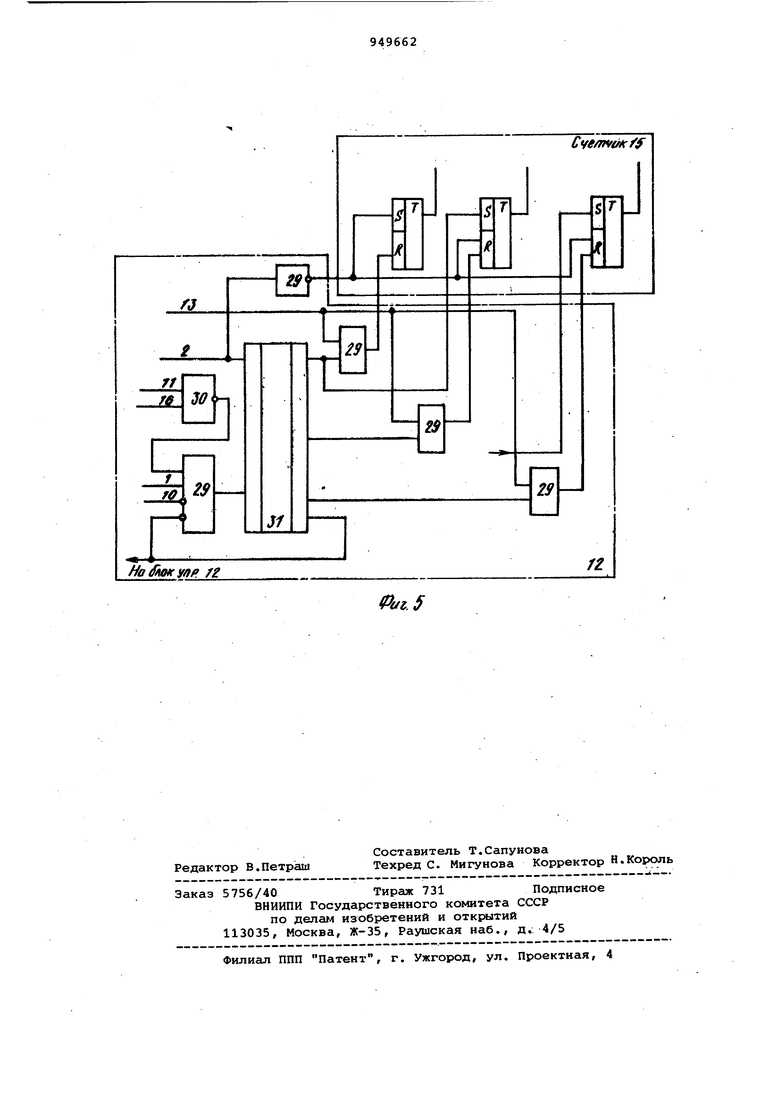

На фиг. 1 представлена блок-схема множительно-делительного устройства; на фиг. 2 - принципиальная схема второго усилителя с управляемым коэффициентом передачи; на фиг. 3 5блок-схема второго блока управления; на фиг. 4 - принципиальная схема первого усилителя с управляемым коэффициентом передачиj на фиг. 5 - принципиальная схема первого блока управ0ления.

Множительно-делительное устройство содержит генератор 1 тактовых импульсов, генератор 2 синхроимпульсов , блок 3 управления, сдвиговые

5 регистры 4 и 5, цифроуправляемый резис.тор б, двухпозиционный переключатель 7, усилители 8 и 9 с управляемым коэффициентом усиления компараторы 10 и 11, блок 12 управления компаратор 13, цифро-аналоговый преобразователь 14, счетчик 15,.триггер 16 переключения режимов. Второй усилитель 8 с управляемым коэффициентом усиления содержит oner рационный уеилитель 17, масяитабные резисторы 18 и ключи 19. Второй блок 3 управления содержит элементы И 20, элементы ИЛИ 21 и КЗ-триггер 22. Первый усилитель 9 с управляемым коэффициентом передачи содержит операционный усилитель 23, масштабный резистор 24, элементы И 25, па:. раллельные цепочки 26 из последовательно соединенных масштабного резистора 27 и ключа 28. Первый блок 12 управления содержит элементы И 29, элемент ИЛИ 30, регистр 31. Аналого-циф| овой преобразователь в который входят компаратор 13, Цифг ро-аналоговый преобразователь ЦАП .4 счетчик 15, блок 12 управления, построен по методу поразрядного уравновешивания. В работе множительно-делительного устройства нужно рассматривать два случая. В первом случае напряжевне на первой входной клемме (U) меньше напряжения на третьей входной клемме (Ug) т.е. U УЗ, причем U nicl4 Ujmcix- максимальное значение знаменателя на четвертой входной клемме, при котором точность вычисления частного соответ ствует заданной. Множительно-делительное устройство работает следующим образом. При поступлении первого синхроимпульса с генератора 2 сияхроимпульсов блок 12 управления подключает двухпозиционный переключатель 7.к третьей ВХОДНОЙ,клемме устройства. Этот же импульс записывает в первый разряд сдвиговых регистров 4 и 5 сигнал логической 1, который устанавливает коэффициенты усиления усилителей 8 и 9 равными соответственно р 1, k 1. Так как U, Uj, где Uj ;f (X компаратор 10, сравнивая напряжение с напряжением Uj-k, и компаратор 11, сравнивая напряжение Ujk с напряжением %waxIДэют запрет блоку 3 управления на прохождение тактовых импульсов с генератора 1 тактовых импульсов на сдвиговый регистр 5 и разрешение блоку 12 управления начать оцифровку Сигнал с выхода компаратора 10 с поступлением первого синхроимпульса с генератора 2 синхроимпульсов на счетный вход триггера 16 переключения режимов устанавливает этот триг гер в первый режим, т.е. когда и,, Ua. Информационные выходы триггера 16 подключены к усилителю 9 с регулируемым коэффициентом усиления. После окончания оцифровки в счетчике 15 записан код N аналогоцифрового преобразования необходимо п импульсов, где п - число разрядов счетчика 15. Следующим тактовым п+1 импульсом блока 12 управления подключает двухпозиционный переключатель 7к цифроуправляемому резистору 6. 8первом случае, когда U U, где Ug Зглох напряжение, подключаемое через переключатель 7 к усилителю 9, равно напряжению на второй входной клемме СУд) устройства. С выхода ЦАП 14 получаем результат так как р k 1. Рассмотрим работу устройства в случае U « Uj, где Uj Компаратор 11 дает разрешение блоку 3 управления на прохождение тактовых импульсов с генератора 1 в сдвиговый регистр 5 и не дает разрешение на начало оцифровки. Каждым импульсом тактовой частоты сигнал логической 1 из младшего разряда сдвигового регистра 5 переносится в старшие и изменяет коэффициент усиления Ui усилителя 9 до тех пор, пока станет изшйк- Как только это происходит компаратор 11 останавливает сдвиговый регистр 5 и дает разрешение на оцифровку. После окончания оцифровки в счетчике 15 записан код N Н,. . Тактовым п+1 и myльcoм блок 12 :. управления подключает двухпозиционный переключатель к цифроуправляемому резистору 6. На выходе цифро-аналогового преобразователя 11 получаем результат um N-Ua-i-n VT Vi D Ur Рассмотрим работу 1 ожительно-делительного устройства во втором случае, когда и Uj, где Uj ътаиПри поступлении первого синхроимпульса от генератора 2 блок 12 управления подключает переключатель 7 к третьей входной клемгле и, . Этот же импульс записывает в первый разряд сдвиговых регистров 4 и 5 сигнал логической 1, который устанавливает коэффициент усиления усилителей 8 и 9равным р 1, k 1. Поскольку и из и Uj ;# Ujp,, компараторы 10и 11 дают разрешение блоку 3 управления на прохождение тактовых импульсов с генератора 1 в сдвиговый регистр 5 а компаратор 10 не дает разрешение на начало оцифровки. Сигнал с выхода компаратора 10 с поотуплением первого синхроимпульса от генератора 2 синхроимпульсов на счетный вход триггера 16 устанавливает этот триггер во второй режим, т.е. когда U, U. Информационные выходы триггера 16 подключены к уси лителю с регулируемым коэффициентом усиления 9. Каждыгл ймпудьсом тактовой частоты сигнал логической 1 из младшего разряда сдвигового регистра 5 переносится в старшие разряды и изменяет коэффициент усиления усилителя 9 до тех пор, пока Uj-k станет U. Как только это происходит, компаратор 10 останавли вает сдвиговый регистр 5 и дает раз решение на оцифровку. При появлении сигнала логической 1 в соответствующих разрядах сдви гового регистра 5 изменяется коэффициент деления цифроуправляемого резистора 6. После окончания оцифро I, для которой требуется п импульки, сов, в счетчике 15 записан код N ufn Следующим п+1 тактовым импульсом блок 12 управления подключа ет двухпозиционный переключатель 7 к цифроуправляемому резистору 6. Во втором случае, когда U U,напряжение, подключаемое через двухпозиционный переключатель 7 к усилителю 9, равно , где i - но мер замкнутого ключа цифроуправляем го резистора 6 Ci lf2, 3, 4). С выхода цифро-аналогового преобразователя получим результат lLi.M -xiJz.,, ui b-Hi yi Г - urrifTarr - тпТОГн Поскольку в формуле результата присутствует множитель -д-.., то в устройстве выведены соответствующие коэффициенты М, равные , где i - номер замкнутого ключа цифро управляемого резистора 6. Ра;ссмотрим работу устройства, ко да U-) Uj,, где Uj . Компара тор 11 и компаратор 10 дают запрет блоку 3 управления на прохождениетактовых импульсов от генератора 1 сдвиговый регистр 5, разрешение на прохождение тактовых импульсов от генератора 1 в сдвиговый регистр 4 и не дают разрешение на начало оциф ровки. Каждыг- импульсом тактовой частоты сигнал логической 1 из младшего разряда сдвигового регистр 4 переносится в старший разряд и из меняет коэффициент усиления усилителя 8 до Тех пор, пока - станет Uj, Как только это происходит, компаратор 10 останавливает сдвиговый регистр 4, а компаратор 11 дает разрешение блоку 3 управления на пр хождение тактовых импульсов от гене- 65 ратора 1 в сдвиговый регистр 5 и не дает разрешение на начало оцифровКи. Каждым импульсом тактовой частоты сигнал логической 1 из младшего разряда сдвигового регистра 5 переносится в старшие и изменяет коэффициент усиления усили.теля 9 до тех пор, пока 4- .Как только это происходит, компаратор 11 останавливает сдвиговый регистр 5, При этом, если - станет больше Uj, компара/гор 10 дает запрет на оцифровку . и разрешение на прохождение тактовых импульсов от генератора 1 в сдвиговый регистр 5, который изменяет коэффициент усиления усилителя 8 до Uxt т, тех пор, пока - станет 4 Ug. только это происходит, т.е. и - Uj, компаратор 10 и 11 дают разрешение блоку 12 управления начинать оцифровку. После окончания оцифровки в счетчике 15 записан код N трт. В этом случае сигнал с выхода ЦАП 14 поступает в блок 3 управления и дает разрешение на прохождение тактовых импульсов от генератора 1 в сдвиговый регистр 4. Каждый импульсом тактовой частоты сигнал логической 1 из старшего разряда сдвигового регистра 4 продвигается в младший и изменяет коэффициент усиления усилителя 9 до тех пор, пока не будет записан О в младьшй разряд сдвигового регистра 4. Как только это происходит, блок 3 управления подключает двухпозиционный переключатель к цифроуправляемому резистору 6. На выходе цифро-аналогового преобразователя 14 получаем результат Pe. N-U,.i Si.U,.| .U. Ti -%|-ui Использование изобретения позволяет увеличить точность вычисления частного при неограниченном увеличении знаменателя. Использование предлагаемого устройства позволит уменьшить объем аппаратуры по сравнению с использованием цифровых методов деления и умножения сигналов и, как следствие, увеличить надежность аппаратуры. По сравнению с аналогичными методами деления в предлагаемом устройстве значительно уменьшается трудность настройки и повышается точность выполнения операции деления. Формула изобретения 1. Множительно-делительное устройство, содержащее генератор синхроимпульсов, первый блок управления, первый вход которого подключен к выходу генератора синхроимпульсов, последовательно соединенные счетчик, цифро-аналоговый преобразователь и первый компаратор, второй вход которого является первым входом устройства, а выход подключен к второму входу первого блока управления, вход счетчика подключен к первому выходу первого блока управления, последовательно соединенные цифроуправляемый резистор, двухпозиционныйпереключатель, первый усилитель с управляемым коэффициентом усиления и второй компаратор, выход которого подключен к третьему входу первого блока управления, информационный вход цифроуправляемого резистора является вторым входом устройства, последовательно соединенные генератор тактовых импульсов и первый сдвиговый регистр, вход синхронизации которого подключен к выходу генератора синхро импульсов, а выход подключен к первому управляющего входу первого усилителя с управляемым коэффициентом усиления, выход генератора тактовых импульсов подключен к четвертому входу первого блока управления, второй информационный вход двухпозиционного переключателя является третьим входом устройства, информационный выход первого усилителя с управляемым коэффициентом усиления подключен к информационному входу цифро-аналогового преобразователя, а группа выходов первого усилителя с управляемым коэффициентом усиления подключена к группе управляющих входов цифроуправляемрго резистора, отличающееся тем, что, с целью повышения точности, в него введены третий компаратор, триггер переключения режимов, второй блок управления, второй усилитель с управляемым коэффициентом усиления и второй сдвиговый регистр, информационный вход второго усилителя с управляемым коэффициентом усиления подключен к второму входу первого компаратора, выход подключен к второму входу второго компаратора, а управляющий вход подключен к первому выходу второго сдвигового регистра, второй выход которого подключен к второму управляющему входу первого усилителя с управляемым коэффициентом усиления, третий выход второго сдвигового регистра подключен к первому входу второго блока управления, первый и второй выходы которого подключены к информационным входам соответственно первого и второго сдвиговых регистров, а третий выход подключен к управляющему входу двухпозиционного переключателя, второй вход второго блока управления подключен к выходу цифро-аналогового преобразователя .и является выходом устройства, третий вход подключен к выходу генератора тактовых импульсов, а четвертый и пятый входы под--ключены соответственно к выходам второго и третьего компараторов, выход генератора синхроимпульсов подключен к входу синхронизации второго сдвигового регистра, первый

вход третьего компаратора является четвертым входом устройства, второй вход третьего компаратора подключен к информационному выходу первого усилителя с управляемым коэффициентом усиления, а выход подключен к третьему управляющему входу первого усилителя с управляемым коэффициентом усиления и к пятому входу первого . блока управления, шестой вход которого подключен к четвертому управляющему входу усилителя с управляемым коэффициентом усиления, выход генератора синхроимпульсов подключен к счетному входу триггера переключения режимов, информационные входы

которого объединены и подключены к

выходу второго компаратора, первый выход триггера переключения режимов подключен к четвертому управляющему входу первого усилителя с управляемым коэффициентом усиления и к шестому входу первого блока управления, второй выход триггера переключения режимов подключен к пятому управляющему входу первого усилителя с управляемым коэффициентом усиления и

к шестому входу второго блока управления, седьмой вход которого подключен к второму выходу первого блока управления.

0 2. Устройство по п.1, отличающееся тем, что второй блок управления содержит девять элементов И, два элемента ИЛИ и RS-триггер, первые входы первого, второго, трё5 тьего, четвертого и пятого элементов И объединены и являются четвертым входом блока управления, вторые входы первого, второго, третьего, четвертого и пятого элементов И объединены и являются пятым входом блока управления, третьи входы первого, второго. Третьего, четвертого и пятого элементов И объединены и являются третьим входом блока управления, четвертые входы третьего и четвертого элементов И объединены и

являются шестым входом блока управления, пятый вход четвертого элемента И является вторым входом блока управления, выходы первого и второго

0 элементов И соответственно подключены к первому и второму входам первого элемента ИЛИ, выход которого является первым выходом блока управления, выход третьего элемента И является

5 вторым выходом блока управления. выход четвертого элемента И подключен к первому входу шестого элемента И, второй вход которого является первым входом блока управления, а выход подключен к первому входу седьмого элемента И, второй вход седьмого элемента И подключен к первому входу восьмого элемента И и является седьмым входом блока управления, выход седьмого элемента И подключен к первому входу девятого элемента И, второй вход которого подключен к первому вьлходу RS-триггера, второй вход восьмого элемента И подключен к второму выходу RS-три гера , S-вход которого подключен к выходу пятого элемента И, а R-вход подключен к выходу второго элемента ИЛИ и является третьим выходом блока управления, выходы восьмого и девятого элементов И соответственно подключены к первому и второму входам второго элемента ИЛИ. 3. Устройство по п,1, отличающ-ееся тем, что, первый уси лительс управляемым коэффициентом усиления содержит операционный усилитель, выход которого является информационнЕзЕМ выходом первого усилителя с управляемым коэффициентом.ус ления, масштабный резистор, один вы вод которого является информационны входом первого усилителя с управляе мым коэффициентом усиления, а второй вывод подключен к Инвертирующем входу операционного усилителя, неинвертирующий вход которого подключен к шине нулевого потенциала, чет ре группы элементов И по п элементо в каждой, (4п+1) параллельных цепочек из последовательно соединенных масштабного резистора и ключа, вклю ченных в цепь отрицательной обратной связи операционного усилителя, первые входы элементов И первой, второй и третьей групп объединены и являются четвертым управляющим входом первого усилителя с управляемым коэффициентом усиления, вторые входы элементов И первой, второй, третьей и четвертой групп объединены и являются пятым управляющим входом первого усилителя с управляемым коэффициентом усиления, третьи входы элементов И первой, второй и четвертой групп объединены и являются третьим управля сядим входом первого усилителя с управляемым коэффициентом усиления/ четвертые входы элементов И первой группы и третьи входы элементов И третьей группы объединены и являются вторым управляющим входом первого усилителя с управляемым коэффициентом усиления, четвертые входаз элементов И второй группы, первые входы элементов И четвертой группы и управляющий вход ключа из ()-й цепочки объединены и являются первым управляющим входом -первого усилите- . ля с управляемым коэффициентом усиления, выходы всех элементов И подключены к управляющим входам ключей соответственно с первого по четвер- тый, выходы элементов И второй группы являются группой выходов первого усилителя с управляемым коэффициентом усиления. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 435530, кл. G Об G 7/16, 1973. 2.Авторское свидетельство СССР по заявке 2830653/18-24, кл. G 06 G 7/16, 1980 (прототип). I AtMflfl fffACfifia о

Cveai i ff

If

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительно-делительное устройство | 1979 |

|

SU840942A1 |

| Множительно-делительное устройство | 1981 |

|

SU993278A2 |

| Детектор @ -зубца электрокардиосигнала | 1984 |

|

SU1260004A1 |

| Многофункциональный тригонометрический преобразователь | 1979 |

|

SU987633A1 |

| СЕЙСМИЧЕСКОЕ УСТРОЙСТВО ОБНАРУЖЕНИЯ ДВИЖУЩИХСЯ ОБЪЕКТОВ | 2006 |

|

RU2306611C1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА ТЕЛЕГРАФНЫХ РАДИОСИГНАЛОВ | 1990 |

|

RU2009615C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ РАДИОТЕЛЕМЕТРИЧЕСКИХ СИГНАЛОВ | 1994 |

|

RU2126139C1 |

| Логарифмический аналого-цифровой преобразователь | 1982 |

|

SU1042036A1 |

| Информационное устройство | 1987 |

|

SU1564066A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОРРЕЛЯЦИОННОЙ ФУНКЦИИ | 1992 |

|

RU2037198C1 |

/J

Ш

f

/J

HofwKygp, fZ

29

n

Авторы

Даты

1982-08-07—Публикация

1980-07-25—Подача