Изобретение относится к специализированным средствам вычислительной техники и предназначено для нахождения оценок корреляционной функции случайных процессов, например, в корреляционно-экстремальных системах навигации или системах оценки параметров сигнала в случае некогерентной их обработки.

Известно устройство для определения корреляционной функции (авт.св. N 1501086, кл. G 06 F 15/336), содержащее усилители, коммутатор, аналого-цифровой преобразователь, цифроаналоговый преобразователь, сумматор, регистр, блок памяти и блок управления.

Недостатком прототипа являются ограниченные функциональные возможности за счет невозможности определения максимума корреляционной функции.

Цель изобретения расширение функциональных возможностей за счет определения максимального значения корреляционной функции при некогерентной обработке.

Устройство для определения корреляционной функции содержит управляемый усилитель, усилитель, коммутатор, аналого-цифровой преобразователь, цифроаналоговый преобразователь, сумматор, регистр, блок памяти, блок управления, причем информационный вход управляемого усилителя и вход усилителя являются соответственно первым и вторым информационными входами устройства, выходы управляемого усилителя и усилителя соединены соответственно с первым и вторым информационными входами коммутатора, выход и управляющий вход которого соединены соответственно с информационным входом аналого-цифрового преобразователя и первым выходом блока управления, второй, четвертый и шестой выходы блока управления соединены соответственно с тактовым входом аналого-цифрового преобразователя, тактовым входом цифроаналогового преобразователя и входом сброса регистра, выход аналого-цифрового преобразователя соединен с информационным входом цифроаналогового преобразователя и первым информационным входом сумматора, выход цифроаналогового преобразователя соединен с входом задания коэффициента усиления управляемого усилителя, выход регистра соединен с вторым информационным входом сумматора, выход сумматора соединен с информационным входом блока памяти, вход запуска аналого-цифрового преобразователя соединен с вторым выходом блока управления, пятый, седьмой, восьмой и девятый выходы блока управления соединены соответственно со стробирующим входом регистра, входами чтения, записи и выбора микросхемы блока памяти, выход блока памяти соединен с информационным входом регистра, десятый выход блока управления соединен с адресным входом блока памяти.

Дополнительно по сравнению с прототипом в устройство введены буферный регистр, блок решения системы управления, кольцевой регистр сдвига, операционный блок, два элемента задержки, регистр сдвига, счетчик-делитель и элемент И, причем выход блока памяти подключен к информационному входу кольцевого регистра сдвига, выходы кольцевого регистра сдвига подключены к информационным входам блока решения системы уравнений и являются первыми выходами устройства, выходы блока решения системы уравнений подключены к информационным входам регистра сдвига, выходы которого подключены к информационным входам операционного блока, первый и второй выходы операционного блока являются соответственно вторым и третьим выходами устройства, третий выход операционного блока подключен к первому входу элемента И и является выходом строба устройства, выход элемента И соединен с синхровходом операционного блока и входом управления регистра сдвига, десятые выходы блока управления подключены к информационным входам буферного регистра, одиннадцатый выход блока управления подключен к управляющим входам буферного регистра и кольцевого регистра сдвига и к входу счетчика-делителя, выход буферного регистра является четвертым выходом устройства, выход счетчика-делителя подключен к второму входу элемента И и через первый элемент задержки подключен к синхровходу блока решения системы уравнений и входу второго элемента задержки, выход второго элемента задержки соединен с входом разрешения записи регистра сдвига, выход переполнения кольцевого регистра сдвига подключен к тактовому входу блока решения системы уравнений, что блок управления содержит генератор тактовых импульсов, генератор одиночного импульса, десять элементов И, три элемента ИЛИ, четыре триггера, три счетчика, два элемента НЕ и элемент ИЛИ-НЕ, причем выход генератора тактовых импульсов соединен с тактовым входом первого триггера, первыми входами первого и второго элементов И и является восьмым выходом блока, прямой выход первого триггера соединен с вторым входом первого элемента И, третий вход которого соединен с информационным входом первого триггера, первым входом третьего элемента И и инверсным выходом второго триггера, прямой выход которого соединен со вторым входом второго элемента И, первым входом четвертого элемента И и является седьмым выходом блока.

Выход первого элемента И соединен с первым входом первого элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом второго элемента И и счетным входом первого счетчика, первый разрядный выход которого соединен с первыми входами элемента ИЛИ-НЕ и пятого и шестого элементов И, второй разрядный выход первого счетчика соединен с вторыми входами элемента ИЛИ-НЕ и шестого элемента И и с первыми входами второго элемента ИЛИ и седьмого элемента И, второй вход второго элемента ИЛИ соединен с третьими входами шестого элемента И и элемента ИЛИ-НЕ и третьим разрядным выходом первого счетчика, четвертый разрядный выход которого соединен с вторыми входами пятого и седьмого элементов И, тактовым входом третьего триггера, первым входом восьмого элемента И и четвертым входом элемента ИЛИ-НЕ, выход которого является вторым выходом блока, выход пятого элемента И соединен с вторыми входами третьего и четвертого элементов И, выходы которых являются соответственно девятым и четвертым выходами блока, инверсный выход седьмого элемента И соединен с входом установки в "1" второго триггера, тактовый вход которого соединен с выходом переполнения второго счетчика и счетным входом третьего счетчика, выход генератора одиночного импульса соединен с входами установки в "0" первого, второго и четвертого триггеров, входом установки в "1" третьего триггера и через первый элемент НЕ с входами установки в "0" первого, второго и третьего счетчиков, выход второго элемента ИЛИ соединен с первым входом третьего элемента ИЛИ и является третьим выходом блока, выход третьего элемента ИЛИ и шестого элемента И являются соответственно пятым и первым выходами блока.

Информационные входы второго, третьего и четвертого триггеров соединены с шиной нулевого потенциала, инверсный выход третьего триггера соединен с вторым входом восьмого элемента И, выход которого соединен с первым входом девятого элемента И и счетным входом второго счетчика, выход которого является шестым выходом блока, первый разрядный выход третьего счетчика соединен через второй элемент НЕ с входом установки в "1" четвертого триггера, выход которого является десятым выходом блока, разрядные выходы группы третьего счетчика соединены с соответствующими входами десятого элемента И, выход которого соединен с вторым входом девятого элемента И, выход девятого элемента И является одиннадцатым выходом блока, выход переполнения третьего счетчика соединен с тактовым входом четвертого триггера. Кроме того операционный блок содержит шесть сумматоров, четыре умножителя, делитель, два компаратора, два элемента ИЛИ, элемент И-НЕ, четыре элемента задержки, причем первый информационный вход блока соединен с первыми входами первого и второго сумматоров, второй информационный вход блока соединен с первым входом третьего сумматора и входом первого умножителя, третий информационный вход блока соединен с вторыми входами первого и второго сумматоров, выход первого сумматора соединен с первым входом делителя и первым входом второго умножителя, выход второго сумматора соединен с вторым входом третьего сумматора и первым входом четвертого сумматора, выход первого умножителя соединен с вторым входом четвертого сумматора, выход третьего сумматора соединен с вторым входом делителя и первым входом третьего умножителя, выходы делителя соединены с информационными входами первого и второго компараторов, первыми и вторыми входами четвертого умножителя, вторыми входами второго умножителя и являются первыми информационными выходами блока, выход четвертого умножителя соединен с вторым входом третьего умножителя, выход третьего умножителя соединен с первым входом пятого сумматора, выход второго умножителя соединен с вторым входом пятого сумматора, выход пятого сумматора соединен с первым входом шестого сумматора, выход четвертого сумматора соединен с вторым входом шестого сумматора являются вторыми информационными входами блока, первый и второй выходы первого компаратора соединены с первым и вторым входами первого элемента ИЛИ, первый и второй выходы второго компаратора соединены с первым и вторым входами второго элемента ИЛИ, выход первого элемента ИЛИ соединен с первым входом элемента И-НЕ, выход второго элемента ИЛИ соединен со вторым входом элемента И-НЕ, выход элемента И-НЕ является выходом строба блока, синхровход блока соеди- нен с входом первого элемента задержки и с синхровходами первого и второго сумматоров, выход первого элемента задержки соединен с синхровходами первого, второго и четвертого умножителей, третьего сумматора и входом второго элемента задержки, выход второго элемента задержки соединен с синхровходами делителя, третьего умножителя, четвертого сумматора и входом третьего элемента задержки, выход третьего элемента задержки соединен с синхровходом пятого сумматора и входом четвертого элемента задержки, выход четвертого элемента задержки соединен с синхровходами первого и второго компаратора и шестого сумматора.

На фиг. 1 изображена структурная схема устройства; на фиг. 2 структурная схема блока управления; на фиг. 3 структурная схема операционного блока; на фиг. 4 и 5 примеры реализации компараторов.

На фиг. 1 приняты обозначения: управляемый усилитель 1, усилитель 2, коммутатор 3, аналого-цифровой преобразователь (АЦП) 4, цифроаналоговый преобразователь (ЦАП) 5, сумматор 6, регистр 7, блок памяти 8, блок 9 управления, входы 10,11, буферный регистр 12, кольцевой регистр сдвига 13, блок 14 решения системы управления (авт.св. N 1462353, кл. G 06 F 15/324; авт.св. N 1644160, кл. G 06 F 15/347, 15/324; авт.св. N 1509932, кл. G 06 F 15/347); регистр сдвига 15, операционный блок 16, счетчик-делитель 17, элементы задержки 18, 19, элемент И 20, выход абсциссы 21, выход ординаты 22, информационные выходы 23, 24, выход строба 25.

На фиг. 2 приняты обозначения: генератор тактовых импульсов 26, триггер 27, элементы И 28, 29, элемент ИЛИ 30, элементы И 31-34, элемент ИЛИ 35, элемент И 36, элемент ИЛИ 37, генератор одиночного импульса 38, триггер 39, счетчик 40, элемент ИЛИ-НЕ 41, элемент НЕ 42, триггер 43, элемент И 44, счетчики 45, 46, элемент И 47, элемент НЕ 48, элемент И 49, триггер 50, выходы блока 51-61.

На фиг. 3 приняты обозначения: синхровход блока 62, информационные входы блока 63, 64, 65, элемент задержки 66, сумматоры 67, 68, умножитель 69-71, элемент задержки 72, сумматор 73, умножитель 74, сумматор 75, элемент задержки 76, делитель 77, сумматор 78, элемент задержки 79, сумматор 80, вход начальной установки 81, компаратор 82, вход начальной установки 83, компаратор 84, элемент ИЛИ 85, 86, элемент И-НЕ 87, первый информационный выход блока 88, выход строба 89, второй информационный вход блока 90.

Для осуществления предлагаемого изобретения на фиг. 1 информационный вход 10 управляемого усилителя 1 и вход 11 усилителя 2 являются соответственно первым и вторым информационными входами устройства, выходы усилителя 2 и управляемого усилителя 1 соединены с первым и вторым входами соответственно коммутатора 3, выход коммутатора 3 соединен с входом аналого-цифрового преобразователя 4, выход аналого-цифрового преобразователя 4 соединен с входом цифроаналогового преобразователя 5 и первым входом сумматора 6, выход цифроаналогового преобразователя 5 соединен с управляющим входом управляемого усилителя 1, выход регистра 7 соединен с вторым входом сумматора 6, выход которого соединен с входом блока памяти 6, первый выход блока управления 9 является управляющим входом коммутатора 3, второй и третий выходы блока управления 9 соединены соответственно с входом пуска и информационным входом аналого-цифрового преобразователя 4, четвертый, пятый, шестой, седьмой, восьмой и девятый выходы блока управления 9 соединены соответственно с тактовым входом цифроаналогового преобразователя 5, со стробирующим входом регистра 7, с входом сброса регистра 7, с входами чтения, записи и выбора микросхемы блока памяти 8, выход блока памяти 8 подключен к информационному входу кольцевого регистра сдвига 13 и входу регистра 7, выходы кольцевого регистра сдвига 13 подключены к информационным входам блока решения системы уравнений 14 и являются выходами 22 устройства, выходы блока решения системы уравнений 14 подключены к информационным входам регистра сдвига 15, выходы регистра сдвига 15 подключены к информационным входам операционного блока 16, первый и второй выходы операционного блока 16 являются соответственно выходами 23 и 24 устройства, третий выход операционного блока 16 подключен к первому входу элемента И 20 и является выходом строба 25 устройства, выход элемента И 20 соединен с синхровходом операционного блока 16 и входом управления регистра сдвига 15, десятые выходы блока управления 9 подключены к информационным входам буферного регистра 12 и адресному входу блока памяти 8, одиннадцатый выход блока управления 9 подключен к управляющим входам буферного регистра 12 и кольцевого регистра сдвига 13 и к входу счетчика-делителя 17, выходы буферного регистра 12 являются выходом 21 устройства, выход счетчика-делителя 17 подключен к второму входу элемента И 20, и через элемент задержки 18 подключен к синхровходу блока решения системы уравнений 14 и входу элемента задержки 19, выходы элемента задержки 19 соединены с входом разрешения записи регистра сдвига 15, выход переполнения кольцевого регистра сдвига 13 соединен с тактовым входом блока решения системы уравнений 14.

На фиг. 2 выход генератора тактовых импульсов 26 блока управления 9 соединен с тактовым входом триггера 27, первыми входами элементов И 28 и 29 и являются выходом блока 51, прямой выход триггера 27 соединен с вторым входом элемента И 28, третий вход которого соединен с информационным входом триггера 27, первым входом элемента И 32 и инверсным выходом триггера 39, прямой выход которого соединен с вторыми входами элементов И 29 и 33 и является выходом блока 56, выход элемента И 28 соединен с вторым входом элемента ИЛИ 30, первый вход и выходы которого соединены соответственно с выходом элемента И 29 и счетным входом счетчика 40, первый разрядный выход которого соединен с первым входом элемента ИЛИ-НЕ 41, первым входом элемента И 36, первым входом элемента И 31, второй разрядный выход счетчика 40 соединен с вторыми входами элемента ИЛИ-НЕ 41 и элемента И 36, с первыми входами элемента ИЛИ 35 и элемента И 34, второй вход элемента ИЛИ 35 соединен с третьим входом элемента И 36 и третьим разрядным выходом счетчика 40 и третьим входом элемента ИЛИ-НЕ 41, четвертый разрядный выход счетчика 40 соединен с четвертым входом элемента ИЛИ-НЕ 41, с тактовым входом триггера 43, первым входом элемента И 44 и вторыми входами элементов И 31 и 34, выход элемента ИЛИ-НЕ 41 является выходом блока 58, выход элемента И 31 соединен с вторыми входами элементов И 32 и 33, выход элемента И 32 является выходом блока 52, выход элемента И 33 соединен с первым входом элемента ИЛИ 37 и является выходом блока 53, выход элемента ИЛИ 35 соединен с вторым входом элемента ИЛИ 37 и является выходом блока 54. Выход элемента ИЛИ 37 является выходом блока 55, выход элемента И 36 является выходом блока 57, инверсный выход элемента И 34 соединен с входом установки в "1" триггера 39, выход генератора одиночного импульса 38 подключен к входам установки в "0" триггера 27, 39 и 50, к входу установки в "1" триггера 43 и через элемент НЕ 42 к входу установки в "0" счетчиков 40, 45 и 46, инверсный выход триггера 43 соединен с вторым входом элемента И 44, выход элемента И 44 соединен с первым входом элемента И 49 и счетным входом счетчика 45, информационные входы триггеров 39, 43 и 50 соединены с шиной нулевого потенциала, выходы счетчика 45 являются выходами блока 60, выход переполнения счетчика 45 соединен с счетным входом счетчика 46 и тактовым входом триггера 39, выход переполнения счетчика 46 соединен с тактовым входом триггера 50, прямой выход которого является выходом блока 60, первый разрядный выход счетчика 46 через элемент НЕ 48 соединен с входом установки в "1" триггера 50, разрядные выходы группы счетчика 46 соединены с соответствующими входами элемента И 47, выход элемента И 47 соединен с вторым входом элемента И 49, выход элемента И 49 соединен с выходом блока 61.

На фиг. 3 первый информационный вход 63 операционного блока 16 соединен с первыми входами сумматоров 67 и 68, второй информационный вход 64 блока 16 соединен с первым входом сумматора 73 и входом умножителя 71, третий информационный вход 65 блока 16 соединен с вторыми входами сумматоров 67 и 68, выход сумматора 67 соединен с первым входом делителя 77 и первым входом умножителя 70, выход сумматора 68 соединен с вторым входом сумматора 73 и первым входом сумматора 75, выход умножителя 71 соединен с вторым входом сумматора 75, выход сумматора 73 соединен с вторым входом делителя 77 и первым входом умножителя 74, выходы делителя 77 соединены с входами компараторов 82 и 84, первыми и вторыми входами умножителя 69, вторыми входами умножителя 70 и являются информационными выходами блока 88, выход умножителя 69 соединен с вторым входом умножителя 74, выход умножителя 74 соединен с первым входом сумматора 78, выход умножителя 70 соединен с вторым входом сумматора 78, выход сумматора 78 соединен с первым входом сумматора 80, выход сумматора 75 соединен с вторым входом сумматора 80, выходы сумматора 80 являются информационными выходами блока 90, выходы компаратора 82 соединены с первым и вторым входами элемента ИЛИ 85, выходы компаратора 84 соединены с первым и вторым входами элемента ИЛИ 86, выход элемента ИЛИ 85 соединен с первым входом элемента И-НЕ 87, выход элемента ИЛИ 86 соединен с вторым входом элемента И-НЕ 87, выход элемента И-НЕ 87 является выходом строба 89 блока, синхровход 72 блока соединен с входом элемента задержки 66 и с синхровходами сумматоров 67 и 68, выход элемента задержки 66 соединен с синхровходами умножителей 69, 70 и 71, с синхровходом сумматора 73 и входом элемента задержки 72, выход элемента задержки 72 соединен с синхровходами делителя 77, умножителя 74, сумматора 75 и входом элемента задержки 76, выход элемента задержки 76 соединен с синхровходами сумматора 78 и входом элемента задержки 79, выход которого соединен с синхровходами компараторов 82 и 84 и сумматора 80.

Устройство работает следующим образом.

На первый 10 и второй 11 входы коррелятора поступают сигналы соответственно х(t) и y(t). В начале цикла определения корреляционной функции коммутатор 3 подключает усилитель 2 на вход АЦП 4, число М разрядов которого зависит от требований точности измерения. Рассмотрим случай с использованием восьмиразрядного АЦП с поразрядным преобразованием. При появлении сигнала "Пуск АЦП" на выходе 2 блока управления 9 АЦП 4 за 8 тактов по импульсам с выхода 3 блока управления 9 выполняет операции преобразования сигнала y(t) в цифровую форму. Этот код с выхода АЦП 4 поступает на информационный вход ЦАП 5 и по сигналу "Строб ЦАП" на выходе 4 блока управления 9 заносится в ЦАП 5. После преобразования усилитель 1 управляет напряжением с выхода ЦАП 5, пропорциональным сигналу усилителя 2, задержанным на время Δ τ задаваемое блоком управления 9, по импульсу с выхода 2 блока управления 9 коммутатор 3 подключает управляемый усилитель 1 к входу АЦП 4. После переключения коммутатора 3 по импульсу с выхода 1 блока 9 сигнал с выхода усилителя 1 первого процесса х(t), пропорциональный произведению х(t1) ˙y(t1 + Δ τ ), поступает на вход АЦП 4 и после преобразования в цифровую форму поступает на вход сумматора 6. Поскольку на инверсный управляющий вход регистра 7 с выхода 6 блока 9 поступает сигнал низкого уровня "Сброс регистра", то на вход сумматора 6 поступает нулевой код, и код на выходе сумматора 6 равен коду АЦП 4. Наличие сигналов разрешения записи "Запись" и "Выбор микросхемы" соответственно на выходах 8 и 9 блока управления 9 обеспечивает запись этого кода в ячейку блока памяти 8 по адресу, установленному на выходе 10 блока управления 9. Этот же код с выхода 10 блока управления 9 поступает в буферный регистр 12, после чего значение адреса на выходе 10 блока 9 увеличивается на единицу.

АЦП 4 осуществляет следующий цикл преобразования и в следующую ячейку блока памяти 8 записывается код, пропорциональный величине х(t2) y(t2 + Δ τ ), т.е. вторая точка корреляционной функции. Преобразование повторяется, но при этом по сигналам разрешения считывания на выходах 7 и 9 блока управления 9 код, хранящийся в ячейке памяти блока 8, по текущему адресу поступает на входы регистра 7 и кольцевого регистра сдвига 13. Код записывается в регистр 7 по сигналу "Строб регистра" на выходе 5 блока управления 9, далее он поступает на вход сумматора 6, и в каждую ячейку записывается сумма текущего значения и значения на текущем цикле измерения i-й точки корреляционной функции.

Таким образом, происходит накапливание К значений ординат корреляционной функции с целью получения усредненного значения в соответствии с формулой

Rxy(Δτ)

x(ti)y(ti+Δτ)

x(ti)y(ti+Δτ)

Для ввода значений точек корреляционной функции и кода адреса на последнем цикле измерения смена адреса сопровождается сигналом на одиннадцатом выходе 11 блока управления 9.

По сигналу с выхода 11 блока управления 9 производится запись кода адреса с выхода 10 блока управления 9 в первые ячейки буферного регистра 12, а в кольцевой регистр сдвига 13 запись значения корреляционной функции с выхода блока 8. Буферный регистр 12 и кольцевой регистр сдвига 13 имеет N-ячеек для записи всех значений корреляционной функции. Сигнал с выхода 11 блока управления 9 задерживается в элементах задержки 17 и 18 на время, необходимое для вычисления всех значений корреляционной функции R(Δti), i  . По окончании записи всех N значений корреляционной функции в кольцевой регистр сдвига 13 на выходе переполнения этого регистра появляется единичный сигнал, который поступает на тактовый вход блока решения системы уравнений 14.

. По окончании записи всех N значений корреляционной функции в кольцевой регистр сдвига 13 на выходе переполнения этого регистра появляется единичный сигнал, который поступает на тактовый вход блока решения системы уравнений 14.

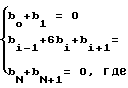

После задержки в элементах задержки 17 и 18 сигнал поступает на синхровход блока решения системы уравнений 14. По этому сигналу блок 14 производит взятие обратной матрицы В-1, т.е. решает систему уравнений (сплайн-аппроксимация отсчетов корреляционной функции Rxy с помощью параболических нормализованных В-сплайнов) 8

8 (

( i

i  по значениям элементов входной корреляционной матрицы R

по значениям элементов входной корреляционной матрицы R  R(

R( )

) . Эти коэффициенты bi с выхода блока 14 поступают в регистр сдвига 15 по приходу на него сигнала разрешения записи с элемента задержки 19, в котором задерживается сигнал на время, необходимое для вычисления коэффициентом bi. По этому импульсу с выхода 11 блока управления 9 последовательно первые три значения коэффициентов bi-1, bi, bi+1 поступают в операционный блок 16, который реализует следующее математическое выражение

. Эти коэффициенты bi с выхода блока 14 поступают в регистр сдвига 15 по приходу на него сигнала разрешения записи с элемента задержки 19, в котором задерживается сигнал на время, необходимое для вычисления коэффициентом bi. По этому импульсу с выхода 11 блока управления 9 последовательно первые три значения коэффициентов bi-1, bi, bi+1 поступают в операционный блок 16, который реализует следующее математическое выражение

bi+

bi+  +

+

+ (1) и повторяет условие:

+ (1) и повторяет условие:

ti≅ τi≅ ti+1 ⇒ ih ≅ τi≅ (i+1)h ⇒ 0 ≅  i ≅ 1 (2) где

i ≅ 1 (2) где

τi= ti+

Если не выполняется условие (2), то на выходе строба блока 16 присутствует единичный сигнал. В момент выполнения условия (2) операционный блок 16 вычисляет максимальное значение корреляционной функции (1).

Если не выполняется условие (2), то на выходе строба блока 16 присутствует единичный сигнал. В момент выполнения условия (2) операционный блок 16 вычисляет максимальное значение корреляционной функции (1).

Значения корреляционной функции Rmax поступают на информационный выход 23 устройства, а также формируется стробирующий сигнал на выходе строба 25 устройства. В случае выполнения условия (2). На выходе 24 устройства формируется сигнал τo в соответствии с выражением τo=  i, соответствующий временному сдвигу внутри шага дискретности h относительно отсчета корреляционной функции в момент времени ti h˙i, что характеризует величину

i, соответствующий временному сдвигу внутри шага дискретности h относительно отсчета корреляционной функции в момент времени ti h˙i, что характеризует величину

Rmax R(ti + τo h).

Сигнал строба (низкий уровень) поступает на элемент И 20, который закрывается и сигнал на тактовые входы блоков 15 и 16 не поступает.

На этом работа устройства заканчивается.

Блок 9 управления (фиг. 2) работает следующим образом. Генератор 26 единичного импульса устанавливает в нулевое состояние первый 40, второй 45 и третий 46 счетчики и D-триггеры 27, 39 и 50. Третий триггер 43 устанавливается в единичное состояние. Первый элемент НЕ 42 предназначен для формирования сигнала сброса счетчиков, на инверсном выходе первого элемента ИЛИ-НЕ 41 появляется единичный сигнал "Пуск АЦП", который поступает на выход 58 блока синхронизации.

Первый импульс с генератора 26 тактовых импульсов переводит первый триггер 27 в единичное состояние, разрешая прохождение тактовых импульсов через первый элемент И 28 и первый элемент ИЛИ 30 на вход первого счетчика 40 с коэффициентом пересчета, равным одиннадцати. Таким образом, осуществляется задержка на один такт, необходимая для переключения коммутатора 3 коррелятора. Сигнал "Запуск АЦП" на выходе 58 блока управления длится два такта. По заднему фронту сигнала "Пуск АЦП" запускается АЦП 4 коррелятора. В течение тактов 3-8 действуют сигналы "чтение" на выходе второго элемента ИЛИ 35 и "Выбор микросхемы" на выходе третьего элемента ИЛИ 37, которые с выхода 54 и 55 блока управления поступают на входы разрешения записи блока 8 памяти. Однако запись содержимого ячейки памяти в регистр 7 не будет осуществляться до тех пор, пока на выходе 60 блока управления имеется сигнал низкого уровня, т.е. четвертый триггер 50 находится в нулевом состоянии.

В течение тактов 3-10 происходит аналого-цифровое преобразование в АЦП 4, на вход которого коммутатор 3 подает сигнал усилителя 2 второго процесса (сигнал управления коммутатор на выходе 58 блока управления равен нулю). Полученный на выходе АЦП 4 код заносится в ЦАП 5 по сигналу "Строб ЦАП", который формируется на одиннадцатом тактовом импульсе третьим элементом И 31 и четвертым элементом И 32. Сигнал с выхода первого элемента И 34 после одиннадцатого тактового импульса устанавливает второй триггер 39 в единичное состояние, что обеспечивает прохождение тактовых импульсов на вход первого счетчика 40 без задержки через второй элемент И 29 и первый элемент ИЛИ 30, а также появление единичного сигнала переключения коммутатора 3. Таким образом, на вход АЦП 4 подключается усилитель 1, управляемый с выхода ЦАП 5 сигналом, пропорциональным ординате второго процесса, задержанным на требуемое время Δ τ

Следующий тактовый импульс сбрасывает выходы первого счетчика 40, что приводит к появлению импульса "Пуск АЦП" на инверсном выходе первого элемента ИЛИ-НЕ 41 и установка третьего триггера 43 в нулевое состояние, разрешающее прохождение импульсов через седьмой элемент И 44 на вход второго счетчика 45.

Последующая серия тактовых импульсов обеспечивает аналого-цифровое преобразование сигнала усилителя 2 в описанном порядке, но вместо сигнала "Строб ЦАП" блок управления формирует на выходе пятого элемента И 33 сигнал "Запись", который разрешает запись в ячейку памяти 8 блока кода с выхода сумматора 6 в соответствии с адресом, установленным на выходе 59 блока управления. На вход сумматора 6 по-прежнему не поступает информация с регистра 7, поскольку сигнал "Сброс регистра" имеет нулевое значение.

После окончания записи в очередную ячейку блока 8 памяти содержимое второго счетчика 45 увеличивается на единицу, что соответствует установке адреса следующей ячейки блока 8 памяти. Такая последовательность работы повторяется до тех пор, пока второй счетчик 45 не заполнится полностью. Коэффициент пересчета этого счетчика равен числу ячеек блока 8 памяти, что соответствует числу точек вычисляемой корреляционной функции.

При переполнении второго счетчика 45 происходит установка второго триггера 39 в нулевое состояние, в результате чего подготавливается цикл вычисления взаимокорреляционной функции следующей реализации случайных процессов, поступающих на входы 10 и 11 коррелятора. Одновременно содержимое третьего счетчика 46 увеличивается на единицу, а сигнал на выходе второго элемента НЕ 48 устанавливает четвертый триггер 50 в единичное состояние, что приводит к снятию сигнала низкого уровня "Сброс регистра" с управляющего входа регистра 7. Следовательно, в каждой ячейке памяти накапливается сумма значений соответствующих точек корреляционной функции, поскольку на вход сумматора 6 поступает записанный в регистр 7 по сигналу "Строб регистра", формируемому на выходе шестого элемента И 36, код содержимого соответствующей ячейки памяти на (i 1)-м цикле измерения, а на другой вход текущий код с выхода АЦП 4.

Третий счетчик 46 служит для подсчета количества К усредняемых измерений корреляционной функции и имеет соответствующий коэффициент пересчета. При заполнении этого счетчика на выходе восьмого элемента И 47 появляется сигнал, разрешающий прохождение через девятый элемент И 49 сигнала "Строб выхода", который используется для синхронизации работы блоков устройства и для стробирования выхода результатов работы устройства.

Операционный блок работает следующим образом.

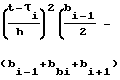

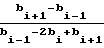

На первые входы сумматоров 67 и 68 поступает код величины bi-1 с входа 63 блока. На вторые входы сумматоров 67 и 68 поступает код величины bi+1 с входа 65 блока. По синхроимпульсу с входа 62 блока сумматора 67 и 68 производят вычисления, в результате которых на выходе сумматора 67 появится код величины (bi+1 bi-1), а на выходе сумматора 68 код величины (bi-1 + +bi+1). Синхроимпульс с входа 62 блока после задержки в элементе 66 на время, необходимое для вычисления в сумматорах 67 и 68, подается на синхровходы сумматора 73, умножителя 71 и перемножителей 69 и 70. На вход умножителя 71 и первый вход сумматора 73 подается код величины bi с входа 64 блока, а на второй вход сумматора 73 подается код величины (bi-1 + bi+1) с выхода сумматора 68. Необходимо отметить, что k-й разряд кода величины bi с входа 64 блока подключен к (k + 1)-му разряду входа сумматора 73, что эквивалентно умножению двоичного кода на 2. На первый и второй входы перемножителя 69 и первый вход перемножителя 70 поступает код величины τo с выхода делителя 77 (в первые такты единичный код), т.е. перемножитель 69 работает как квадратор. На второй вход перемножителя 70 подается код величины (bi+1 bi-1) с выхода сумматора 67, по синхроимпульсу, с выхода элемента задержки 66 сумматор 73, умножитель 71 и перемножители 69, 70 производят вычисление, в результате которых на выходе сумматора 73 появится код величины (bi-1 2bi + bi+1), на выходе умножителя 71 код величины 6bi, т.е. осуществляет умножение на 6, на выходе перемножителя 69 код величины τo2, на выходе перемножителя 70 код величины (bi+1 -bi-1) τo/2. Синхроимпульс после задержки в элементе 72 на время, необходимое для вычисления в сумматоре 73, умножителе 71 и перемножителях 69 и 70, подается на синхровходы делителя 77, перемножителя 74 и сумматора 75. k-й разряд кода величины (bi-1 2bi + bi+1) c выхода сумматора 73 подключен к (k 1)-м разрядам первого входа перемножителя 74, что соответствует делению на 2, на второй вход перемножителя 74 подается код величины τo2 с выхода перемножителя 69. k-й разряд кода величины (bi-1- 2bi + bi+1) с выхода сумматора 73 подключен к (k + 1)-му разряду второго входа делителя 77, что соответствует умножению двоичного кода на 2, на первый вход делителя 77 подается код величины (bi+1 bi-1), с выхода сумматора 67. На первый вход сумматора 75 подается код величины (bi+1 + bi-1) с выхода сумматора 68, на второй вход сумматора 75 подается код величины 6bi с выхода умножителя 71. По синхроимпульсу с выхода элемента задержки 72 делитель 77, перемножитель 74 и сумматор 75 производят вычисления, в результате чего на выходе делителя 74 появится код величины τo=

который поступает на 88 выход блока, на выходе перемножителя 74 появится код величины

который поступает на 88 выход блока, на выходе перемножителя 74 появится код величины  bi+

bi+  , на выходе сумматора 75 код величины (bi-1 + 6bi + bi+1). Далее синхроимпульс с выхода элемента задержки 78, в котором задерживается на время, необходимое для вычисления в делителе 77, перемножителе 74 и сумматоре 75, подается на синхровход сумматора 78. На первый вход сумматора 78 подается код величины

, на выходе сумматора 75 код величины (bi-1 + 6bi + bi+1). Далее синхроимпульс с выхода элемента задержки 78, в котором задерживается на время, необходимое для вычисления в делителе 77, перемножителе 74 и сумматоре 75, подается на синхровход сумматора 78. На первый вход сумматора 78 подается код величины  bi+

bi+  с выхода перемножителя 74, на второй вход сумматора 78 подается код величины (bi+1 bi-1) τo/2 с выхода перемножителя 70.

с выхода перемножителя 74, на второй вход сумматора 78 подается код величины (bi+1 bi-1) τo/2 с выхода перемножителя 70.

По синхроимпульсу с выхода элемента задержки 70 сумматор 78 производит вычисление, в результате которого на выходе сумматора 78 появится код величины  bi+

bi+  +

+

. Далее синхроимпульс после задержки в элементе задержки 79 на время, необходимое для вычисления в сумматоре 78, подается на синхровходы компараторов 82, 84 и сумматора 80. На первый вход сумматора 80 пода- ется код величины

. Далее синхроимпульс после задержки в элементе задержки 79 на время, необходимое для вычисления в сумматоре 78, подается на синхровходы компараторов 82, 84 и сумматора 80. На первый вход сумматора 80 пода- ется код величины  bi+

bi+  +

+

с выхода сумматора 78. k-й разряд кода величины (bi-1 + 6bi + bi+1) с выхода сумматора 75 подключен к (k 3)-му разряду входа сумматора 80, что соответствует делению двоичного кода на 8. На установочный вход 81 компаратора 82 подается единичный код, соответствующий коду единичного уровня сигнала, а на установочный вход 83 компаратора 84 подается нулевой код (все разряды соединены с нулевой шиной). На информационные входы компаратора 82 и 84 подается код τo с выхода делителя 77. По синхроимпульсу с выхода элемента задержки 79 компараторы 82 и 84 производят сравнение вида (2), а на выходе сумматора 80 появляется код величины

с выхода сумматора 78. k-й разряд кода величины (bi-1 + 6bi + bi+1) с выхода сумматора 75 подключен к (k 3)-му разряду входа сумматора 80, что соответствует делению двоичного кода на 8. На установочный вход 81 компаратора 82 подается единичный код, соответствующий коду единичного уровня сигнала, а на установочный вход 83 компаратора 84 подается нулевой код (все разряды соединены с нулевой шиной). На информационные входы компаратора 82 и 84 подается код τo с выхода делителя 77. По синхроимпульсу с выхода элемента задержки 79 компараторы 82 и 84 производят сравнение вида (2), а на выходе сумматора 80 появляется код величины

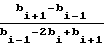

Rmax=  bi+

bi+  +

+

+

+  bi-1+6bi+b

bi-1+6bi+b этот код поступает на выход 90 блока. Компараторы 82 и 84 производят сравнение кода величины τo соответственно с единичными "1" и "0" кодами. Если код τo < 1 или τo 1, то на соответствующем выходе компаратора 82 Р < Q или Р Q появится единичный сигнал, который через элемент "ИЛИ" 85 поступает на первый вход элемента "И-НЕ" 87. Если код τo > 0 или τo 0, то на соответствующем выходе компаратора 84 Р > Q или Р Q появится единичный сигнал, который через элемент "ИЛИ" 86 поступает на второй вход элемента И-НЕ 87. Таким образом, на выходе элемента И-НЕ 87 и соответственно на выходе 89 блока появится нулевой сигнал в случае, когда

этот код поступает на выход 90 блока. Компараторы 82 и 84 производят сравнение кода величины τo соответственно с единичными "1" и "0" кодами. Если код τo < 1 или τo 1, то на соответствующем выходе компаратора 82 Р < Q или Р Q появится единичный сигнал, который через элемент "ИЛИ" 85 поступает на первый вход элемента "И-НЕ" 87. Если код τo > 0 или τo 0, то на соответствующем выходе компаратора 84 Р > Q или Р Q появится единичный сигнал, который через элемент "ИЛИ" 86 поступает на второй вход элемента И-НЕ 87. Таким образом, на выходе элемента И-НЕ 87 и соответственно на выходе 89 блока появится нулевой сигнал в случае, когда

0 ≅ τo ≅ 1, где τo=  i

i

Таким образом, устройство для определения корреляционной функции дополнительно позволяет определять уточненное значение максимума корреляционной функции Rmax R(ti + τoh) в случае некогерентной обработки сигналов, т. е. расширяет функциональные возможности прототипа, чем достигается поставленная цель изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВАЯ РЕГУЛИРУЕМАЯ ЛИНИЯ ЗАДЕЖКИ | 1992 |

|

RU2011290C1 |

| Устройство отождествления | 1991 |

|

SU1803910A1 |

| Устройство для обработки информации | 1989 |

|

SU1631539A1 |

| Устройство для определения взаимной корреляционной функции | 1990 |

|

SU1751779A1 |

| Устройство обработки информации комплексной измерительной системы | 1990 |

|

SU1837283A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ МЕСТ ПОВРЕЖДЕНИЯ НАПОРНОГО ТРУБОПРОВОДА | 1992 |

|

RU2046251C1 |

| Устройство для измерения расстояния между центрами двух изображений точечного объекта | 1990 |

|

SU1788597A1 |

| Устройство для мажоритарного декодирования | 1987 |

|

SU1517137A1 |

| ГЕНЕРАТОР ПОСЛЕДОВАТЕЛЬНОСТЕЙ КОДА СТИФФЛЕРА | 2017 |

|

RU2668742C1 |

| Делительное устройство | 1983 |

|

SU1168929A1 |

Устройство для определения корреляционной функции относится к цифровой обработке сигналов и позволяет наряду с получением отсчетов корреляционной функции формировать максимальное значение корреляционной функции при некогерентной обработке сигналов, и может быть использовано в устройствах оценки параметров сигналов, следящих измерителях, системах синхронизации за счет введения в устройство буферного регистра, блока решения системы управления, кольцевого регистра сдвига операционного блока, элементов задержки, регистра сдвига, счетчика-делителя и элемента И. 2 з.п. ф-лы, 5 ил.

| Устройство для определения корреляционной функции | 1987 |

|

SU1501086A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1995-06-09—Публикация

1992-07-29—Подача