(54) МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительно-делительное устройство | 1981 |

|

SU993278A2 |

| Множительно-делительное устройство | 1980 |

|

SU949662A1 |

| Множительно-делительное устройство | 1978 |

|

SU763915A1 |

| АНАЛОГО-ЦИФРОВАЯ МНОГОПРОЦЕССОРНАЯ СИСТЕМА | 2006 |

|

RU2333533C1 |

| Множительно-делительное устройство | 1980 |

|

SU902026A1 |

| Множительно-делительное устройство | 1980 |

|

SU883920A2 |

| АНАЛОГО-ЦИФРОВОЕ МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1997 |

|

RU2121712C1 |

| Вычислительное устройство | 1986 |

|

SU1320819A1 |

| МНОГОКАНАЛЬНАЯ АКУСТИКО-ЭМИССИОННАЯ СИСТЕМА ДИАГНОСТИКИ КОНСТРУКЦИЙ | 2017 |

|

RU2664795C1 |

| АНАЛОГО-ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1997 |

|

RU2123720C1 |

Изобретение относится к аналогов и аналого-цифровой вычислительной технике и может быть- использовано . в вычислительных машинах, моделирующих установках и других областях и мерительной техники. Известны устройства для определе ния отношения двух напряжений, реализуемые с помощью аналоговых вычислительных устройств. Недостатки этих устройств - напряжение смещения числителя, напряжение смещения знаменателя, погрешность масштабного коэффициента, нелинейность f(Uqд, и), и, как сл ствие, трудность настройки. .Известно также множительно-делительное устройство (ВДУ), использующее принцип аналого-цифрового преобразования, состоящее из компа.ратора, квантующего генератора, клю ча, счетчика, цифроаналогового преобразователя ЦАП), умножителя и та тового генератора Q . Недостаток этого МДУ - ограниченный динамический диапазон входных сигналов, а также сложность настойки и изготовления умножителя. Наиболее близким по технической сущности к предлагаемому является множительно делительное устройство, состоящее из генератора синхроимпульсов, компаратора, схемы И, двухпозиционного ключа, входного вентиля и запоминающего устройства 2}. Недостаток этого МДУ ограниченные функциональные возможности устройства и, как следствие этого, ограниченный диапазон входных сигналов, так как, исходя из принципа работы АЦП, отношение числителя к знаменателю должно быть всегда меньше 1. Цель изобретения - расширение динамического диапазона входных аналоговых сигналов. Поставленная цель достигается тем, что в множительно-делителькое устройство, содержащее генератор сиихроимпульсов, генератор тактовых импульсов, двухпозиционный ключ, один информационный вход которого является входом делителя устройства, счетчик, цифроаналоговый преобразователь, первый вход которого подключен к выходу счетчика, первый компаратор, первый вход которого подключен к выходу цифроаналогового преобразователя, второй вход первого компаратора является входом первого сомножителя устройства, введены блок управления, усилитель с регулируемым коэффициентом усиления, второй компаратор, резистивный делитель напряжения, сдвиговый регистр, первьй вход которого подключен к генератору синхроимпульсов и к первому входу блока управления, второй вход - к генератору тактовых импульсов и ко второму входу блока управления, третий вход подключен к выходу второго компаратора и к третьему входу блока управления, выход сдвигового регистра подключен к управляющим входам резистивного делителя напряжений и усилителя с регулируемым коэффициентом усиления, первый вход второго компаратора подключен к выходу усилителя с регулируемым коэффициентом усиления, второй вход второго компаратора подключен ко входу первого сомножителя устройства, информационный вход резистивного делителя напряжений подключен ко входу второго сомножителя устройства, выход резистивного делителя напряжений подключен ко второму информационному входу ключа, управляющий вход которого подключен кпервому выходу блока управления, а выход двухпозиционного ключа подключен ко входу усилителя с регулируемым коэффициентом усиления, выход которого подключен ко второму входу цифроаналогового преобразователя, выход первого ком паратора подключен к четвертому входу блока управления, второй выход блока управления подключен ко входу счетчика.

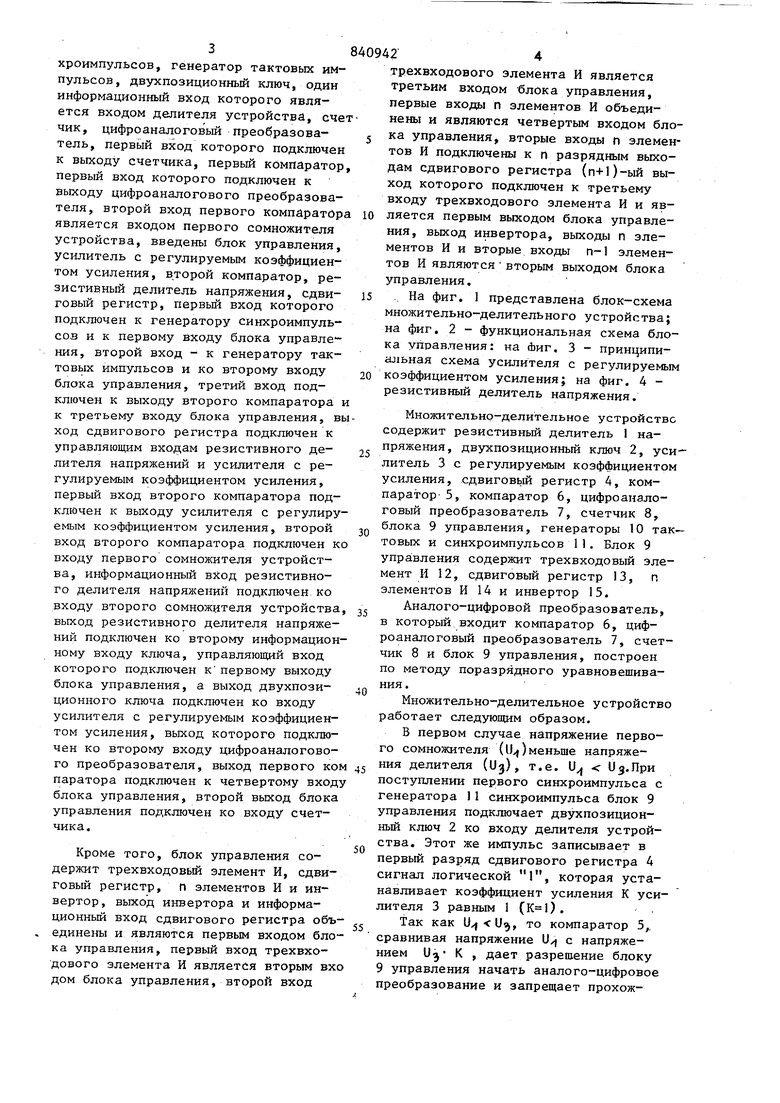

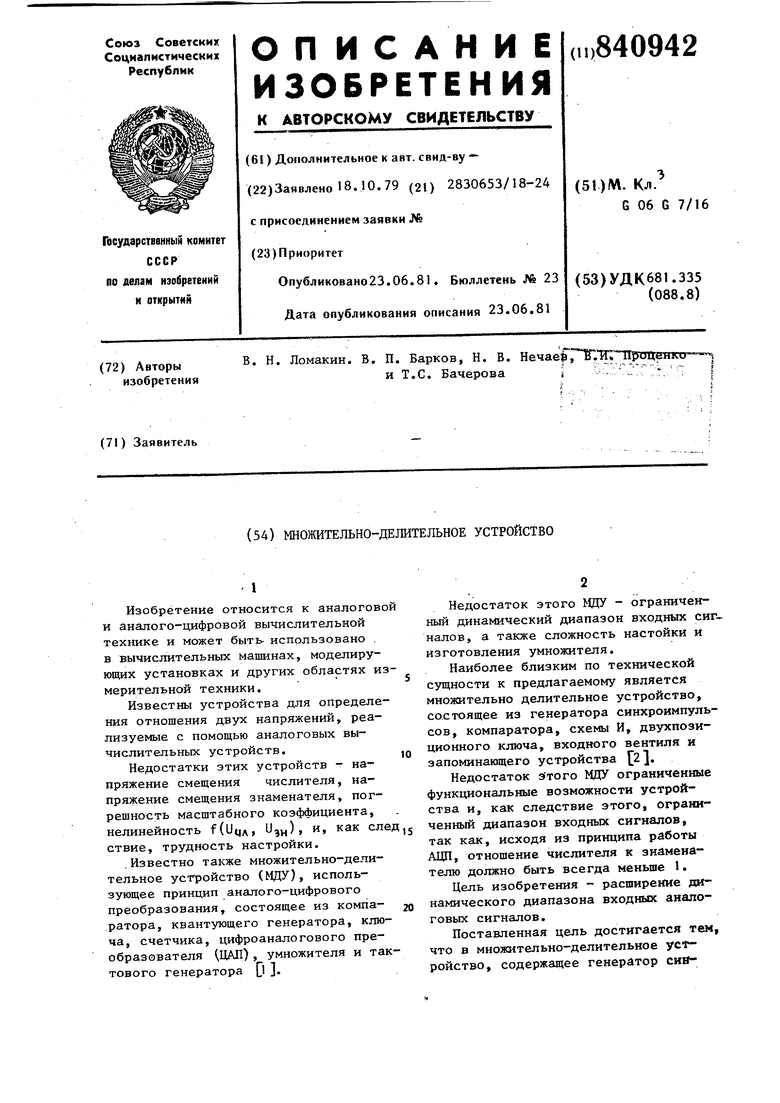

Кроме того, блок управления содержит трехвходовый элемент И, сдвиговый регистр, п элементов И и инвертор , выход инвертора и информационный вход сдвигового регистра объединены и являются первым входом блока управления, первый вход трехвходового элемента И является вторым вхо дом блока управления, второй вход

трехвходового элемента И является третьим входом блока управления, первые входы п элементов И объединены и являются четвертым входом блока управления, вторые входы п элементов И подключены к п разрядным выходам сдвигового регистра (п+1)-ый выход которого подключен к третьему входу трехвходового элемента И и является первым выходом блока управления, выход инвертора, выходы п элементов И и вторые входы п-1 элементов И являютсявторьм выходом блока управления.

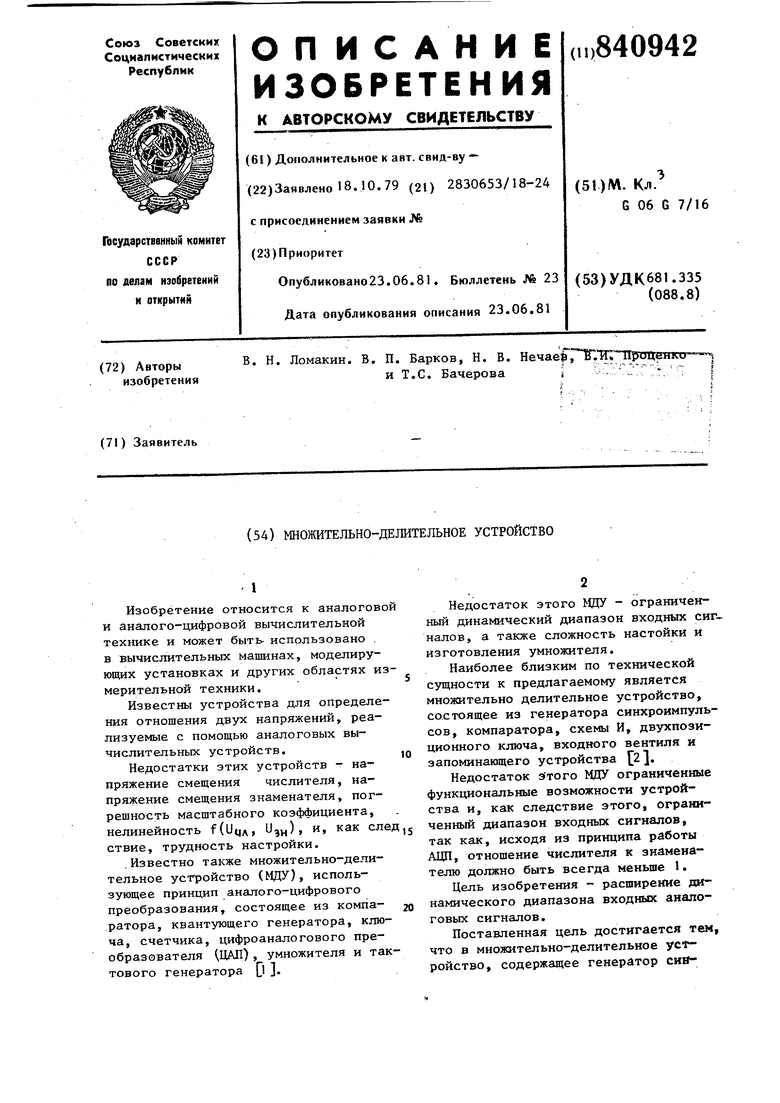

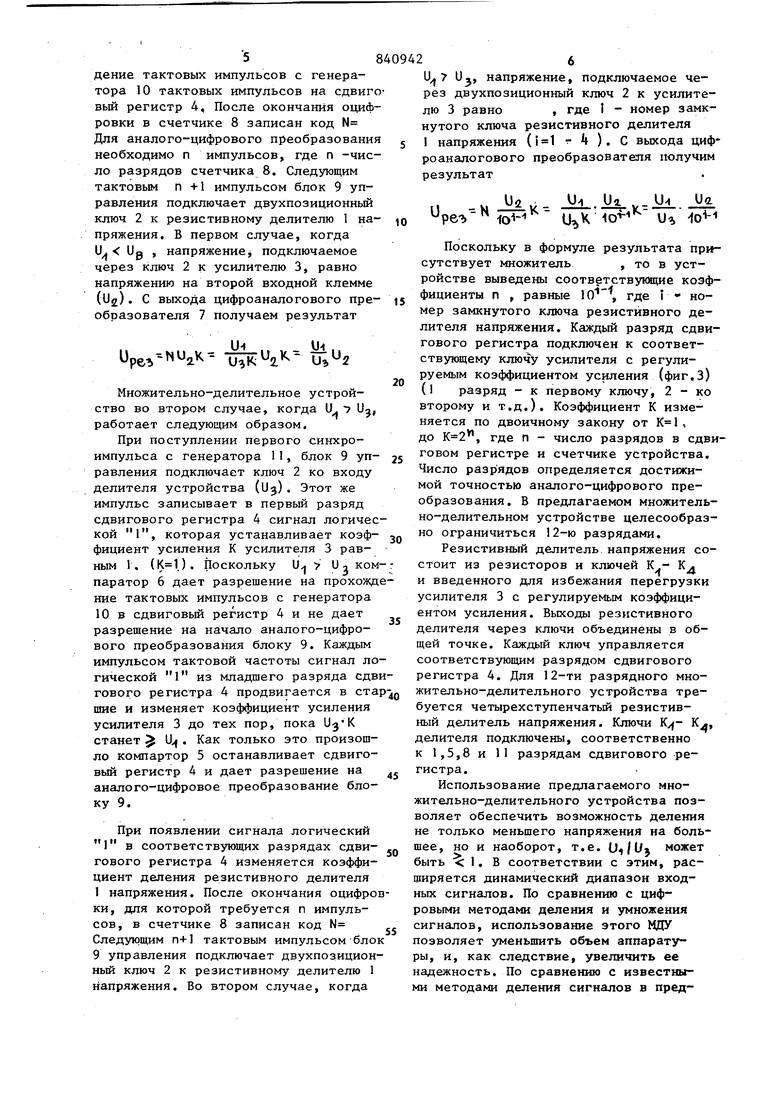

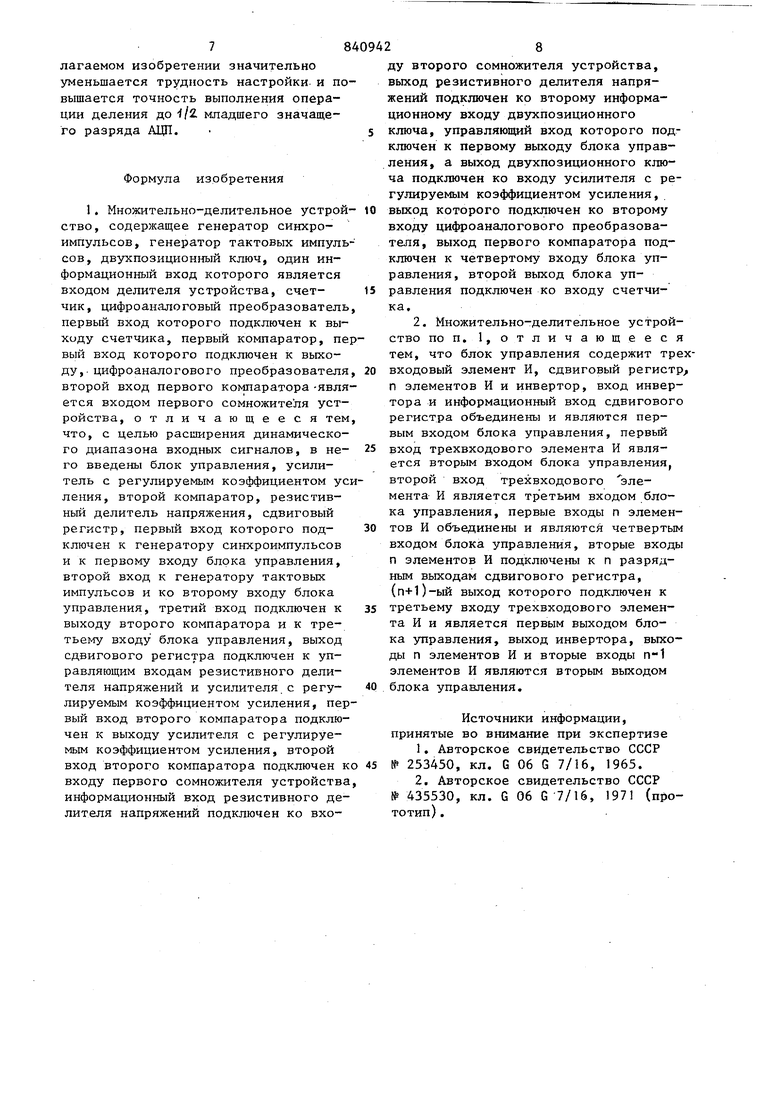

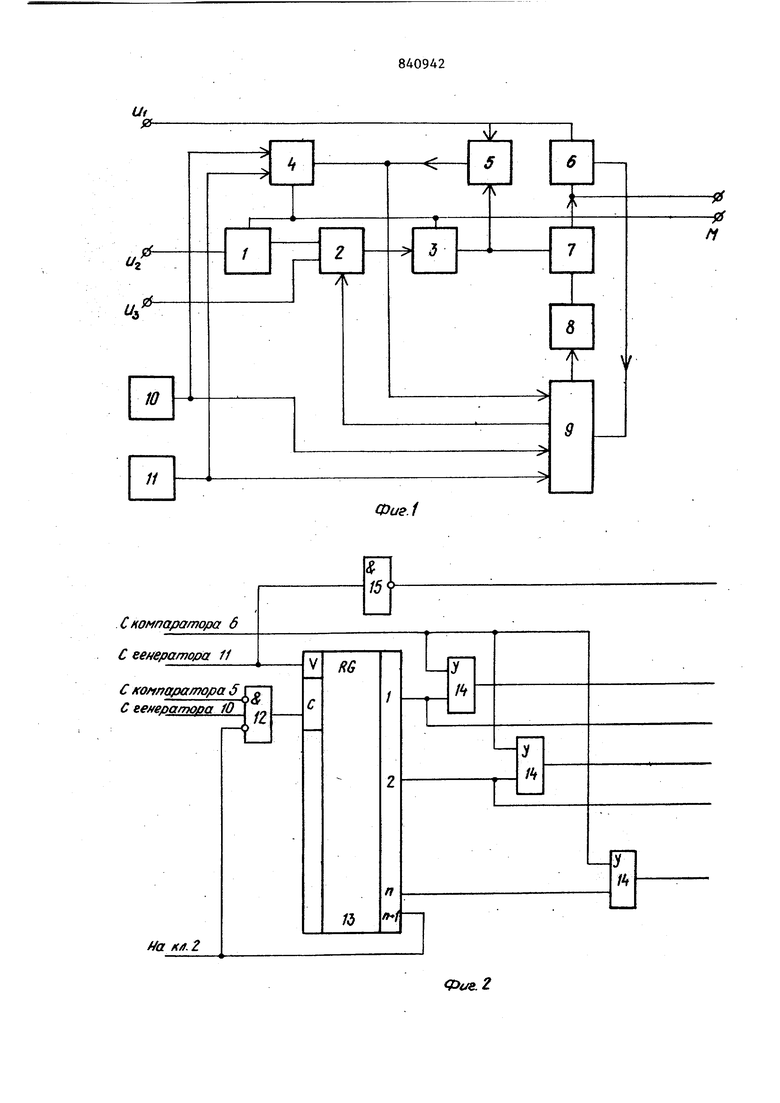

., На фиг. 1 представлена блок-схема множительно-делительного устройства; на фиг. 2 - функциональная схема блока управления: на Фиг. 3 - принципиальная схема усилителя с регулируемым коэффициентом усиления; на фиг. 4 резистивный делитель напряжения.

Множительнр-делительное устройстве содержит резистивный делитель 1 напряжения, двухпозиционный ключ 2, усилитель 3 с регулируемым коэффициентом усиления, сдвиговый регистр 4, компаратор- 5, компаратор 6, цифроаналоговый преобразователь 7, счетчик 8, блока 9 управления, генераторы 10 тактовых и синхроимпульсов 11. Блок 9 управления содержит трехвходовый элемент И 12, сдвиговый регистр 13, п элементов И 14 и инвертор 15.

Аналого-цифровой преобразователь, в который входит компаратор 6, цифроаналоговый преобразователь 7, счетчик 8 и блок 9 управления, построен по методу поразрядного уравновешивания ,

Множительно-делительное устройство работает следующим образом.

В первом случае напряжение первого сомножителя (Uxj) меньше напряжения делителя (U), т.е. 11 и.При поступлении первого синхроимпульса с генератора 11 синхроимпульса блок 9 управления подключает двухпозиционный ключ 2 ко входу делителя устройства. Этот же импульс записывает в первый разряд сдвигового регистра 4 сигнал логической 1, которая устанавливает коэффициент усиления К усилителя 3 равным 1 ().

Так как U,(U, то компаратор 5,, сравнивая напряжение U/| с напряжением К , дает разрешение блоку 9 управления начать аналого-цифровое преобразование и запрещает прохождение тактовых импульсов с генератора 10 тактовых импульсов на сдвиго вый регистр 4, После окончания оцифровки в счетчике 8 записан код N Для аналого-цифрового преобразования необходимо п импульсов, где п -число разрядов счетчика 8. Следующим тактовым п +1 импульсом блок 9 управления подключает двухпозиционный ключ 2 к резистивному делителю 1 напряжения. В первом случае, когда и. Ug , напряжение, подключаемое через ключ 2 к усилителю 3, равно напряжению на второй входной клемме (1)2). С выхода цифроаналогового преобразователя 7 получаем результат Upe,,-Nu,,K-- u;u. Множительно-делительное устройство во втором случае, когда U 7 U, работает следующим образом. При поступлении первого синхроимпульса с генератора 11, блок 9 управления подключает ключ 2 ко входу делителя устройства (УЗ). Этот же импульс записывает в первый разряд сдвигового регистра 4 сигнал логичес кой 1, которая устанавливает коэффициент усиления К усилителя 3 равным 1. (). Поскольку и У и т ком паратор 6 дает разрешение на прохожд ние тактовых импульсов с генератора 10 в сдвиговый регистр 4 и не дает разрешение на начало аналого-цифрового преобразования блоку 9. Каждым импульсом тактовой частоты сигнал ло гической 1 из младшего разряда сдв гового регистра 4 продвигается в ста шие и изменяет коэффициент усиления усилителя 3 до тех пор, пока станет Щ. Как только это произошло компартор 5 останавливает сдвиговый регистр 4 и дает разрешение на аналого-цифровое преобразование блоку 9. При появлении сигнала логический 1 в соответствующих разрядах сдвигового регистра 4 изменяется коэффициент деления резистивного делителя 1 напряжения. После окончания оцифро ки, для которой требуется п импульсов, в счетчике 8 записан код N Следующим п+1 тактовым импульсомбло 9 управления подключает двухпозицион ный ключ 2 к резистивному делителю 1 напряжения. Во втором случае, когда 8 2 и, напряжение, подключаемое через двухпозиционный ключ 2 к усилителю 3 равно , где I - номер замкнутого ключа резистивного делителя 1 напряжения (i 1 - ). С выхода цифроаналогового преобразователя получим результат iJi.v-ibL U% Поскольку в формуле результата присутствует множитель , то в устройстве выведены соответствукяцие коэффициенты п , равные Ю, где номер замкнутого ключа резистивного делителя напряжения. Каждый разряд сдвигового регистра подключен к соответствующему ключу усилителя с регулируемым коэффициентом усиления (фиг.З) (1 разряд - к первому ключу, 2 - ко второму и т.д.). Коэффициент К изменяется по двоичному закону от , до , где п - число разрядов в сдвиговом регистре и счетчике устройства. Число разрядов определяется достижимой точностью аналого-цифрового преобразования . В предлагаемом множительно-делительном устройстве целесообразно ограничиться 12-ю разрядами. Резистивный делитель, напряжения состоит из резисторов и ключей К - Кд и введенного для избежания перегрузки усилителя 3 с регулируемьм коэффициентом усиления. Выходы резистивного делителя через ключи объединены в общей точке. Каждый ключ управляется соответствующим разрядом сдвигового регистра 4. Для 12-ти разрядного множительно-делительного устройства требуется четырехступенчатый резистивный делитель напряжения. Ключи К«, делителя подключены, соответственно к 1,5,8 и 11 разрядам сдвигового регистра. Использование предлагаемого множительно-делительного устройства позволяет обеспечить возможность деления не только меньшего напряжения на большее, но и наоборот, т.е. может быть 1. В соответствии с этим, расширяется динамический диапазон входных сигналов. По сравнению с цифровыми методами деления и умножения сигналов, использование этого МДУ озволяет уменьшить объем аппаратуры, и, как следствие, увеличить ее надежность. По сравнению с известныи методами деления сигналов в предлагаемом изобретении значительно уменьшается трудность настройки и повышается точность выполнения операции деления до /2 младшего значащего разряда АЦП.

Формула изобретения

второй вход трехвходового элемента И является третьим входом блока управления, первые входы п элементов И объединены и являются четвертьм входом блока управления, вторые входы п элементов И подключены к п разрядным выходам сдвигового регистра, (п+1)-ый выход которого подключен к третьему входу трехвходового элемента И и является первым выходом блока управления, выход инвертора, выходы п элементов И и вторые входы п-1 элементов И являются вторым выходом блока управления.

Источники информации, принятые во внимание при экспертизе

№ 435530, кл. G 06 G 7/16, 1971 (прототип) .

Фиг.1

Фи. 5

Авторы

Даты

1981-06-23—Публикация

1979-10-18—Подача