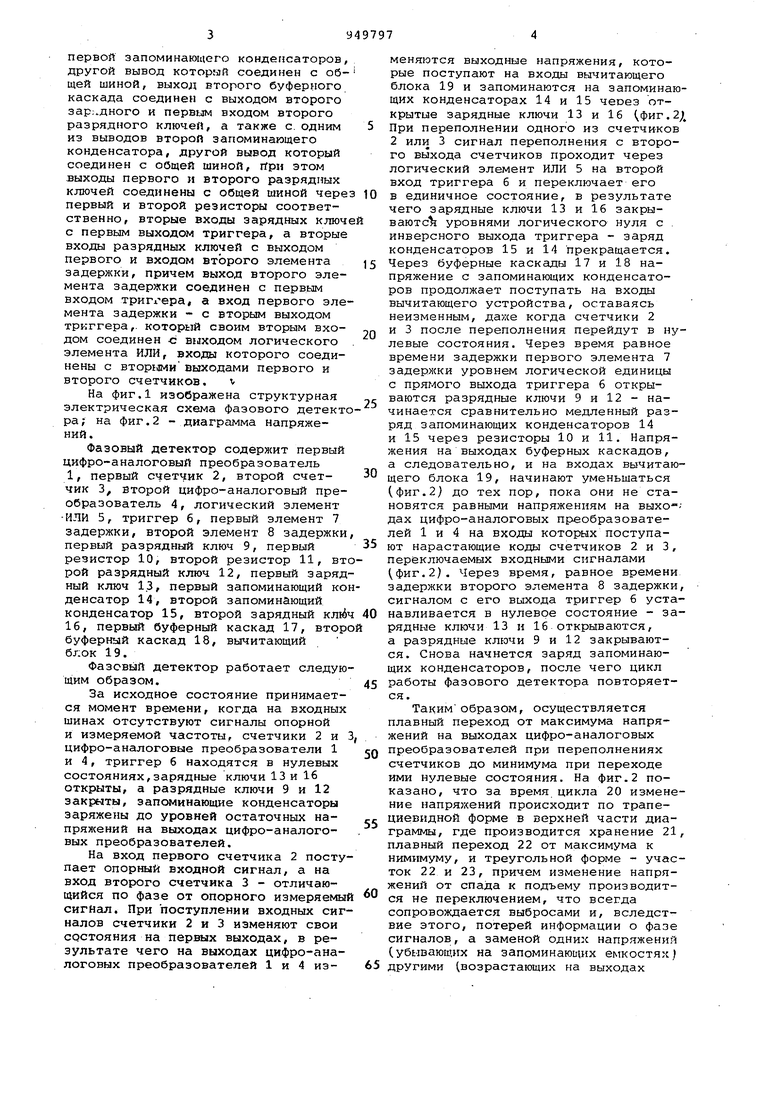

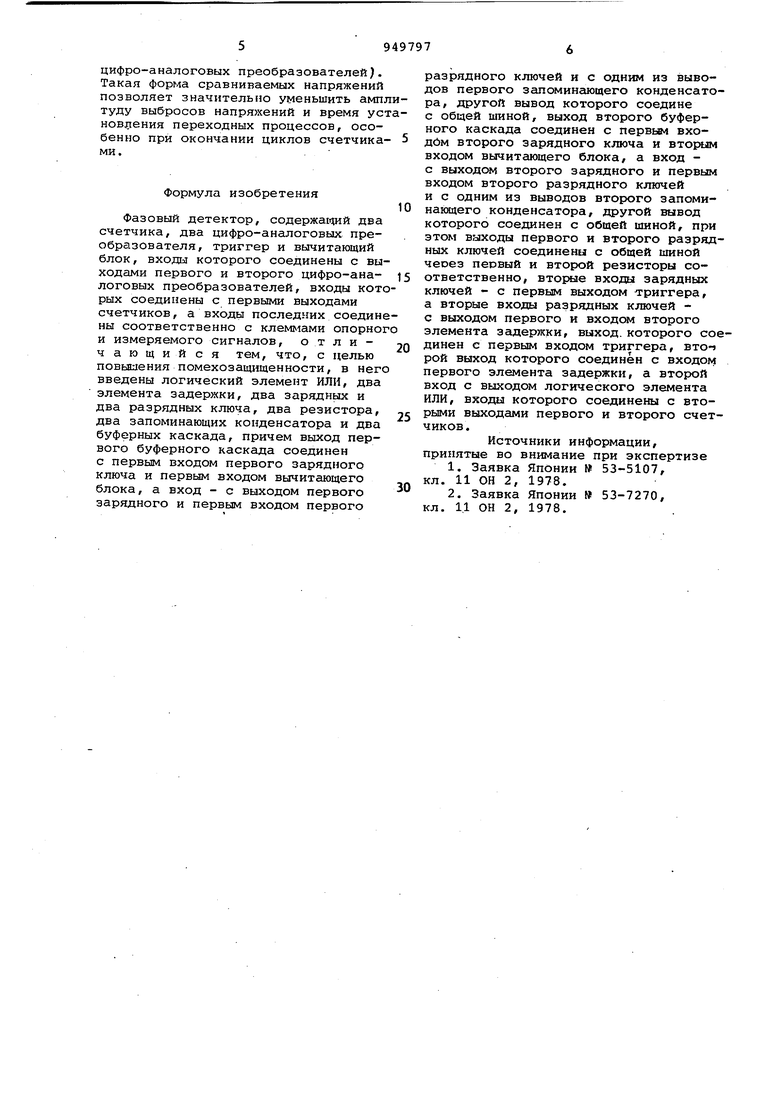

Изобретение относится к радиотехнике и может быть использовано в информационно-измерительной технике и системах импульсно-фазовой автоподстройки частоты. Известен фазовый детектор, содержащий два счетчика, два триггера, цифровое вычитающее устройство, цифро-аналоговый преобразователь и фильтр. В этом фазовом детекторе выходной сигнал формируется вычитанием кодов счетчиков с последующим преобразованием результатов вычитания в аналоговую величину Cl. Недостатком этого фазового детектора является низкая помехозащищенность . Наиболее близким по технической сущности к предлагаемому является фазовый детектор, содержащий два счетчика, два цифро-аналоговых преобразователя, два триггера, вычитающее устройство и фильтр, в котором с целью увеличения помехозащищеннос ти в момент сброса любого из счетчи ков цифро-аналоговые преобразователи устанавливаются не в нулевое сое тояние, а поддерживают определенный уровень C2D. Однако данный фазовий детектор также имеет недостаточно высокую помехозащищенность. Цель изобретения - повышение помехозащищенности фазового детектора. Поставленная цель достигается тем, что в фазовый детектор, содержащий два счетчика, два цифро-аналоговых преобразователя, триггер и вычитающий блок, соединенные входами с выходами первого и второго цифроаналоговых преобразователей, входы которых соединены с первыми выходами счетчиков, которые входами соединены с клеммами опорного и измеряемого сигнала, дополнительно, введены логический элемент ИЛИ, два элемента задержки, два зарядных и два разрядных ключа, два резистора, два запоминающих конденсатора и два буферных каскада, выход первого из которых соесоединен с первым входом первого зарядного ключа и первым входом вычитающего блока, а выход второго с первым входом второго зарядного ключа и вторым входом вычитающего блока, вход первого буферного каскада соединен с выходом первого зарядного и первым входом первого зарядного ключей, а также с одним из выводов первой запоминающего конденсаторов другой вывод котормй соединен с общей шиной, выход второго буферного каскада соединен с выходом второго зар;.дного и первым входом второго разрядного ключей, а также с. одним из выводов второй запоминающего конденсатора, другой вывод который соединен с общей шиной, гГрн этом выходы первого н второго разрядных ключей соединены с общей шиной чере первый и второй резисторы соответственно, вторые входы зарядных ключ с первым выходом триггера, а вторые входы разрядных ключей с выходом первого и входом второго элемента задержки, причем выход второго элемента задержки соединен с первым входом триггера, а вход первого эле мента задержки - с вторым выходом триггера,, который своим вторым входом соединен -с выходом логического элемента ИЛИ, входы которого соединены с вторыми выходами первого и второго счетчиков. v На фиг.1 изображена структурная электрическая схема фазового детект ра ; на фиг.2 - диаграмма напряжений. Фазовый детектор содержит первый цифро-аналоговый преобразователь 1, первый счетчик 2, второй счетчик 3, Второй цифро-аналоговый преобразователь 4, логический элемент ИЛИ 5, триггер 6, первый элемент 7 задержки, второй элемент 8 задержки первый разрядный ключ 9, первый резистор 10, второй резистор 11, вт рой разрядный ключ 12, первый заряд ный ключ 1,3, первый запоминающий ко денсатор 14, второй запоминающий конденсатор 15, второй зарядный кли 16, первый буферный каскад 17, втор буферный каскад 18, вычитающий блок 19. Фазовый детектор работает следую щим образом. За исходное состояние принимается момент времени, когда на входных шинах отсутствуют сигналы опорной и измеряемой частоты, счетчики 2 и цифро-аналоговые преобразователи 1 и 4, триггер 6 находятся в нулевых состояниях,зарядные ключи 13 и 16 открыты, а разрядные ключи 9 и 12 закрыты, запоминающие конденсаторы заряжены до уровней остаточных напряжений на выходах цифро-аналоговых преобразователей. На вход первого счетчика 2 посту пает опорный входной сигнал, а на вход второго счетчика 3 - отличающийся по фазе от опорного измеряемы сигнал. При поступлении входных сиг налов счетчики 2 и 3 изменяют свои состояния на первых выходах, в результате чего на выходах цифро-аналоговых преобразователей 1 и 4 изменяются выходные напряжения, которые поступают на входы вычитающего блока 19 и запоминаются на запоминающих конденсаторах 14 и 15 чеоез открытые зарядные ключи 13 и 16 фиг.. При переполнении одного из счетчиков 2 или 3 сигнал переполнения с второго выхода счетчиков проходит через логический элемент ИЛИ 5 на второй вход триггера 6 и переключает его в единичное состояние, в результате чего зарядные ключи 13 и 16 закрываютс уровнями логического нуля с . инверсного выхода триггера - заряд конденсаторов 15 и 14 прекращается. Через буферные каскады 17 и 18 напряжение с запоминающих конденсаторов продолжает поступать на входы вычитающего устройства, оставаясь неизменным, дахсе когда счетчики 2 и 3 после переполнения перейдут в нулевые состояния. Через время равное времени задержки первого элемента 7 задержки уровнем логической единицы с прямого выхода триггера 6 открываются разрядные ключи 9 и 12 - начинается сравнительно медленный разряд запоминающих конденсаторов 14 и 15 через резисторы 10 и 11. Напряжения на выходах буферных каскадов, а следовательно, и на входах вычитающего блока 19, начинают уменьшаться (фиг.2) до тех пор, пока они не становятся равными напряжениям на цифро-аналоговых преобразователей 1 и 4 на входы которых поступают нарастающие коды счетчиков 2 и 3, переключаемых входными сигналами (фиг.2). Через время, равное времени задержки второго элемента 8 задержки, сигналом с его выхода триггер 6 устанавливается в нулевое состояние - зарядные ключи 13 и 16 открываются, а разрядные ключи 9 и 12 закрываются. Снова начнется заряд запоминающих конденсаторов, после чего цикл работы фазового детектора повторяется. Такимобразом, осуществляется плавный переход от максимума напряжений на выходах цифро-аналоговых преобразователей при переполнениях счетчиков до минимума при переходе ими нулевые состояния. На фиг.2 показано, что за время цикла 20 изменение напряжений происходит по трапециевидной форме в верхней части диаграммы, где производится хранение 21, плавный переход 22 от максимума к нимимуму, и треугольной форме - участок 22 и 23, причем изменение напряжений от спада к подъему производится не переключением, что всегда сопровождается выбросами и, вследствие этого, потерей информации о фазе сигналов, а заменой одних напряжений (убывающих на запоминающих емкостях) другими (возрастающих на выходах цифро-аналоговых преобразователей). Такая форма сравниваемых напряжений позволяет значительно уменьшить ампл туду выбросов напряжений и время уст переходных процессов, особенно при окончании циклов счетчиками. Формула изобретения Фазовый детектор, содержащий два счетчика, два цифро-аналоговых преобразователя, триггер и вычитающий блок, входы которого соединены с выходами первого и второго цифро-аналоговых преобразователей, входы кото рых соединены с первыми выходами счетчиков, а входы последних соедине ны соответственно с клеммами опорног и измеряемого сигналов, о т л и чающийся тем, что, с целью повышения помехозащищенности, в него введены логический элемент ИЛИ, два элемента задержки, два зарядных и два разрядных ключа, два резистора, два запоминающих конденсатора и два буферных каскада, причем выход первого буферного каскада соединен с первым входом первого зарядного ключа и первым входом вычитающего блока, а вход - с выходом первого зарядного и первЕдм входом первого разрядного ключей и с одним из выводов первого запоминающего конденсатора, другой вывод которого соедине с общей шиной, выход второго буферного каскада соединен с перньм входим второго зарядного ключа и вторым входом вычитающего блока, а вход с выходом второго зарядного и первым входом второго разрядного ключей и с одним из выводов второго запоминающего конденсатора, другой вывод которого соединен с общей шиной, при этом выходы первого и второго разрядных ключей соединены с общей шиной чеоез первый и второй резисторы соответственно, вторые входы зарядных ключей - с первым выходом триггера, а вторые входы разрядных ключей с выходом первого и входе второго элемента задержки, выход, которого соединен с первым входом триггера, BTOI рой выход которого соединен с входом первого элемента задержки, а второй вход с выходом логического элемента ИЛИ, входы которого соединены с вторыми выходами первого и второго счетчиков. Источники информации, принятые во внимание при экспертизе 1.Заявка Японии 53-5107, кл. 11 ОН 2, 1978. 2.Заявка Японии 53-7270, кл. 1,1 ОН 2, 1978.

| название | год | авторы | номер документа |

|---|---|---|---|

| Измеритель нелинейности импульсовпилООбРАзНОгО НАпРяжЕНия | 1979 |

|

SU805207A1 |

| ПИКОВЫЙ ДЕТЕКТОР | 2009 |

|

RU2409818C1 |

| Измеритель коэффициента нелинейности пилообразного напряжения | 1980 |

|

SU894607A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU771729A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ РЕЗОНАНСНОЙ ЧАСТОТЫ ЭЛЕМЕНТОВ КОНСТРУКЦИИ | 1991 |

|

RU2017082C1 |

| СПОСОБ ВИХРЕТОКОВОГО КОНТРОЛЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2007 |

|

RU2365910C2 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| Устройство для измерения коэффициента нелинейности пилообразного напряжения | 1981 |

|

SU978077A1 |

| Фазовый детектор | 1980 |

|

SU879764A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU984041A1 |

Авторы

Даты

1982-08-07—Публикация

1980-12-30—Подача