Изобретение относится к цифровой электронно-измерительной технике и может быть использовано в цифровых измерительных системах,

Целью изобретения является повышение точности и помехозащищенности преобразователя.

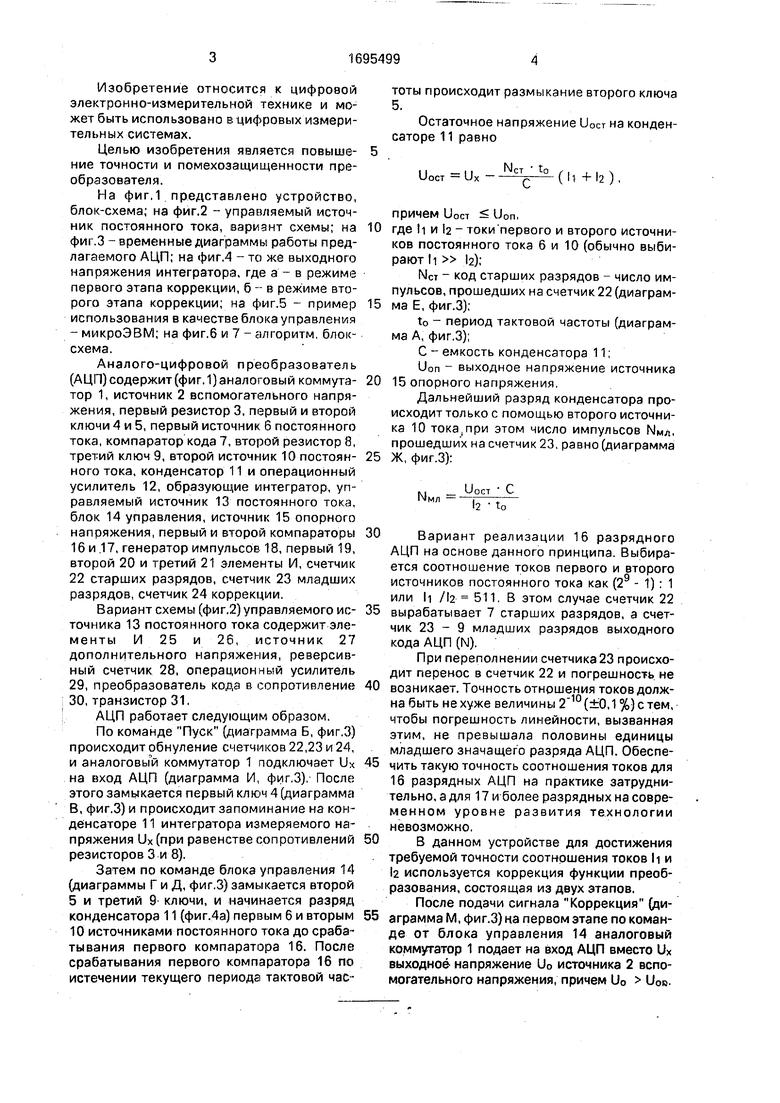

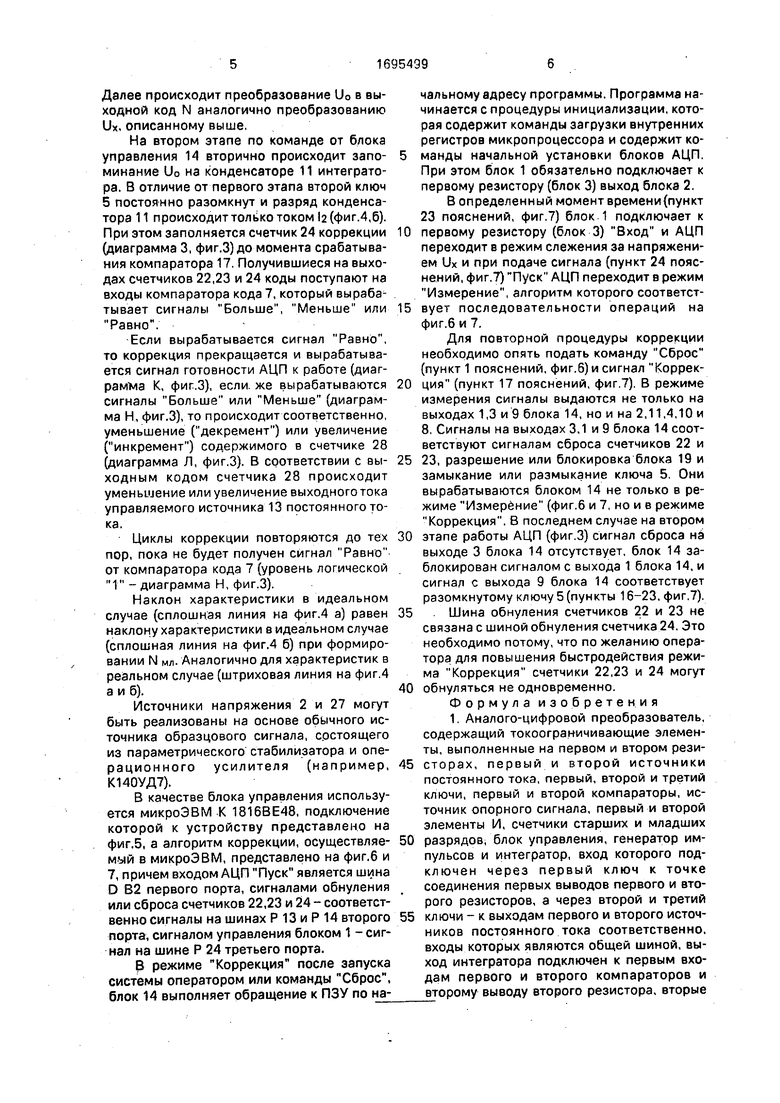

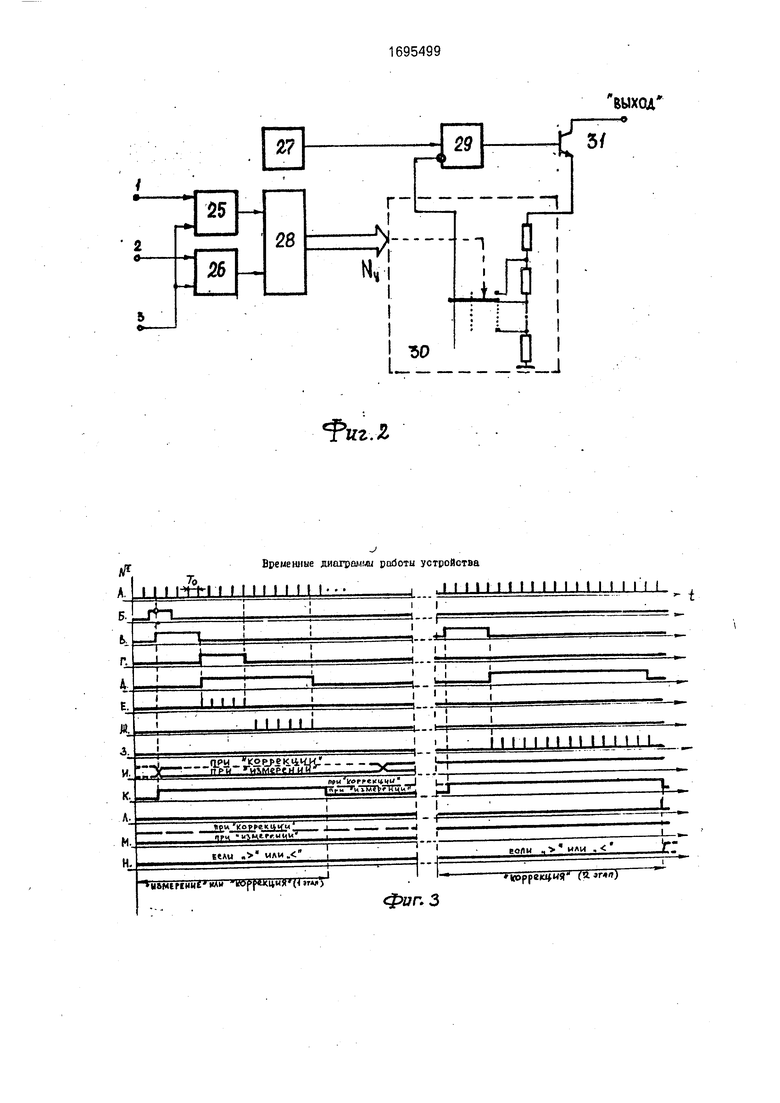

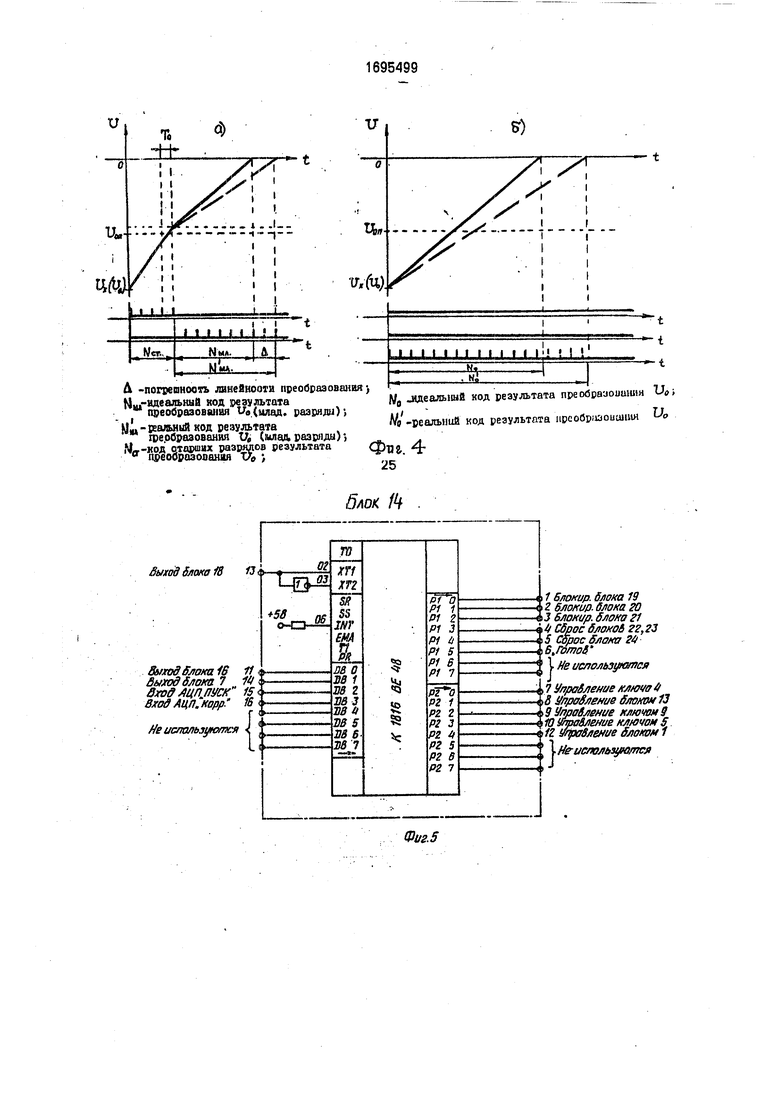

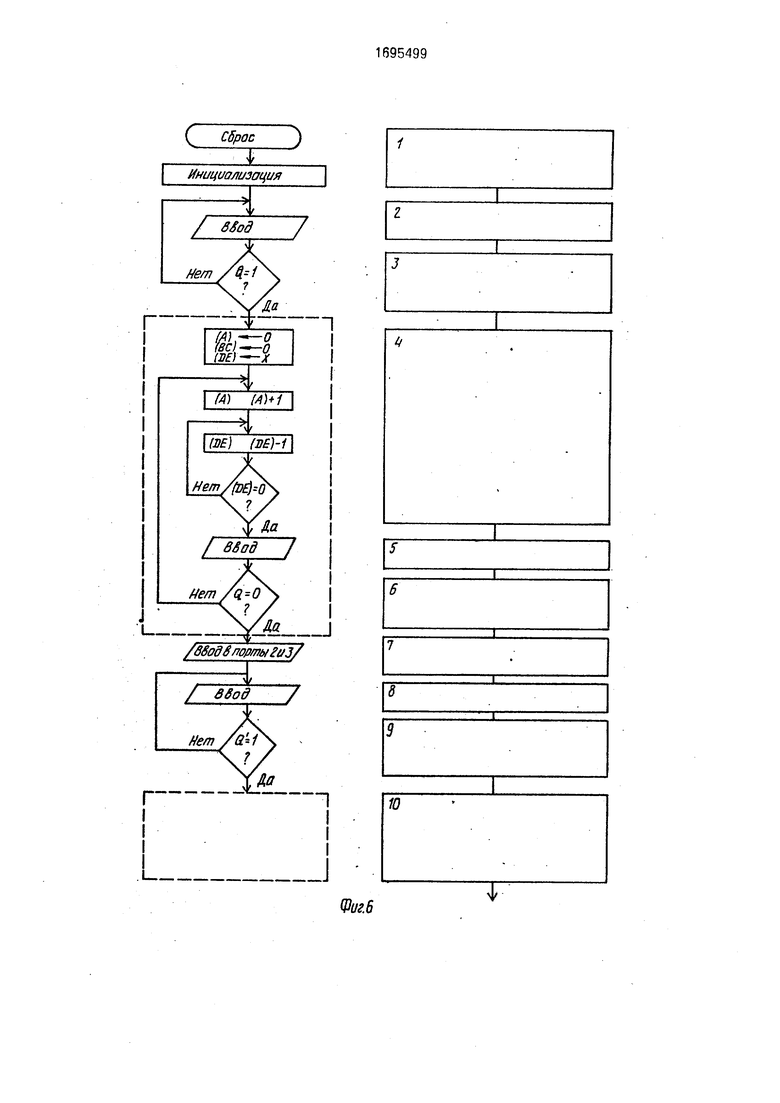

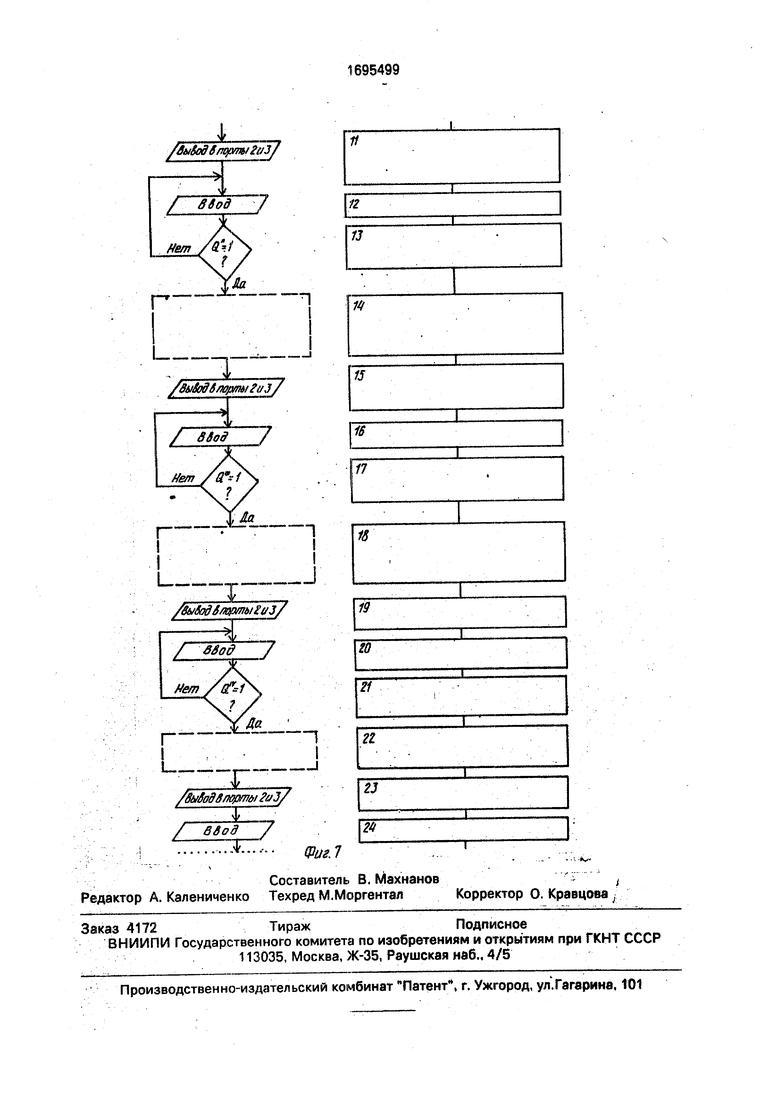

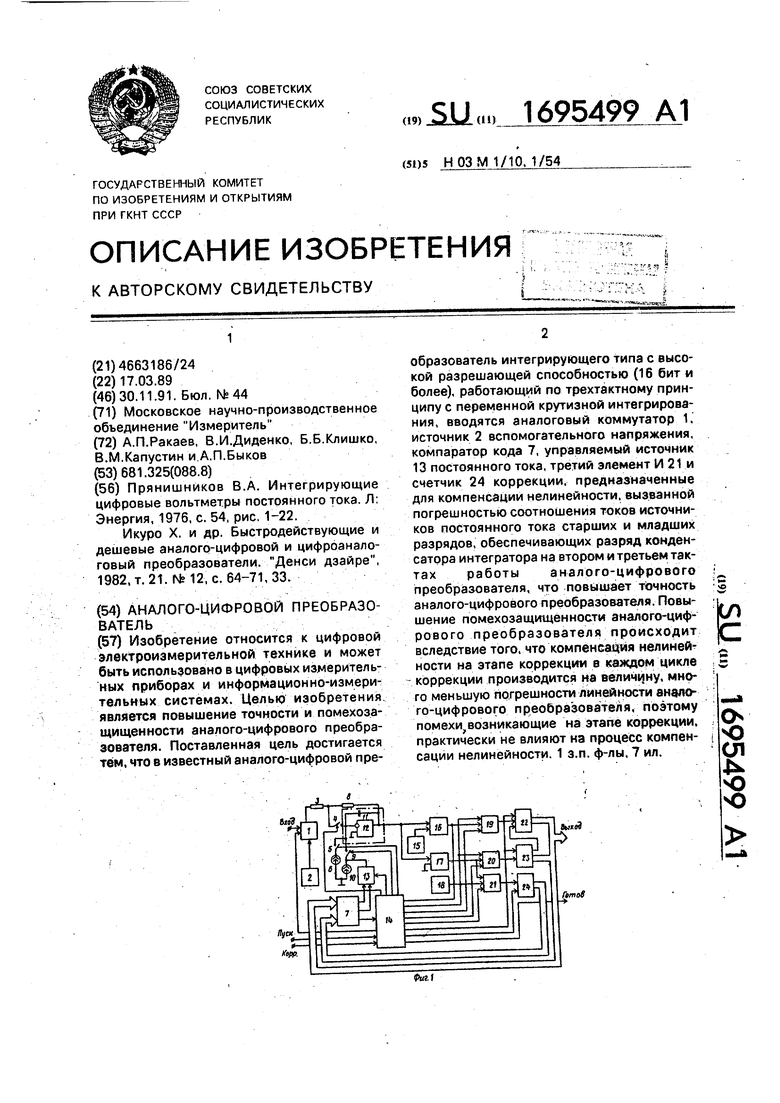

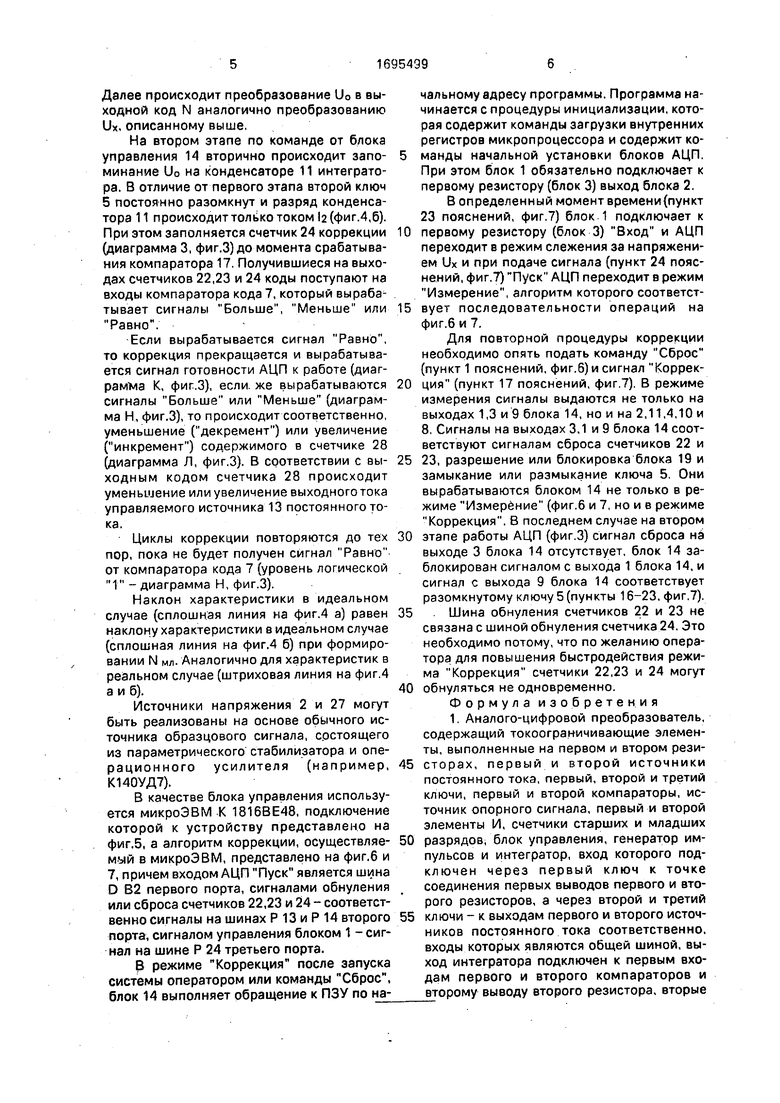

На фиг,1 представлено устройство, блок-схема; на фиг.2 - управляемый источник постоянного тока, вариант схемы; на фиг.З - временные диаграммы работы предлагаемого АЦП; на фиг.4 - то же выходного напряжения интегратора, где а - в режиме первого этапа коррекции, б - в режиме второго этапа коррекции; на фиг.5 - пример использования в качестве блока управления - микроЭВМ; на фиг.б и 7 - алгоритм, блок- схема.

Аналого-цифровой преобразователь (АЦП) содержит (фиг. 1) аналоговый коммутатор 1, источник 2 вспомогательного напряжения, первый резистор 3, первый и второй ключи 4 и 5, первый источник 6 постоянного тока, компаратор кода 7, второй резистор 8, третий ключ 9, второй источник 10 постоянного тока, конденсатор 11 и операционный усилитель 12, образующие интегратор, управляемый источник 13 постоянного тока, блок 14 управления, источник 15 опорного напряжения, первый и второй компараторы 16и,17, генератор импульсов 18, первый 19, второй 20 и третий 21 элементы И, счетчик 22 старших разрядов, счетчик 23 младших разрядов, счетчик 24 коррекции.

Вариант схемы (фиг.2) управляемого источника 13 постоянного тока содержит элементы И 25 и 26, источник 27 дополнительного напряжения, реверсивный счетчик 28, операционный усилитель

29,преобразователь кода в сопротивление

30,транзистор 31.

АЦП работает следующим образом.

По команде Пуск (диаграмма Б, фиг.З) происходит обнуление счетчиков 22,23 и 24, и аналоговый коммутатор 1 подключает Ux на вход АЦП (диаграмма И, фиг.З). После этого замыкается первый ключ 4 (диаграмма В, фиг.З) и происходит запоминание на конденсаторе 11 интегратора измеряемого напряжения 1)х(при равенстве сопротивлений резисторов 3 и 8).

Затем по команде блока управления 14 (диаграммы Г и Д, фиг.З) замыкается второй 5 и третий 9 ключи, и начинается разряд конденсатора 11 (фиг.4а) первым 6 и вторым 10 источниками постоянного тока до срабатывания первого компаратора 16. После срабатывания первого компаратора 16 по истечении текущего периода тактовой частоты происходит размыкание второго ключа 5.

Остаточное напряжение DOCT на конденсаторе 11 равно

I ,Net to f i , | ч

ост UxQ( 11 + 2 ) ,

причем UOCT Uon,

где li и 2 - токи первого и второго источников постоянного тока 6 и 10 (обычно выбирают И la);

NCT - код старших разрядов - число импульсов, прошедших на счетчик 22 (диаграм- ма Е, фиг.З);

t0 - период тактовой частоты (диаграмма А, фиг.З);

С - емкость конденсатора 11; Don - выходное напряжение источника 15 опорного напряжения.

Дальнейший разряд конденсатора происходит только с помощью второго источника 10 тока,при этом число импульсов ЫМл, прошедших на счетчик 23, равно (диаграмма Ж, фиг.З):

Ммл

UOCT

h to

Вариант реализации 16 разрядного

АЦП на основе данного принципа. Выбирается соотношение токов первого и второго источников постоянного тока как (29 - 1): 1 или И Ла 511. В этом случае счетчик 22

вырабатывает 7 старших разрядов, а счетчик 23-9 младших разрядов выходного кода АЦП (N).

При переполнении счетчика 23 происходит перенос в счетчик 22 и погрешность не

возникает. Точность отношения токов должна быть не хуже величины 210 (±0,1 %) с тем, чтобы погрешность линейности, вызванная этим, не превышала половины единицы младшего значащего разряда АЦП. Обеспечить такую точность соотношения токов для 16 разрядных АЦП на практике затруднительно, а для 17 и более разрядных на современном уровне развития технологии невозможно.

в данном устройстве для достижения требуемой точности соотношения токов h и Iz используется коррекция функции преобразования, состоящая из двух этапов.

После подачи сигнала Коррекция (диаграмма М, фиг.З) на первом этапе по команде от блока управления 14 аналоговый коммутатор 1 подает на вход АЦП вместо Ux выходное- напряжение U0 источника 2 вспомогательного напряжения, причем U0 U0.

Далее происходит преобразование U0 в выходной код N аналогично преобразованию Ux, описанному выше,

На втором этапе по команде от блока управления 14 вторично происходит запоминание Uo на конденсаторе 11 интегратора. В отличие от первого этапа второй ключ 5 постоянно разомкнут и разряд конденсатора 11 происходит только током 2(фиг.4,б). При этом заполняется счетчик 24 коррекции (диаграмма 3, фиг.З) до момента срабатывания компаратора 17. Получившиеся на выходах счетчиков 22,23 и 24 коды поступают на входы компаратора кода 7, который вырабатывает сигналы Больше, Меньше или Равно.

Если вырабатывается сигнал Равно, то коррекция прекращается и вырабатывается сигнал готовности АЦП к работе (диаг- рамтма К, фиг.З), если же вырабатываются сигналы Больше или Меньше (диаграмма Н, фиг.З), то происходит соответствен но, уменьшение (декремент) или увеличение (инкремент) содержимого в счетчике 28 (диаграмма Л, фиг.З), В соответствии с выходным кодом счетчика 28 происходит уменьшение или увеличение выходного тока управляемого источника 13 постоянного тока.

Циклы коррекции повторяются до тех пор, пока не будет получен сигнал Равно от компаратора кода 7 (уровень логической 1 - диаграмма Н, фиг.З).

Наклон характеристики в идеальном случае (сплошная линия на фиг.4 а) равен наклону характеристики в идеальном случае (сплошная линия на фиг,4 б) при формировании N Мл. Аналогично для характеристик в реальном случае (штриховая линия на фиг.4 а и б).

Источники напряжения 2 и 27 могут быть реализованы на основе обычного источника образцового сигнала, состоящего из параметрического стабилизатора и операционного усилителя (например, К140УД7).

В качестве блока управления используется микроЭВМ К 1816ВЕ48, подключение которой к устройству представлено на фиг.5, а алгоритм коррекции, осуществляемый в микроЭВМ, представлено на фиг.6 и 7, причем входом АЦП Пуск является шина D B2 первого порта, сигналами обнуления или сброса счетчиков 22,23 и 24 - соответственно сигналы на шинах Р 13 и Р 14 второго порта, сигналом управления блоком 1 -сигнал на шине Р 24 третьего порта.

В режиме Коррекция после запуска системы оператором или команды Сброс, блок 14 выполняет обращение к ПЗУ по начальному адресу программы, Программа начинается с процедуры инициализации, которая содержит команды загрузки внутренних регистров микропроцессора и содержит команды начальной установки блоков АЦП, При этом блок 1 обязательно подключает к первому резистору (блок 3) выход блока 2,

В определенный момент времени(пункт 23 пояснений, фиг.7) блок 1 подключает к

0 первому резистору (блок 3) Вход и АЦП переходит в режим слежения за напряжением Ux и при подаче сигнала (пункт 24 пояснений, фиг.7) Пуск АЦП переходит в режим Измерение, алгоритм которого соответст5 вует последовательности операций на фиг.6 и 7.

Для повторной процедуры коррекции необходимо опять подать команду Сброс (пункт 1 пояснений, фиг.6) и сигнал Коррек0 ция (пункт 17 пояснений, фиг.7). В режиме измерения сигналы выдаются не только на выходах 1,3 и 9 блока 14, но и на 2,11,4,10 и 8. Сигналы на выходах 3,1 и 9 блока 14 соответствуют сигналам сброса счетчиков 22 и

5 23, разрешение или блокировка блока 19 и замыкание или размыкание ключа 5. Они вырабатываются блоком 14 не только в режиме Измерение (фиг.6 и 7, но и в режиме Коррекция. В последнем случае на втором

0 этапе работы АЦП (фиг.З) сигнал сброса на выходе 3 блока 14 отсутствует, блок 14 заблокирован сигналом с выхода 1 блока 14, и сигнал с выхода 9 блока 14 соответствует разомкнутому ключу 5 (пункты 16-23, фиг.7).

5 Шина обнуления счетчиков 22 и 23 не связана с шиной обнуления счетчика 24. Это необходимо потому, что по желанию оператора для повышения быстродействия режима Коррекция счетчики 22,23 и 24 могут

0 обнуляться не одновременно.

Формула изобретения 1. Аналого-цифровой преобразователь, содержащий токоограничивающие элементы, выполненные на первом и втором рези5 сторах, первый и второй источники постоянного тока, первый, второй и третий ключи, первый и второй компараторы, источник опорного сигнала, первый и второй элементы И, счетчики старших и младших

0 разрядов, блок управления, генератор импульсов и интегратор, вход которого подключен через первый ключ к точке соединения первых выводов первого и второго резисторов, а через второй и третий

5 ключи - к выходам первого и второго источников постоянного тока соответственно, входы которых являются общей шиной, выход интегратора подключен к первым входам первого и второго компараторов и второму выводу второго резистора, вторые

входы первого и второго компараторов подключены соответственно к выходу источника опорного напряжения и общей шине, выход первого компаратора подключен к первому входу первого элемента И, выход второго компаратора - к первому входу второго элемента И, вторые входы элементов И соединены с выходом генератора импульсов, третьим входы - с первым и вторым выходами блока управления, соответственно, выход переноса счетчика младших разрядов соединен с первым входом счетчика старших разрядов, выход первого элемента И подключен к второму входу счетчика старших разрядов, выход второго элемента И подключен к первому входу счетчика младших разрядов, третий выход блока управления подключен к третьему входу счетчика старших разрядов и второму входу счетчика младших разрядов, соответственно, а четвертый выход- к входу управления первого ключа, а выходы счетчиков старших и младших разрядов являются выходной шиной, отличающийся тем, что, с целью повышения точности преобразователя, в него введены источник вспомогательного напряжения, третий элемент И, счетчик коррекции, компаратор кода, управляемый источник постоянного тока и аналоговый коммутатор, первый информационный вход которого является входной шиной, а выход - подключен к второму выводу первого резистора, второй информационный вход аналогового коммутатора подключен к выходу источника вспомогательного напряжения, выход генератора импульсов соединен с первым входом третьего элемента И, выход второго компаратора соединен с вторым входом третьего элемента И, выход которого соединен с первым входом счетчика коррекции, выходы которого подключены к соответствующим первым входам компаратора кода, вторые входы которого являются выходной шиной, а первый и второй выходы компаратора кода подключены соответственно к первому и второму входам управляемого источника постоянного тока, выход которого соединен с выходом второго источника постоянного тока, пятый, шестой, седьмой, восьмой, девятый и десятый выходы

блока управления соединены соответственно с третьим входом третьего элемента И, с вторым входом счетчика коррекции, с треть1 им входом управления источника постоянного тока, с входом управления аналоговым

коммутатором, с входами управления второго и третьего ключей, одиннадцатый выход является шиной готовности кода, а первый, второй и третий входы блока управления соединены соответственно с выходом первого компаратора, третьим выходом компаратора кода и выходом генератора импульсов, четвертый и пятый входы являются соответственно шиной пуска и коррекции.

2, Преобразователь по п. 1, от л и ч а ю- щ и и с я тем, что, с целью повышения помехозащищенности преобразователя, управляемый источник постоянного тока выполнен на источнике дополнительного

напряжения, реверсивном счетчике, операционном усилителе, преобразователе кода в сопротивление, транзисторе и первом и втором элементах И, первые входы которых являются соответственно первым и вторым

входами блока, вторые входы - объединены и являются третьим входом блока, выход первого элемента И подключен к входу Декремент, а выход второго элемента И - к входу Инкремент реверсивного счетчика,

выход источника дополнительного напряжения соединен с неинвертирующим входом операционного усилителя, инвертирующий вход которого объединен с первым входом преобразователя кода в

сопротивление, второй вход которого соединен с выходом реверсивного счетчика, выход операционного усилителя соединен с базой транзистора, эмиттер которого подключен к третьему входу преобразователя кода в сопротивление, а выходом блока является коллектор транзистора.

выход

| название | год | авторы | номер документа |

|---|---|---|---|

| Измерительный преобразователь для тензорезисторных весоизмерительных устройств | 1990 |

|

SU1830463A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1132357A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1200421A1 |

| Аналого-цифровой преобразователь с автоматической коррекцией функции преобразования | 1988 |

|

SU1667246A1 |

| Аналого-цифровой преобразователь с промежуточным преобразованием в частоту | 1987 |

|

SU1441479A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1181144A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU884127A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДЕЙСТВИЯ | 2003 |

|

RU2245000C2 |

| Интегрирующий аналого-цифровой преобразователь | 1985 |

|

SU1279069A1 |

| Цифроаналоговый преобразователь | 1987 |

|

SU1538254A1 |

Изобретение относится к цифровой электроизмерительной технике и может быть использовано в цифровых измерительных приборах и информационно-измерительных системах. Целью изобретения является повышение точности и помехозащищенности аналого-цифрового преобразователя. Поставленная цель достигается тем, что в известный аналого-цифровой преобразователь интегрирующего типа с высокой разрешающей способностью (16 бит и более), работающий по трехтактному принципу с переменной крутизной интегрирования, вводятся аналоговый коммутатор 1. источник 2 вспомогательного напряжения, компаратор кода 7, управляемый источник 13 постоянного тока, третий элемент И 21 и счетчик 24 коррекции, предназначенные для компенсации нелинейности, вызванной погрешностью соотношения токов источников постоянного тока старших и младших разрядов, обеспечивающих разряд конденсатора интегратора на втором и третьем тактах работы аналого-цифрового преобразователя, что повышает точность аналого-цифрового преобразователя. Повышение помехозащищенности аналого-цифрового преобразователя происходит вследствие того, что компенсация нелинейности на этапе коррекции в каждом цикле коррекции производится на величину, много меньшую погрешности линейности аналого-цифрового преобразователя, поэтому помехи возникающие на этапе коррекции, практически не влияют на процесс компенсации нелинейности. 1 з.п. ф-лы, 7 ил. у Ј О Ч 2 чэ о Фиг.1

uz.Z

J

KI.

- J-iti

Т

l

7

Ц.---Mer,

1 I I I I i I «

NMA.

t Ч

Mm.

Л -погрешность линейности преобразования-, .„„mum U/,

N -ВДеашшй код результатаМ0 -ВДеалышй код результата преоврвэошшня U.,

преобразования 1Ге(илад. разряди)

У-.-реальный код результата

грербразования U, (ьлал разряды), М--код старших разрядов результата а преобразооания V0 ,

Л/д -реаяышй код результата ирсобршоиании У

Фиг. 4

А//Й блока 18 Я i

Выход Влока 1В 11, Выход 6л ока 7 Ш Вхо9АЦП.ПУСК Вход Ацп. корр.

Не используются

V,(4).e

М0 -ВДеалышй код результата преоврвэошшня U.,

Л/д -реаяышй код результата ирсобршоиании У

Фиг. 4

5/10Х / .

1 Блокир. блока 19 2 блокир. блока го J блокир. блока 21 Ц Сброс SJIOKD& 22,23 5 Сорос S/iaxa 24 Б So/not

Не используются

7 Улрабление мюча 6 S Управление едоком 13 9 Управление ключом $ Ю Управление ключом 5 К Управление Злаком 1

Неиспользуются

| Прянишников В.А | |||

| Интегрирующие цифровые вольтметры постоянного тока | |||

| Л: Энергия, 1976 | |||

| с | |||

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Икуро X | |||

| и др | |||

| Быстродействующие и дешевые аналого-цифровой и цифроанало- говый преобразователи | |||

| Денси дзайре, 1982, т | |||

| Выбрасывающий ячеистый аппарат для рядовых сеялок | 1922 |

|

SU21A1 |

| Способ гальванического снятия позолоты с серебряных изделий без заметного изменения их формы | 1923 |

|

SU12A1 |

| Нефтяной конвертер | 1922 |

|

SU64A1 |

Авторы

Даты

1991-11-30—Публикация

1989-03-17—Подача