(54) УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА КОДОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема и передачи кодов | 1976 |

|

SU738187A1 |

| Селектор-преобразователь импульсных сигналов | 1981 |

|

SU966879A1 |

| Оконечное телеграфное передающее устройство | 1979 |

|

SU879807A2 |

| Генератор кода морзе | 1977 |

|

SU750750A2 |

| ВСЕСОЮЗНАЯ . | 1973 |

|

SU370737A1 |

| Автоматизированный передатчик телеграфных сообщений | 1978 |

|

SU1312752A1 |

| Система передачи дискретной информации с решающей обратной связью | 1983 |

|

SU1111258A1 |

| Устройство для передачи дискретных сигналов | 1981 |

|

SU978379A1 |

| Селектор импульсов | 1979 |

|

SU871325A2 |

| Селектор-преобразователь импульсныхСигНАлОВ | 1979 |

|

SU849469A1 |

1

Изобретение относится к радиотехнике и может использоваться для приема и передачи сообщений произвольными кодами по каналам проводной связи и радиосвязи.

Известно устройство для передачи и приема кодов, содержащее оконечный согласующий блок, усилитель и последовательно соединенные генератор импульсов и первый элемент ЗАПРЕТ, ко второму входу которого подключен первый выход стартстопного триггера, второй выход которого соединен со входами клавиатурного блока, выходы которого подключены ко входам щифратора, выходы которого соединены со входами первого коммутатора, при этом выход приемника подключен к первым входам второго элемента ЗАПРЕТ и основного элемента ИЛИ, выход которого соединен с первым входом стартстопного триггера, а выход первого элемента ЗАПРЕТ подключен ко входу распределителя I.

Однако известное устройство не обеспечивает высокую помехоустойчивость передачи и приема кодовых сообщений.

Цель изобретения - повышение помехоустойчивости.

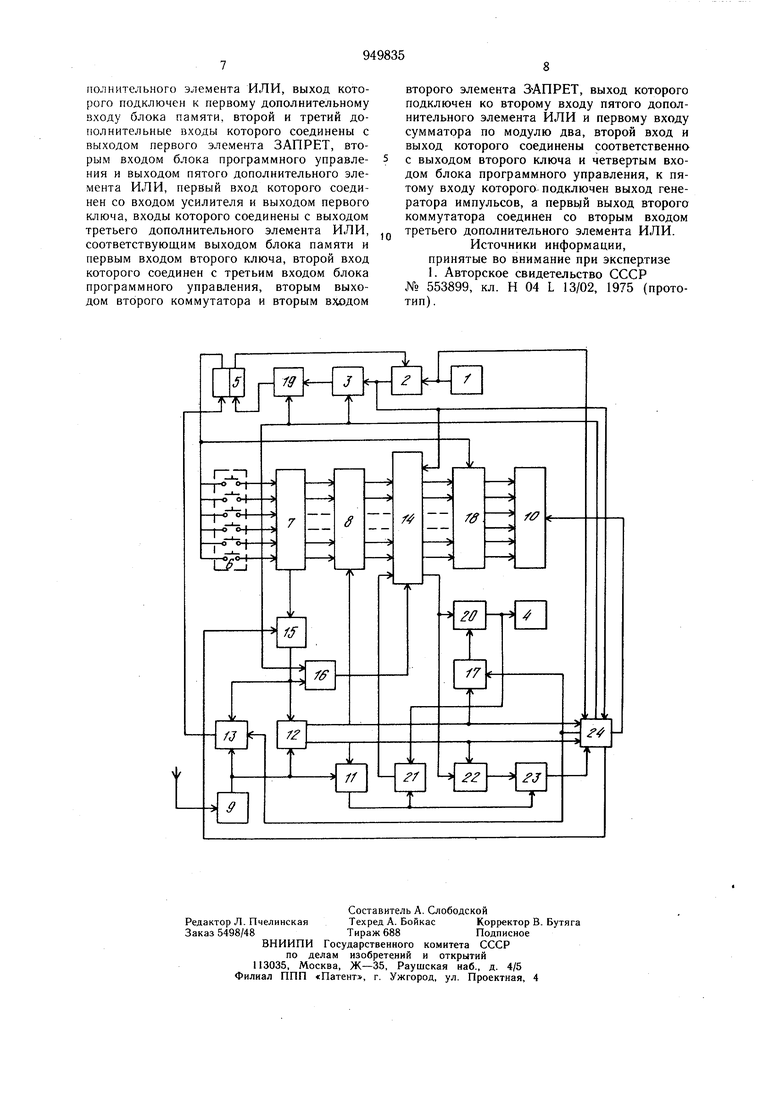

Для достижения поставленной цели в устройство для передачи и приема кодов, содержащее оконечный согласующий блок, усилитель и последовательно соединенные генератор импульсов и первый элемент ЗАПРЕТ, ко второму входу которого подключен первый выход стартстопного триггера, второй выход кото| ого соединен со входами клавиатурного блока, выходы которого подключены ко входам шифратора, 10 выходы которого соединены со входами первого коммутатора, при этом выход приемника подключен к первым входам второго элемента ЗАПРЕТ и основного элемента ИЛИ, выход которого соединен с первым входом стартстопного триггера, а выход первого элемента ЗАПРЕТ подключен ко входу распределителя, введены блок памяти, дешифратор, пять дополнительных элементов ИЛИ, два ключа, второй коммутатор сумматор по модулю два и блок программного го управления, выходы которого подключены к управляющему входу оконечного согласующего блока, первым входам первого второго и третьего дополнительных элементов ИЛИ, второму входу основного элемента ИЛИ, управляющему входу распределителя и первому входу четвертого дополнительного элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом распределителя и вторым входом стартстопного триггера, второй выход которого подключен к управляющему входу дещифратора, информационные выходы и входы которого соединены соответственно со входами оконечного согласующего блока и выходами блока памяти, ко входам которого подключены выходы первого коммутатора, дополнительный вход которого соединен с первым входом блока программного управления и первым выходом второго коммутатора, входы которого соединены с выходом приемника, третьим входом основного элемента ИЛИ, выходом первого дополнительного элемента ИЛИ, ко второму входу которого подключен соответствующий выход шифратора, и вторым входом второго дополнительного элемента ИЛИ, выход которого подключен к первому дополнительному входу блока памяти, второй и третий дополнительные входы которого соединены с выходом первого элемента ЗАПРЕТ, вторым входом блока программного управления и выходом пятого дополнительного элемента ИЛИ, первый вход которого соединен со входом усилителя и выходом первого ключа, входы которого соединены с выходом третьего дополнительного элемента ИЛИ, соответствующим выходом блока памяти и первым входом второго ключа, второй вход которого соединен с третьим входом блока программного управления, вторым выходом второго коммутатора и вторым входом второго элемента ЗАПРЕТ, выход которого подключен ко второму входу пятого дополнительного элемента ИЛИ и первому входу сумматора по модулю два, второй вход и выход которого соединен соответственно с выходом второго ключа и четвертым входом блока программного управления, к пятому входу которого подключен выход генератора импульсов, а первый выход второго коммутатора соединен со вторым входом третьего дополнительного элемента ИЛИ. На чертеже изображена структурная электрическая схема предлагаемого устройства. Устройство для передачи и приема кодов содержит генератор 1 импульсов, первый элемент ЗАПРЕТ 2, распределитель 3, усилитель 4, стартстопный триггер 5, клавиатурный блок 6, щифратор 7, первый коммутатор 8, приемник 9, оконечный согласующий блок 10, второй элемент ЗАПРЕТ 11, второй коммутатор 12, основной элемент ИЛИ 13, блок 14 памяти, первый дополнительный элемент ИЛИ 15, второй дополнительный элемент ИЛИ 16, третий дополнительный элемент ИЛИ 17, дешифратор 18, четвертый дополнительный элемент ИЛИ 19, первый ключ 20, пятый дополнительный элемент ИЛИ) 21, второй ключ 22, сумматор 23 по модулю два и блок 24 программного управления. Устройство работает следующим образом. При передаче оператор воздействует на клавиатурный блок б, что обеспечивает появление на дополнительном выходе шифратора 7 сигнала, включающего второй коммутатор 12 через первый дополнительный элемент ИЛИ 15 в положение, при котором отпирается первый коммутатор 8 и первый ключ 20 через третий дополнительный элемент ИЛИ 17, запирается приемный вход пятого дополнительного элемента ИЛИ 21 и сумматора 23 по модулю два из-за срабатывания , второго элемента ЗАПРЕТ 11 и осуществляется переключение на передачу программы блока 24. Этот же сигнал поступает на установочный- вход блока 14 через второй дополнительный элемент ИЛИ 16 и подготавливает блок 14 для записи информации и на один из входов основного элемента ИЛИ 13, который включает стартстопный триггер 5. Последнний отключает первый элемент ЗАПРЕТ 2, и импульсы генератора 1 поступают на распределитель 3 и тактовый вход блока 14. Воздействие оператора на клавиатурный блок 6 представляется посредством шифратора 7 в виде определенной комбинации, значения разрядов которой через первый коммутатор 8 записываются в соответствующие ячейки блока 14. Под действием импульсов, подаваемых с первого элемента ЗАПРЕТ 2 на тактовый вход блока 14, комбинация, записанная в блок 14, выводится поразрядно на передачу через первый ключ 20, усилитель 4 и далее на выход устройства. При выводе информации из блока 14 производится перезапись значений разрядов передаваемой комбинации в блоке 14 по входу последовательного ввода информации через первый ключ 20 и пятый дополнительный элемент ИЛИ 21. После передачи всех разрядов сформированной шифратором 7 комбинации распределитель 3 вырабатывает сигнал, который через четвертый дополнительный элемент ИЛИ 19 воздействует на стартстопный триггер 5 и переводит устройство в режим дежурного приема. Блок 24 по сигналам генератора 1, первого элемента ЗАПРЕТ 2 и второго коммутатора 12 вырабатывает в соответствии с заданной программой сигналы на повторение передачи, подаваемые на второй вход первого дополнительного, элемента ИЛИ 15, либо сигнал отсутствия обмена, воспроизводимый на блоке 24. Временное положение сигнала на повторение передачи определяется по импульсам, подаваемым с генератора 1, и может быть

задано программой из соображений декорреляции ошибок.

При приеме сигнал с приемника 9 поступает одновременно на второй коммутатор 12, второй элемент ЗАПРЕТ 11 и на один из входов основного элемента ИЛИ 13, который включает стартстопный триггер 5. Последний отключает первый элемент ЗАПРЕТ 2, и импульсы генератора 1 поступают на распределитель 3 и тактовый вход блока 14. Второй коммутатор 12 включается в положение, при котором запирается первый коммутатор 8 и первый ключ 20 и отпирается второй элемент ЗАПРЕТ 11 и второй ключ 22 и переключается на прием программа блока 24. Отпирание второго элемента ЗАПРЕТ И обеспечивает прохождение принимаемой информации на запись в блок 14 по входу последовательного ввода информации через пятый дополнительный элемент ИЛИ 21 и на сумматор 23 по модулю два. На второй вход сумматора 23 по модулю два поступает информация из блока 14 через второй ключ 22. В сумматоре 23 по модулю два проводится контроль принимаемой информации и формирование сигналов несоответствия при несоответствии информации на его входах. Сигналы несоответствия подаются на блок 24, который в соответствии с ними и программой приема в соответствующих разрядах принимаемой комбинации вырабатывает сигнал начальной установки, подаваемый на распределитель 3, стартстопный триггер 5 через четвертый дополнительный элемент ИЛИ 19 и блок 14 через третий дополнительный элемент ИЛИ 16.

При отсутствии контролируемых сигналов несоответствия процесс приема длится до выработки сигнала распределителем 3, по которому стартстопный триггер 5 устанавливается в исходное состояние через четвертый дополнительный элемент ИЛИ 19. Стартстопный триггер 5 запрещает работу распределителя 3 и разрешает работу дешифратора 18, который дещифрирует записанную при приеме в блок 14 комбинацию и подает ее на оконечный согласующий блок 10. Оконечный согласующий блок 10 воспроизводит получателю принятую информацию при наличии разрешающего сигнала с блока 24, вырабатываемого им по сигналам с выхода первого элемента ЗАПРЕТ 2. В соответствии с заданной программой приема блок 24 вырабатывает сигнал на выдачу квитанции, запускающей стартстопный триггер 5 через основной элемент ИЛИ 13 и открывающей первый ключ 20 через третий дополнительный элемент ИЛИ 17 либо просто сигнал наличия обмена, воепроизводимый на блоке 24. Время выдачи квитанции устанавливается программой из соображений декорреляции ошибок.

Введение в устрой(тво блока 14, сумматора 23 по модулю два первого и второго ключей 20 и 22, дешифратора 18, блока 24 и логических элементов, связывающих их с остальными элементами, а также наличие изменяемых программ приема и передачи сообщений в блоке 24 позволяет повысить его помехоустойчивость, способствует рациональному введению избыточности в сообщение, увеличению скорости передачи и приема, адаптации устройства к конкретным условиям работы.

Формула изобретения

Устройство для передачи и приема кодов, содержащее оконечный согласующий блок, усилитель и последовательно соединенные генератор импульсов и первый элемент ЗАПРЕТ, ко второму входу которого подключен первый выход стартстопного триггера, второй выход которого соединен со входами клавиатурного блока, выходы которого подключены ко входам шифратора, выходы которого соединены со входами первого коммутатора, при этом выход приемника подключен к первым входам второго элемента ЗАПРЕТ и основного элемента ИЛИ, выход которого соединен с первым входом стартстопного триггера, а выход первого элемента ЗАПРЕТ подключен ко входу распределителя, отличающееся тем, что, с целью повышения помехоустойчивости, в него введены блок памяти, дещифратор, пять дополнительных элементов ИЛИ, два ключа, второй коммутатор, сумматор по модулю два и блок программного управления, выходы которого подключены к управляющему входу оконечного согласующего блока, первым входам первого, второго и третьего дополнительных элементов ИЛИ, второму входу основного элемента ИЛИ, управляющему входу распределителя и первому входу четвертого дополнительного элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом распределителя и вторым входом стартстопного триггера, второй выход которого подключен к управляющему входу дешифратора, информационные выходы и входы которого соединены соответственно со входами оконечного согласующего блока и выходами блока памяти, ко входам которого подключены выходы первого коммутатора, дополнительный вход которого соединен с первым входом блока программного управления и первым выходом второго коммутатора, входы которого соединены с выходом приемника, третьим входом основного элемента ИЛИ, выходом первого дополнительного элемента ИЛИ, ко второму входу которого подключен соответствующий выход шифратора, и вторым входом второго дополнительного элемента ИЛИ, выход которого подключен к первому дополнительному входу блока памяти, второй и третий дополнительные входы которого соединены с выходом первого элемента ЗАПРЕТ, вторым входом блока программного управления и выходом пятого дополнительного элемента ИЛИ, первый вход которого соединен со входом усилителя и выходом первого ключа, входы которого соединены с выходом третьего дополнительного элемента ИЛИ, соответствующим выходом блока памяти и первым входом второго ключа, второй вход которого соединен с третьим входом блока программного управления, вторым выходом второго коммутатора и вторым входом

второго элемента 3-АПРЕТ, выход которого подключен ко второму входу пятого дополнительного элемента ИЛИ и первому входу сумматора по модулю два, второй вход и выход которого соединены соответственно с выходом второго ключа и четвертым входом блока программного управления, к пятому входу которого подключен выход генератора импульсов, а первь1Й выход второго коммутатора соединен со вторым входом третьего дополнительного элемента ИЛИ.

Источники информации, принятые во внимание при экспертизе I. Авторское свидетельство СССР № 553899, кл. Н 04 L 13/02, 1975 (прототип) .

Авторы

Даты

1982-08-07—Публикация

1978-09-04—Подача