(54) СЕЛЕКТОР ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема и передачи кодов | 1976 |

|

SU738187A1 |

| УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ РЕЧЕВОЙ ИНФОРМАЦИИ | 1992 |

|

RU2008728C1 |

| Устройство для передачи и приема кодов | 1978 |

|

SU949835A1 |

| Система коммутации | 1985 |

|

SU1317448A1 |

| Селектор-преобразователь импульсных сигналов | 1981 |

|

SU966879A1 |

| Устройство для отображения информации на экране матричной индикаторной панели | 1982 |

|

SU1115090A1 |

| Оперативное запоминающее устройство | 1981 |

|

SU970462A1 |

| Устройство для обнаружения и регистрациипОТОКА ОшибОК диСКРЕТНОгО КАНАлА СВязи | 1979 |

|

SU836804A2 |

| Устройство для ввода информации | 1983 |

|

SU1149236A1 |

| ПРИБОР ДЛЯ ИЗМЕРЕНИЯ ПАРАМЕТРОВ ПАРАЗИТНЫХ ИМПУЛЬСНЫХ ВОЗМУЩЕНИЙ В СЕТЯХ ЭЛЕКТРОПИТАНИЯ С ПЕРЕМЕННЫМ НАПРЯЖЕНИЕМ | 2002 |

|

RU2239201C2 |

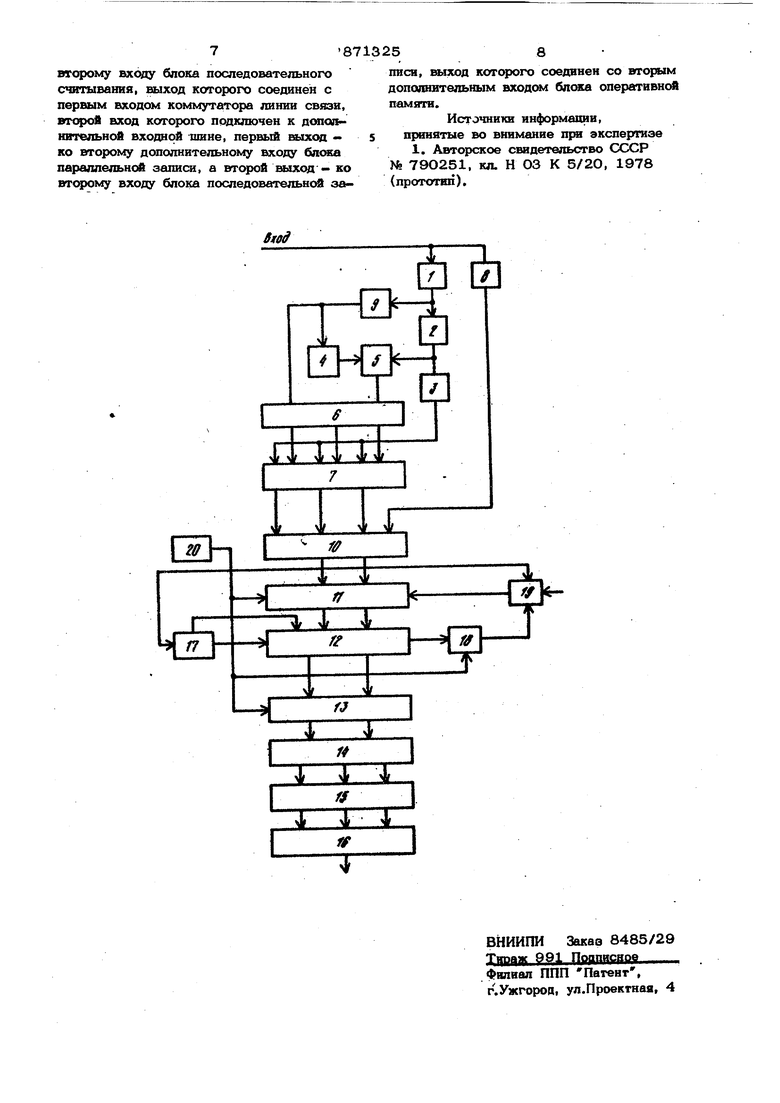

/ Изобретение относится чс измеритель- ной технике и может быть использовано для анализа различных сигналов, а также в качестве средства приема и передачи информации в Ш1ФРОВОЙ форме. В основном изобретении авт. св. № 790251 описан сенектор импульсов, содержащий генератор импульсов, последо вательно соединенные блок укорочения входных импульсов, инвертор и дифференхшруюший элемент, выход которого соедииен с первыми входами элементов совпадения, выходы которых подключены к выходным шинам устройства, распределитель сигналов, выходы которого соединены соответственно со вторыми входами элементов совпадения, вентиль, выход которого подключен к первому входу распределите- ля сигналов, а входы соответственно - к выходам генератора импулыЛв а инвертора, и синхронизатор, вход которого сое динен со шсодом инвертора, а выход с .синхронизирующими входами рас1федвлите ля сигналов и генератора импульсовЩНедостатком этого устройства является п -канальная форма выходного сигнала, требующая дополнительных устройств преобразования для передачи этого сигнала Б обычных каналах связи. Кроме того, известное устройство, осушестбпяя разложение сигнала цо каналам, не обеспечивает восстановления сигнала. Целью настоящего изобретения является расширение функциональных возможиостей устройства путем обеспечения прямого и обратного преобразования сигаала в цифровую форму. Поставленная цель достигается тем, что в селектор импульсов, содержащий генератор импульсов, последовательно соединенные блок укорочения входных импульсов, инвертор и дифференцирующий элемент, выход которого соединен с первыми входами элементов соединения, распределитель сигналов, выходы которого соединены соответственно со вторыми входами элементов совпадения, вентиль, выход которого подключен к первому входу расрре- делителя сигналов, а входы соответствен- но - к выходам генератора импульсов и инвертора, и синхронизатор, вход которого соединен со входом инвертора, а выхо с синхронизирующими входами распределителя сигналов и генератора импульсов, введены тактовый генератор, блок последовательной записи, блок последовательно го считывания, коммутатор линии связи, дополнительный инвертор, последовательно соединенные шифратор, блок параллельной записи, блок оперативной памяти, блок параллельного считывания, дешифратор, блок генераторов и сумматор. При этом входы шифратора подключены к выходам элементов совпадения, а дополнительный вход через дополнительный инвертор - ко входной шине, причём выход тактового генератора соединен с первьши входами блока последовательной записи и блока последовательного считывания, с дополнительным входом блока параллельного считывания, с первым дополнительным входом блока параллельной записи и с первым дополнительным входом блока оперативной памяти, дополнительный выход которого подключен ко второму входу блока последовательного считывания, выход которого соединен с первым входом коммутатора линии связи, второй вход которо- го подключен к дополнительной вхсйгной шине, первый выход - ко второму дополнительному входу блока параллельной записи, а второй выход - ко второму входу блока последовательной записи, выход ко торого соединен со вторым дополнительным входом блока оперативной памяти. На чертеже изображена структурная электрическая схема устройства. Устройство содержит последовательно соединенные блок 1 укорочения входных импульсов, инвертор 2 и дифференцир5юйшй элемент 3, генератор 4 импульсов, вентиль 5, входы которого подключены соответственно к выходам генератора 4 импульсов и инвертора 2, распределитель 6 сигналов, элементы 7 совпадения, первые входы которых соединены с выходом дифференцирующего элемента 3, а вторые входы - соответственно с выходами распределителя 6 сигналов, первый вход которого подключен к выходу вентиля 5, а второй вход - к синхронизирующему входу генератор 4 импульсов, дополнительный инвертор 8, синхронизатор 9, выход которого соединен с синхронизирующим входом генератора 4 импульсов, а вхоД - со входом инвертора 2, шифратор 1О,вхо ды которого соединены с выходами эле- ментов 7 совпадения, а дополнительный вход через дополнительный инвертор 8 со входной щиной, последовательно соединенные блок 11 параллельной записи,блок 12 оперативной памяти, блок 13 параллельного считывания, дешифратор 14, блок 15 генераторов и сумматор 16. Кроме того, устройство включает в себя блок 17 последовательной записи, блок 18 последовательного считывания, коммутатор 19 линии связи, тактовый генератор 2О, выход которого соединен с первыми входами блока 17 последовательной записи и блока 18 последовательного считывания, дополнительным входом блока 13 параллельного считывания, с первым дополнительным входом блока 11 параллельной записи и с первым дополнительным входом блока 12 оперативной памяти, дополнительный выход которого соединен со вторым входом блока 18 последовательного считывания, выход которого подключен к первому входу коммутатора 19 линии связи, второй вход которого соединен с дополнительной входной шиной, первый выход - со вторым дополнительным. входом блока 11 параллельной записи, а второй выход - со вторым входом блока 17 последовательной записи, выход которого подключен ко второму дополнительному входу блока 12 оперативной памяти. Дополнительная входная шина является линией связи. Устройство работает следуюпшм образом. Исследуемая последовательность HRiпульсов например, имитированная речь, по ступает на вход блока 1. Последний укорачивает до заданной минимальной длитель-. кости каждый входной импульс. Импульсы менее этой длительности не конт. ропируются и в дальнейшей работе не участвуют. Для импульсов с болыией длительностьк) сигнал разности входного и укороченного импульсов на выходе блока 1 инвертируется инвертором 2 и отпирает вентиль 5. Одновременно с началом этого сигнала, синхронизатор устанавливает в исходное состояние распределитель 6 и заданную фазу генератсфа 4. Импульсы с выхода последнего поступают через открытый вентиль 5 на вход распределителя 6, в результате чего на каждом из п выяо дов последнего появляются импуАьсы, вы- пслняюшие функцию перемещающегося интервала контроля, равного периоду Т работы генератора 4. По окончании упомянутого сигнала разности на выходе элемента 3 формируется импульс, поотупак 01ИЙ на входы элементов 7, в результате чего на одном из ц выходов элементов 7 регистрируется входной импульс, длительность которого,,

. Далее импульсы с выходов элементов :7 поступают на входы шифратора 10, на выходе которого формируется та или иная кодовая комбинация, распределенная по его выходным шинам и однозначно опре.делшошая измеренное значение длительнос ти входного импульса. Конкретное исподнекие шифратора 10, как и способ кодирования, зависит от желания потребителя, однако для наглядности описание работы устройства рассматривается на двоичной обработке информации. В этом случае чис ло N выходных шин 1О определяется известным выражением:. ), включая сигнал с выхода инвертора 8 и на его выходах формируется одна из статических кодовых комбинаций для каждого из измеренных входных импульсов и одна кодовая комбинация, соответст- вуюшая паузе между импульсами. Этот статический N -разряаный сигнал с выходов шифратора 1О поступает на блок 11, а оггтуда на входы блока 12, который в данном конкретном случае может быть вы попней в виде сдвигового регистра, если блок 11 не саперт сигналом коммутатора 19. Последний работает с приоритетом для приема сообщений из линии связи и . отпирает блок 11 на время, когда линия связи свободна, а также переключает линию связи на выход блока 18. При этом статический сигнал с выхода блока 11, поступающий в блок 12 под воздействием генератора 2О, считывается из блока 12 блоксял 18 и в виде динамического N -раз рядного двоичного сигнала поступает в ли нию связи и, например, на вход аиалошчного селектора импульсов на другом объекте. П(Я1 поступлении из линии связи динамического двоичного N -разрядного сигнала коммутатор 19 переключает линию . связи на вход блока 17 и запирает блок 11. С помощью блока 17 и генератора. 20 динамический входной сигнал записывается в блок 12 и преобразуется в статический с помощью блока 13, с выходов которого поступает на дешифратор 14, вы попаяюший операцию, обратную той, лоторую идпапняет шифратор 1О. В результа8713256

те на т1-«-1 выходах дешифрптора 14 формируются импульсы, которые, поступая на вход блока 15, включают тот или иной генератор импульсов, каждый из которых 5 формирует импульсы, длительность которых определяется упоминавшимся выражением а один из них формирует паузу , длительность которой определяется числом повторяоошейся кодовой комбинации, соответствующей паузе. Выходные сигналы всех этих генераторов поступают на сумматор 16, с выхода которого снимается исследуемый сйгтнал, восстановленный с точностью, определяемой значениями п иТ. Таким образом, введение в селектор импульсов шифратора 10, блоков 11, 12, 13, 15, 17, 18, дешифратора 14, сумматора 16, генератора 20, инвертора 8 и коммутатора 19 позволяет не только ана- лизировать входной сигаал по текущим длительностям, но передавать и принимать результаты анализа в радио и проводных каналах связи в различной форме, например цифровой, а также восстанавливать исходный сигнал по результатам анализа с любой наперед заданной точностью. Формула изобретения Селектор импульсов по авт. св. № 79О251, отличающий.ся тем, что, с целью расширения функциональных возможностей путем обеспечения прямого и o6pt THoro преобразования сигнала в цифровую форму, в него введены тактовый генератор, бпсж последовательной записи, блок последовательного считывания, коммутатор линии связи, дополнительный инвертор, последовательно соединенные шифратор, блок параллельнс записи, блок оператишюй памяти, блок параллельного считывания, дешифратор, блок генераторов и сумматор, при этом входы шифратора подключены к выходам элементов совпадения, а детюлнительный вход - через дополнительный инвертор ко входной шине, причем выход тактового генератора соединен с первыми входами блока последовательной записи и блока последовательного считывания, с дополнительным входом блока параллельного считывания, с первым допсипнительным входом блока параллельной записи и с первым дополнительным входом блока оперативной памяти, допоп- нительный выход которого подключен ко

второму входу блока последовательного считывания, выход которого соединен с первым входом коммутатора линии связи, вт(фой вход которого подключен к д4Я1опнительной входной шине, первый выхоа - ко второму дополнительному ккоду параллельной записи, а второй выход - ко BTqpOMy входу блока последовательней записи, шлход которого соединен со вторым дополнительным входом блока оперативней памяти.

Источники информации, принятые во внимание щт экспертизе

ffff

Авторы

Даты

1981-10-07—Публикация

1979-08-13—Подача