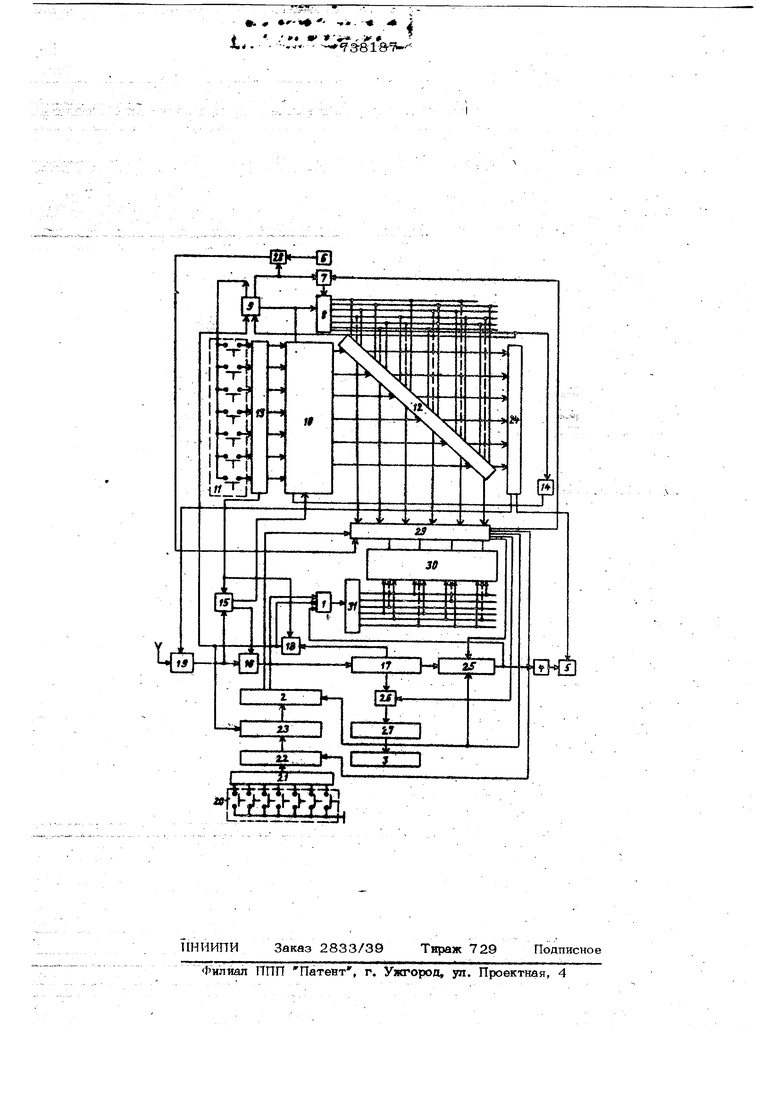

I- . Изобретение относится к радиотехнике и может использоваться для приема, .обработки и передачи дискретной информации. ;. Известно устройстводля приема и передачи кодов, содержащее первый элемен ИЛИ, блок оперативной, памяти, оконечный согласующий блок, последовательно соединенные усилитель и выходной блок, генератор, первый элемент запрета, соединенный с одним входом первого распределителя, второй вход которого соединен с одним выходом стартстоттого триггера, соединенного с дополнительным входом коммутатора ячеек программной матрицы, другие выходы стартстопного триггера соединены с одним вxoдo первого элемента запрета и входом блока клавиатуры соответственно, выходы первого рас1федепителя соединены с одними входами про.граммной матрицы, другие входы которой соединены с быходами блока клавиатуры через последовательно соединенные шифратор и коммутатора ячеек программной матрицы, дЪПолнитёльный вход которого соединен через схему сброса с дополнительным выходом первого распределителя, соединенного также с одним входом отартстопного триггера, причем дотЬпнитепьный выход шифратора через последовательно соёдинёнйыё кзоммутатор работы и второй элемент запрета соединен с входом блока Ьпрзнрвания сигаала, а также через второй элемент ИЛИ - с другим входом стйртстоиного триггера, при этом Ёыход приемника соединен с другими входами коммутатора режимов работы и второго элемента запрета. Однако в известном устройстве производитсй обмбн информации только в одном заранее выбранном канале связи. Цель изобретения - передача и прием сигналов произвольных двоичных кодов с одновременным автоматическим выбором канала. Для этого в устройство для приема и передачи кодов, содержащее первый эле73мент ИЛИ, блок оперативной памяти, оконечный согласующий блок, последовательно соединенные усилитель и выходной блОй, генератор, первый элемент запрета, соединенный с одним вхЬйЬм пёр iBOro распределителя, второй вход котороixi соединен с одним выходом стартстопногЪ tpjTfireра, соединенного с дополнительным входой ШЙй ytSf&pa я|Шё k программной матрицы, другие вьссоды стартстШЙЬТб триггера-соединены с одним входом первые элемента-загфета и входом блока клавиатуры соответственнс), выходы первого распределителя соединены с одними входами программной матрицы, другие входы которой соединены с вькодами блока 1отабиатуры через последовательно соединенные шифратор и {оммутатор ячеек программной матрицы, дополнительный : вход которого соединен через схему сброса с 1аойбпнительным выходом первого рйспрёделиТёля, соединенного также с одним входом стартстопного триггера, причем дополнительный выход шифратора iepea йоследовательно соединенные коммута тор режимов работы и второй элемент запре та соединен с входом блока опознования сиг нала, а также через второй элемент ИЛИ - с другим входом Ьтарт.стопного триггера, при этом выход приемника соединен с другими входом ctapTcfonHoro триггера, при этом выход приемника соединен с другими вЛ;одами коммутатора режимов работы и второго элемента запрета, введены последовательно соединенные дополнительные блок клавиатуры, шифратор, первый блок доп овременнрй памяти и блок перезаписи, блок выбора канала, формирователь, последовательно соединенные третий элемент запрета и второй блок долговременной памяти, четвертый элемент запрета, выход которого соединен с одним входом введенного блока оперативного управлеНИИ, другие входы которого через введенную дополнительную программную матриЙ -ШёйШены с выходами введенного второго распределителя, вход которого соедйНей с выходом Первого элемента ИЛИ, причем выход блока перезаписи соединен с одним входом блока оперативной памяти, другой вход которого соединен с одним выходом блока операттшного упра&й1Шя,йругиё вадьйы Которого соединены соответственно с другими ксодамй первого элемента запрета, первого блока дол- говременнОй памяти и первым входом фоу Шрбба ШЯ, и также первым входом третьего элемента запрета, другой вход которого соединен с блоком опознования 7Л . сигнала, выходы которого соответственно соединены с Другим входом второго элемента ИЛИ, и вторым входом формирователя, третий вход которого соединен с дополнительным выходом блока оперативного управления, первый вход которого соединен с одним выходом блока оперативной памяти; другие входы блока оперативного управления соединены с соответствующими выходами программной магрицы, другие выходы которой соединены соответствующими входами блока выбоканала, вБкоды которого соединены соответственно с входами приемника, и выходного блока, при этом первый вход первого элемента ИЛИ соединен с другим выходом блока оперативной памяти, а второй и третий входы - соответственно с выходами второго элемента ИЛИ и формирователя, соединённого с усилителем, выход второго блока долговременной памяти соединен с оконечным согласуюшим блоком, а выход генератора - с одним входом четвертого элемента запрета, другой вход которого соединен с другим выходом стартстопного триггера, при этом выход второго элемента ИЛИ соединен с другим входом блока перезаписи, а другой выход коммутатора ре мов работы соединен с дополнительным входом коммутатора ячеек программной матрицы, причем выход схемы сброса соединен с другим входом второго распределителя. На чертеже изображена структурная электрическая схема предлагаемого устройства. Устройство для приема и передачи содержит первый элемент ИЛИ 1, блок оперативной памяти 2, оконечный согласуюший блок 3, последовательно соединенные усилитель 4 и выходной блок 5, генератор 6, первый элемент запрета с°вД ® Чый с одним входом первого распределителя 8, второй вход которого соединен с одним выходом стартстопного триггера 9, соединенного с дополнительным входам коммутатора 1О ячеек программной .Mf --рицы, другие выходы стартстопного триггера 9 соединены с одним входом первого элемента запрета 7 и входом блока клавиатуры Ц соответственно, выходы первого распределителя 8 соединены с одними входами программной матрицы 12, другие входы которой соединены с выходами блока клавиатуры Ц через последовательно соединенные шифратор 13 и коммутатор 10 ячеек программной матрицы, дополнительный вход которого соединен через схему сброса 14 i с дополнительным выходом первого распределителя 8, соединенного также с одним входом стартстопного триггера 9, дополнительный выход шифратора 13 через последовательно соединенн.ьге коммутатор режимов работы 15 и второй элемент запрета 16 соединен с входом блока опознованйя сигнала 17, а также через второй элемент ИЛИ 18 - с други входом стартстопного триггера 9 , при этом выход приемника 19 соединен с другими входами коммутатора режимов ; работы 15 и второго элемента запрета .16, последовательно соединенные дополнительные бпок клавиатуры 2О, шифратор 21, первый блок долговременной памяти 22 и блок перезаписи 23, блок выборка канала 24, формирователь 25, последова тельно соединенные третий элемент запрета 26 и второй блок долговременной памяти 27, четвертый элемент запрета 28, выход которого соединен с одним входом блока оперативного 5иравления 29, другие 5 входы которого через дополнительную про граммную матрицу ЗО соединены с выходами второго распределителя 31, вход которого соединен с выходом первого эле мента И71И 1, причем выход блока перезаписи 23 соединен с одним входом блока оперативной памяти 2, другой вход которого соединен с одним выходом блока оперативного управления 29, другие выходы которого соединены соответственно с другими входами первого элемента запрета 7, первого блока долговременной памяти 22 и первым входом формирователя 25 а также первым входом третьего элемента запрета 26, дру1гой вход которого соединен с блоком опознованйя сигнала 17, выходы которого соответртвенно соединены с Другим входом второго элемента ИЛИ 18 и вторым входом формирователя 25, третий вход которого сое динен с дополнительным выходом блока оперативного управления 29, первый вход которого соединен с одним выходом блока опе1)ативной памяти 2, другие входы блока оперативного управления 29 соединены с соответствующими выходами программной Матрицы 12, другие выходы которой соединены с соответствующими входами блока выбора канала 24, выходы которого соединены соответственно с входами приемника 19 и выходного блока 5, при этом первый вход первого элемента ИЛИ 1 соединен с другим выходом блока one-

ративной памяти 2, а второй и третий входы - соответственно с вькоцами второго элемента ИЛИ 18 и формирователи 25, соединенного с усилителем 4, вьрсод второго блока долговременной памяти 27 соединен с оконечным согласуюшим блоком 3, а выход генератора 6 - с одним входом четвертого элемента запрета 28, вход котсфогхэ соединен с другим выходом стартстопного триггера 9, при этом выход второго элемента

ИЛИ 18 соединен с др|угиМ входной блока перезаписи 23, а другой выход коммутатора режимов работы 15 соединен с дополнительным входом коммутатора 10 ячеек программной матрицы, причем выход схемы сброса 14 соединен с другим входом второго распределителя 31.

Устройство работает следующим обраээй. -- -- . .. -.,

До режима передачи оператором производится запись передаваемой информации по заданной программе в первый блок долговременной памяти 22 при помощи дополнительного блока клавиатуры 20 и дополнительного шифратора 21. При передаче оператор воздействует на блок клавиатуры 11, что обеспечивает на выходе шифратора 13 появление сигнала, включающего коммутатор режимов работы 15 в положение, при котором отпирается коммутатор Ю ячеек программной матрицы, обеспечивая включение одного из YI каналов связи сигналом выбора с выхода блока выбора канала 24 связи , и запирается приемный вход блока опознования сигнала 17 из-за срабатьшания четвертого элемента запрета 28 приема сигнала. Этот же сигнал поступает на один из входов второго элемента ИЛИ 18, которь1й включает блок перезаписи 23 и стартстопный триггер 9. Последний отключает первый элемент запрета 7 и импульсы генератора 6 поступают на вход блока .оперативного управления 29. Кроме эГого сигнал через один из входов первого мента ИЛИ 1, второй распределитель 31 и дополнительную программную матрицу 30 воздействует на вход блока оперативного управления 29, на выходе которогх в зависимости от состояния ячеек дополнительной программной матрицы 3.0 и ячеек программной матрицы 12 появляется сигнал, выбирающий передаваемую информацию из ячеек первого блока долговременной памяти 2.2. и згшисываюший ее через блок перезаписи 23 в блок oneративной памяти 2, с которого информаЦйясчитывается в блок оперативного управления 29. Сигнал окончания считывания информации поступает на вход первого элемента ИЛИ 1 и воздействует через второй распределитель 31 и ячейки дополнительной программной матрицы 30 на блок оперативного управления 29, включающий формирователь 25, который формирует кодовые комбинации, поступающие через усилитель 4 на выходной блок 5. Сигнал окончания кодовой комбинации поступает на вход первого элемента ИЛИ.1 и воздействует через второй распределитель 31 и ячейки дополнительной программной матрицы 30 на блок оперативного управления 29, с выхода которого на установочные входы формирователя 25 йоступает сигнал сброса, С другого выхода блока оперативного управления 29 сигнал поступает через чет вертый элемент запрета 28.на первый распределитель 8, и с его дополнительного выхода (например, дополнительного разряда регистра сдвига) сигнал выключает стартстопный триггер 9 и Пёрейодит устройство в режимдежурного приема, устанавливая через схему сброса 14 в начальное йопожение коммутатор 10 ячее nporp MMHot матрицы и второй рас пределитбль 31. ... При приеме сигнал с выхода приемника 19 (ипв проводной линии связи) поступает на коммутатор режимов работы 15, который запирает коммутатор 10 ячеек программной матрицы и отключает второй элемент запрета 16 приема сигналов, что обеспечивает прохождение сигнала от приемника 19 к блоку опознования сигнала 17. Если принят сигнал свой ,1с вь1хода блока опознования сигнала 17 на другой вход .второго элемен та ИЛИ 18 поступает сигнал, который через один из входов первого элемента ИЛИ 1, второй распределитель 31 и дополнительную трограммную матрицу 30 воздействует на блок оперативного управ ления 29, с вьйода которого управляющий сигнал переписьтает через третий элемент запрета 26 в одну из ячеек второго блока долговременной памяти 27 принятую информацию, откуда зафиксированный сигйал поступает на оконечный согласующий блок 3, одновременно вклвэчает блок перезаписи 23, а также стартстопный триггер 9, обеспечивающий в зависимости от клавиш блока клавиатуры 11 включение заданного канала связи и оявление на выходе шифратора 13 сигнаа, включаюи(его коммутатор режимов, аботы 15 в положение, при котором втоматически осуществляются передачи информации, хранящейся в устройстве, . по описанному выше способу. Предложенное устройство по сравнению, d известным позволяет передавать и принимать сигналы прои 1вольных двоичных кодов с одновременным автоматическим выбором канала . Ф о рмула изобретения Устройство для приема и передачи кодов, содержащее первый элемент ИЛИ;, блок оперативной памяти, оконечный согласующий бло.к, :последоЁательно соединенные усилитель и выходной блок, генератор, первый элемент запрета, соединенный с одним входом первого распределителя, второй вход которого соединен с одним выходом стартстопного триггера, соединенного с дополнительным входом комыутатора ячеек программной, матрицы, другие выходы стартстопного триггера соединены с одним входом первого элемента запрета и входом блока клавиатуры соответственно, выходы первого распределителя соединены с одними входами программной матрицы, другие входй которой соединены с выходами блока клавиатуры через последовательно соединенньш шифратор и коммутатор ячеек программной матрицы, дополнительный вход которого соединен через схему .сброса с дополнительным выходом первого распределителя, соединенного также с одним входом стартстопного триггера, причем дополнительный выход щифратора через .последовательно соедйненнйе Коммутатор режимов работы и второй элемент запрета соединен с . входом блока опознования сигнала, а также через второй элемент ИЛИ - с другим входом стартстопного триггера, при этом выход приемника соединен с другими входами коммутатора режимов работы и второго элемента запрета, о т л и .4 а ю щ е е с я тем, что, с целью передачи и приема сигналов произвольных . двоичных кодов с одновременным автоматическим выбором канала, в него введены последовательно соединенные дополнительные блок клавиатуры, щифратор, первый блок долговременной памяти и блок перезаписи, блок выбора канала, формирователь, последовательно

(Соединенные третий элемент запрета и второй блок долговременной памяти, четвертый элемент запрета, выход которого соединен с одним входом введенного блока, оперативного управления, другие входыкоторого через введенную дополнительную программную матрицу соединены с выходами введенного второго распределителя, вход которого соединен с выходом первого элемента ИЛИ, причем выход блока перезаписи соединен с одним входом блока оперативной памяти, другой вход которого соединен с одним выходом блока оперативного управления, другие выходы которого соединены соответствен,но с другими входами первого элемента запрета, первого блока долговременной памяти и первым входом формиройателя, а также первым входом третьего элемента запрета, другой вход которого соединен с блоком опознования сигнала, выходы которого соответственно соединены с другим входом второго элемента ИЛИ, и вторым входом формирователя, третий вход которого соединен с дополнительным

выходом блока оперативного управления, первый вход которого соединен с одним

ВЫХОДОМ блока оперативной памяти, дру:гие входы блока оперативного управления соединены с соответствующими выходами программной матрицы, другие выходы которой соединены с соответствующими входами блока выбора канала, выходы которого соединены .соответственно с входами приемника, и выходного блока, при этом первый вход первого элемента ИЛИ соединен с другим выходом блока оперативной памяти, а второй и третий входы соответственно с выходами второго элемента ИЛИ и формирователя, соединенного с усилителем, выход второго блока долговременной памяти соединен с оконечным согласующим блоком, а выход генератора - с одним входом четвертого элемента запрета, другой вход которого соединен с другим выходом стартстопного триггера, при этом вькод второго элемента ИЛИ соединен с другим входом блока перезаписи, ai другой выход коммутатора режимов работы соединен с дополнительным входом коммутатора ячеек программной матрицы, причем выход схемы сброса соединен с другим входом второго распределителя.

. ф. , T,.-t I

t о #i., „ 4. . . -.«. - - 3-8-18-T

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи и приема кодов | 1978 |

|

SU949835A1 |

| Селектор-преобразователь импульсных сигналов | 1981 |

|

SU966879A1 |

| Генератор кода морзе | 1977 |

|

SU750750A2 |

| Автоматический генератор кода Морзе | 1983 |

|

SU1107318A1 |

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| ВСЕСОЮЗНАЯ . | 1973 |

|

SU370737A1 |

| Генератор кода Морзе | 1985 |

|

SU1243107A2 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ТЕШ^ХАНИЧШКОИ ШФОРЩЦИИ | 1972 |

|

SU433524A1 |

| Селектор импульсов | 1979 |

|

SU871325A2 |

| Устройство для искажения стартстопногоТАКСТА | 1979 |

|

SU843276A1 |

чгжнз

Авторы

Даты

1980-05-30—Публикация

1976-10-05—Подача