Изобретение относится к вычислительной технике, в частности к вычислительным системам, системам передачи и обработки дискретной информации, и может быть использовано для опера тинной встроенной проверки исправности систем при обеспечении самопроверяемости устройства обнаружения дефектов .

Известно самопроверяемое устройство обнаружения дефектов для проверки цифровых систем с данными, кодированными кодом к-из-п, состоящее из двух независимых логических схем на элементах И-ИЛИ (или ИЛИ-И), каждая из которых имеет по одному выходу, на которых формируются взаимодействующие сигналы. Эти два выхода принимают значения 01 (или 10) в случае когда в контролируемой системе дефекты отсутствуют, и 00 (или 11), в противном случае это устройство выполнено таким образом, чтд на входах каждого логического элемента в процессе нормального функционирования контролируемой (основной) системы и блока кодирования образуется проверяющий тест. Тем самым обеспечивается необходимое условие самопроверки (самотестируемости) устройства. Назначение блока кодирования состоит в том, чтобы для любого фиксированного дефекта в основной системе (или блоке кодирования) генерировать по крайней мере один код, который является тестовым воздействием для данного дефекта, т.е. в случае подачи на вход устройства обнаружения дефектов этого кода оно выдает значение, отличное от значения выдаваемого при отсутствии данного дефекта ij.

Недостатком известного устройства является то, что для его синтеза требуется специальный блок кодирования, синтез которого весьма трудоемок, а также малая достоверность контроля, обусловленная, во-первых, тем, что смена значений сигналов 01 На 10 (или 10 на 01), соответст20вующих исправному состоянию системы, происходит в произвольные (заранее не известные) моменты времени и, тем самым, отсутствует возможность проверки правильности переключений,

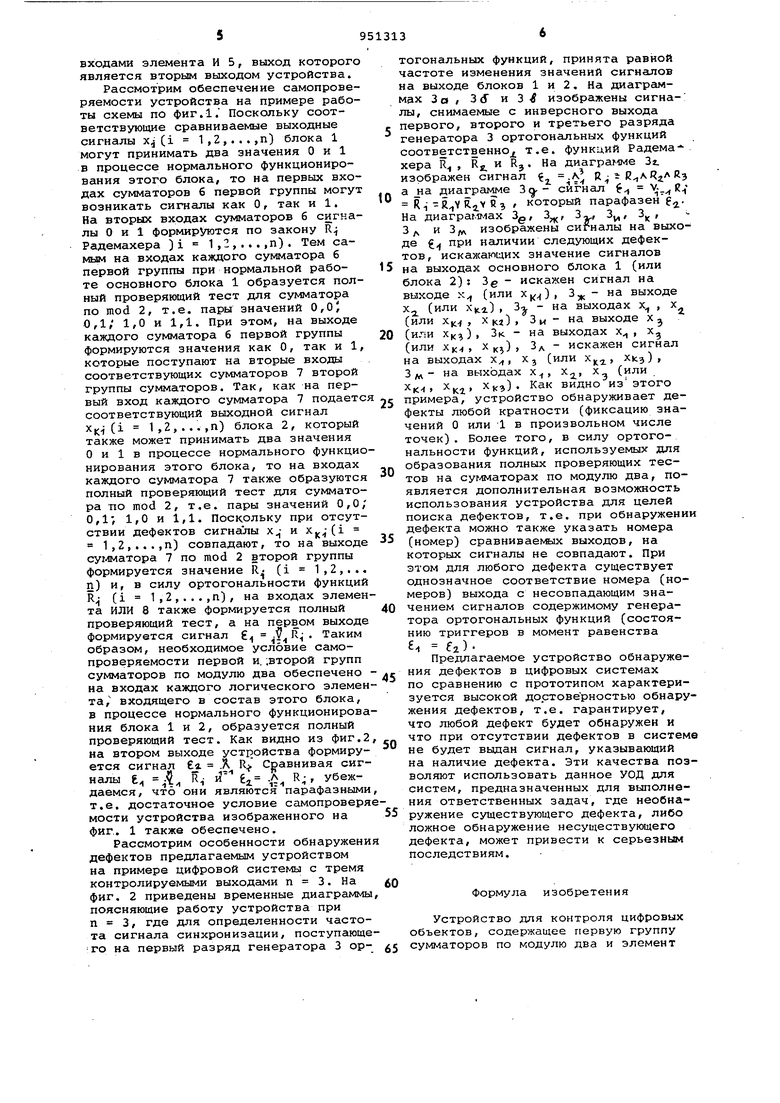

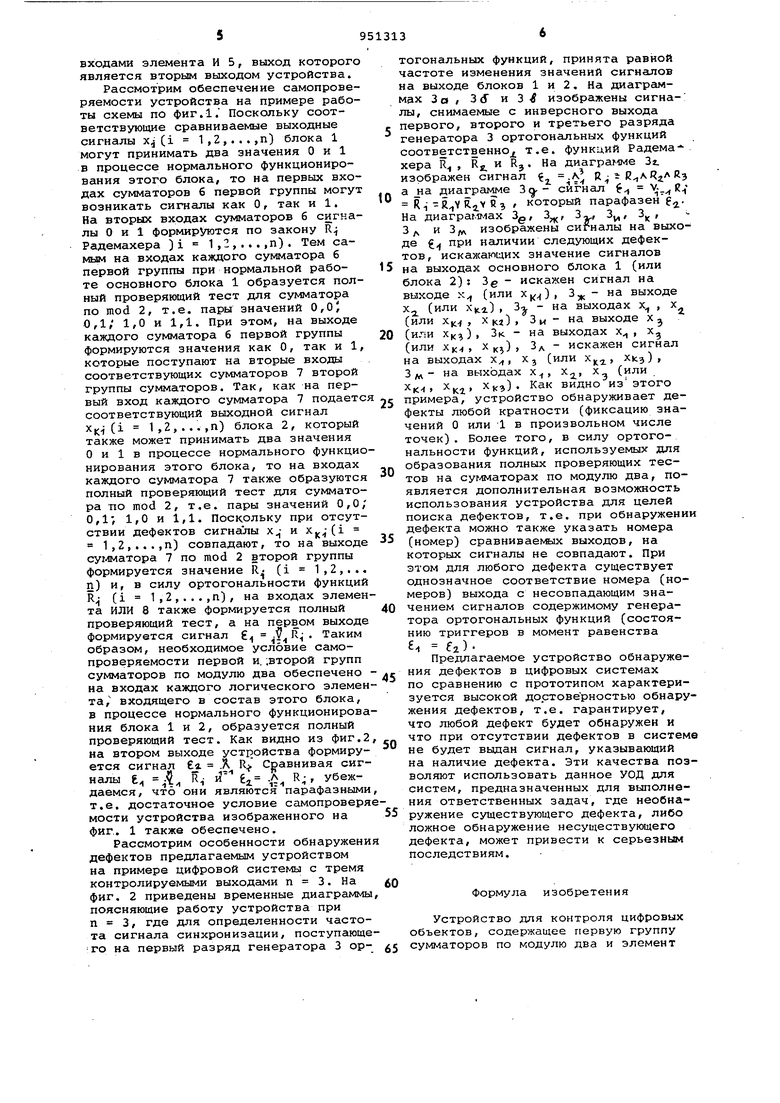

25 а главное, проверки факта переключения, т.е. дефекты, приводя1иие к фиксаЦии значений 01 (или 10) не обнаружены устройством. Во-вторых, малая достоверность связана с том, что на входах независимых логических CXGM. формирующих значения 01 (10) , образуется не полный проверяющий тост, позволяющий обнаруживать дефекты произвольной кратности, а рассчитанный лишь на обнаружение однократных дефектов. , Известно также устройство для обнаружения дефектов в цифровых автоматах, содержащее основной и конт рольный блоки, на входы которых поступают рабочие входные воздействия а группы выходов этих блоков соедине ны с блоком сравнения сигналов, в состав которого входит группа сумматора по mod 2 и элемент ИЛИ, причем срав шваемые выходы попарно подаиотся на входы соответствующих сумма.торов по mod 2, выход каждого из которых соединен с одним из входов элемента ИЛИ. Контрольный блок реализуется таким образом, что на его выходах формируются сигналы, которые при отсутствии дефектов совпадают с выходными сигнсшами основного блока. В простейшем, случае в качестве контрольного блока может быть исполь зован блок, идентичный основному. Ис пользование подобного устройства не требует специального кодирования (например, кодом к-из-п) и исключает трудоемкий синтез блока кодирования. В случае отсутствия дефектов на входах каждого из сумматоров по mod 2 формируется пара сигналов 00 (или 11), при этом элемент ИЛИ формирует на выходе сигнал g О, соответствующий исправному состоянию основного и контрольного блока. При наличии дефекта в основном или контрольном блоке на выходах одного или нескольких сумматоров образуется пара сигналов 01 (или 10), которые формируют значение 1 на выходе одног (или нескольких) сумматоров по mod 2 Данная единица через элемент ИЛИ формирует сигнал 6 1, указывающий о наличии дефекта 2j. , Недостатком известного устройства является ниэкая достоверность контроля в связи с тем, что он не позволяет обнаруживать однократные дефекВХОДОВ и выходов сумматоров по mod 2 и элемента ИЛИ. Цель изобретения - повышение достоверности контроля без применения специального кодирования. Поставленная цель достигается тем, что в устройство для контроля цифровых объектов, содержащее первую группу сумматоров по модулю два и ИЛИ, причем информационные входы устройства соединены с выxoдaI основного и вспомогательного контролируемых цифровых объектов, выходы основного контролируемого цифрового объекта соединены с первой группой входов сумматоров по модулю два первой группы, выход элемента ИЛИ является первым выходом устройства. Оно содержит генератор ортогональных функций, элемент И и вторую группу сумматоров по модулю два, причем информационные входы первой группы генератора ортогональных функций соединены с вторыми входами соответствующих сумматоров по модулю два первой группы, выходы сумматоров по модулю два первой группы соединены с первыми входами соответствующих сумматоров по модулю два второй группы, выходи вспомогательного контролируемого цифрового объекта соединены с вторыми входами соответствующих сумматоров по модулю два второй группы, выходы сумматоров по модулю два второй группы соединены с соответствующими входами элемента ИЛИ, вторая группа выходов генератора ортого.нальных функций соединена с входами элемента И, выход которого является вторым выходом устройства, вход генератора ортогональных функций является синхровходом устройства, входом блока сравнения. Генератор ортогональных функций (например, Радемахера) состоит из делителя частоты с числом разрядов, райным числу сравниваемых выходов основного и вспомогательного цифровых объектов. На фиг, 1 представлено устройство для контроля цифровых объектов/ на фиг. 2 - временные диаграммы работы устройства для случая контроля с тремя контролируемыми выходами, I Устройство для контроля цифровых объектов (фиг.1) содержит основной 1 и контрольный 2 цифровые объекты генератор 3 ортогональных функций, элемент ИЛИ 4 элемент И 5. Сумматоры 6по mod 2 образуют первую группу сумматоров по mod 2, входами которых являются соответствующие выходы основного цифрового объекта 1 и инверсные выходы генератора 3 ортогональных функция. Сумматоры 7 по mod 2 образуют вторую группу сумматоров по mod 2, входами которых являются выходы сумматоров 6 по mod 2 первой группы и выходы вспомогательного цифрового объекта 2. Входами элемента ИЛИ 4 являются выходы сумматоров 7по mod 2 второй группы, а его выход является первым выходом устройства. Генератор 3 ортогонашьных функций состоит из группы последовательно соединенных счетных триггеров 8.1-8.П и является делителем частоты с числом разрядов, равным числу контролируемых выходов основного цифрового объекта 1, Вход генератора 3 ортогональных функций соединен с выходом синхронизации основного цифрового объекта 1, Сигналы, снимаемые с прямых выходов разрядов, являются

входами элемента И 5, выход которого является вторым выходом устройства.

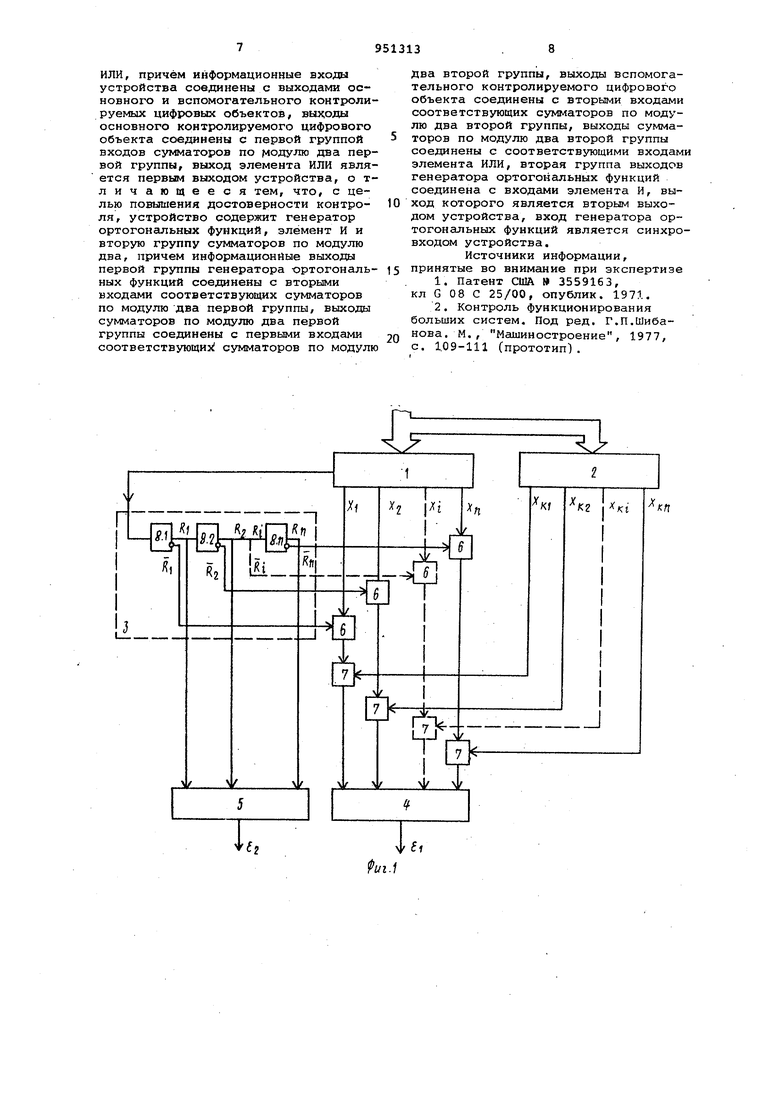

Рассмотрим обеспечение самопроверяемости устройства на примере работы схемы по фиг,1. Поскольку соответствующие сравниваемые выходные сигналы x,j (i l,2,...,n) блока 1 могут принимать два значения О и 1 в процессе нормального функционирования этого блока, то на первых входах сумматоров б первой группы могут возникать сигналы как О, так и 1. На вторых входах сумматоров б сигналы О и 1 формируются по закону R Радемахера )i 1 ,2, ... ,п) . Тем самым на входах каждого сумматора б первой группы при нормальной работе основного блока 1 образуется полный проверяющий тест для сумматора по mod 2, т.е. пары значений 0,0j од; 1,0 и 1,1. При этом, на выходе каждого сумматора б первой группы формируются значения как О, так и 1, которые поступают на вторые входы соответствующих сумматоров 7 второй группы сумматоров. Так, как на первый вход каждого сумматора 7 подаетс соответствующий выходной сигнал х,, (i 1,2,...,п) блока 2, который также может принимать два значения О и 1 в процессе нормального функционирования этого блока, то на входах каждого сумматора 7 также образуются полный проверяющий тест для сумматора по mod 2, т.е. пары значений 0,0/ 0,1; 1,0 и 1,1. Поскольку при отсутствии дефектов сигналы и (1 1,Z,...,n) совпадают, то на выходе су1иматора 7 по mod 2 второй группы формируется значение R. (i 1,2,... п) и, в силу ортогонгшьности функций R (i 1|2,...,п), на входах элемента ИЛИ 8 также формируется полный проверяющий тест, а на первом выходе формируется сигнал . . Таким образом, необходимое условие самопроверяемости первой и. ;второй групп сумматоров по модулю два обеспечено на входах каждого логического элемента/ входящего в состав этого блока, в процессе нормального функционирования блока 1 и 2, образуется полный проверяющий тест. Как видно из фиг.2 на втором выходе устгзойства формируется сигнал а. .Я R Сравнивая сигналы е Д R,- и i .л R, убеждаемся, что они являются парафазными т.е. достаточное условие самопроверямости устройства изображенного на фиг. 1 также обеспечено.

Рассмотрим особенности обнаружени дефектов предлагаемым устройством на примере цифровой системы с тремя контролируемыми выходами п 3. На фиг. 2 приведены временные диаграммы поясняющие работу устройства при п 3, где для определенности частота сигнала синхронизации, поступающе го на первый разряд генератора 3 ортогональных функций, принята равной частоте изменения значений сигналов на выходе блоков 1 и 2. На диаграммах За , 3(Г и 3 в изображены сигналы, снимаемые с инверсного выхода первого, второго и третьего разряда генератора 3 ортогональных функций соответственно т.е. функций Радемахера R , R и Rj. На диаграмме 3г. изображен сигнал R г C,,Ri К а jia диагрс1мме Зд-- сигнал V-. К RI R2.V К , который парафазене, На диагра№ ах 3g, 3, З-, 3j, 3, Зд и 3;л изображены сигналы на выходе при наличии следующих дефектов, искахсающих значение сигналов на выходах основного блока 1 (или блока 2): Зе - искахсен сигнал на выходе х (или х), 3 - на выходе х (или ) , 3-J - на выходах х , х (или х, , XK.Z), Зи us выходе х (или х), Зк - на выходах х, х (или х, , X к) , Зд искажен сигнал на выходах х, х, (или х,, ) ,

X (или 3/VV - на выходах х, к.

, ) Как видно из этого

Xк

К

примера, устройство обнаруживает дефекты любой кратности (фиксацию значений О или 1 в произвольном числе точек). Более того, в силу ортогональности функций, используемых для образования полных проверяющих тестов на суглматорах по модулю два, появляется дополнительная возможность использования устройства для целей поиска дефектов, т.е. при обнаружени дефекта можно также указать номера (номер) сравниваемых выходов, на которых сигналы не совпадают. При этом для любого дефекта существует однозначное соответствие номера (номеров) выхода с несовпадающим значением сигналов содержимому генератора ортогональных функций (состоянию триггеров в момент равенства

fz)Предлагаемое устройство обнаружения дефектов в цифровых системах по сравнению с прототипом характеризуется высокой достоверностью обнаружения дефектов, т.е. гарантирует, что любой дефект будет обнаружен и что при отсутствии дефектов в систем не будет выдан сигнал, указывающий на наличие дефекта. Эти качества позволяют использовать данное УОД для систем, предназначенных для выполнения ответственных задач, где необнаружение существующего дефекта, либо ложное обнаружение несуществующего дефекта, может привести к серьезным последствиям.

Формула изобретения

Устройство для контроля цифровых объектов, содержащее первую группу сумматоров по модулю два и элемент

ИЛИ, причём информационные входы устройства соединены с выходами основного и вспомогательного контролируемых цифровых объектов, выходы основного контролируемого цифрового объекта соединены с первой группой входов суг«1маторов по модулю два первой группы, выход элемента ИЛИ является первым выходом устройства, о тличающееся тем, что, с целью повышения достоверности контроля, устройство содержит генератор ортогональных функций, элемент И и вторую группу сумматоров по модулю два, причем информационйые выходы первой группы генератора ортогональных функций соединены с вторыми входами соответствующих сумматоров по модулю два первой группы, выходы сумматоров по модулю два первой группы соединены с первыми входами соответствующий сумматоров по модулю

Два второй группы, выходы вспомогательного контролируемого цифрового объекта соединены с вторыми входами соответствующих сумматоров по модулю два второй группы, выходы сумматоров по модулю два второй группы соединены с соответствующими входам элемента ИЛИ, вторая группа выходов генератора ортогональных функций соединена с входами элемента И, выход которого является вторым выходом устройства, вход генератора ортогональных функций является синхровходом устройства.

Источники информации, принятые во внимание при экспертизе

1.Патент США 3559163,

кл G 08 С 25/00, опублик. 197:1..

2.Контроль функционирования больших систем. Под ред. Г.П.Шибанова. М., Машиностроение, 1977, с. 1.09-111 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых объектов | 1987 |

|

SU1441404A2 |

| ГЕНЕРАТОР КВАЗИОРТОГОНАЛЬНО-ПРОТИВОПОЛОЖНЫХ СИГНАЛОВ | 1999 |

|

RU2187144C2 |

| N-канальный линейный цифровой фильтр с контролем | 1986 |

|

SU1325512A1 |

| Генератор квазиортогональных сигналов | 1989 |

|

SU1755270A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ КОЭФФИЦИЕНТОВ БУЛЕВЫХ ПРЕОБРАЗОВАНИЙ НАД ПОЛЕМ ГАЛУА GF(2) | 2011 |

|

RU2475810C2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2439667C1 |

| Способ передачи дискретных сообщений с расширенным шифрованием кодов и система для его осуществления | 2022 |

|

RU2819200C1 |

| Способ передачи дискретных сообщений с расширенной системой шифрования и система устройств для его осуществления | 2022 |

|

RU2823549C1 |

| Способ передачи дискретных сообщений с расширенной системой синхронизируемого шифрования и устройство для его осуществления | 2024 |

|

RU2832047C1 |

а ff 5 t

e

ж .

5

ы

к/f

Авторы

Даты

1982-08-15—Публикация

1980-12-01—Подача