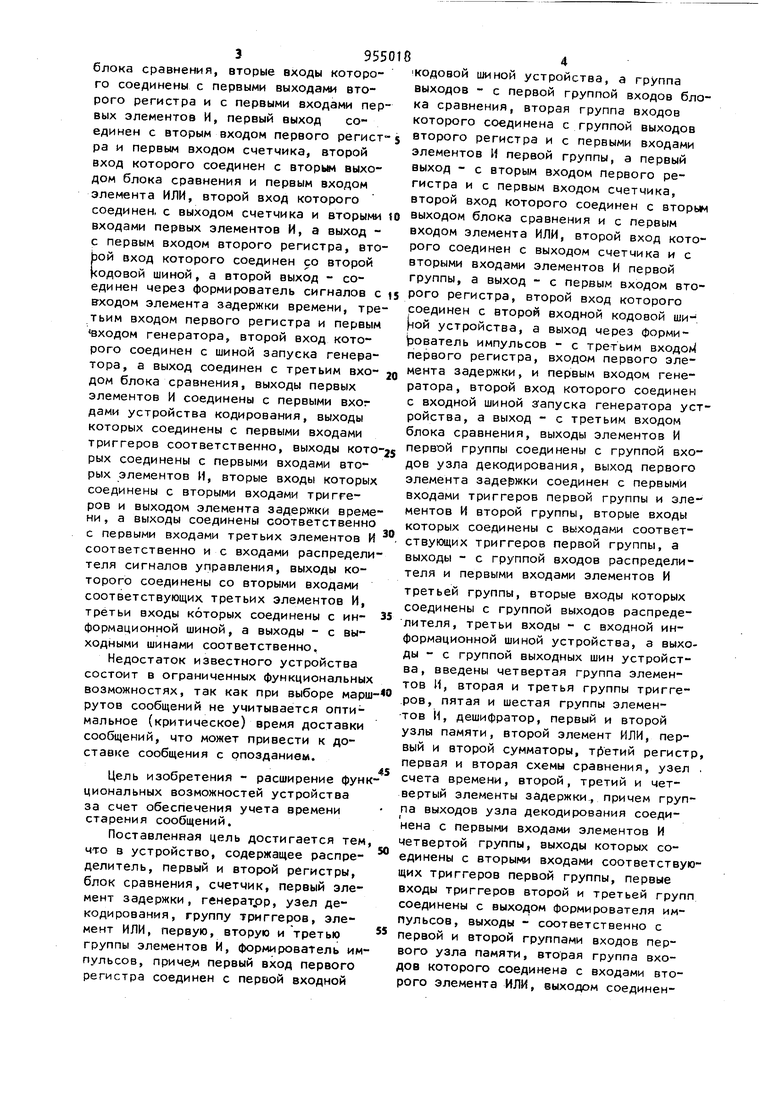

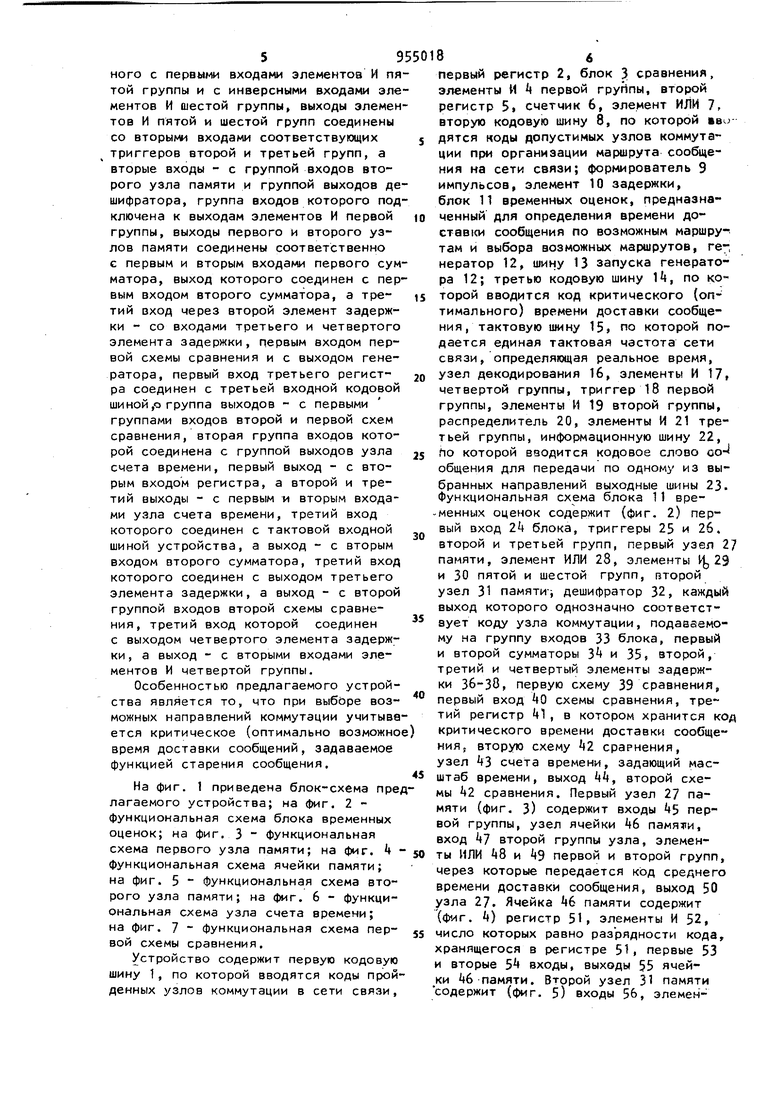

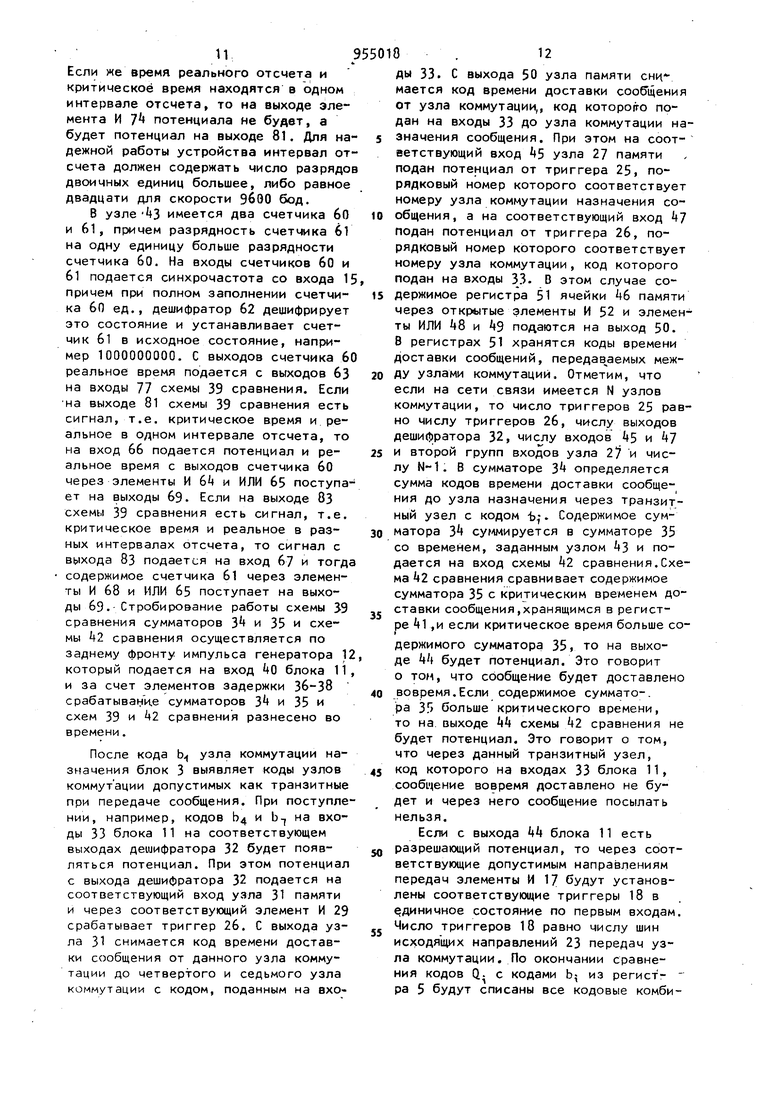

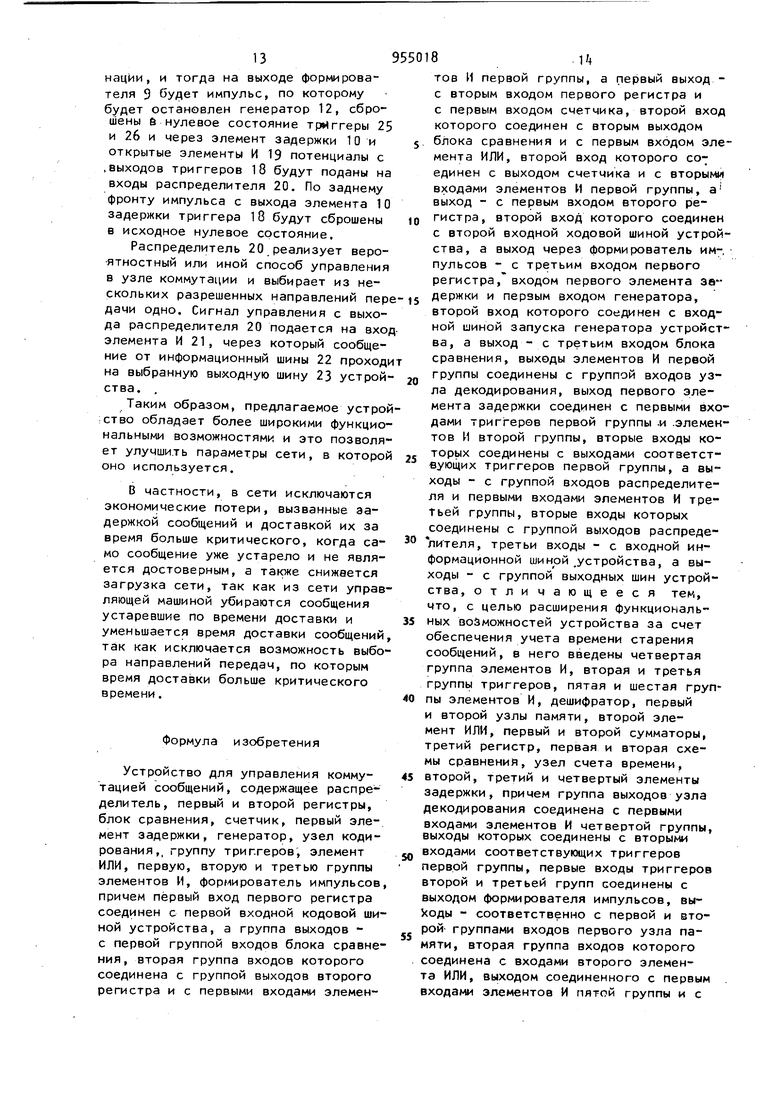

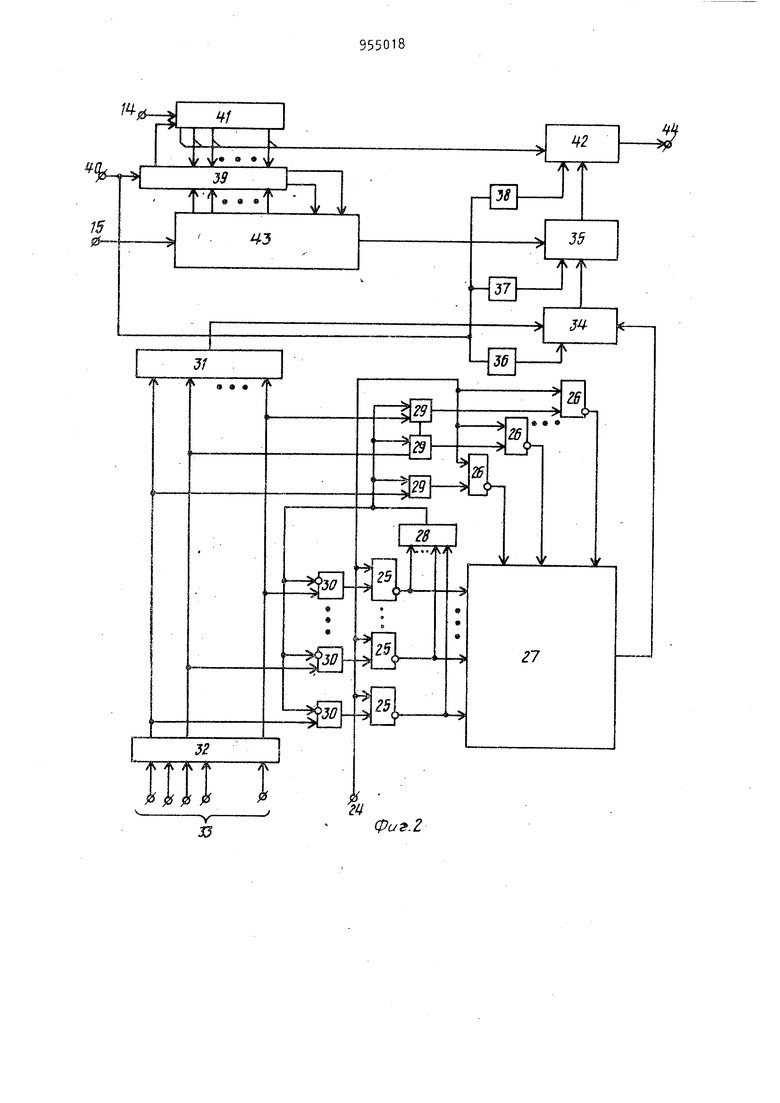

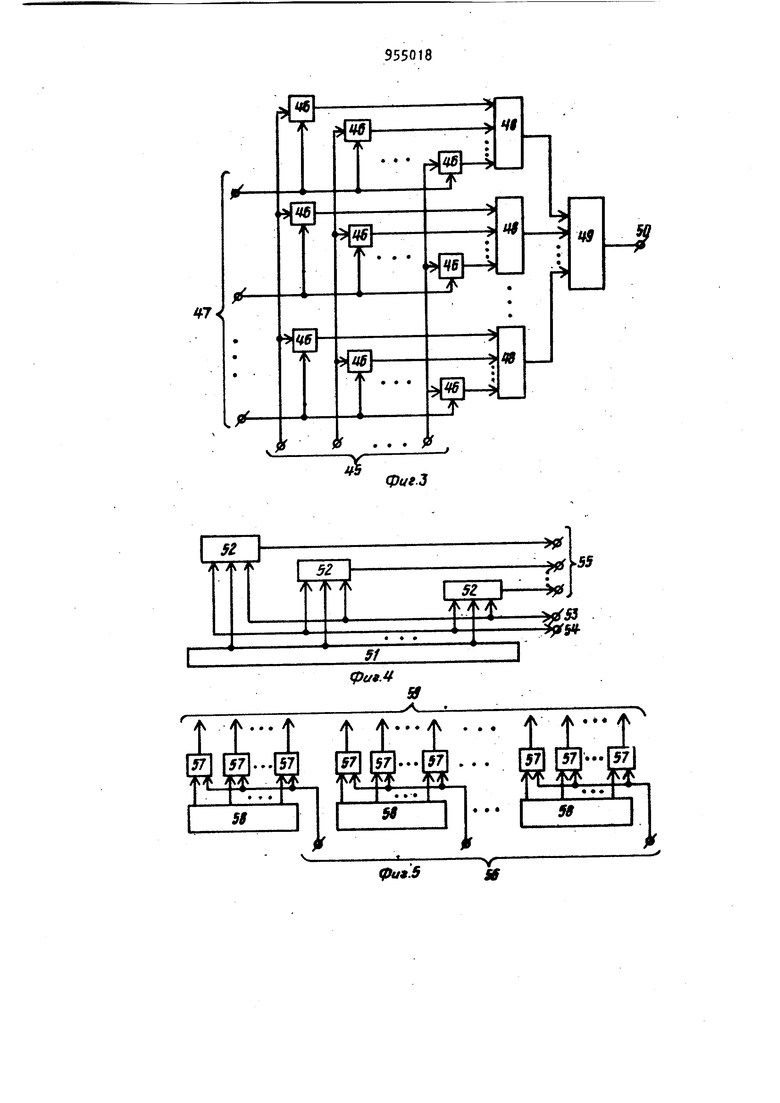

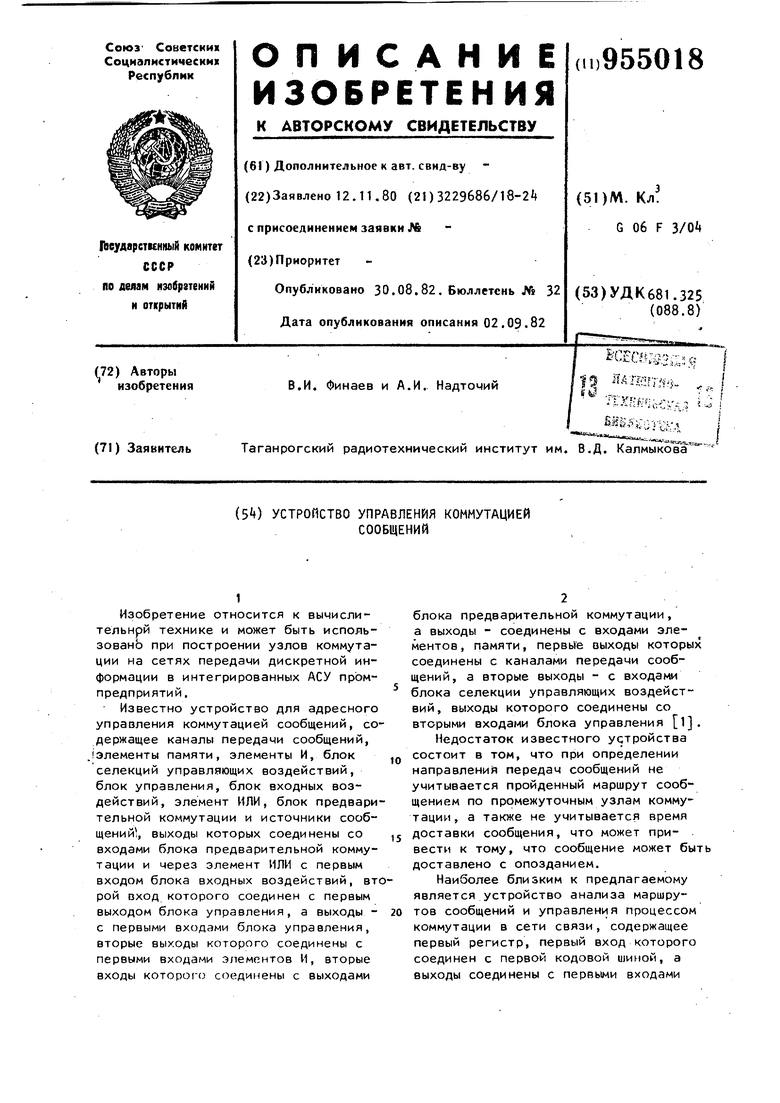

Изобретение относится к вычислительирй технике и может быть использованЬ при построении узлов коммутации на сетях передачи дискретной информации в интегрированных АСУ прЬмпредприятий. Известно устройство для адресного управления коммутацией сообщений, со держащее каналы передачи сообщений, элементы памяти, элементы И, блок селекции управляющих воздействий, блок управления, блок входных воздействий, элемент ИЛИ, блок предвари тельной коммутации и источники сообщений, выходы которых соединены со входами блока предварительной коммутации и через элемент ИЛИ с первым входом блока входных воздействий, вт рой вход которого соединен с первым выходом блока управления, а выходы с первыми входами блока управления, вторые выходы которого соединены с первыми входами элементов И, вторые входы которого соединены с выходами блока предварительной коммутации, а выходы - соединены с входами элементов , памяти, первые выходы которых соединены с каналами передачи сообщений, а вторые выходы - с входами блока селекции управляющих воздействий, выходы которого соединены со вторыми входами блока управления Недостаток известного устройства состоит в том, что при определении направления передач сообщений не учитывается пройденный маршрут сообщением по промежуточным узлам коммутации, а также не учитывается время доставки сообщения, что может привести к тому, что сообщение может быть доставлено с опозданием. Наиболее близким к предлагаемому является устройство анализа маршрутов сообщений и управления процессом коммутации в сети связи, содержащее первый регистр, первый вход которого соединен с первой кодовой шиной, а выходы соединены с первыми входами 3955 блока сравнения, вторые входы которого соединены с первыми выходами второго регистра и с первыми входами пер вых элементов И, первый выход соединен с вторым входом первого регист ра и первым входом счетчика, второй вход которого соединен с вторьм выходом блока сравнения и первым входом элемента ИЛИ, второй вход которого соединен, с выходом счетчика и вторыми входами первых элементов И, а выход с первым входом второго регистра, вто 1эой вход которого соединен со второй } одовой шиной, а второй выход - соединен через формирователь сигналов с входом элемента задержки времени, тре тьим входом первого регистра и первым входом генератора, второй вход которого соединен с шиной запуска генератора, а выход соединен с третьим входом блока сравнения, выходы первых элементов И соединены с первыми вхог дами устройства кодирования, выходы которых соединены с первыми входами триггеров соответственно, выходы кото рых соединены с первыми входами вторых элементов И, вторые входы которых соединены с вторыми входами триггеров и выходом элемента задержки време ни , а выходы соединены соответственно с первыми входами третьих элементов И соответственно и с входами распредели теля сигналов управления, выходы которого соединены со вторыми входами соответствующих третьих элементов И, третьи входы которых соединены с информационной шиной, а выходы - с выходными шинами соответственно. Недостаток известного устройства состоит в ограниченных функциональных возможностях, так как при выборе марш рутов сообщений не учитывается оптимальное (критическое) время доставки сообщений, что может привести к доставке сообщения с опозданием. Цель изобретения - расширение функ циональных возможностей устройства за счет обеспечения учета времени старения сообщений. Поставленная цель достигается тем что в устройство, содержащее распределитель, первый и второй регистры, блок сравнения, счетчик, первый элемент задержки, генератрр, узел декодирования, группу триггеров, элемент ИЛИ, первую, вторую и третью группы элементов И, формирователь импульсов, причем первый вход первого регистра соединен с первой входной КОДОВОЙ шиной устройства, а группа выходов - с первой группой входов блока сравнения, вторая группа входов которого соединена с группой выходов второго регистра и с первыми входами элементов И первой группы, а первый выход - с вторым входом первого регистра и с первым входом счетчика, второй вход которого соединен с вторьм выходом блока сравнения и с первым входом элемента ИЛИ, второй вход которого соединен с выходом счетчика и с вторыми входами элементов И первой группы, а выход - с первым входом второго регистра, второй вход которого соединен с второй входной кодовой ши-. |ной устройства, а выход через формирователь импульсов - с третьим входов первого регистра, входом первого элемента задержки, и первым входом генератора , второй вход которого соединен с входной шиной запуска генератора устройства, а выход - с третьим входом блока сравнения, выходы элементов И первой группы соединены с группой входов узла декодирования, выход первого элемента задержки соединен с первыми входами триггеров первой группы и элементов И второй группы, вторые входы которых соединены с выходами соответствующих триггеров первой группы, а выходы - с группой входов распределителя и первыми входами элементов И третьей группы, вторые входы которых соединены с группой выходов распределителя, третьи входы - с входной информационной шиной устройства, а выходы - с группой выходных шин устройства, введены четвертая группа элементов И, вторая и третья группы тригге.ров, пятая и шестая группы элементов И, дешифратор, первый и второй узлы памяти, второй элемент ИЛИ, первый и второй сумматоры, третий регистр, первая и вторая схемы сравнения, узел . счета времени, второй, третий и четвертый элементы задержки., причем группа выходов узла декодирования соединена с первыми входами элементов И четвертой группы, выходы которых соединены с вторыкм входами соответствующих триггеров первой группы, первые входы триггеров второй и третьей групп соединены с выходом формирователя импульсов, выходы - соответственно с первой и второй группами входов первого узла памяти, вторая группа входов которого соединена с входами второго элемента ИЛИ, выходом соединенного с первыми входами элементов И пя той группы и с инверсными входами эле ментов И шестой группы, выходы элемен тов И пятой и шестой групп соединены со вторыми входами соответствующих триггеров второй и третьей групп, а вторые входы - с группой входов второго узла памяти и группой выходов де шифратора, группа входов которого под ключена к выходам элементов И первой группы, выходы первого и второго узлов памяти соединены соответственно с первым и вторым входами первого сум матора, выход которого соединен с пер вым входом второго сумматора, а третий вход через второй элемент задержки - со входами третьего и четвертого элемента задержки, первым входом первой схемы сравнения и с выходом генератора, первый вход третьего регистра соединен с третьей входной кодовой шиной,о группа выходов - с первыми группами входов второй и первой схем сравнения, вторая группа входов которой соединена с группой выходов узла счета времени, первый выход - с вторым входом регистра, а второй и третий выходы - с первым и вторым входами узла счета времени, третий вход которого соединен с тактовой входной шиной устройства, а выход - с вторым входом второго сумматора, третий вход которого соединен с выходом третьего элемента задержки, а выход - с второй группой входов второй схемы сравнения, третий вход которой соединен с выходом четвертого элемента задержки , а выход - с вторыми входами элементов И четвертой группы. Особенностью предлагаемого устройства является то, что при выборе возможных направлений коммутации учитыва ется критическое (оптимально возможно время доставки сообщений, задаваемое функцией старения сообщения. На фиг, 1 приведена блок-схема пре лагаемого устройства; на фиг, 2 функциональная схема блока временных оценок; на фиг, 3 - функциональная схема первого узла памяти; на фиг, функциональная схема ячейки памяти; на фиг. 5 - функциональная схема второго узла памяти; на фиг. 6 - функциональная схема узла счета времени; на фиг. 7 - функциональная схема первой схемы сравнения. Устройство содержит первую кодовую шину 1, по которой вводятся коды прой денных узлов коммутации в сети связи. первый регистр 2, блок 3 сравнения, элементы И i первой груНпы, второй регистр 5. счетчик 6, элемент ИЛИ 7, вторую кодовую шину 8, по которой вводятся коды допустимых узлов коммутации при организации маршрута сообщения на сети связи; формирователь 9 импульсов, элемент 10 задержки, блок 11 временных оценок, предназначенный для определения времени достав1си сообщения по возможным маршрутам и выбора возможных маршрутов, ге-, нератор 12, шину 13 запуска генератора 12; третью кодовую шину , по которой вводится код критического (оптимального) времени доставки сообщения, тактовую шину 15 по которой подается единая тактовая частота сети связи, определяющая реальное время, узел декодирования 16, элементы И 17, четвертой группы, триггер 18 первой группы, элементы И 19 второй группы, распределитель 20, элементы И 21 третьей группы, информационную шину 22, Ьо которой вводится кодовое слово оообщения для передачи по одному из выбранных направлений выходные шины 23. Функциональная схема блока 11 временных оценок содержит (фиг. 2) первый вход 2 блока, триггеры 25 и 26, второй и третьей групп, первый узел 27 памяти, элемент ИЛИ 28, элементы 29 и 30 пятой и шестой групп, второй узел 31 памяти- дешифратор 32, каждый выход которого однозначно соответствует коду узла коммутации, подаваемому на группу входов 33 блока, первый и второй сумматоры З и 35, второй, третий и четвертый элементы задержки 36-38, первую схему 39 сравнения, первый вход 40 схемы сравнения, третий регистр k , в котором хранится код критического времени доставки сообщения, вторую схему 12 срарнения, узел 3 счета времени, задающий масштаб времени, выход ЦЦ, второй схемы k2 сравнения. Первый узел 27 памяти (фиг. 3) содержит входы k первой группы, узел ячейки 46 памяти, вход k7 второй группы узла, элементы ИЛИ А8 и 9 первой и второй групп, через которые передается код среднего времени доставки сообщения, выход 50 узла 27. Ячейка 46 памяти содержит (фиг, it) регистр 51, элементы И 52, число которых равно разрядности кода, хранящегося в регистре 51, первые 53 и вторые 5 входы, выходы 55 ячейки 46 памяти. Второй узел 31 памяти содержит (фиг, 5) входы 56, элемен79

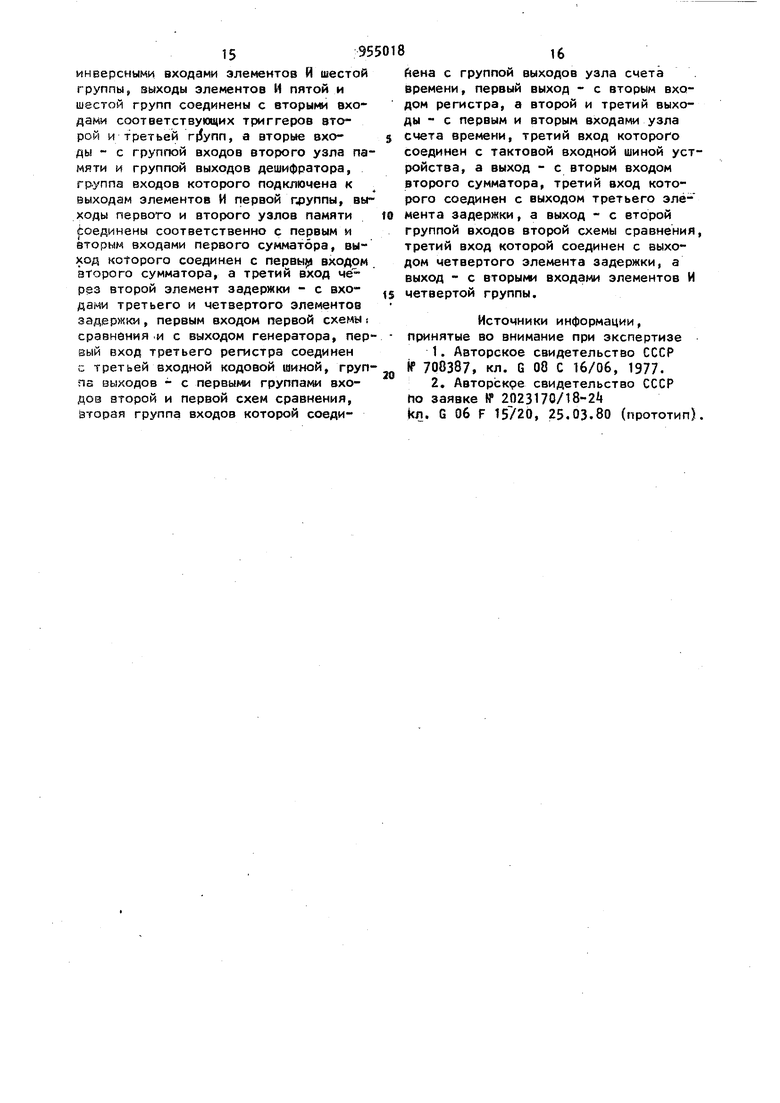

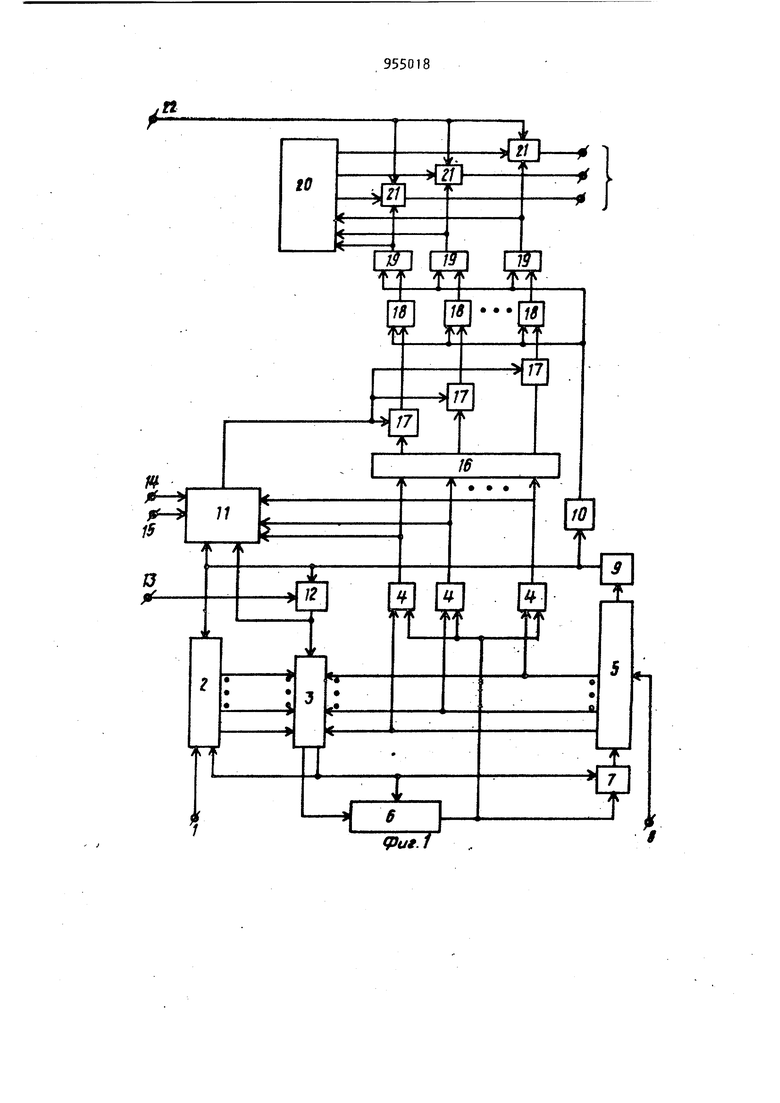

ты И 57, регистры 58, число которых равно п-1, где п - число узлов коммутации в сети связи, выходы 59 второго узла 31 памяти. Узел счета времени содержит (фиг. 6) первый и &торой счетчики 60 и 61, задающие реальное время, причем второй счетчик б1 по разрядности на одну единицу больше первого счетчика 60, дешифратор 62, дешифрирующий нулевое состояние счетчика 60 и сбрасывающий в нулевое состояние счетчик.61, первые выходы 63 узла +3, элементы И б первой,, группы, элементы ИЛИ б5, входы 66 и 67 узла t3, элементы И 68 второй группы, вторые выходы 69 узла 3. Первая схема 39 сравнения содержит входы 70 первой группы, элемент И 71 с инверсным выходом, элементы ИЛИ 72 и 73, элемент И 7, элемент И 75 с инверсным выходом, элемент ИЛИ J6, входы 77 второй группы, элемент ИЛИ 78, элемент И 79, первый и второй выходы 80 и 81, элемент НЕ 82 и третий выход 83 схемы сравнения. ;

Устройство работает следующим образом.

По шине 1 (фиг. 1) вводятся коды пройденных узлов коммутации сообщением по сети связи (не показаны). Причем известно, что максимально воз можное число кодов, определяемое структурой сети, число узлов коммутации на сети и маршрутами сообщений равно N. Коды адресов пройденных узлов коммутации записываются последовательно в регистр 2 в виде последовательностей слов Q., разрядность которых постоянна, а их число не более N. Одновременно по кодовой шине 8 вводятся от управляющей вычислитель-. ной машины (не показана) коды Ь, тех коммутаций, которые допустимы как транзитные при прохождении сообщений от адреса узла коммутации возникновения к адресу узла коммутации назначения данного сообщения. Коды адресов допустимых как транзитные узлов коммутации вводятся в регистр 5.

По окончании ввода кодов по шиНам и 8, по шине 13 запускается генератор 12, который синхронизирует работу блока 3 и блока. 11. Блок 3 осущесвляет сравнение кодов регистра 2 и регистра 5.. По первому импульсу генератора 12 сравниваются коды Ь причем код b.-i есть код узла коммутации назначения. Код Q. не равен коду Ь по символам каждого разряда и на

88

первом выходе блока 3 будет импульс, по которому в счетчик 6 записывается единица, а содержимое регистра 2 (первая кодовая комбинация Q) будет передвинута на последнее место (регистр 2 циклически замкнут), т.е. в регистре 2 будет кодовое слово Q., Q вместо бывшего раньше слова Q, ,...,Q|v(. По второму импульсу от генератора 12 блок 3 сравнивает код Q t и Ь. Коды Q12 и b не равны, снова будет импульс на первом выходе блока 3, по которому в счетчик 6 запишется вторая единица, а кодовое слово в регистре 2 изменится на Qa,...,Q(i. Таким образом, произойдет сравнение всех кодов Q-(,N) с кодом Ь..Счетчик 6 досчитает до N и на его выходе появится импульс, по которому код Ъ-1 поступит через элементы И 4 на узел 16 и на входыблока 11, а через элемент ИЛИ 7 слодо регистра 5 сдвигается влево со стиранием кода Ь , т.е. в регистре 5 будет слово Ь ,...,bj; вместо слова b,.,.,. Счетчик 5 при достижении счета до N автоматически сбрасывается в исходное состояние. Затем по импульсу генератора 12 осуществляется сравнение кодов Q и Ьг, если, например разряды кода Q и b,j равны по символам, то на втором выход блока 3 будет потенциал, который сбросит счетчик 6 в нулевое (исходное) состояние и через элемент ИЛИ 7 сдвинет содержимое регистра 5 влево со |стиранием кода Ь. Таким образом.будет произведено сравнение кодов Q. с каждым из кодов и коды Ь , равные всем кодам Q, будут поданы через элементы И i на входы 16, и блока 11.

Узел 1б устанавливает соответст- . вие коду узла коммутации исходящих направлений передач т.е. определяет номера выходных шин 23 устройства, по которым возможна коммутация сообщений. Так, если к узлу коммутации с кодом Ь, возможна передача по направлениям 23, 239, импульсы будут на первом, втором и четвертом выходах узла 16. Реализуется узел 16 как дешифратор, каждый выход которого однозначно определяет кодовую комбинацию единственного узла коммутации, а выходы дешифратора подсоединены через элементы ИЛИ по закону возможных направлений передач. Например, если к i-му узлу коммутации возможна передача по направлениям 23., 23е , 23, то i-ый выход дешифратора будет подсоединен по входам второго, пятого и шестого элементов ИЛИ, число которых в узле 16 равно числу исходящих шин направлений передач 23. Рассмотрим работу блока 11 времен ных оценок. Первым кодом, подаваемым на вход 33 блока 11 является код узла назначения сообщения. Предварител но по шине Т вводится код критического времени доставки сообщения от вычислительной машины, который записан в заголовке сообщения. Считается . критическим временем тот момент времени, дб которого необходимо передать сообщение. По шине 15 подаются импульсы тактовой частоты, зада ющие реальное время на сети связи. Код узла коммутации назначения дешиф рируется дешифратором 32, на выходе которого появляется потенциал. Кажды выход йешифратора 32 однозначно соот ветствует кодовой комбинации на его входах. Потенциал с одного из выходо дешифратора 32 подается на соответст вующий вход узла 31 памяти и через открытый элемент И 30 перебрасывает один из триггеров 25 в единичное со стояние. При этом через элемент ИЛИ закрываются элементы И 30 и разрешается прохождение импульсов через эле менты И 29 Триггеры 26 находятся в нулевом (исходном) состоянии и с вых да узла 27 памяти снимается пока нулевой код. Отметим, что узел 27 памяти хранит и выдает на сумматор 3 код времени доставки сообщения, одно го передаваемых между узлами коммутации, а узел памяти 31 хранит и выдает код времени доставки сообщения от узла коммутации, на котором стоит данное устройство, до узла коммутации, код которого подан на входы 33. Таким образом, при подаче кЪдов узла назначения сообщения с выхода узла 27 памяти снимается нулевая комбинация, а с выхода узла 31 памяти снимается кодовая комбинация времени доставки сообщения к узлу с кодом Ь, . Узел памяти работает следующим образом (фиг. 5). В регистрах 58 хранятся коды времени доставки сообщений к узлам коммутации сети от данного узла. При поступлении сигнала на один из входов 5б с соответствующих выходов 59 будет снята кодовая комбинация времени доставки сообщения через открытые элементы И 37 Данный код времени доставки будет подан в сумматор 3 и с его выхода этот же код (так как на первом входе сумматора нулевая комбинация) будет подан на первый вход второго сумматора 35, в котором формируется сумма времени доставки к узлу коммутации назначения сообщения и текущего времени , код которого подается от узла . Схема k2 сравнения сравнивает код критического времени, хранящийся в регистре tl и код суммы сумматора 35 и, если код критического времени больше кода сумматора 35 Ro абсолютной величине, то на выходе t схемы 42 сравнения будет потенциал, в противном случае он отсутствует. Задание реального (текущего времени) осуществляется схемой 39 сравнения и узлом . Схема 39 сравнения необходима для того, чтобы контролировать расхождения реального времени и критического времени. Действительно, счетчики отсчета времени имеют конечное число разрядов и при их полном заполнении отсчет начинается с нуля. . Следовательно возможны случаи, когда критическое время задается в последующем интервале отсчета, например кодом 000000101, а отсчет реального времени ведется в существующем интервале отсчета, т.е. в данный моменто код времени 100100110. Либо критическое время задано в предыдущем интервале отсчета, например 111001001, а в настоящий момент идет новый интервал отсчета. Очевидно, что в первом случае необходимо увеличивать разрядность кода реального времени, а во втором случае увеличивать разрядность кода текущего времени. Схема 39 сравнения (фиг. 7) осуществляет выявление данных отклонений. В первом случае на выходе элемента И 72 будет единица, на выходе элемента И 71 будет также едини14а, на выходе элемента ИЛИ 78 будет единица, и на выходе 80 будет потенциал, который будет подан на вход регистра 41 и разрядность кода подаваемого на вход схемы k2 сравнения будет увеличена на диницу, т.е. вместо кода, например 00001010, будет подан код 1000001010, о втором случае код, подаваемый на входы 70 схемы 39 сравнения, по веичине больше кода, подаваемого на входы 77 от узла 43, и тогда потенциал будет на выходе элемента И 74 и : удет отсутствовать на выходе 81. Если же время реального отсчета и критическое время находятся в одном интервале отсчета, то на выходе элемента И 7 потенциала не будет, а будет потенциал на выходе 81. Для надежной работы устройства интервал отсчета должен содержать число разрядов двоичных единиц большее, либо равное двадцати для скорости 9бОО бод, В узле k имеется два счетчика 60 и 61, причем разрядность счетчика 61 на одну единицу больше разрядности счетчика 60. На входы счетчиков 60 и 61 подается синхрочастота со входа 15 причем при полном заполнении счетчика 6П ед., дешифратор 62 дешифрирует это состояние и устанавливает счетчик 61 в исходное состояние, например 1000000000. С выходов счетчика 60 реальное время подается с выходов 63 на входы 77 схемы 39 сравнения. Если на выходе 81 схемы 39 сравнения есть сигнал, т.е. критическое время и реальное в одном интервале отсчета, то на вход 66 подается потенциал и реальное время с выходов счетчика 60 через элементы И б и ИЛИ б5 поступает на выходы б9. Если на выходе 83 схемы 39 сравнения есть сигнал, т.е. критическое время и реальное в разных интервалах отсчета, то сигнал с выхода 83 подается на вход 67 и тогда содержимое счетчика 61 через элементы И 68 и ИЛИ 65 поступает на выходы б9. Стробирование работы схемы 39 сравнения сумматоров 3 и 35 и схемы 2 сравнения осуществляется по заднему фронту импульса генератора 12 который подается на вход ЦО блока 11 и за счет элементов задержки Зб-38 срабатыванке сумматоров 3 и 35 и схем 39 и А2 сравнения разнесено во времени. После кода Ь узла коммутации назначения блок 3 выявляет коды узлов коммутации допустимых как транзитные при передаче сообщения. При поступле нии, например, кодов Ь и Ь-, на входы 33 блока 11 на соответствующем выходах дешифратора 32 будет появляться потенциал. При этом потенциал с выхода дешифратора 32 подается на соответствующий вход узла 31 памяти и через соответствующий элемент И 29 срабатывает триггер 2б. С выхода узла 31 снимается код времени доставки сообщения от данного узла коммутации до четвертого и седьмого узла коммутации с кодом, поданным на вхо. 12 ды 33. С выхода 50 узла памяти сни мается код времени доставки сообщения от узла коммутации,, код которогго подан на входы 33 до узла коммутации назначения сообщения. При этом на соответствующий вход 5 узла 27 памяти подан потенциал от триггера 25, порядковый номер которого соответствует номеру узла коммутации назначения сообщения, а на соответствующий вход 7 подан потенциал от триггера 26, порядковый номер которого соответствует номеру узла коммутации, код которого подан на входы 33. В этом случае содержимое регистра 51 ячейки 46 памяти через открытые элементы И 52 и элементы ИЛИ 8 и ЦЭ подаются на выход 50. В регистрах 51 хранятся коды времени доставки сообщений, передав аемых межДУ узлами коммутаций. Отметим, что если на сети связи имеется N узлов коммутации, то число триггеров 25 равно числу триггеров 2б, числу выходов дешифратора 32, числу входов kS и kj и второй групп входов узла 2 и числу N-1. В сумматоре З определяется сумма кодов времени доставки сообщения до узла назначения через транзитный узел с кодом -Ь,-. Содержимое сумматора 3 суглмируется в сумматоре 35 со временем, заданным узлом 3 и подается на вход схемы 2 сравнения.Схема 42 сравнения сравнивает содержимое сумматора 35 с критическим временем доставки сообщения,хранящимся в регистре 41 ,и если критическое время больше содержимого сумматора 35, то на выходе 44 будет потенциал. Это говорит о том, что сообщение будет доставлено вовремя.Если содержимое суммато-. ра ЗГ больше критического времени, то на. выходе 44 схемы 42 сравнения не будет потенциал. Это говорит о том, что через данный транзитный узел, код которого на входах 33 блока 11, сообщение вовремя доставлено не будет и через него сообщение посылать нельзя. Если с выхода 44 блока 11 есть разрешающий потенциал, то через соответствующие допустимым направлениям передач элементы И 17 будут установлены соответствующие триггеры 18 в единичное состояние по первым входам. Число триггеров 18 равно числу шин исходящих направлений 23 передач узла коммутации. По окончании сравнения кодов (1- с кодами Ь из регист- ра 5 будут списаны все кодовые комбинации, и тогда на выходе формирователя 9 будет импульс, по которому будет остановлен генератор 12, сброшены S нулевое состояние триггеры 25 и 26 и через элемент задержки 10 и открытые элементы И 19 потенциалы с .выходов триггеров 18 будут поданы на входы распределителя 20. По заднему фронту импульса с выхода элемента 10 задержки триггера 18 будут сброшены в исходное нулевое состояние. Распределитель 20 реализует вероятностный или иной способ управления в узле коммутации и выбирает из нескольких разрешенных направлений пер дачи одно. Сигнал управления с выхода распределителя 20 подается на вхо элемента И 21, через который сообщение от информационный шины 22 проход на выбранную выходную шину 23 устрой ства. , Таким образом, предлагаемое устро ;ство обладает более широкими функцио нальными возможностями и это позволя ет улучшить параметры сети, в которо оно используется. В частности, в сети исключаются экономические потери, вызванные задержкой сообщений и доставкой их за время больше критического, когда само сообщение уже устарело и не является достоверным, а также снижается загрузка сети, так как из сети управ ляющей машиной убираются сообщения устаревшие по времени доставки и уменьшается время доставки сообщений так как исключается возможность выбо ра направлений передач, по которым время доставки больше критического времени. Формула изобретения Устройство для управления коммутацией сообщений, содержащее распределитель, первый и второй регистры, блок сравнения, счетчик, первый элемент задержки, генератор, узел кодирования,, группу триггеров, элемент ИЛИ, первую, вторую и третью группы элементов И, формирователь импульсов причем первый вход первого регистра соединен с первой входной кодовой ши ной устройства, а группа выходов с первой группой входов блока сравне ния, вторая группа входов которого соединена с группой выходов второго регистра и с первыми входами элемен8.Ц тов и первой группы, а первый выход с вторым входом первого регистра и с первым входом счетчика, второй вход которого соединен с вторым выходом блока сравнения и с первым входом элемента ИЛИ, второй вход которого соединен с выходом счетчика и с втopы w входами элементов И первой группы, а выход - с первым входом второго регистра, второй вход которого соединен с второй входной ходовой шиной устройства, а выход через формирователь им-, пульсов - с третьим входом первого регистра,входом первого элемента задержки и первым входом генератора, второй вход которого соединен с входной шиной запуска генератора устройства, а выход - с третьим входом блока сравнения, выходы элементов И первой соединены с группой входов узла декодирования, выход первого элемента задержки соединен с первыми входами триггеров первой группы -и .элементов И второй группы, вторые входы которь1Х соединены с выходами соответствующих триггеров первой группы, а выходы - с группой входов распределителя и первыми входами элементов И третьей группы, вторые входы которых соединены с группой выходов распределителя, третьи входы - с входной информационной шиной устройства, а выходы - с группой выходных шин устройства, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения умета времени старения сообщений, в него введены четвертая группа элементов И, вторая и третья группы триггеров, пятая и шестая группы элементов И, дешифратор, первый и второй узлы памяти, второй элемент ИЛИ, первый и второй сумматоры, третий регистр, первая и вторая схемы сравнения, узел счета времени, второй, третий и четвертый элементы задержки, причем группа выходов узла декодирования соединена с первыми входами элементов И четвертой группы, выходы которых соединены с вторыми входами соответствующих триггеров первой группы, первые входы триггеров второй и третьей групп соединены с выходом формирователя импульсов, выходы - соответственно с первой и второй группами входов первого узла памяти, вторая группа входов которого соединена с входами второго элемента ИЛИ, выходом соединенного с первым входами элементов И пятой группы и с 1595 инверсными входами элементов и шестой группы, 8ЫХОДЫ элементов И пятой и шестой групп соединены с вторыми входами соответствующих триггеров второй и третьей riiynn, а вторые входы - с группой входов второго узла памяти и группой выходов дешифратора, гр.уппа входов которого подключена к выходам элементов И первой Г4эуппы, выходы первого и второго узлов памяти :оединены соответственно с первым и вторым входами первого сумматора, выход которого соединен с первы входом второго сумматора, а третий вход чераз второй элемент задержки - с входами третьего и четвертого элементов задержки, первым входом первой схему i сравнения ,и с выходом генератора, первый вход третьего регистра соединен с третьей входной кодовой шиной, группа выходов - с первыми группами входов второй и первой схем сравнения, йторзя группа входов которой соедийена с группой выходов узла счета времени, первый выход - с вторым входом регистра, а второй и третий выходы - с первым и вторым входами узла счета времени, третий вход которого соединен с тактовой входной шиной устройства, а выход - с вторым входом второго сумматора, третий вход которого соединен с выходом третьего элемента задержки, а выход - с второй группой входов второй схемы сравнения, третий вход которой соединен с выходом четвертого элемента задержки, а выход - с вторыми входами элементов И четвертой группы. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 708387, кл. G 08 С 16/06, 1977. 2.Авторскре свидетельство СССР ho заявке № 2023170/18-2 йл. G 06 F 15/20, 25,03.80 (прототип).

V

3J

Фи.г

ж

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования маршрутов сообщений и управления процессом коммутации в сети связи | 1980 |

|

SU922757A1 |

| Устройство для коммутации информационных каналов | 1981 |

|

SU1003123A1 |

| Устройство для сопряжения дискретных датчиков с электронной вычислительной машиной | 1982 |

|

SU1024898A2 |

| Устройство для приема информации | 1982 |

|

SU1022204A1 |

| Устройство для коррекции нелинейности | 1982 |

|

SU1056228A1 |

| Устройство декодирования циклических кодов | 1990 |

|

SU1735996A2 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| Устройство для передачи и приема кодированного сигнала изображения | 1989 |

|

SU1686706A1 |

| Устройство для коммутации сообщений | 1983 |

|

SU1161979A1 |

| Устройство для контроля и диагностики логических блоков | 1984 |

|

SU1295401A1 |

Щ

Ж

f

7

41

-j

tfS

И A

.

49

vA

.. .

фиг.З

g)u9.4

У

ЛГ

pu9.5

i6

Авторы

Даты

1982-08-30—Публикация

1980-11-12—Подача