05 СП

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО АДАПТИВНОГО КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ | 2000 |

|

RU2169431C1 |

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ КОДОМ ПЕРЕМЕННОЙ ДЛИНЫ | 1996 |

|

RU2123765C1 |

| Устройство декодирования циклических кодов | 1987 |

|

SU1496009A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ КАСКАДНОГО КОДА РИДА-СОЛОМОНА | 1993 |

|

RU2036512C1 |

| Устройство защиты от ошибок внешней памяти | 1981 |

|

SU1018119A1 |

| Устройство для декодирования линейных кодов | 1985 |

|

SU1287297A1 |

| Функциональный генератор | 1979 |

|

SU781839A1 |

| Устройство обнаружения и исправления ошибок в кодах Рида-Соломона | 1986 |

|

SU1381719A1 |

| Устройство для исправления ошибок | 1984 |

|

SU1216832A1 |

| Устройство для исправления ошибок | 1987 |

|

SU1432787A1 |

Изобретение относится к технике связи и может быть применено в системах передачи информации при построении дискретного канала (как декодирующее устройство кодов различной корректирующей способности с обнаружением ошибок). Цель изобретения - расширение функциональных возможностей путем кодирования кодов 1Р

to зъ

к

15к Фиг1

переменной длины Устройство содержит группу управляющих входов кодер 2 полинома, перестраиваемый счетчик 3, коммутатор , канальный коммутатор 5, канальный выход 6 устройства , вход 7 управления.декодированием устройства, вход В управления кодированием устройства, ключ 9 упИзобретение относится к технике связи и может быть применено в систмах передачи информации при построении дискретного канала как декодирующее и кодирующее устройство кодов различной корректирующей способности с обнаружением ошибок

Известно устройство для декодирования циклических кодов, содержащее первый и второй регистры, блок фазирования по тактам, первый и второй распределители импульсов, первый - пятый элементы И, блок декодирования блок выявления ошибок, блок элементо И, первый и второй блоки элементов ИЛИ, первый, второй и третий элементы ИЛИ, первый и второй триггеры

Известное устройство можно приме- нить только для декодирования кодов постоянно заданной корректирующей (способности и нельзя использовать дл кодирования и декодирования кодов, корректирующая способность которых адаптивно изменяется при изменении помеховой обстановки в канале

Известно декодирующее устройство, содержащее первый - четвертый ре- гистры памяти, первый и второй i счетчики, элемент ЗАПРЕТ, элемент И, сумматор по модулю два, блок сравнения, генератор кодовых слов, первый и второй ключи

Недостаток известного устройства состоит в ограниченных его функциональных возможностях Действительно известное устройство не может быть использовано при изменении длины кода в случае необходимости изменения его корректирующей способности.

Наиболее близким к предлагаемому устройство декодирования циклических кодов, содержащее кодер полинома, перестраиваемый счетчик, коммутатор, перестраиваемый регистр памяти, генератор тактовых импульсов, элемент ИЛИ-НЕ, элемент Ис

17359964

равления, информационный вход 10 устройства, сумматор 11 по модулю два, вычислитель 12 синдрома, пере- страиваемый регистр 13 памяти, генератор 1 тактовых импульсов, группу информационных выходов устройства 15т -15)-.. элемент И 16, элемент ИЛИ-НЕ 17. 2 з„п ф-лы, 9 ил„

5

5

0

5

0

S

0

5

Известное устройство обладает недостатком, состоящим в следующем. При передаче сообщений различного назначения, например, команды телеуправления, телесигнализации, сигналы телеметрии, аварийной сигнализации и прочее, используются системы передачи дискретной информации, в приемопередающих комплектах которых необходимо наличие устройств защиты от ошибок, которые кодируют и декодируют информацию, передаваемую кодами переменной длины. Известные устройства предназначены для передачи информации кодами постоянной корректирующей способности (постоянной длины) , что ограничивает их функциональные возможности, в то время как для передачи сообщений различного назначения требуются устройства, которые бы применяли коды различной коррвк- тирующей способности.

Цель изобретения состоит в расширении функциональных возможностей путем кодирования кодов переменной длины

Цель достигается тем, что в устройство декодирования циклических кодов дополнительно введены сумматор по модулю два, ключ управления и между информационным входом устройства и информационным входом коммутатора соответственно информационными входами и выходом введен канальный коммутатор, управляющий вход и вход- выход которого являются соответственно входом управления декодированием и номинальным входом-выходом устройства, первый управляющий вход и первый и второй информационные входы ключа управления подключены соответственно к второму выходу перестраиваемого счетчика, второму информационному входу вычислителя синдрома и второму информационному входу канального коммутатора, второй управ5t735396

ляющий вход которого объединен с одU п

ноименным входом ключа управления и является входом управления кодированием устройства, третий управляющий и информационные входы ключа управления подключены соответственно к третьему выходу перестраиваемого счет чика и выходу сумматора по модулю два, первый и второй входы которого подключены соответственно к соответствующему выходу вычислителя синдрома и информационному входу устройства. Канальный коммутатор содержит элемент ИЛИ и первый и второй элементы И, первые входы которых и первый и второй входы элемента ИЛИ являются Ъэответственно первым и вторым информационными входами блока, выход элемента ИЛИ подключен к второму входу второго элемента И, выход которого подключен к второму входу первого элемента И и вляется входом- выходом блока, выход первого элемента И подключен к информационному выходу блока. Ключ управления содержит триггер, первый, второй и третий элементы И, причем первый управляющий вход соединен с первым входом первого элемента И, второй вход которого соединен с вторым управляющим входом ключа, а выход - с единичным выходом триггера, нулевой вход которого соединен с третьим управляющим входом ключа, информационный вход которого соединен с первыми входами

второго и третьего элементов И, выход первого элемента И соединен с

первым информационным выходом ключа, а второй вход - с единичным выходом триггера, нулевой выход которого соединен с вторым входом третьего элемента И, выход которого соединен с вторым информационным выходом ключа управления.

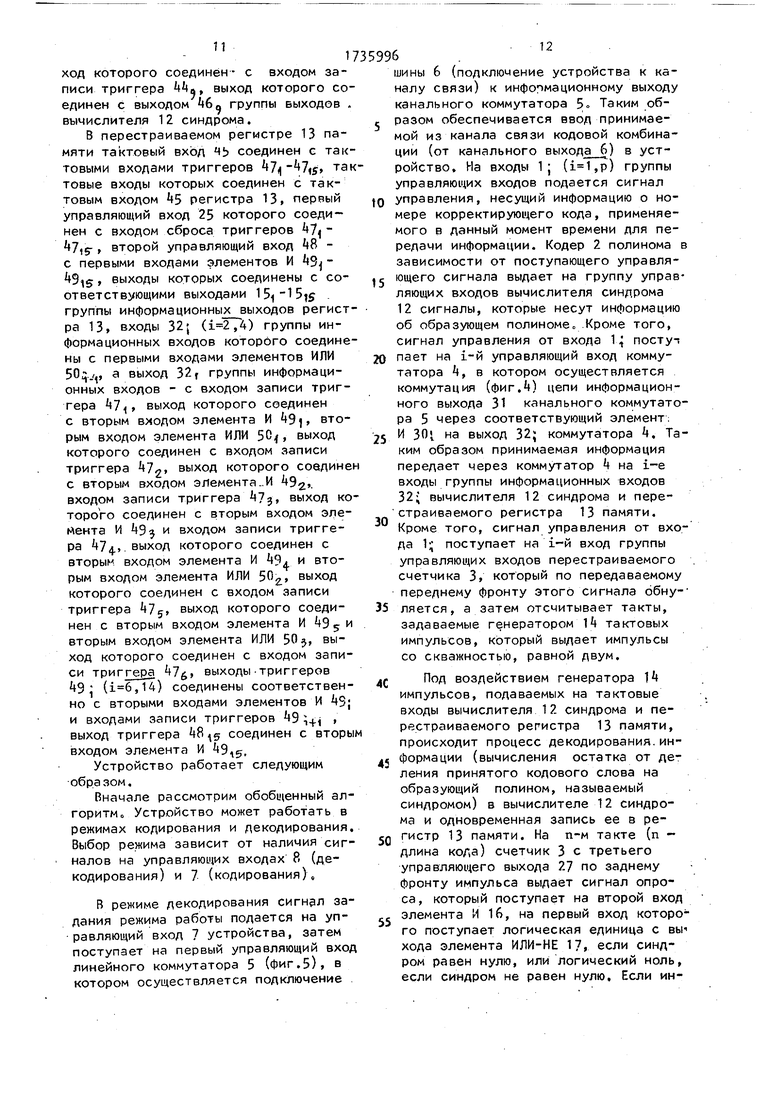

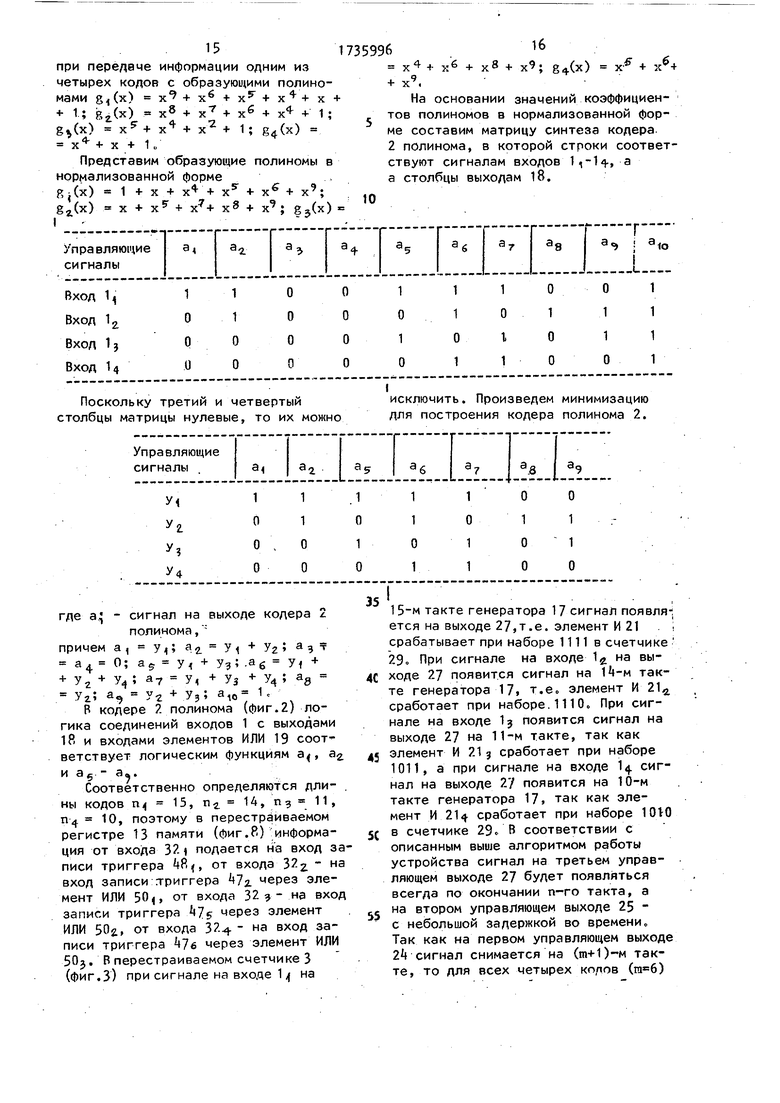

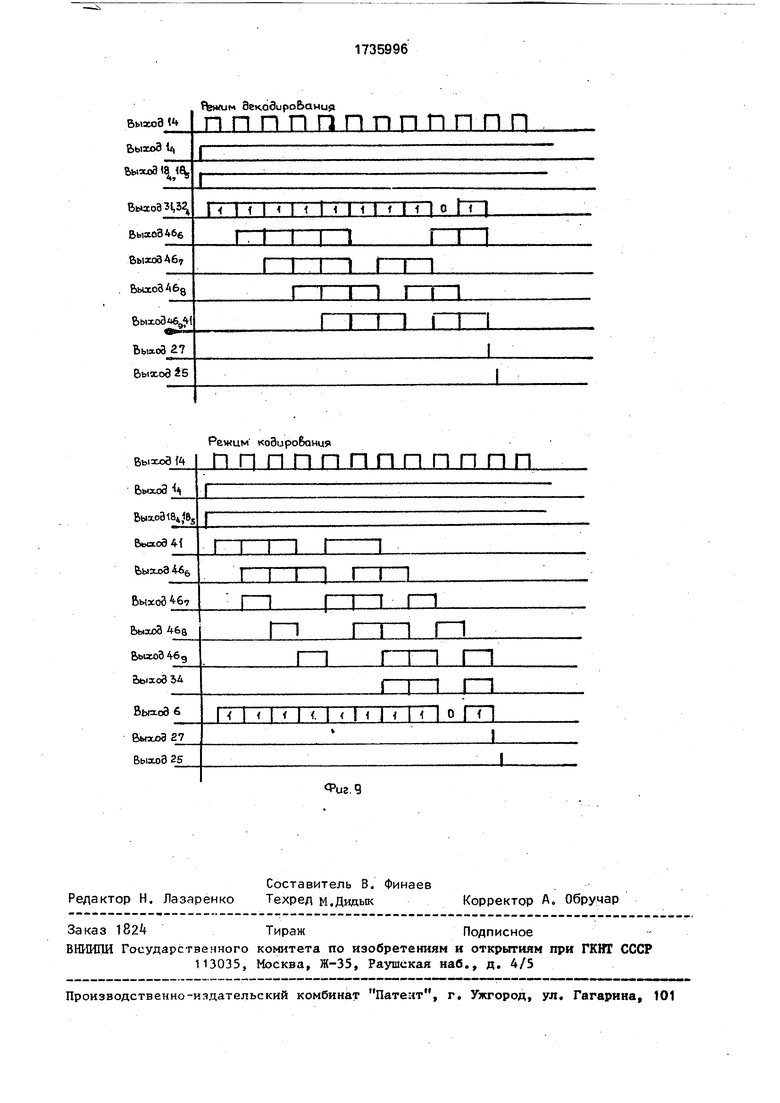

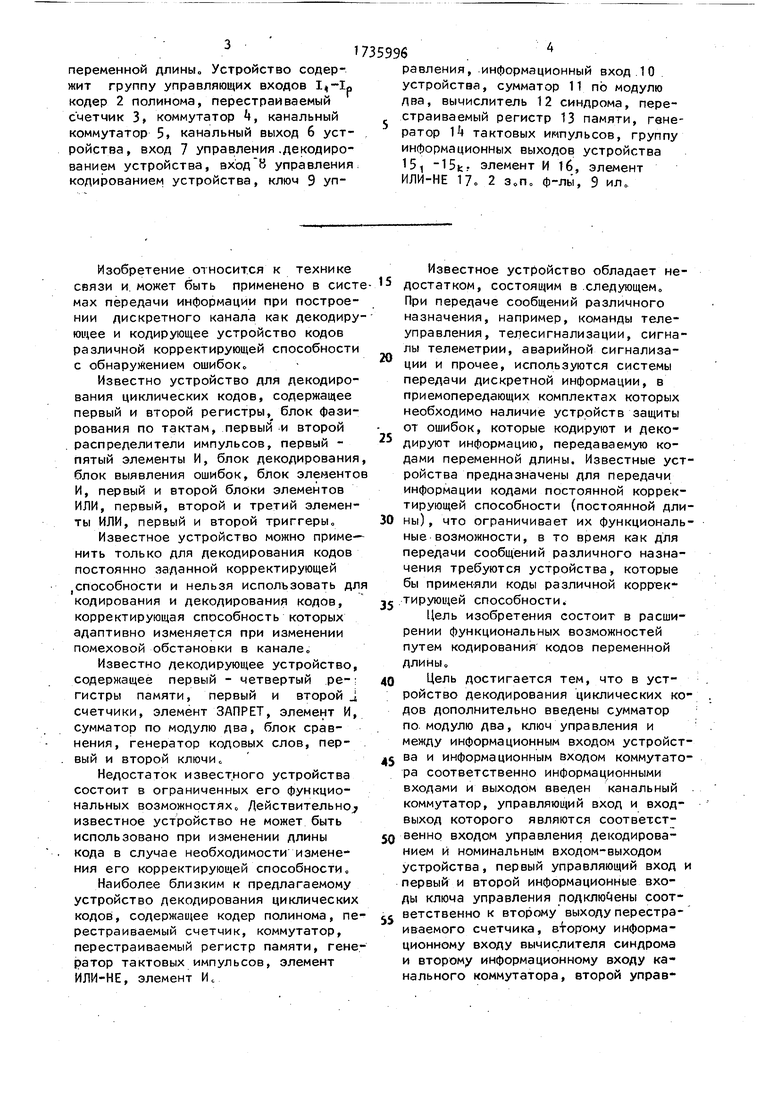

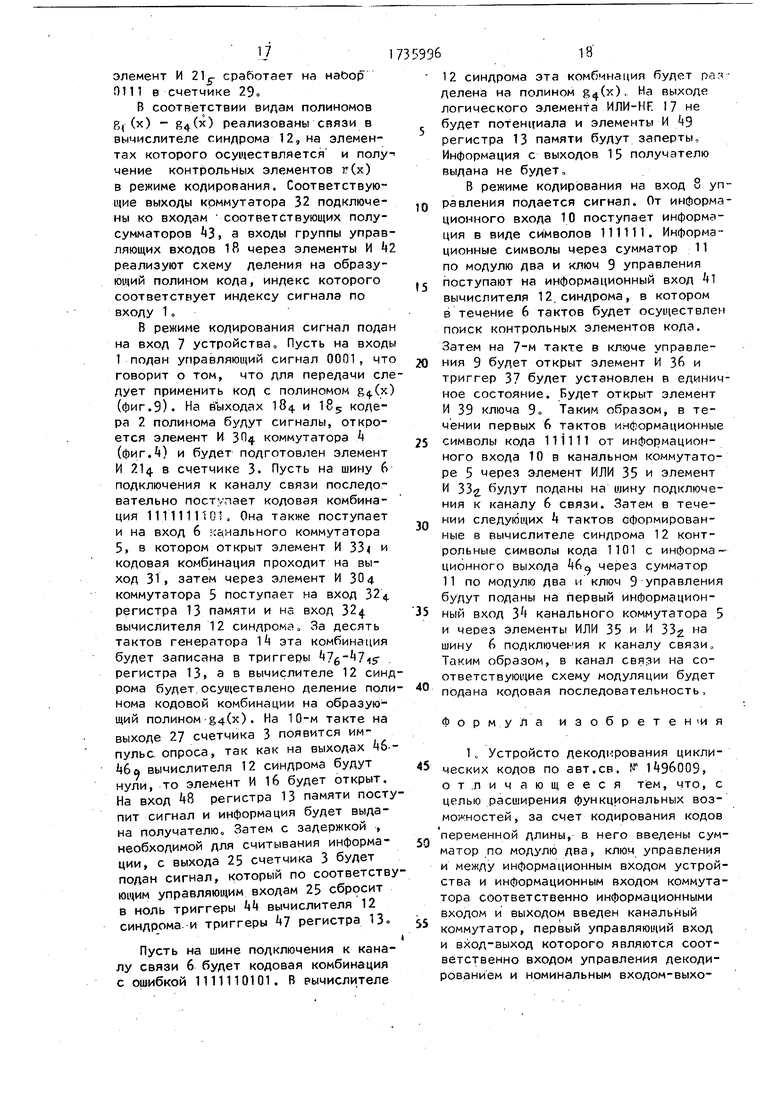

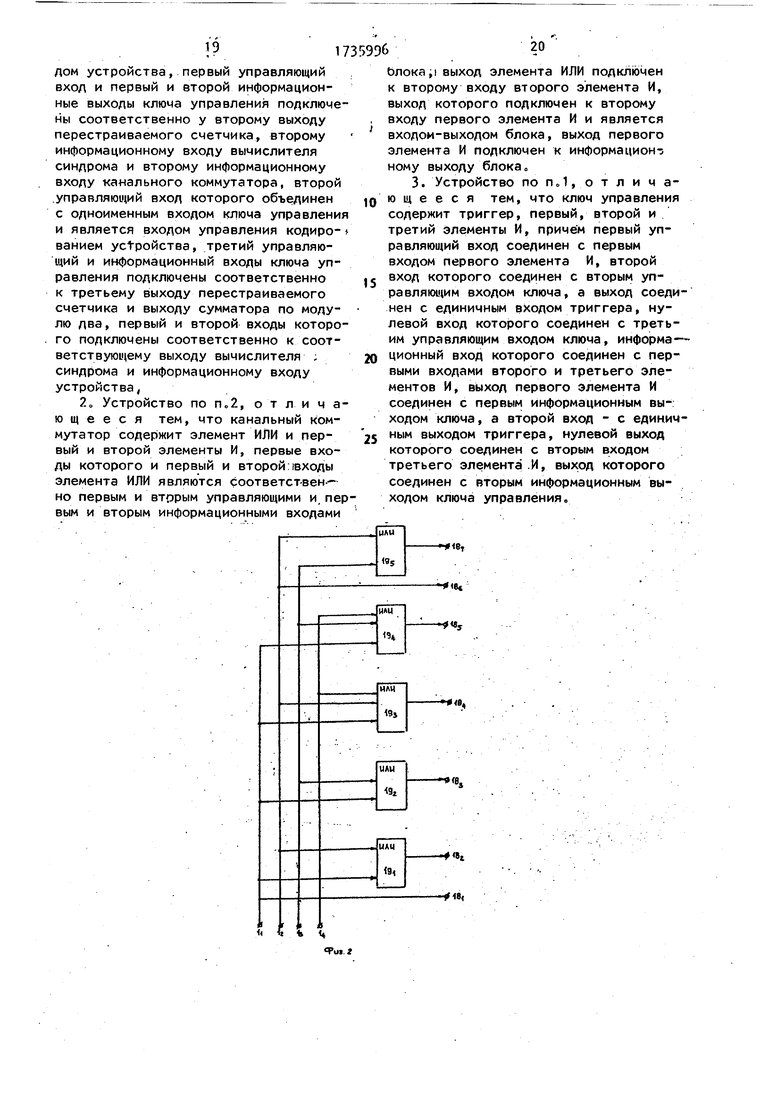

На фиг,1 приведена блок-схема устройства; на фиг,2 - функциональная схема кодера полинома; на фиг.З - функциональная схема перестраиваемого счетчика; на фиг Л - функциональная схема коммутатора; на фиг,5 функциональная схема канального коммутатора; на фиг,6 - функциональная схема ключа управления; на фиг„7 - функциональная схема вычислителя

Синдрома; на фиг,8 - функциональная i

схема перестраиваемого регистра памяти; на фиг.9 - временные диаграммы, поясняющие работу устройства.

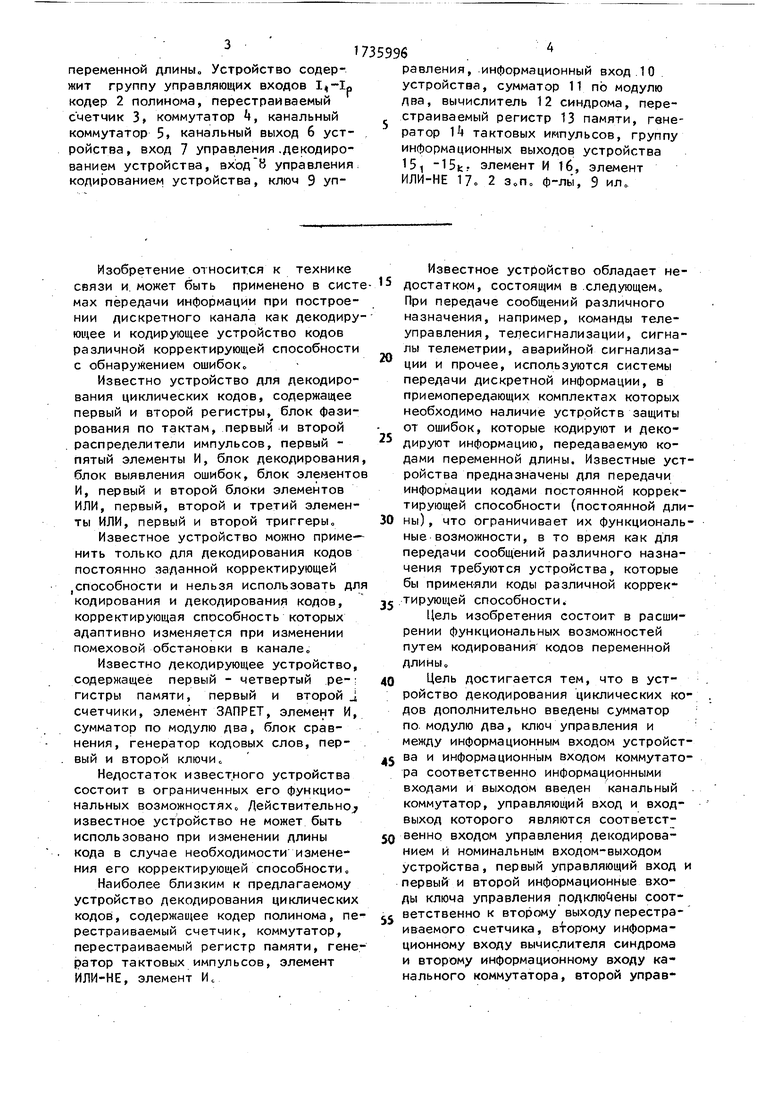

Блок-схема устройства декодирования (фиг01) содержит группу управля- ющих входов 1ц-1ь, кодер 2 полиномов, U перестраиваемый счетчик 3, коммутатор k, канальный коммутатор 5, канальный выход 6, вход 7 управления декодированием, вход 8 управления кодированием, ключ 9 управления, информационт

ный вход 10, сумматор 11 по модулю два, вычислитель 12 синдрома. перестраиваемый регистр 13 памяти, генератор Ik тактовых импульсов, группу информационных выходов ,

5 элемент И 16, элемент ИЛИ-НЕ 17.

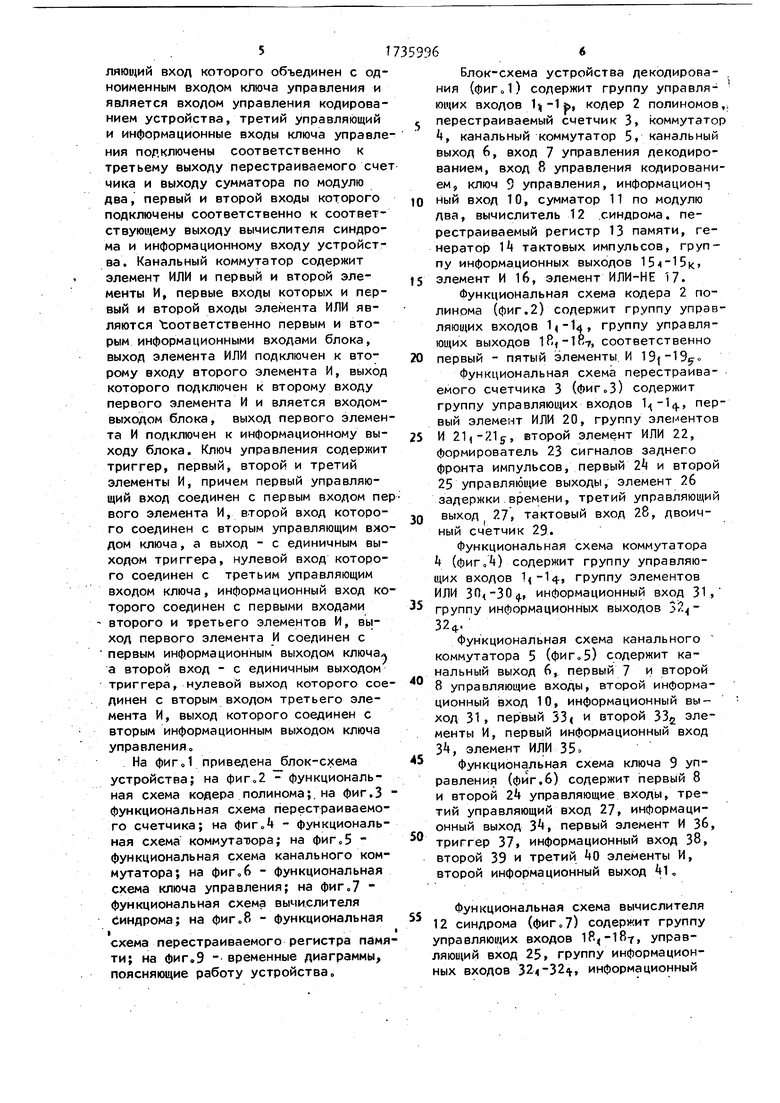

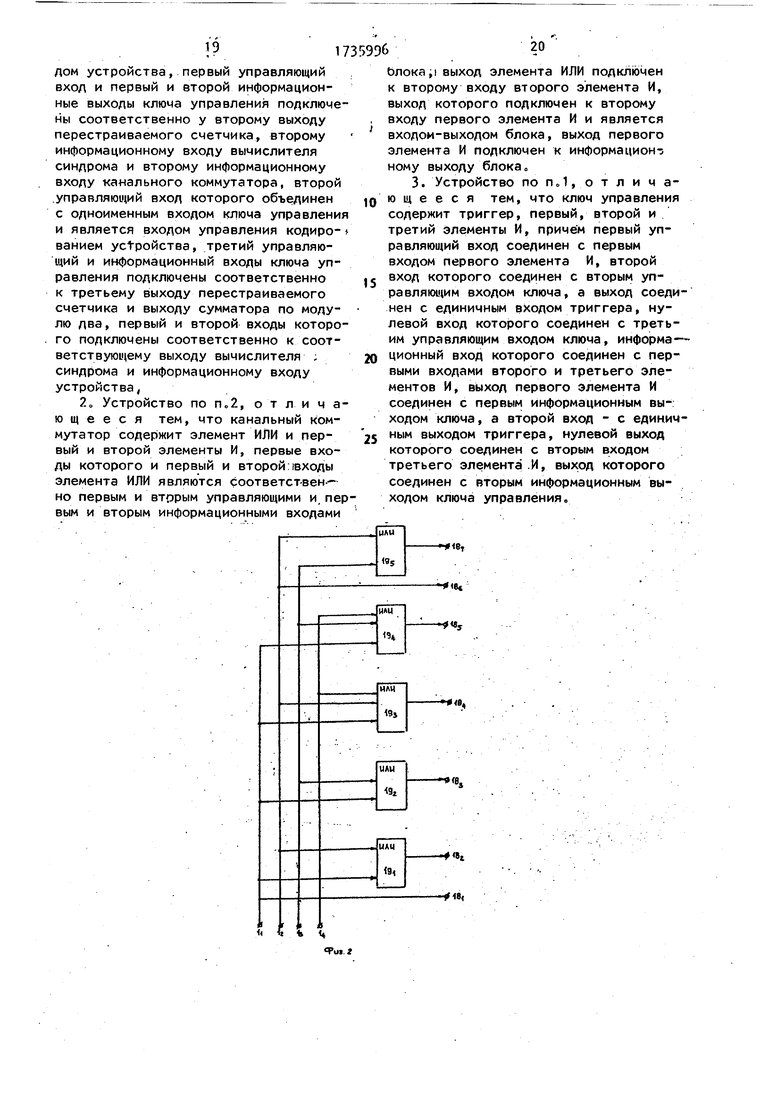

Функциональная схема кодера 2 полинома (фиг.2) содержит группу управляющих входов группу управляющих выходов 18(-1Й7 соответственно

0 первый - пятый элементы И 19(

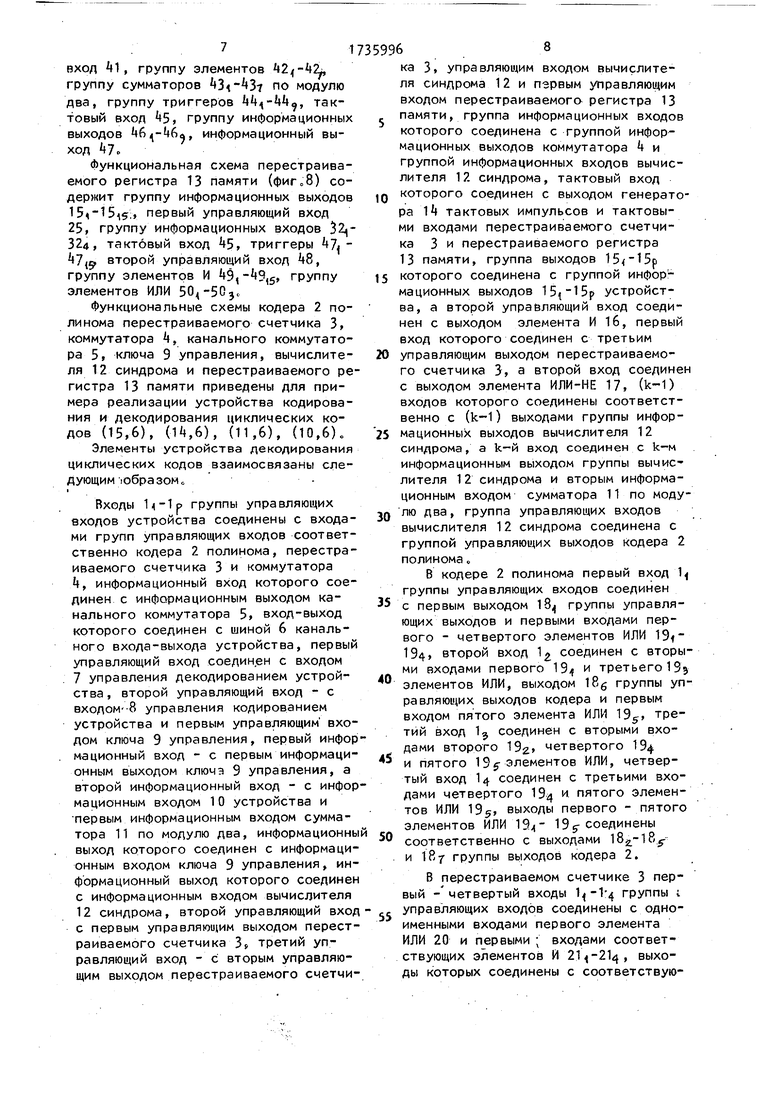

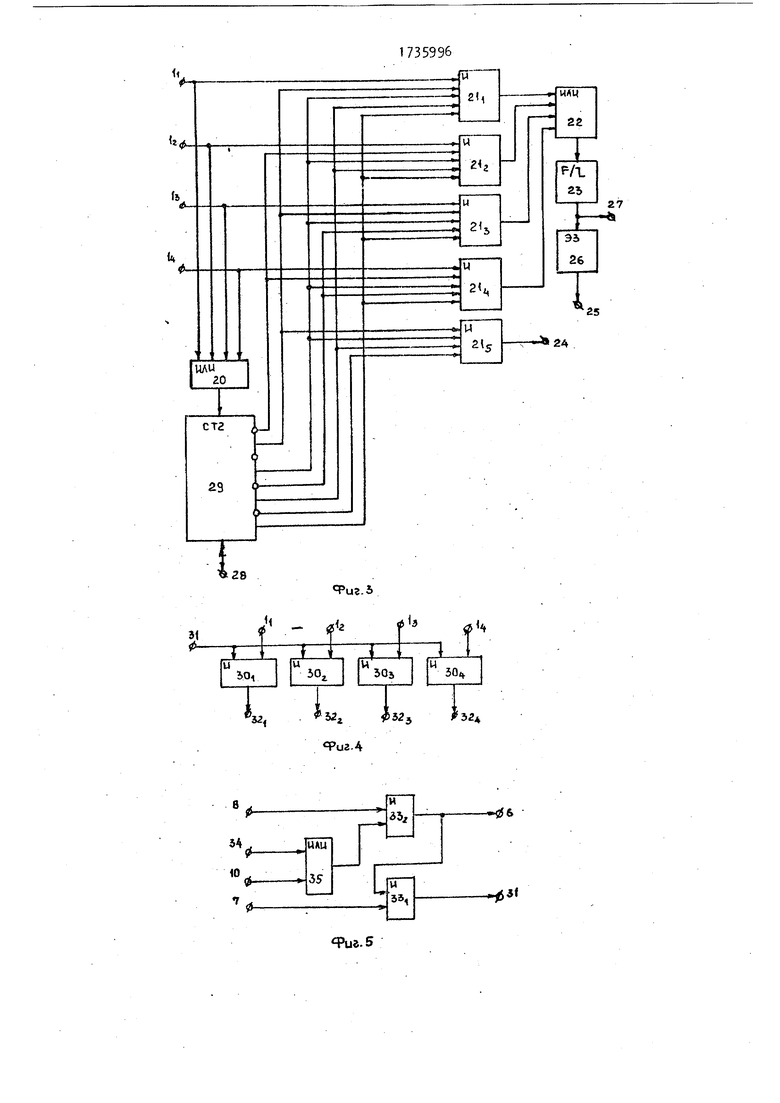

Функциональная схема перестраиваемого счетчика 3 (фиг.З) содержит группу управляющих входов ., первый элемент ИЛИ 20, группу элементов

5 И 21,-215, второй элемент ИЛИ 22, формирователь 23 сигналов заднего фронта импульсов, первый 2k и второй 25 управляющие выходы, элемент 26 задержки времени, третий управляющий

о выход 27, тактовый вход 28, двоичный счетчик 29.

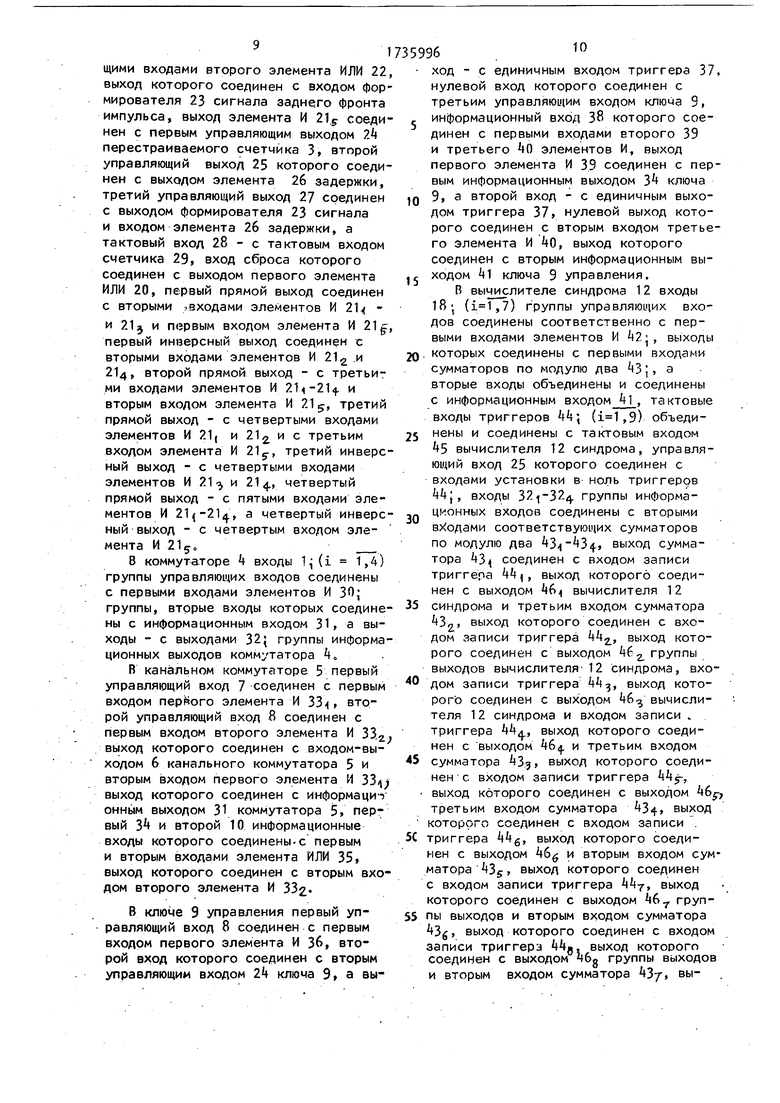

Функциональная схема коммутатора k (фиго ) содержит группу управляющих входов группу элементов ИЛИ 304-30 j., информационный вход 31,

группу информационных выходов

32 4Функциональная схема канального коммутатора 5 (фиг,5) содержит канальный выход 6, первый 7 и второй 8 управляющие входы, второй информационный вход 10, информационный выход 31 , первый 33 и второй 332 элементы И, первый информационный вход 3k, элемент ИЛИ 35

Функциональная схема ключа 9 управления (фиг.6) содержит первый 8 и второй 2k управляющие входы, третий управляющий вход 27, информационный выход 3k, первый элемент И 36, триггер 37, информационный вход 38, второй 39 и третий АО элементы И, второй информационный выход А1„

0

5

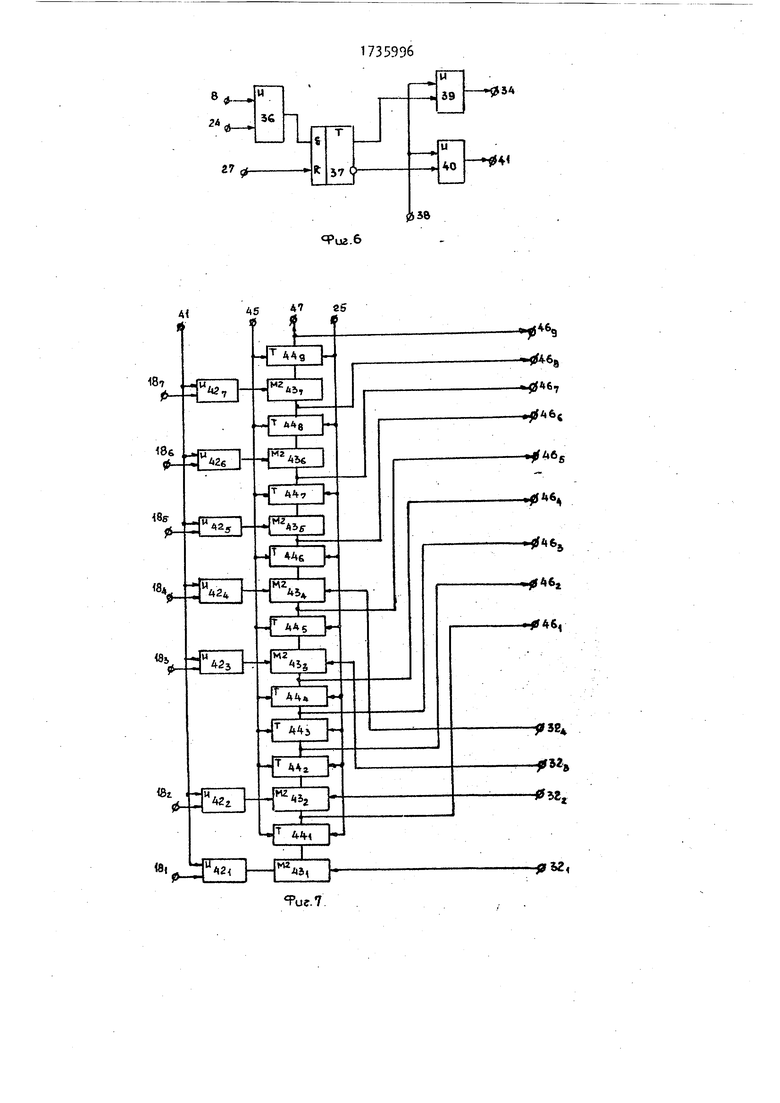

Функциональная схема вычислителя 12 синдрома (фиг о 7) содержит группу управляющих входов , управляющий вход 25, группу информационных входов , информационный

вход 41, группу элементов 42J-42- группу сумматоров по модулю два, группу триггеров , тактовый вход 45, группу информационных выходов 46,j-46a, информационный выход 47

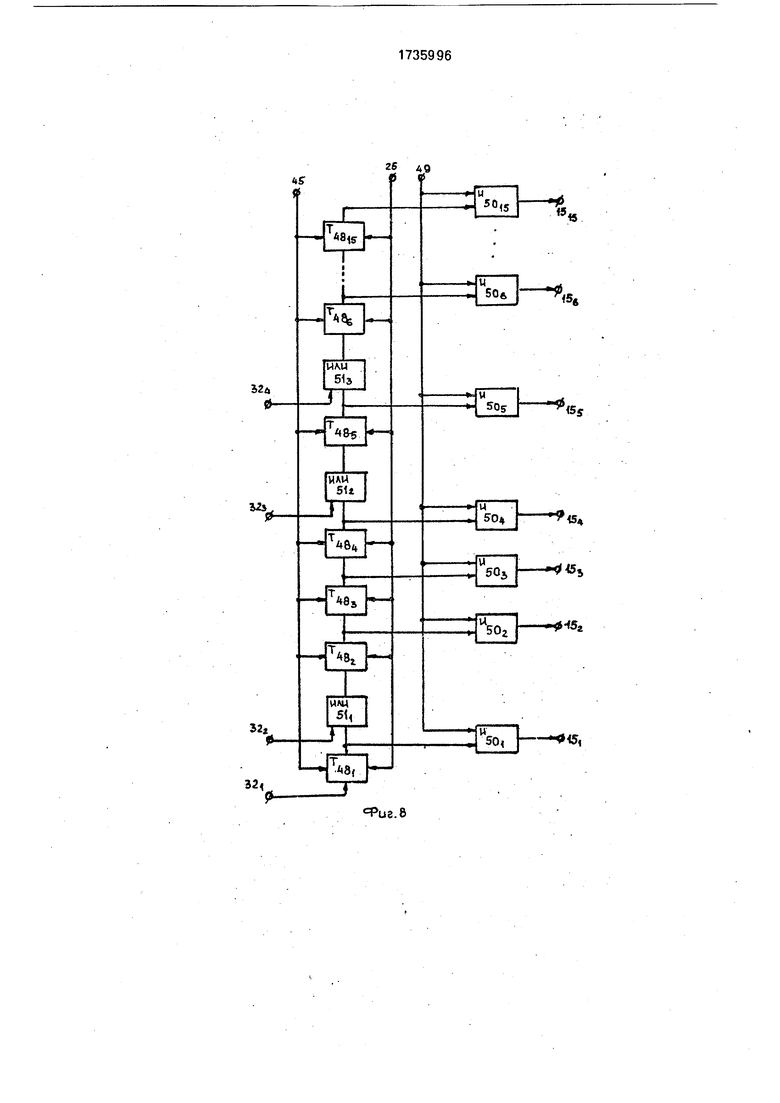

«Функциональная схема перестраиваемого регистра 13 памяти (фиг,8) содержит группу информационных выходов 15 -15i5 первый управляющий вход 25, группу информационных входов 324, тактовый вход 45, триггеры kj, - , второй управляющий вход 48, группу элементов И 49,-49,5, группу элементов ИЛИ 504-50э

Функциональные схемы кодера 2 полинома перестраиваемого счетчика 3, коммутатора 4, канального коммутатора 5, ключа 9 управления, вычислителя 12 синдрома и перестраиваемого регистра 13 памяти приведены для примера реализации устройства кодирования и декодирования циклических кодов (15,6), (14,6), (11,6), (10,6).

Элементы устройства декодирования циклических кодов взаимосвязаны следующим .образом о

Входы группы управляющих входов устройства соединены с входами групп управляющих входов соответственно кодера 2 полинома, перестраиваемого счетчика 3 и коммутатора 4, информационный вход которого соединен с информационным выходом канального коммутатора 5, вход-выход которого соединен с шиной 6 канального входа-выхода устройства, первый управляющий вход соединен с входом 7 управления декодированием устройства, второй управляющий вход - с входом-8 управления кодированием устройства и первым управляющим входом ключа 9 управления, первый информационный вход - с первым информационным выходом ключа 9 управления, а второй информационный вход - с информационным входом 10 устройства и первым информационным входом сумматора 11 по модулю два, информационны выход которого соединен с информационным входом ключа 9 управления, информационный выход которого соединен с информационным входом вычислителя

12 синдрома, второй управляющий вход- ,-суправляющих входов соединены с однос первым управляющим выходом перест-именными входами первого элемента

раиваемого счетчика 3, третий уп-ИЛИ 20 и первыми ; входами соответ

равляющий вход - с вторым управляю-ствующих элементов И , выхощим выходом перестраиваемого счетчи-ды которых соединены с соответствую

й

10

15

20

25

7359968

ка 3, управляющим входом вычислителя синдрома 12 и пэрвым управляющим входом перестраиваемого регистра 13 памяти, группа информационных входов которого соединена с группой информационных выходов коммутатора 4 и группой информационных входов вычислителя 12 синдрома, тактовый вход которого соединен с выходом генератора 14 тактовых импульсов и тактовыми входами перестраиваемого счетчика 3 и перестраиваемого регистра 13 памяти, группа выходов которого соединена с группой информационных выходов устройства, а второй управляющий вход соединен с выходом элемента И 16, первый вход которого соединен с третьим управляющим выходом перестраиваемого счетчика 3, а второй вход соединен с выходом элемента ИЛИ-НЕ 17, (k-1) входов которого соединены соответственно с (k-1) выходами группы информационных выходов вычислителя 12 синдрома, a k-и вход соединен с k-м информационным выходом группы вычислителя 12 синдрома и вторым информационным входом сумматора 11 по модулю два, группа управляющих входов вычислителя 12 синдрома соединена с группой управляющих выходов кодера 2 полинома„

В кодере 2 полинома первый вход 1 группы управляющих входов соединен

$5 с первым выходом 18,) группы управляющих выходов и первыми входами первого - четвертого элементов ИЛИ 194 второй вход 1 соединен с вторыми входами первого 19 и третьего 19j

® элементов ИЛИ, выходом 18 группы управляющих выходов кодера и первым входом пятого элемента ИЛИ 195, третий вход 19 соединен с вторыми входами второго 19Z, четвертого 194

3 и пятого 19$- элементов ИЛИ, четвертый вход 14 соединен с третьими входами четвертого 194 и пятого элементов ИЛИ 195 выходы первого - пятого элементов ИЛИ 19 g-соединены соответственно с выходами и 18/ группы выходов кодера 2.

В перестраиваемом счетчике 3 первый - четвертый входы группы ;

30

50

1

щими входами второго элемента ИЛИ 22, выход которого соединен с входом формирователя 23 сигнала заднего фронта импульса, выход элемента И 21$ соединен с первым управляющим выходом 24 перестраиваемого счетчика 3, второй управляющий выход 25 которого соединен с выходом элемента 26 задержки, третий управляющий выход 27 соединен с выходом формирователя 23 сигнала и входом элемента 26 задержки, а тактовый вход 28 - с тактовым входом счетчика 29, вход сброса которого соединен с выходом первого элемента ИЛИ 20, первый прямой выход соединен с вторыми .входами элементов И 21 - и 21 и первым входом элемента И 21g:, первый инверсный выход соединен с вторыми входами элементов И 212 и 214, второй прямой выход - с третьими входами элементов И и вторым входом элемента И 21 5, третий прямой выход - с четвертыми входами элементов И 21( и 212 и с третьим входом элемента И 21, третий инверсный выход - с четвертыми входами элементов И 21 и 21., четвертый прямой выход - с пятыми входами элементов И 21 (-21,, а четвертый инверсный выход - с четвертым входом элемента И 21 у,

В коммутаторе 4 входы 1(1 1,4) группы управляющих входов соединены с первыми входами элементов И 30; группы, вторые входы которых соединены с информационным входом 31, а выходы - с выходами 32, группы информационных выходов коммутатора 4

В канальном коммутаторе 5 первый управляющий вход 7 соединен с первым входом первого элемента И 33, второй управляющий вход Я соединен с первым входом второго элемента И 33 выход которого соединен с входом-выходом 6 канального коммутатора 5 и вторым входом первого элемента И выход которого соединен с информаци-г онным выходом 31 коммутатора 5 первый 34 и второй 10 информационные входы которого соединены-с первым и вторым входами элемента ИЛИ 35 выход которого соединен с вторым входом второго элемента И 33Ј.

В ключе 9 управления первый управляющий вход 8 соединен с первым входом первого элемента И 36, второй вход которого соединен с вторым управляющим входом 2 ключа 9, а выг

3599610

- ход - с единичным входом триггера 37, нулевой вход которого соединен с третьим управляющим входом ключа 9, информационный вход 38 которого соединен с первыми входами второго 39 и третьего 40 элементов И, выход первого элемента И 39 соединен с первым информационным выходом 34 ключа 9, а второй вход - с единичным выходом триггера 37, нулевой выход которого соединен с вторым входом третьего элемента И 40, выход которого соединен с вторым информационным выходом 41 ключа 9 управления.

В вычислителе синдрома 12 входы 18 -, (,7) группы управляющих входов соединены соответственно с первыми входами элементов И , выходы

10

15

30

35

20 которых соединены с первыми входами сумматоров по модулю два 43, а вторые входы объединены и соединены с информационным входом 4j , тактовые входы триггеров 44, (,9) объеди25 нены и соединены с тактовым входом 45 вычислителя 12 синдрома, управляющий вход 25 которого соединен с входами установки в ноль триггеров 44j, входы группы информационных входов соединены с вторыми входами соответствующих сумматоров по модулю два ., выход сумматора 43 соединен с входом записи триггера 44, выход которого соединен с выходом 46 вычислителя 12 синдрома и третьим входом сумматора 43г, выход которого соединен с входом записи триггера 442, выход которого соединен с выходом 4f группы выходов вычислителя112 синдрома, дом записи триггера 44 , выход которого соединен с выходом 46- вычислителя 12 синдрома и входом записи .. триггера 44, выход которого соединен с выходом 46ф и третьим входом

45 сумматора 43д, выход которого соединен с входом записи триггера 44, выход которого соединен с выходом ,

третьим входом сумматора 43 выход которого соединен с входом записи

5С триггера 44б, выход которого соединен с выходом 46g и вторым входом сумматора 435, выход которого соединен с входом записи триггера 44, выход которого соединен с выходом 46 7 груп55 пы выходов и вторым входом сумматора 43g, выход которого соединен с входом записи триггера 44. выход которого соединен с выходом 46g группы выходов

и вторым входом сумматора 43/ вы

ход

которого соединен чч,

входом записи триггера чча, выход которого соединен с выходом Чб« группы выходов . вычислителя 12 синдрома.

В перестраиваемом регистре 13 памяти тактовый вход ЧЬ соединен с тактовыми входами триггеров 1& та товые входы которых соединен с тактовым входом 45 регистра 13, первый управляющий вход 25 которого соединен с входом сброса триггеров ч7 - 47,5- второй управляющий вход ч8 - с первыми входами элементов И , выходы которых соединены с соответствующими выходами группы информационных выходов регистра 13, входы 32; () группы информационных входов которого соединены с первыми входами элементов ИЛИ 50., а выход 32 г группы информационных входов - с входом записи триггера 47 , выход которого соединен с вторым входом элемента И 49 j, вторым входом элемента ИЛИ 50{, выход которого соединен с входом записи триггера Ч72, выход которого соедине с вторым входом элемента.И Ч92, входом записи триггера 47$, выход которого соединен с вторым входом элемента И 49 и входом записи триггера 47 4. выход которого соединен с вторым входом элемента И . и вторым входом элемента ИЛИ 50 2, выход которого соединен с входом записи триггера Ч75, выход которого соединен с вторым входом элемента И 49 и вторым входом элемента ИЛИ 50$, выход которого соединен с входом записи триггера 47$, выходы триггеров 49 (,14) соединены соответственно с вторыми входами элементов И 49; и входами записи триггеров 49 + , выход триггера ч8 $ соединен с вторы входом элемента И Ч915.

Устройство работает следующим образом.

Вначале рассмотрим обобщенный алгоритм. Устройство может работать в режимах кодирования и декодирования. Выбор режима зависит от наличия сигналов на управляющих входах 8 (декодирования) и 7 (кодирования),

В режиме декодирования сигнал задания режима работы подается на управляющий вход 7 устройства, затем поступает на первый управляющий вход линейного коммутатора 5 (фиг.5), в котором осуществляется подключение

5

5

0

5

С

5

0

5

шины 6 (подключение устройства к каналу связи) к информационному выходу канального коммутатора 5° Таким образом обеспечивается ввод принимаемой из канала связи кодовой комбинации (от канального выхода 6) в устройство. На входы 1j (,p) группы управляющих входов подается сигнал управления, несущий информацию о номере корректирующего кода, применяемого в данный момент времени для передачи информации. Кодер 2 полинома в зависимости от поступающего управляющего сигнала выдает на группу управляющих входов вычислителя синдрома 12 сигналы, которые несут информацию об образующем полиноме„ Кроме того, сигнал управления от входа 1 постут пает на i-й управляющий вход коммутатора Ч, в котором осуществляется коммутация (фиг.ч) цепи информационного выхода 31 канального коммутатора 5 через соответствующий элемент И на выход 32; коммутатора Ч. Таким образом принимаемая информация передает через коммутатор Ч на 1-е входы группы информационных входов 32; вычислителя 12 синдрома и перестраиваемого регистра 13 памяти. Кроме того, сигнал управления от входа 1 поступает на i-й вход группы управляющих входов перестраиваемого счетчика 3, который по передаваемому переднему фронту этого сигнала обну-- ляется, а затем отсчитывает такты, задаваемые генератором k тактовых импульсов, который выдает импульсы со скважностью, равной двум.

Под воздействием генератора 1ч импульсов, подаваемых на тактовые входы вычислителя 12 синдрома и перестраиваемого регистра 13 памяти, происходит процесс декодирования информации (вычисления остатка от деления принятого кодового слова на образующий полином, называемый синдромом) в вычислителе 12 синдрома и одновременная запись ее в регистр 13 памяти. На n-м такте (п - длина кода) счетчик 3 с третьего управляющего выхода 27 по заднему фронту импульса выдает сигнал опроса, который поступает на второй вход элемента И 16, на первый вход которого поступает логическая единица с вы хода элемента ИЛИ-НЕ 17, если синдром равен нулю, или логический ноль, если синдром не равен нулю. Если ин

131

формация не содержит обнаруживаемых кодом ошибок, то на выходе элемента И 16 будет единица, которая поступает на второй управляющий вход 8 регистра 13 памяти и разрешает выдачу информации на выходы устройства. Если же в коде обнаружится ошика, то на второй управляющий вход 8 регистра 13 памяти поступает ноль и информация не выдается получателю (синдром не равен нулю).

На n-м такте генератора 1А по заднему фронту сигнала с небольшой задержкой во времени с второго управляющего выхода 25 счетчика 3 подается импульс на управляющий вход вычислителя 12 синдрома и первый управляющий вход перестраиваемого регистра 13 памяти, в которых элементы памяти устанавливаются в исходное состояние. Устройство вновь готово к декодированию очередной кодовой комбинации

В режиме кодирования сигнал управления подается на управляющий вход 8 канального коммутатора 5, в котором осуществляется подключение первого З и второго 10 информационных входов к шине 6 устройства Так обеспечивается вывод формируемой устройством кодовой комбинации в канал свя зи. Кроме того, сигнал управления от входа 8 поступает на первый управляющий вход 8 ключа 9 управления, разрешая прием управляющих сигналов поступающих на второй управляющий вход ключа 9 с первого управляющего выхода счетчика 3.

На входы 1; (,р) группы управляющих входов подается сигнал управления, несущий информацию о номере корректирующего кода, применяемого в данный момент для передачи информации. Кодер 2 полинома в зависимости от поступившего управляющего сигнала выдает на группу управляющих входов вычислителя 12 синдрома сигналы, которые несут информацию об образующем полиноме Кроме того, сигнал управления от входа 1; поступает на 1-й вхо группы управляющих входов счетчика 3, который по переднему фронту этого сигнала сбрасывается в ноль, а затем отсчитывают такты, задаваемые генератором 14, скважность импульсов которого равна двум,

Процедура кодирования реализуется в соответствии с соотношением

0

s

0

5

996

0

5

0

С

5

И

I/

а(х) с(х)х + г(х) где а(х)

)

кодовый полином циклического кода (образующий полином); с(х) - полином информационных

символов;

к - степень образующего полинома g(x), равная телу контрольных символов кода; г(х) - полином контрольных символов, равный остатку от деления полинома с(х)хк на полином g(x), В течение первым m тактов (где m - число информационных сисоолов в коде) происходит .выдача информационных символов, поступающих от информационного входа 10 в устройство через канальный коммутатор 5 (элементы ИЛИ 35 и И 33 на фиг.5) на шину 6 подключения к каналу связи и одновременно происходит процесс вычисления с помощью сумматора 11 по модулю два и вычислителя 12 синдрома полинома г(х), коэффициентами которого являются контрольные символы кода. При этом ключ 9 управления подключает выход сумматора 11 к первому информационному входу 1 вычислителя 12 синдрома.

На (т+1)-м такте перестраиваемый счетчик 3 с первого выхода 2k выдает сигнал, под действием которого ключ 9 управления подключает выход сумматора 11 к первому информационному входу канального коммутатора 5 (фиг,5)о В течение к последующих тактов (с(т+1)-го по n-й такт) контрольные символы из вычислителя 12 синдрома через сумматор 11, ключ 9 управления,- канальный коммутатор 5 выдаются на шину подключения устройства к каналу связи. На n-м такте генератора 1 по заднему фронту CHI- нала с небольшой задержкой во време ни с второго выхода счетчика 3 (выход 25 на фиг„3) подается импульс на третий вход ключа 9 управления и вход вычислителя 12 синдрома, в которых элементы памяти устанавливаются в исходное состояние, Устройство вновь готово к кодированию очередной кодовой комбинации,

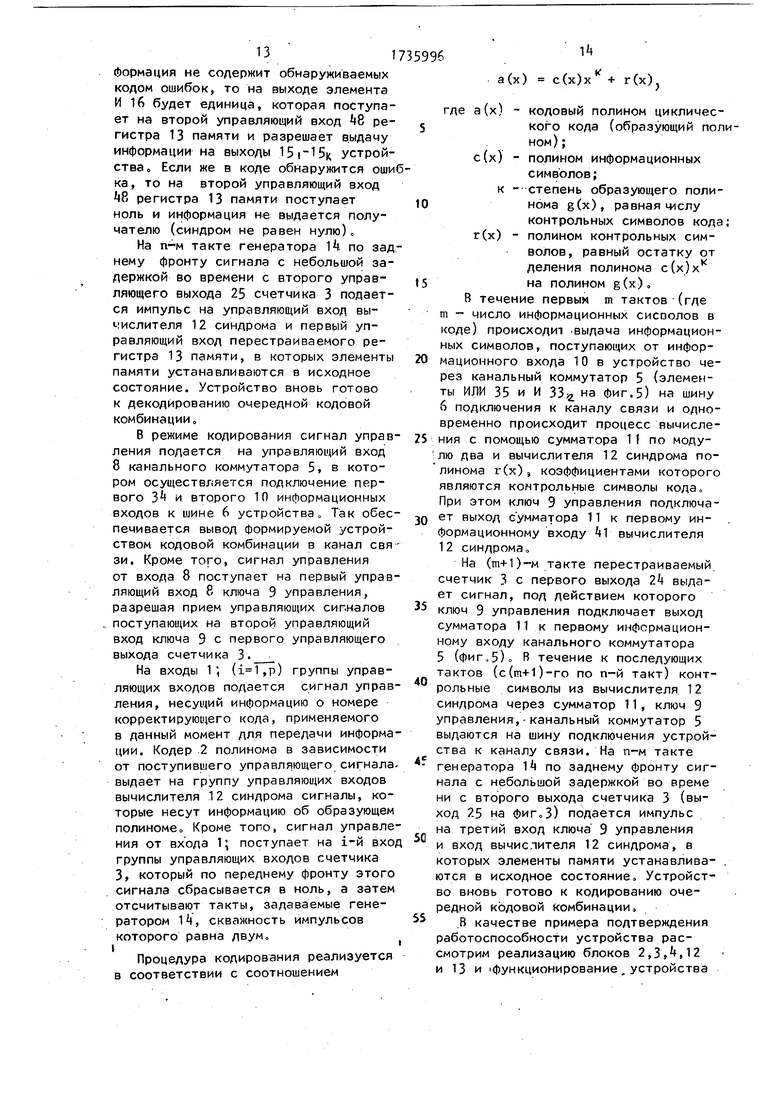

В качестве примера подтверждения работоспособности устройства рассмотрим реализацию блоков 2,3,,12 и 13 и функционирование, устройства

где а - сигнал на выходе кодера /.

полинома,

причем а, у4;аа у1 + у2;а,т а

0; а5 у + аб у + + Уг + У45 а7 у, + у3 + у4 ; а&

B.Q

У2 а,

УЗ;

110

В кодере 2 полинома (сЬиг.2) логика соединений входов 1 с выходами 18 и входами элементов ИЛИ 19 соответствует логическим функциям а, а и а6 - а.

Соответственно определяются длины кодов п 15, Пг 14, п 11, П4 0 поэтому в перестраиваемом регистре 13 памяти (Лиг.Р) информация от входа подается на вход зписи триггера W(, от входа . н вход записи триггера kj через элемент ИЛИ 50, от входа на вхо записи триггера 7$ через элемент ИЛИ 50, от входа 3 - на вход записи триггера 7б через элемент ИЛИ 50j. В перестраиваемом счетчике 3 (фиг.З) при сигнале на входе 1 на

1 5-м такте генератора 17 сигнал появляется на выходе 27, т.е. элемент И 21 срабатывает при наборе 1111 в счетчике 29 При сигнале на входе 1г на выходе 27 появится сигнал на такте генератора 17. т.е. элемент И 21й сработает при наборе 1110. При сигнале на входе 1 появится сигнал на выходе 27 на 11-м такте, так как

элемент И 21з сработает при наборе 1011, а при сигнале на входе сигнал на выходе . / появится на 10-м такте генератора 17, так как элемент И 2Ц сработает при наборе 10VO в счетчике 29° В соответствии с описанным выше алгоритмом работы устройства сигнал на третьем управляющем выходе 27 будет появляться всегда по окончании n-го такта, а на втором управляющем выходе 25 - с небольшой задержкой во времени. Так как на первом управляющем выходе 2Ц сигнал снимается на (т+1)-м такте, то для всех четырех ко.лов ()

элемент И сработает на наоор 0111 в счетчике 29

В соответствии вилам полиномов В, (х) - ) реализованы связи в вычислителе синдрома 12, на элементах которого осуществляется и полу чение контрольных элементов г(х) в режиме кодирования. Соответствующие выходы коммутатора 32 подключены ко входам соответствующих полусумматоров 43, а входы группы управляющих входов 18 через элементы И 42 реализуют схему деления на образующий полином кода, индекс которого соответстЕ)ует индексу сигнала по входу 1 о

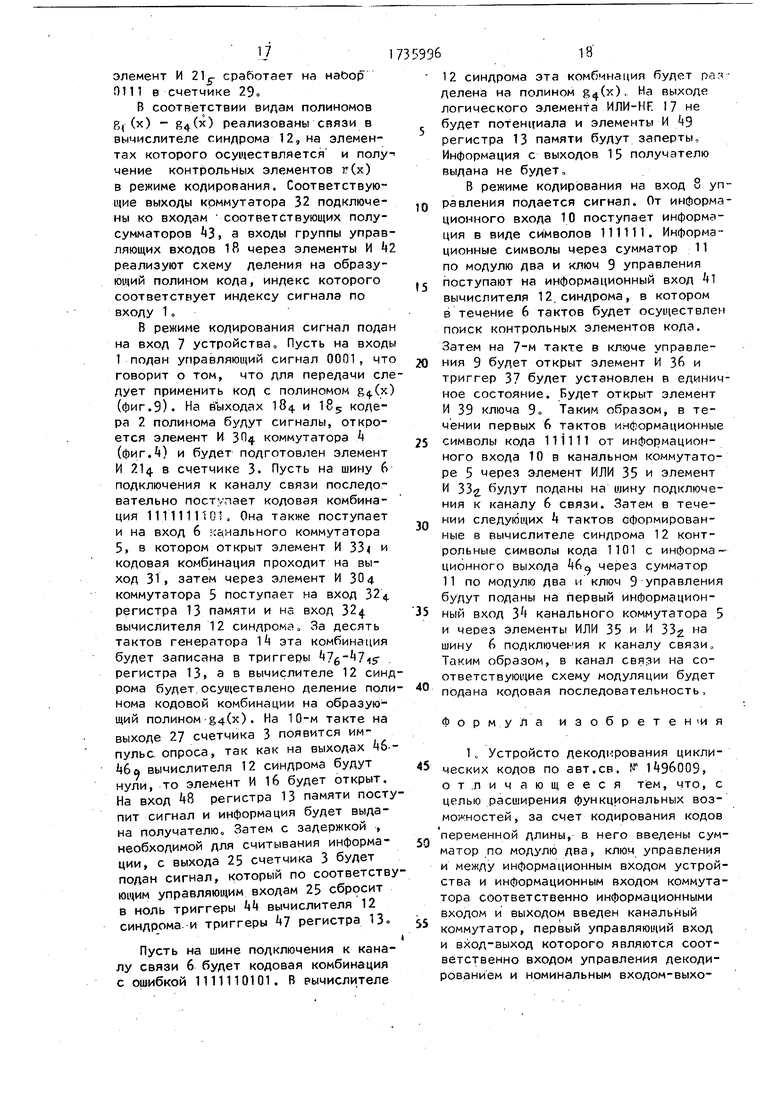

В режиме кодирования сигнал подан на вход 7 устройства. Пусть на входы 1 подан управляющий сигнал 0001, что говорит о том, что для передачи следует применить код с полиномом .(x) (фиг.9). На выходах 184 и 185 кодера 2 полинома будут сигналы, откроется элемент И ЗП4 коммутатора 4 (фиг.) и будет подготовлен элемент И 214 в счетчике 3. Пусть на шину 6 подключения к каналу связи последовательно поступает кодовая комбинация 111111110, Она также поступает и на вход 6 -сьнального коммутатора 5, в котором открыт элемент И 33 и кодовая комбинация проходит на выход 31, затем через элемент И 304 коммутатора 5 поступает на вход 32 ф регистра 13 памяти и на вход 32,j. вычислителя 12 синдрома, За десять тактов генератора 1 эта комбинация будет записана в триггеры 7(,7 регистра 13, а в вычислителе 12 синдрома будет осуществлено деление полинома кодовой комбинации на образующий полином g4(x). На 10-м такте на выходе 27 счетчика 3 появится импульс опроса, так как на выходах 45- 46 а вычислителя 12 синдрома будут нули, то элемент И 16 будет открыт. На вход 48 регистра 13 памяти поступит сигнал и информация будет выдана получателю. Затем с задержкой , необходимой для считывания информации, с выхода 25 счетчика 3 будет подан сигнал, который по соответствующим управляющим входам 25 сбросит в ноль триггеры 44 вычислителя 12 синдрома и триггеры 4 регистра 13-.

Пусть на шине подключения к каналу связи 6 будет кодовая комбинация с ошибкой 1111110101. В вычислителе

12 синдрома эта комбинация будет рлч делена на полином g,j(x). На выходе логического элемента ИЛИ-HF. 17 не будет потенциала и элементы И 49 регистра 13 памяти будут заперты. Информация с выходов 15 получателю выдана не будет,

В режиме кодирования на вход 8 упQ равления подается сигнал. От информационного входа 10 поступает информация в виде символов 111111. Информационные символы через сумматор 11 по модулю два и ключ 9 управления

5 поступают на информационный вход 41 вычислителя 12 синдрома, в котором в течение 6 тактов будет осуществлен поиск контрольных элементов кода.

Затем на такте в ключе управле0 ния 9 будет открыт элемент И 36 и

триггер 37 будет установлен в единичное состояние. Будет открыт элемент И 39 ключа 9о Таким образом, в течении первых 6 тактов информационные

5 символы кода 1lil11 от информационного входа 10 в канальном коммутаторе 5 через элемент ИЛИ 35 и элемент И 33. будут поданы на шину подключения к каналу 6 связи. Затем в течеQ нии следующих 4 тактов сформированные в вычислителе синдрома 12 контрольные символе кода 1101 с информационного выхода 46с) через сумматор 11 по модулю два и ключ 9 управления будут поданы на первый информацион5 ный вход 3 i канального коммутатора 5 и через элементы ИЛИ 35 и И 33 ||а шину 6 подключения к каналу связи. Таким образом, в канал на соответствующие схему модуляции будет

подана кодовая последовательность,

Формула изобретения

1 Устройсто декодирования цикли- 5 ческих кодов по авт.св. N 1496009, отличающееся тем, что, с целью расширения функциональных возможностей, за счет кодирования кодов

переменной длины, в него введены сумматор по модулю два, ключ управления и между информационным входом устройства и информационным входом коммутатора соответственно информационными входом и выходом введен канальный коммутатор, первый управляющий вход и вход-выход которого являются соответственно входом управления декодированием и номинальным входом-выхо0

5

лом устройства, первый управляющий вход и первый и второй информационные выходы ключа управления подключены соответственно у второму выходу перестраиваемого счетчика, второму информационному входу вычислителя синдрома и второму информационному входу канального коммутатора, второй управляющий вход которого объединен с одноименным входом ключа управления и является входом управления кодиро- ванием устройства, третий управляющий и информационный входы ключа управления подключены соответственно к третьему выходу перестраиваемого счетчика и выходу сумматора по модулю два, первый и второй входы которого подключены соответственно к соответствующему выходу вычислителя , синдрома и информационному входу устройства,

2 „ Устройство по п.2, отличающее с я тем, что канальный коммутатор содержит элемент ИЛИ и первый и второй элементы И, первые входы которого и первый и второй входы элемента ИЛИ являются соответствен- но первым и вторым управляющими и, первым и вторым информационными входами

олока, выход элемента ИЛИ подключен к второму входу второго элемента И, выход которого подключен к второму , входу первого элемента И и является входом-выходом блока, выход первого элемента И подключен к информацион-з ному выходу блока.

5 ВХ°Д которого соединен с вторым управляющим входом ключа, а выход соединен с единичным входом триггера, нулевой вход которого соединен с третьим управляющим входом ключа, информа-

0 ционный вход которого соединен с первыми входами второго и третьего элементов И, выход первого элемента И соединен с первым информационным выходом ключа, а второй вход - с единич- 5 ным выходом триггера, нулевой выход которого соединен с вторым входом третьего элемента И, выход которого соединен с вторым информационным выходом ключа управления.

1в.

или

91

I

28

Фиг. 5

зг, г Жз23 i

Фиг. 5

52

Ф-г

.6

Д

Тие.7

,

5,

.в

| Устройство декодирования циклических кодов | 1987 |

|

SU1496009A1 |

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| it | |||

Авторы

Даты

1992-05-23—Публикация

1990-02-05—Подача