Изобретение относится к вычислительной технике и предназначено для тестового контроля и диагностики логических блоков.

Цель изобретения - расширение но- менклатуры контролируемых блоков и расширение функциональных возможностей за счет организации дополнительных режимов контроля.

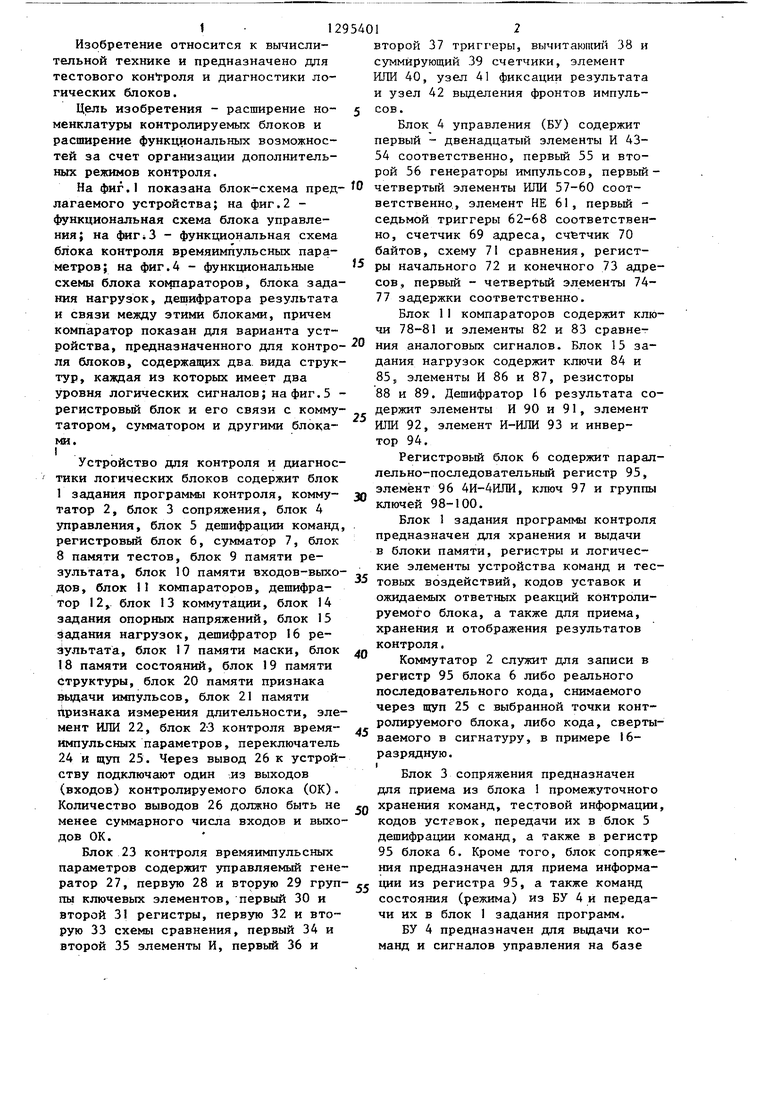

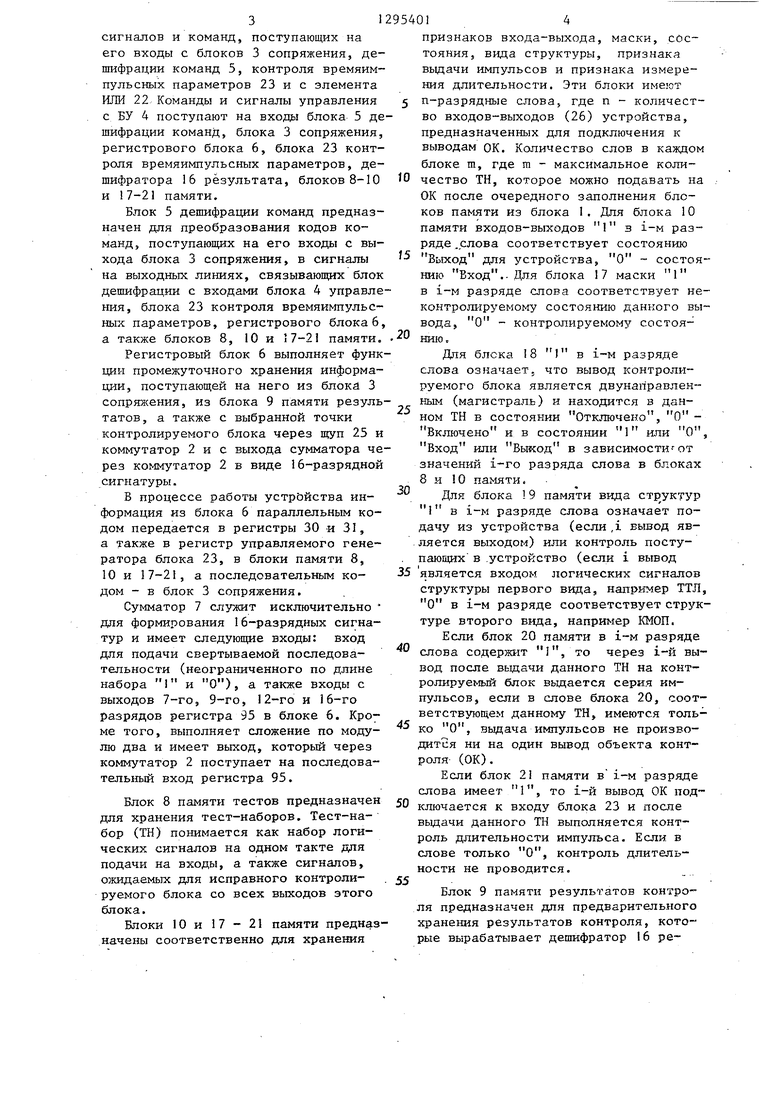

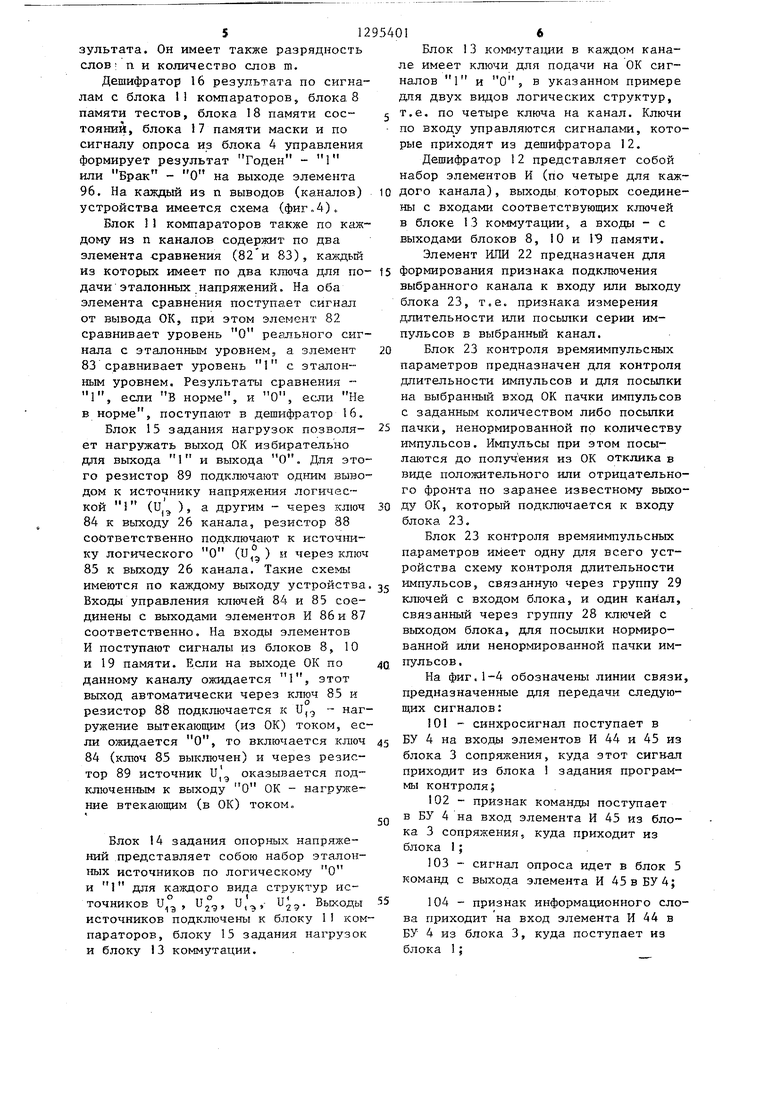

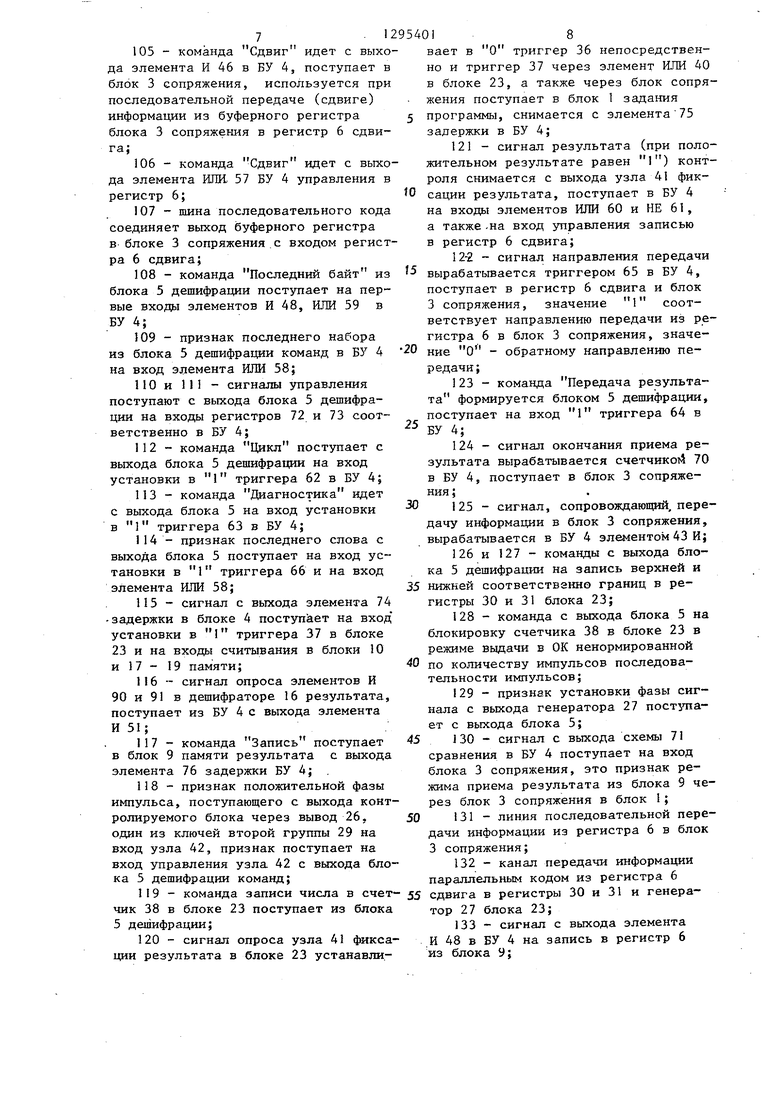

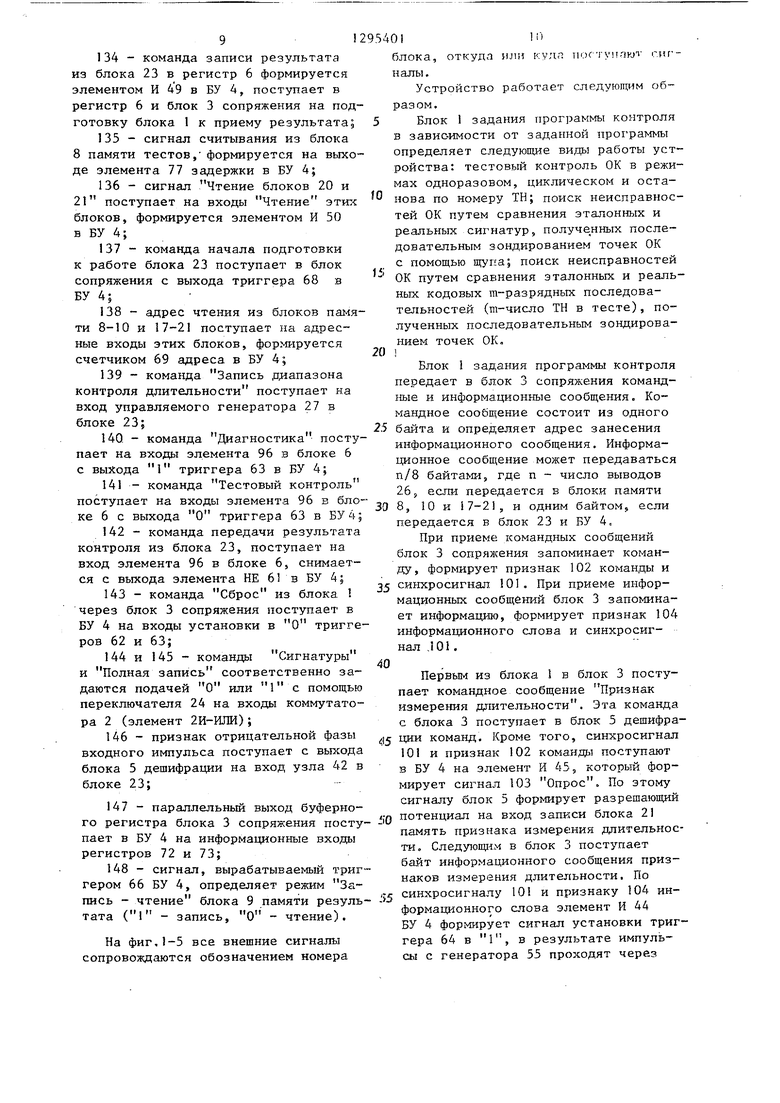

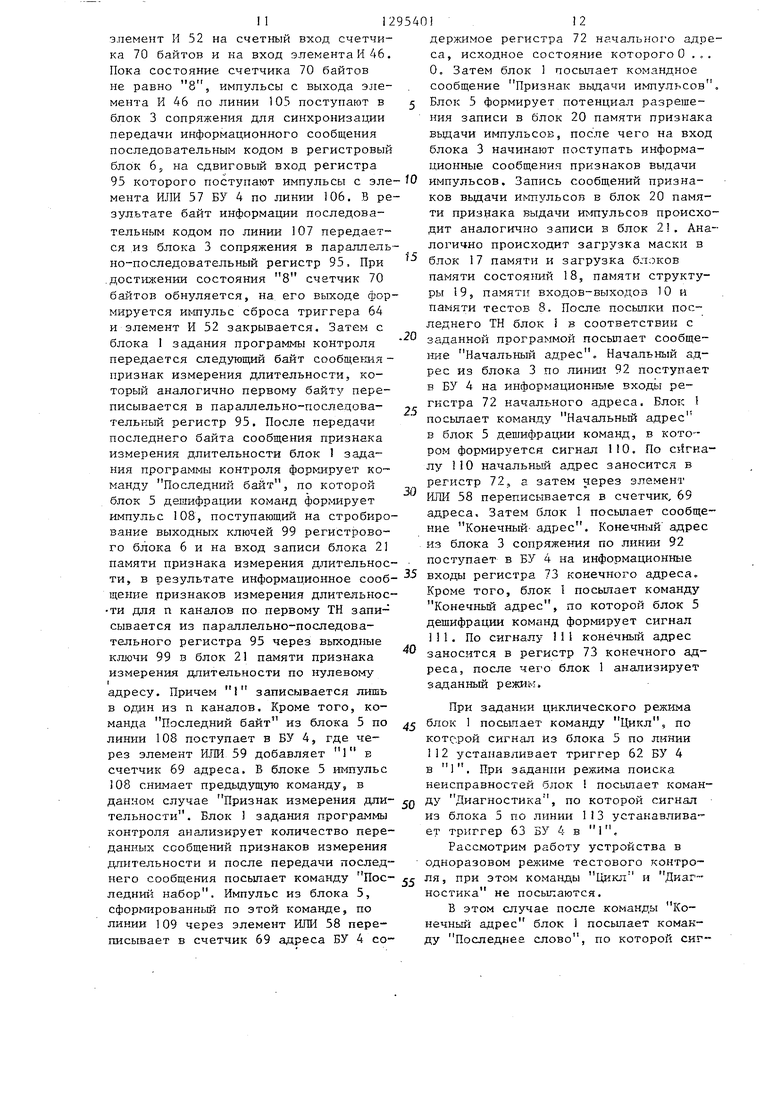

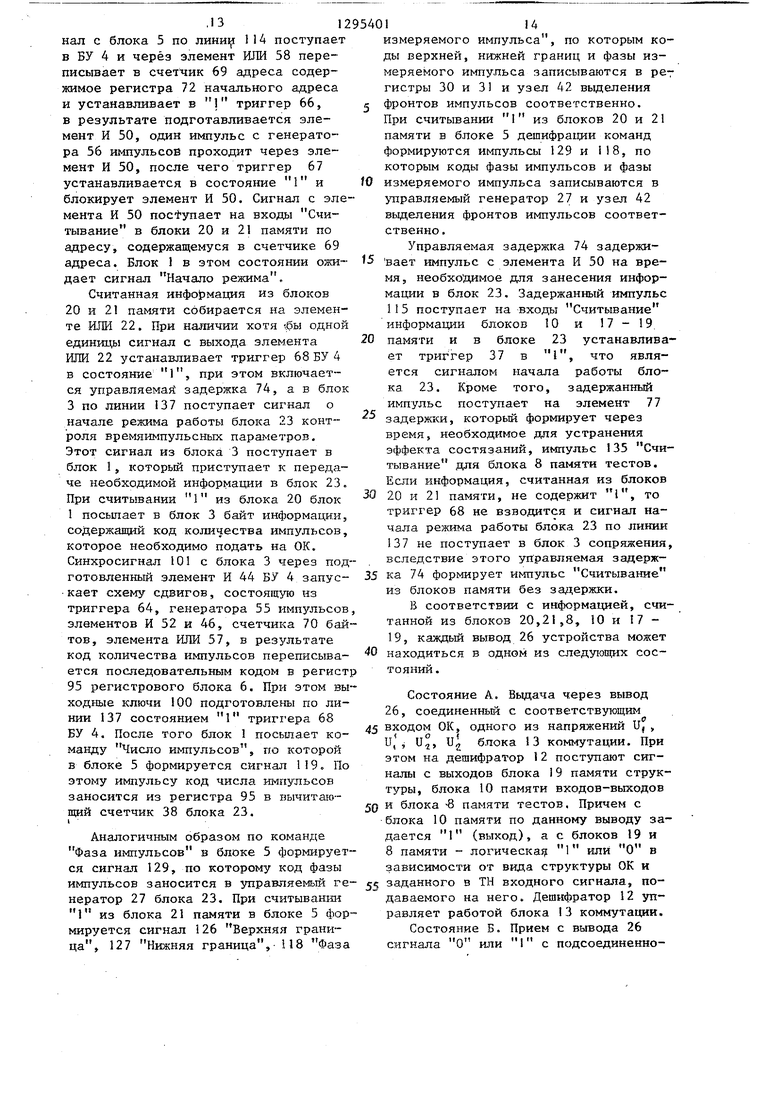

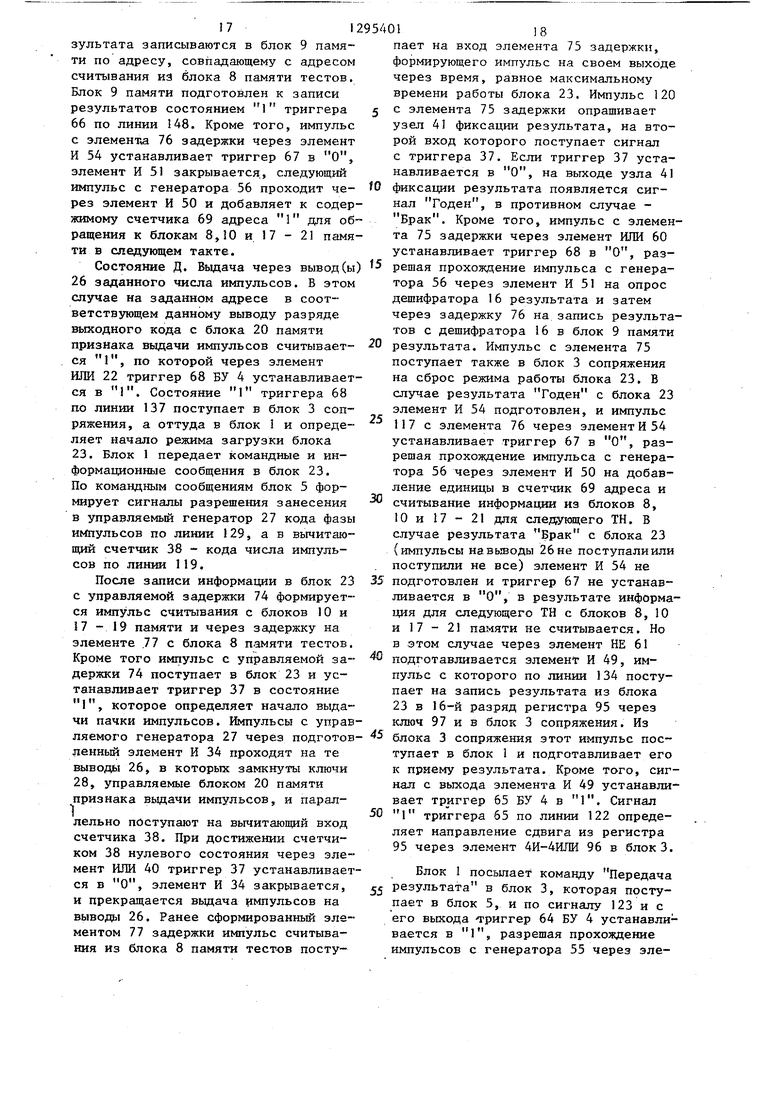

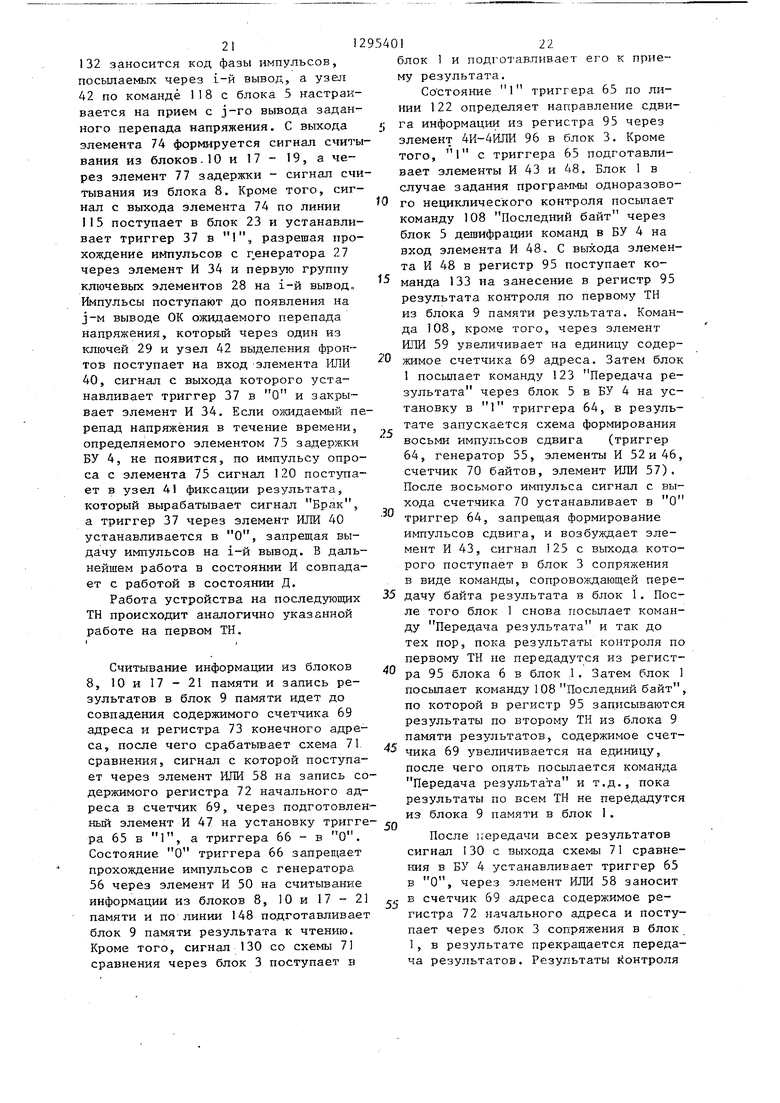

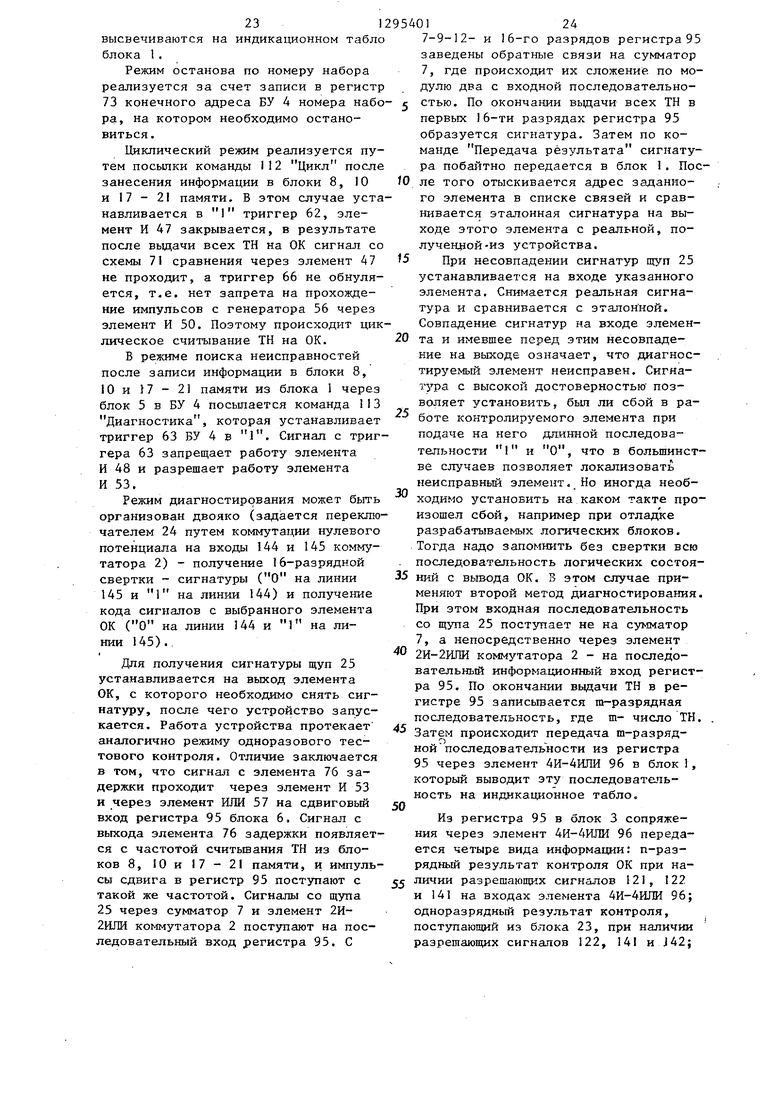

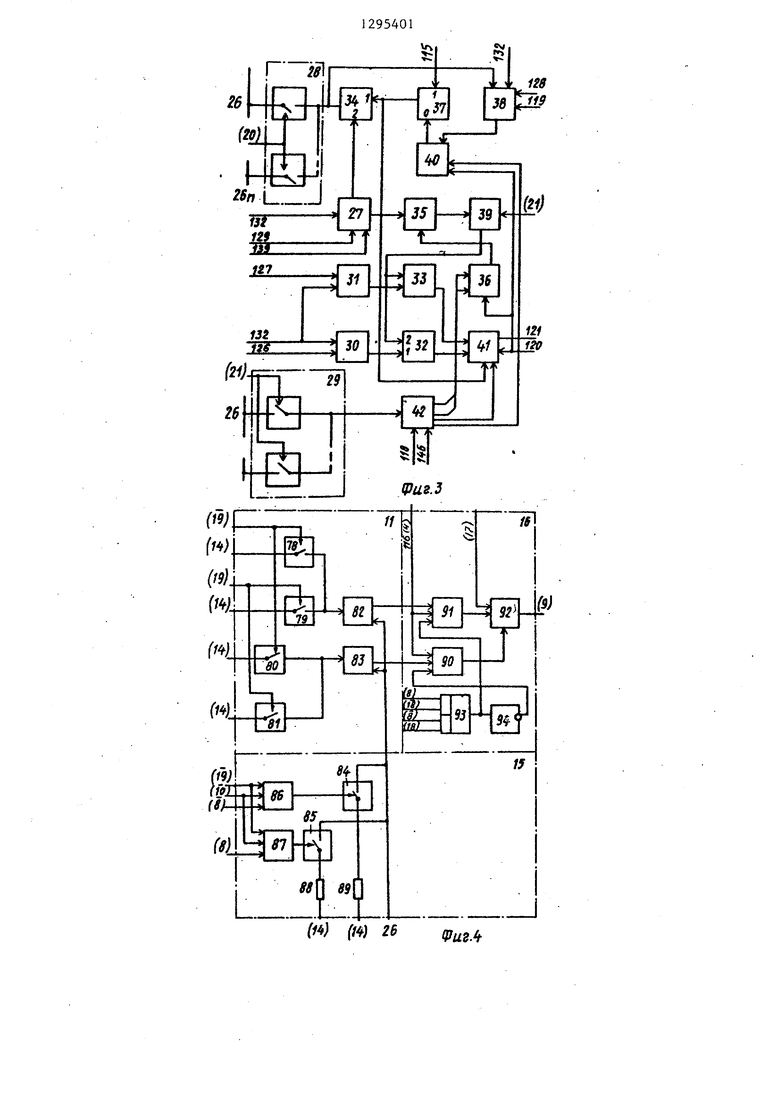

На фиг.1 показана блок-схема пред лагаемого устройства; на фиг.2 - функциональная схема блока управления; на 4мгi3 - функциональная схема блока контроля времяимпульсных параметров; на фиг.4 - функциональные схемы блока коьшараторов, блока задания нагрузок, дешифратора результата и связи между этими блоками, причем компаратор показан для варианта устройства, предназначенного для контро ля блоков, содержащих два вида структур, каждая из которых имеет два уровня логических сигналов; на фиг.5 регистровый блок и его связи с коммутатором, сумматором и другими блоками.

Устройство для контроля и диагностики логических блоков содержит блок 1 задания программы контроля, коммутатор 2, блок 3 сопряжения, блок 4 управления, блок 5 дешифрации команд регистровый блок 6, сумматор 7, блок 8 памяти тестов, блок 9 памяти результата, блок 10 памяти входов-выходов, блок 1I компараторов, дешифратор I2, блок 13 коммутации, блок 14 задания опорных напряжений, блок 15 задания нагрузок, дешифратор 16 ре- ультата, блок 17 памяти маски, блок 18 памяти состояний, блок 19 памяти структуры, блок 20 памяти признака выдачи импульсов, блок 21 памяти признака измерения длительности, элемент ИЛИ 22, блок 2-3 контроля время- импульсных параметров, переключатель 24 и щуп 25. Через вывод 26 к устройству подключают один .из выходов (входов) контролируемого блока (ОК), Количество выводов 26 должно быть не менее суммарного числа входов и выходов ОК.

Блок 23 контроля времяимпульсных параметров содержит управляемый генератор 27, первую 28 и вторую 29 группы ключевых элементов, первый 30 и второй 31 регистры, первую 32 и вторую 33 схемы сравнения, первый 34 и второй 35 элементы И, первый 36 и

второй 37 триггеры, вычитаюти11 38 и суммирующий 39 счетчики, элемент ИЛИ 40, узел 41 фиксации результата и узел 42 вьщеления фронтов импульсов.

Блок 4 управления (БУ) содержит первый - двенадцатый элементы И 43- 54 соответственно, первый 55 и вто

четвертый ния

рой 56 генераторы импульсов, первыйэлементы ИЛИ 57-60 соответственно., элемент НЕ 61, первый - седьмой триггеры 62-68 соответственно, счетчик 69 адреса, счетчик 70 байтов, схему 71 сравнения, регистры начального 72 и конечного 73 адресов, первый - четвертый элементы 74- 77 задержки соответственно.

Блок 11 компараторов содержит ключи 78-81 и элементы 82 и 83 сравнеаналоговых сигналов. Блок 15 задания нагрузок содержит ключи 84 и 85J элементы И 86 и 87, резисторы 88 и 89. Дешифратор 16 результата содержит элементы И 90 и 91, элемент ИЛИ 92, элемент И-ШШ 93 и инвертор 94.

Регистровый блок 6 содержит параллельно-последовательный регистр 95, элемент 96 4И-4ИЛИ, ключ 97 и группы ключей 98-100.

Блок 1 задания программы контроля предназначен для хранения и выдачи в блоки памяти, регистры и логические элементы устройства команд и тес- товых воздействий, кодов уставок и ожидаемых ответных реакций контролируемого блока, а также для приема, хранения и отображения результатов контроля.

Коммутатор 2 служит для записи в регистр 95 блока 6 либо реального последовательного кода, снимаемого через щуп 25 с выбранной точки контролируемого блока, либо кода, сверты- ваемого в сигнатуру, в примере 16- разрядную.

Блок 3 сопряжения предназначен для приема из блока 1 промежуточного хранения команд, тестовой информации, кодов устрвок, передачи их в блок 5 дешифрации команд, а также в регистр 95 блока 6. Кроме того, блок сопряжения предназначен для приема информации из регистра 95, а также команд состояния (режима) из БУ 4 и передачи их в блок 1 задания программ.

БУ 4 предназначен для выдачи команд и сигналов управления на базе

сигналов и команд, поступающих на его входы с блоков 3 сопряжения, дешифрации команд 5, контроля времяим- пульсных параметров 23 и с элемента ИЛИ 22 Команды и сигналы управления с БУ 4 поступают на входы блока 5 дешифрации команд, блока 3 сопряжения, регистрового блока 6, блока 23 контроля времяимпульсных параметров, дешифратора 16 результата, блоков 8-10 и 17-21 памяти.

Блок 5 дешифрации команд предназначен для преобразования кодов команд, поступающих на его входы с выхода блока 3 сопряжения, в сигналы

на выходных линиях, связывающих блок дешифрации с входами блока 4 управления, блока 23 контроля времяимпульсных параметров, регистрового блока 6, а также блоков 8, 10 и 17-21 памяти.

Регистровый блок 6 выполняет функции промежуточного хранения информации, поступающей на него из блоки 3 сопряжения, из блока 9 памяти результатов , а также с выбранной точки контролируемого блока через щуп 25 и коммутатор 2 и с выхода сумматора через коммутатор 2 в виде 16-разрядной сигнатуры,

В процессе работы устройства информация из блока 6 параллельным кодом передается в регистры 30 и 31, а также в регистр управляемого генератора блока 23, в блоки памяти 8, 10 и 17-21, а последовательным кодом - в блок 3 сопряжения.

Сумматор 7 служит исключительно для формирования 16-разрядных сигнатур и имеет следующие входы: вход для подачи свертываемой последовательности (неограниченного по длине набора и О), а также входы с выходов 7-го, 9-го, 12-го и 16-го разрядов регистра 95 в блоке 6. Кроме того, выполняет сложение по модулю два и имеет выход, который через коммутатор 2 поступает на последовательный вход регистра 95.

Блок 8 памяти тестов предназначен для хранения тест-наборов. Тест-набор (ТН) понимается как набор логических сигналов на одном такте дпя подачи на входы, а также сигналов, озкидаемых для исправного контролируемого блока со всех выходов этого блока.

Блоки 10 и 17 - 21 памяти предназначены соответственно для хранения

954014

признаков входа-выхода, маски, состояния, вида структуры, признака выдачи импульсов и признака измерения длительности. Эти блоки имеют 5 п-разрядные слова, где п - количество входов-выходов (26) устройства, предназначенных для подключения к выводам ОК. Количество слов в каждом блоке т, где m - максимальное коли- 10 чество ТН, которое можно подавать на ОК после очередного заполнения блоков памяти из блока I. Для блока 10 памяти входов-выходов в i-м разряде .слова соответствует состоянию Выход для устройства, О состоянию Вход.. Для блока 17 маски 1 в i-M разряде слова соответствует неконтролируемому состоянию данного вывода, О - контролируемому состоянию.

Для блока 18 ) в i-м разряде слова означает5 что вывод контролируемого блока является двунаправленным (магистраль) и находится в дан20

25

30

35

40

45

50

55

ном ТН в состоянии Отключено, О - Включено и в состоянии 1 или О, Вход или Выкод в зависимости-от значений i-ro разряда слова в блоках 8 и 10 памяти.

«

Для блока 9 памяти вида стр уктур 1 в i-M разряде слова означает подачу из устройства (если ,i вывод является выходом) или контроль поступающих в .устройство (если i вывод является входом логических сигналов структуры первого вида, например ТТЛ, О в i-M разряде соответствует структуре второго вида, например КМОП,

Если блок 20 памяти в i-м разряде слова содержит 1, то через i-й вывод после вьщачи данного ТН на контролируемый блок вьщается серия импульсов, если в слове блока 20, соответствующем данному ТН, имеются только О, выдача импульсов не производится ни на один вывод объекта контроля (ОК).

Если блок 21 памяти в i-м разряде слова имеет 1, то i-й вывод ОК подключается к входу блока 23 и после вьщачи данного ТН выполняется контроль длительности импульса. Если в слове только О, контроль длительности не проводится.

Блок 9 памяти результатов контроля предназначен для предварительного хранения результатов контроля, которые вырабатывает дешифратор I6 результата. Он имеет также разрядность слов- п и количество слов т.

Дешифратор 16 результата по сигналам с блока I компараторов, блока 8 памяти тестов, блока 18 памяти состоянии, блока 17 памяти маски и по сигналу опроса из блока 4 управления формирует результат Годен - 1 или Брак - О на выходе элемента 96. На каждый из п выводов (каналов) устройства имеется схема (фиг.4).

Блок }1 компараторов также по каждому из п каналов содержит по два элемента сравнения (82 и 83), каладый из которых имеет по два ключа для подачи эталонных напряжений. На оба элемента сравнения поступает сигнал от вывода ОК, при этом элемент 82 сравнивает уровень О реального сигнала с эталонным уровнем, а элемент

83сравнивает уровень 1 с эталонным уровнем. Результаты сравнения - I, если В норме, и О, если Не в норме, поступают в дешифратор 16,

Блок 15 задания нагрузок позволяет нагружать выход ОК избирательно для выхода 1 и выхода О. Для этого резистор 89 подключают одним выводом к источнику напряжения логической 1 ( другим - через ключ

84к выходу 26 канала, резистор 88 соответственно подключают к источнику логического О (U) и через ключ

85к выходу 26 канала. Такие схемы имеются по каждому выходу устройства. Входы управления ключей 84 и 85 соединены с выходами элементов И 86 и 87 соответственно. На входы элементов

И поступают сигналы из блоков 8, 10 и 19 памяти. Если на выходе ОК по данному каналу ожидается 1, этот выход автоматически через ключ 85 и резистор 88 подключается к U, -- наг- ружение вытекающим (из ОК) током, если ожидается О, то включается ключ 84 (ключ 85 выключен) и через резистор 89 источник Ujg оказывается подключенным к выходу О ОК - нагруже- ние втекающим (в ОК) током.

Блок 14 задания опорных напряжений представляет собою набор эталон- iftix источников по логическому О и 1 для каждого вида структур источников , U°g, U,,- U29 Выходы источников подключены к блоку 11 компараторов, блоку 15 задания нагрузок и блоку 13 коммутации.

Блок 13 коммутации в каждом канале имеет ключи для подачи на ОК сигналов 1 и О, в указанном примере для двух видов логических структур, т.е. по четыре ключа на канал. Ключи по входу управляются сигналами, которые приходят из дешифратора 12,

Дешифратор 12 представляет собой набор элементов И (по четыре для каждого канала), выходы которых соединены с входами соответствующих ключей в блоке 13 коммутацииJ а входы - с выходами блоков 8, 10 и памяти. Элемент ИПИ 22 предназначен для

формирования признака подключения выбранного канала к входу или выходу блока 23, т.е. признака измерения длительности или посылки серии импульсов в выбранньй канал.

Блок 23 контроля времяимпульсных параметров предназначен для контроля длительности импульсов и для посыпки на выбранньш вход ОК пачки импульсов с заданньм количеством либо посылки

пачки, ненормированной по количеству импульсов. Импульсы при этом посылаются до получения из ОК отклика в виде положительного или отрицательного фронта по заранее известному выхоДУ ОК, который подключается к входу блока 23.

Блок 23 контроля времяимпульсных параметров имеет одну для всего устройства схему контроля длительности

импульсов, связаннзто через группу 29 ключей с входом блока, и один канал, связанный через группу 28 ключей с выходом блока, для посылки нормированной или ненормированной пачки импульсов.

На фиг.1-4 обозначены линии связи, предназначенные д.пя передачи следующих сигналов:

01 - синхросигнал поступает в

БУ 4 на входы элементов И 44 и 45 из блока 3 сопряжения, куда этот сигнал приходит из блока задания программы контроля;

102- признак команды поступает в БУ 4 на вход элемента И 45 из блока 3 сопряжения, куда приходит из блока ;

103- сигнал опроса идет в блок 5 команд с выхода элемента И 45вБУ4;

104 - признак информационного слова приходит на вход элемента И 44 в БУ 4 из блока 3, куда поступает из блока 1;

105- команда Сдвиг идет с выхода элемента И 46 в БУ 4, поступает в блок 3 сопряжения, используется при последовательной передаче (сдвиге) информации из буферного регистра блока 3 сопряжения в регистр 6 сдвига;

106- команда Сдвиг идет с выхода элемента ИЛИ 57 БУ 4 управления в регистр 6;

107- шина последовательного кода соединяет выход буферного регистра

в блоке 3 сопряжения.с входом регистра 6 сдвига;

108- команда Последний байт из блока 5 дешифрации поступает на первые входы элементов И 48, ИЛИ 59 в БУ 4;

509 - признак последнего набора из блока 5 дешифрации команд в БЗ 4 на вход элемента ИЛИ 58;

110 и 111 - сигналы управления поступают с выхода блока 5 дешифрации на входы регистров 72 и 73 соответственно в БУ 4;

112- команда Цикл поступает с выхода блока 5 дешифрации на вход установки в 1 триггера 62 в БУ 4;

113- команда Диагностика идет с выхода блока 5 на вход установки в 1 триггера 63 в БУ 4;

114- признак последнего слова с выхода блока 5 поступает на вход установки в 1 триггера 66 и на вход элемента РШИ 58;

115- сигнал с выхода элемента 74 -задержки в блоке 4 поступает на вход

установки в I триггера 37 в блоке 23 и на входы считывания в блоки 10 и 17 - 19 памяти;

116- сигнал опроса элементов И 90 и 91 в дешифраторе 16 результата, поступает из БУ 4 с выхода элемента И 51;

117- команда Запись поступает в блок 9 памяти результата с выхода элемента 76 задержки БУ 4; ,

118- признак положительной фазы импульса, поступающего с выхода контролируемого блока через вывод 26, один из ключей второй группы 29 на вход узла 42, признак поступает на вход управления узла 42 с выхода бловает в О триггер 36 непос но и триггер 37 через элеме в блоке 23, а также через б жения поступает в блок 1 за программы, снимается с элем задержки в БУ 4;

121 - сигнал результата жительном результате равен роля снимается с выхода узл

0 сации результата, поступает на входы элементов ИЛИ 60 и а также -на вход управления в регистр 6 сдвига;

12-i - сигнал направления

5 вырабатывается триггером 65 поступает в регистр 6 сдвиг 3 сопряжения, значение 1 ветствует направлению перед гистра 6 в блок 3 сопряжени 20 кие О - обратному направл редачи;

123- команда Передача та формируется блоком 5 де поступает на вход 1 тригг

БУ 4;

124- сигнал окончания п зультата вырабатывается сче в БУ 4, поступает в блок 3 ния;

30 125 - сигнал, сопровожда дачу информации в блок 3 со вырабатывается в БУ 4 элеме 126 и 127 - команды с вы ка 5 дешифрации на запись в

35 нижней соответстванно грани гистры 30 и 31 блока 23;

128- команда с выхода бл блокировку счетчика 38 в бл режиме выдачи в ОК ненормир

40 по количеству импульсов посл тельности импульсов;

129- признак установки ф нала с выхода генератора 27 ет с выхода блока 5;

45 J 30 - сигнал с выхода сх сравнения в БУ 4 поступает блока 3 сопряжения, это при жима приема результата из бл рез блок 3 сопряжения в бло

50 131 - линия последовател дачи информации из регистра 3 сопряжения;

132 - канал передачи инфо параллельным кодом из регис

ка 5 дешифрации команд;

119- команда записи числа в счет- 55 сдвига в регистры 30 и 31 и чик 38 в блоке 23 поступает из блока тор 27 блока 23;

5 дешифрации;

120- сигнал опроса узла 41 фиксации результата в блоке 23 устанавли133 - сигнал с выхода эле И 48 в БУ 4 на запись в реги из блока 9;

вает в О триггер 36 непосредственно и триггер 37 через элемент ИЛИ 40 в блоке 23, а также через блок сопряжения поступает в блок 1 задания программы, снимается с элемента 75 задержки в БУ 4;

121 - сигнал результата (при положительном результате равен 1) контроля снимается с выхода узла 41 фик0 сации результата, поступает в БУ 4 на входы элементов ИЛИ 60 и НЕ 61, а также -на вход управления записью в регистр 6 сдвига;

12-i - сигнал направления передачи

5 вырабатывается триггером 65 в БУ 4, поступает в регистр 6 сдвига и блок 3 сопряжения, значение 1 соответствует направлению передачи из регистра 6 в блок 3 сопряжения, значе- 0 кие О - обратному направлению передачи;

123- команда Передача результата формируется блоком 5 дешифрации, поступает на вход 1 триггера 64 в

БУ 4;

124- сигнал окончания приема результата вырабатывается счетчикот5 70 в БУ 4, поступает в блок 3 сопряжения;

0 125 - сигнал, сопровождающий, передачу информации в блок 3 сопряжения, вырабатывается в БУ 4 элементом 43 И; 126 и 127 - команды с выхода блока 5 дешифрации на запись верхней и

5 нижней соответстванно границ в регистры 30 и 31 блока 23;

128- команда с выхода блока 5 на блокировку счетчика 38 в блоке 23 в режиме выдачи в ОК ненормированной

0 по количеству импульсов последовательности импульсов;

129- признак установки фазы сигнала с выхода генератора 27 постзтта- ет с выхода блока 5;

5 J 30 - сигнал с выхода схемы 71 сравнения в БУ 4 поступает на вход блока 3 сопряжения, это признак режима приема результата из блока 9 через блок 3 сопряжения в блок 1;

0 131 - линия последовательной передачи информации из регистра 6 в блок 3 сопряжения;

132 - канал передачи информации параллельным кодом из регистра 6

генера-

5 сдвига в регистры 30 и 31 и тор 27 блока 23;

133 - сигнал с выхода элемента И 48 в БУ 4 на запись в регистр 6 из блока 9;

9

134- команда записи результата из блока 23 в регистр 6 формируется элементом И 49 в БУ 4, поступает в регистр 6 и блок 3 сопряжения на подготовку блока 1 к приему результата5

135- сигнал считывания из блока

8 памяти тестов, формируется на выходе элемента 77 задержки в БУ 4;

136- сигнал Чтение блоков 20 и 21 поступает на входы Чтение этих блоков, формируется элементом И 50

в БУ 4;

137- команда начала подготовки к работе блока 23 поступает в блок сопряжения с выхода триггера 68 в БУ 4;

138 адрес чтения из блоков памяти 8-10 и 17-21 поступает на адресные входы этих блоков, формируется счетчиком 69 адреса в БУ 4;

139- команда Запись диапазона контроля длительности поступает на вход управляемого генератора 27 в блоке 23;

140. - команда Диагностика поступает на входы элемента 96 в блоке 6 с выхода 1 триггера 63 в БУ 4;

141- команда Тестовый контроль поступает на входы элемента 96 в блоке 6 с выхода О триггера 63 в БУ4;

142- команда передачи результата контроля из блока 23, поступает на вход элемента 96 в блоке 6, снимается с выхода элемента НЕ 61 в БУ 4;

143- команда Сброс из блока 1 через блок 3 сопряжения поступает в БУ 4 на входы установки в О триггеров 62 и 63;

144и 145 - команды Сигнатуры и Полная запись соответственно задаются подачей О или 1 с помощью переключателя 24 на входы коммутатора 2 (элемент 2И-ИЛИ);

146 - признак отрицательной фазы входного импульса поступает с вьпсода блока 5 дешифрации на вход узла 42 в блоке 23;

,

147- параллельный выход буферного регистра блока 3 сопряжения посту пает в БУ 4 на информационные входы регистров 72 и 73;

148- сигнал, вырабатываемый триг гером 66 БУ 4, определяет режим Запись - чтение блока 9 памяти резуль тата (1 - запись, О - чтение).

На фиг,1-5 все внешние сигналы сопровождаются обозначением номера

,

TIi;)f 1-у.)ЮТ Г.ИГ 10

15

9540111

блока, откуда или налы.

Устройство работает следующим образом.

5 Блок 1 задания программы контроля в завис-имости от заданной программы определяет следующие виды работы устройства: тестовый контроль ОК в режимах одноразовом, циклическом и останова по номеру ТН; поиск неисправностей ОК путем сравнения эталонных и реальных сигнатур, получе нных последовательным зондированием точек ОК с помощью щупа; поиск неисправностей ОК путем сравнения эталонных и реальных кодовых П1 разрядных последовательностей (т-число ТН в тесте), полученных последовательным зондированием точек ОК. 20 1

Блок 1 задания программы контроля передает в блок 3 сопряжения командные и информационные сообщения. Командное сообщение состоит из одного

25 байта и определяет адрес занесения информационного сообщения. Информационное сообп1ение может передаваться п/8 байтами, где п - число выводов 26, если передается в блоки памяти

30 8, 10 и 7-2, и одним байтом, если передается в блок 23 и БУ 4

При приеме командных сообщений блок 3 сопряжения запоминает команду, формирует признак 102 команды и

35 синхросигнал 101. При приеме информационных сообщений блок 3 запоминает информацию, формирует признак 104 информационного слова и синхросигнал ,101 ,

40

Первьм из блока в блок 3 поступает командное сообщение Признак измерения длительности. Эта команда с блока 3 поступает в блок 5 дешифра- )5 Ции команд. Кроме того, синхросигнал 101 и признак 102 команды поступают в БУ 4 на элемент И 45, который формирует сигнал 103 Опрос. По зтому сигналу блок 5 формирует разрешающий i;Q потенциал на вход записи блока 21

память признака измерения длительности. Следующим в блок 3 поступает байт информационного сообщения признаков измерения длительности. По 1J5 синхросигналу 10 и признаку 104 информационного слова элемент И 44 БУ 4 фор:ушрует сигнал установки триггера 64 в 1, в результате импульсы с генератора 55 проходят через

II1295

элемент И 52 на счетный вход счетчика 70 байтов и на вход элемента И 46. Пока состояние счетчика 70 байтов не равно 8, импульсы с выхода элемента И 46 по линии 105 поступают в блок 3 сопряжения для синхронизации передачи информационного сообщения последовательным кодом в регистровый блок 6. на сдвиговый вход регистра

95 которого поступают импульсы с эле- Шимпульсов. Запись сообщений признамента ИЛИ 57 БУ 4 по линии 106, В ре-ков выдачи и myльcoв в блок 20 памязультате байт информации последова-ти признака выдачи импульсов происхотельным кодом по линии 107 передает-дит аналогично записи в блок 21, Анася .из блока 3 сопряжения в параллельно-последовательный регистр 95. При .достижении состояния 8 счетчик 70 байтов обнуляется, на его выходе формируется и fflyльc сброса триггера 64 и элемент И 52 закрывается. Затем с блока 1 задания программы контроля передается следующий байт сообщения - признак измерения длительности, который аналогично первому байту переписывается в параллельно-последовательный регистр 95. После передачи последнего байта сообщения признака измерения длительности блок 1 задания программы контроля формирует команду Последний байт, по которой блок 5 дешифрации команд формирует импульс 108, поступающий на стробиро- вание выходных ключей 99 регистрового блока 6 и на вход записи блока 21 памяти признака измерения длительнослогично происходит загрузка маски блок 17 памяти и загрузка блоков памяти СОСТОЯ1ШЙ 18, памяти структ ры 19, памяти входов-выходов 10 и памяти тестов 8. После посыпки последнего ТН блок i в соответствии с заданной программой посьтает сообще ние Начальный адрес. Начапьный ад рес из блока 3 по линии 92 поступае в БУ 4 на информационные входы регистра 72 начального адреса. Блок 1 посьшает команду Начальный адрес в блок 5 дешифрации команд, в котором формируется сигнал ПО. По сигн лу 10 начальный адрес заносится в регистр 72, а затем через элемент ИЛИ 58 переписывается в счетчик, 69 адреса. Затем блок 1 посьтает сообщ ние Конечный- адрес. Конечный адре из блока 3 сопряжения по линии 92 поступает в БУ 4 на информационные

30

ти, в результате информационное сооб- входы регистра 73 конечного адреса.

Кроме того, блок 1 посьшает команду Конечный адрес, по которой блок 5 дешифрации команд формирует сигнал 111. По сигналу 111 конечный адрес заносится в регистр 73 конечного ад реса, после чег о блок 1 анализирует заданный режим.

щение признаков измерения длительное ти для п каналов по первому ТН записывается из параллельно-последовательного регистра 95 через выходные ключи 99 в блок 21 памяти признака

измерения длительности по нулевому t

адресу. Причем 1 записывается лишь в оддгн из п каналов. Кроме того, команда Последний байт из блока 5 по линии 108 поступает в БУ 4, где через элемент ИЛИ 59 добавляет 1 в счетчик 69 адреса. В блоке 5 импульс 108 снимает предыдущую команду, в

40

Кроме того, блок 1 посьшает команду Конечный адрес, по которой блок 5 дешифрации команд формирует сигнал 111. По сигналу 111 конечный адрес заносится в регистр 73 конечного адреса, после чег о блок 1 анализирует заданный режим.

При задании циклического реж1-ша 45 блок 1 посьшает команду Цикл, по

которой сигнал из блока 5 по линии 112 устанавливает триггер 62 БУ 4 в 1. При задании режима поиска неисправностей блок посыпает коман- данном случае Признак измерения дин- Q ду Диагностика, по которой сигнал тельности. Блок 1 задания nporpaMt«.i из блока 5 по линии 113 устакавлива-- контроля анализирует количество пере- ет триггер 63 БУ 4 в 1. данных сообщений признаков измерения Рассмотрим работу устройства в дпительности и после передачи послед- одноразовом режиме тестового контро- него сообщения посыпает команду Пос- ля, при этом комаьады и Диагледний набор. Импульс из блока 5, cфopмIipoвaнный по этой команде, по линии 109 через элемент ШШ 58 переписывает в счетчик 69 адреса БУ 4 соностика не посыпаются.

В этом случае после команды Конечный адрес блок 1 посылает команду Последнее слово, по которой сиг1

12

держимое регистра 72 начальнох о адреса, исходное состояние которого О ... 0. Затем блок 1 посьшает командное сообщение Признак вьщачи импульсов. Блок 5 формирует потенциал разрешения записи в блок 20 памяти признака вьщачи импульсов, после чего на вход блока 3 начинают поступать информационные сообщения признаков выдачи

логично происходит загрузка маски в блок 17 памяти и загрузка блоков памяти СОСТОЯ1ШЙ 18, памяти структуры 19, памяти входов-выходов 10 и памяти тестов 8. После посыпки последнего ТН блок i в соответствии с заданной программой посьтает сообщение Начальный адрес. Начапьный адрес из блока 3 по линии 92 поступает в БУ 4 на информационные входы регистра 72 начального адреса. Блок 1 посьшает команду Начальный адрес в блок 5 дешифрации команд, в котором формируется сигнал ПО. По сигналу 10 начальный адрес заносится в регистр 72, а затем через элемент ИЛИ 58 переписывается в счетчик, 69 адреса. Затем блок 1 посьтает сообщение Конечный- адрес. Конечный адрес из блока 3 сопряжения по линии 92 поступает в БУ 4 на информационные

входы регистра 73 конечного адреса.

Кроме того, блок 1 посьшает команду Конечный адрес, по которой блок 5 дешифрации команд формирует сигнал 111. По сигналу 111 конечный адрес заносится в регистр 73 конечного адреса, после чег о блок 1 анализирует заданный режим.

При задании циклического реж1-ша 45 блок 1 посьшает команду Цикл, по

ностика не посыпаются.

В этом случае после команды Конечный адрес блок 1 посылает команду Последнее слово, по которой сигнал с блока 5 по лини 1 14 поступает в БУ 4 и через элемент ИЛИ 58 переписывает в счетчик 69 адреса содержимое регистра 72 начального адреса и устанавливает в 1 триггер 66, в результате подготавливается элемент И 50, один импульс с генератора 56 импульсов проходит через элемент И 50, после чего триггер 67 устанавливается в состояние 1 и блокирует элемент И 50. Сигнал с элемента И 50 поступает на входы Считывание в блоки 20 и 21 памяти по адресу, содержащемуся в счетчике 69 адреса. Блок I в этом состоянии ожидает сигнал Начало режима.

Считанная инфoi5мaция из блоков 20 и 21 памяти собирается на элементе ИЛИ 22. При наличии хотя .бы одной единицы сигнал с выхода элемента ИЛИ 22 устанавливает триггер 68 БУ 4 в состояние 1, при этом включается управляема задержка 74, а в блок 3 по линии 137 поступает сигнал о начале режима работы блока 23 контроля времяимпульсных параметров. Этот сигнал из блока 3 поступает в блок 1, который приступает к передаче необходимой информации в блок 23, При считывании Г из блока 20 блок 1 посылает в блок 3 байт информации, содержащий код количества импульсов, которое необходимо подать на ОК. Синхросигнал 101 с блока 3 через подготовленный элемент И 44 БУ 4 запус- кает схему сдвигов, состоящую из триггера 64, генератора 55 импульсов, элементов И 52 и 46, счетчика 70 байтов, элемента ИЛИ 57, в результате код количества импульсов переписывается последовательным кодом в регистр 95 регистрового блока 6. При этом выходные ключи 100 подготовлены по линии 137 состоянием 1 триггера 68 БУ 4. После того блок 1 посьшает команду Число импульсов, по которой в блоке 5 формируется сигнал 119. По этому импульсу код числа импульсов заносится из регистра 95 в вычитающий счетчик 38 блока 23.

L

Аналогичным образом по команде Фаза импульсов в блоке 5 формируется сигнал 129, по которому код фазы импульсов заносится в управляемый генератор 27 блока 23. При считывашш 1 из блока 21 памяти в блоке 5 формируется сигнал 126 Верхняя граниизмеряемого импульса , по которым коды верхней, нижней границ и фазы измеряемого импульса записываются в рет гистры 30 и 31 и узел 42 вьщеления

5 фронтов импульсов соответственно. При считывании 1 из блоков 20 и 21 памяти в блоке 5 дешифрации команд формируются импульсы 129 и 118, по которым коды фазы импульсов и фазы

Ю измеряемого импульса записываются в отправляемый генератор 27 и узел 42 выделения фронтов импульсов соответственно .

Управляемая задержка 74 задержи 5 вает импульс с элемента И 50 на время, необхо димое для занесения информации в блок 23. Задержанный импульс 115 поступает на входы Считывание информации блоков 10 и 17-19,

20 памяти и в блоке 23 устанавлива ет триггер 37 в I, что является сигналом начала работы блока 23. Кроме того, задержанный импульс поступает на элемент 77

задержки, который формирует через время, необходимое для устранения эффекта состязаний, импульс 135 Считывание для блока 8 памяти тестов. Если информация, считанная из блоков

30 20 и 21 памяти, не содержит 1, то триггер 68 не взводится и сигнал начала режима работы блока 23 по линии 137 не поступает в блок 3 сопряжения, вследствие этого управляемая задерж-

35 ка 74 формирует импульс Считывание из блоков памяти без задержки.

В соответствии с информацией, считанной из блоков 20,21,8, 10 и 17 - 19, каждый вывод 26 устройства может

40 находиться в одном из следующих состояний.

Состояние А. Вьщача через вывод 26, соединенньп с соответствующим

45 входом ОК, одного из напряжений U , и и, Ug блока 13 коммутации. При этом на дешифратор 2 поступают сигналы с выходов блока 19 памяти структуры, блока 10 памяти входов-выходов

50 и блока -8 памяти тестов. Причем с блока 10 памяти по данному выводу задается 1 (выход), а с блоков 19 и 8 памяти - логическая 1 или О в зависимости от вида структуры ОК и

заданного в ТН входного сигнала, подаваемого на него. Дешифратор 12 управляет работой блока 13 коммутации. Состояние Б. Прием с вывода 26

ца.

127 Нижняя граница, 118 Фаза сигнала О или 1 с подсоединениеизмеряемого импульса , по которым коды верхней, нижней границ и фазы измеряемого импульса записываются в рет гистры 30 и 31 и узел 42 вьщеления

фронтов импульсов соответственно. При считывании 1 из блоков 20 и 21 памяти в блоке 5 дешифрации команд формируются импульсы 129 и 118, по которым коды фазы импульсов и фазы

измеряемого импульса записываются в отправляемый генератор 27 и узел 42 выделения фронтов импульсов соответственно .

Управляемая задержка 74 задержи вает импульс с элемента И 50 на время, необхо димое для занесения информации в блок 23. Задержанный импульс 115 поступает на входы Считывание информации блоков 10 и 17-19,

памяти и в блоке 23 устанавливает триггер 37 в I, что является сигналом начала работы блока 23. Кроме того, задержанный импульс поступает на элемент 77

задержки, который формирует через время, необходимое для устранения эффекта состязаний, импульс 135 Считывание для блока 8 памяти тестов. Если информация, считанная из блоков

20 и 21 памяти, не содержит 1, то триггер 68 не взводится и сигнал начала режима работы блока 23 по линии 137 не поступает в блок 3 сопряжения, вследствие этого управляемая задерж-

ка 74 формирует импульс Считывание из блоков памяти без задержки.

В соответствии с информацией, считанной из блоков 20,21,8, 10 и 17 - 19, каждый вывод 26 устройства может

находиться в одном из следующих состояний.

Состояние А. Вьщача через вывод 26, соединенньп с соответствующим

входом ОК, одного из напряжений U , и и, Ug блока 13 коммутации. При этом на дешифратор 2 поступают сигналы с выходов блока 19 памяти структуры, блока 10 памяти входов-выходов

и блока -8 памяти тестов. Причем с блока 10 памяти по данному выводу задается 1 (выход), а с блоков 19 и 8 памяти - логическая 1 или О в зависимости от вида структуры ОК и

заданного в ТН входного сигнала, подаваемого на него. Дешифратор 12 управляет работой блока 13 коммутации. Состояние Б. Прием с вывода 26

151

t o к нему выхода ОК. В этом случае замыкается один из ключей 84 и 85 блока 15 задания нагрузок в зависимости от сигналов на выходах элементов И 86 и 87. Если в канале ожидается сигнал О, то замыкается ключ 84 и нагрузка 89 оказывается включенной между источником U| и выходом ОК.

Если в выводе 26 ожидается сигнал 1, то замыкается ключ 87 и нагрузка 88 включается между источником и, и выходом проверяемого блока. Подобным образом могут быть подключены нагрузки (на фиг.4 не показаны) для второго вида структуры между U, U, и выводом 26. На входы элементов И 86 и 87 подаются сигналы с выходов блоков 19, 10 и 8 памяти, причем с выхода блока 10 памяти - О (вывод- вход), с выхода блока 19 памяти - О или 1 в зависимости от структуры .контролируемого элемента, с выхода блока 8 памяти - О или 1 в зависимости от того, какой сигнал ожидается с выхода проверяемого блока.

На первые входы компараторов 82 и 83 в состоянии А или Б подаются из блока 14 эталонные напряжения U°g , и, или 23 соответствую- пще структуре проверяемого блока, и вторые входы соединены с выводами

26. В состоянии А на компараторах

- 11° сравнивается одно из напряжении и, ,

и , и°, U- блока 13 коммутации с

,, о ,т TiO ,т

эталонными и, , U, U, , если .устройство исправно, то с помощью элементов 91, 90 и 94 дешифратора 16 результата формируется результат Годен. В СОСТОЯНИИ В с теми же эталонными уровнями напряжений на компараторах 82 и 83 сравнивается входное напряжение Ug с вывода 26.

Если выполняются условия:

( вх U, при ожидаемой (1)

при ожидаемом О, (2)

то на выходе дешифратора 16 - результат Годен, при невыполнении (1) или (2) - результат Брак.

Состояние В. Контроль состояния Отключено вьшода ОК типа Магистраль. Это состояние в отличие от состояний I и О проверяется за два ТН. В первом ТН по данному выводу с блока 18 памяти состояний считывается 1, с блока 19 памяти структуры-- информация, соответствующая

9540116

структуре проверяемого блока, с блока 10 памяти входов-выходов - О (вход), а с блока 8 памяти тестов - t. Во втором ТН информация с бло5 ков 19, 10 и 18 памяти повторяется, а с блока 8 памяти тестов считывается О. При этом, если с блока 19 памяти считывается О, через нагрузку 88 и ключ 85 к выводу 26 подклю- 0 чается напряжение из блока 14 задания опорных напряжений, а в дешифраторе 16,результата на входы элементов И 90 и 91 в первом ТН подаются соответственно О и 1. Это дости- гается с помощью логических элементов 93 и 94. Во втором ТН через нагрузку 89 и ключ 84 к выводу 26 подключается напряжение U,, а на входы элементов И 90 и 91 подаются соответ20 ственно сигналы 1 и О. Если вывод ОК должен находиться и находится в состоянии Отключено, то его выходное сопротивление значительно больше сопротивления резисторов 88 и 89, и выводу 26 навязывается потенциал и и соответственно в первом и втором ТН, а на выходе элементй ИЛИ 92 в обоих случаях формируется сигнал Годен. Если вывод ОК имеет

25

30

состояние Г или О , а должен находиться в состоянии Отключено, то выходное сопротивление его зна:читель- но меньше сопротивления резисторов 88 и 89, к выводу 26 навязывается по35 хенциал выхода ОК. В-этом случае на одном из ТН на выходе элемента ИЛИ 92 появляется сигнал Брак.

Состояние Г. Канал не контролируется. С соответствующего этому кана- лу разряда блока 17 памяти маски считывается 1 и поступает на вход элемента ИЛИ 92, в результате на его выходе принудительно формируется сигнал Годен без анализа действительного состояния вывода, т.е. вне зависимости от считываемой информации из блоков 20,21,8,10 и 18, памяти. I

В состояниях А-Г после считывания

50 информации из блока 8 памяти тестов через подготовленный элемент И 5 (поскольку триггер 68 в состоянии О) проходит второй импульс по линии 116 с генератора 56 импульсов на

55 опрос дешифратора 16 результата, и через элемент 76 задержки формируется сигнал 117 записи результата в блок 9 памяти результата, по которому результаты с дешифратора 16 ре45

17

fO

зультата записываются в блок 9 памяти по адресу, совпадающему с адресом считывания из блока 8 памяти тестов, Блок 9 памяти подготовлен к записи результатов состоянием 1 триггера 66 по линии 148. Кроме того, импульс с элемента 76 задержки через элемент И 54 устанавливает триггер 67 в О, элемент И 51 закрывается., следующий импульс с генератора 56 проходит через элемент И 50 и добавляет к содержимому счетчика 69 адреса 1 для об ращения к блокам 8,10 и 17 - 2 памяти в следующем такте.

Состояние Д. Выдача через вывод(ы) 26 заданного числа импульсов. Б этом сп5гчае на заданном адресе в соответствующем данному выводу разряде выходного кода с блока 20 памяти признака вьодачи импульсов считывается 1, по которой через элемент ИЛИ 22 триггер 68 БУ 4 устанавливается в 1. Состояние 1 триггера 68 по линии 137 поступает в блок 3 сопряжения, а оттуда в блок I и определяет начало режима загрузки блока 23. Блок 1 передает командные и информационные сообщения в блок 23. По командным сообщениям блок 5 формирует сигналы разрешения занесения в управляемьй генератор 27 кода фазы импульсов по линии 129, а в вычитающий счетчик 38 - кода числа импульсов по линии 119.

После записи информации в блок 23 с управляемой задержки 74 формируется импУльс считывания с блоков 10 и 7 - 19 памяти и через задержку на элементе .77 с блока 8 п-амяти тестов. Кроме того импульс с управляемой задержки 74 поступает в блок 23 и устанавливает триггер 37 в состояние 1, которое определяет начало выдачи пачки импульсов, йчпульсы с управпает на вход элемента 75 задержки, формирующего импульс на своем выходе через время, равное максимальному времени работы блока 23. Импульс 120 с элемента 75 задержки опращивает узел 41 фиксации результата, на второй вход которого поступает сигнал с триггера 37. Если триггер 37 устанавливается в О, на выходе узла 41 фиксации результата появляется сигнал Годен, в противном случае - Брак. Кроме того, импульс с элемента 75 задержки через элемент ИЛИ 60 устанавливает триггер 68 в О, разрешая прохождение импульса с генератора 56 через элемент И 51 на опрос дещифратора 16 результата и затем через задержку 76 на запись результатов с дещифратора 16 в блок 9 памяти результата. Импульс с элемента 75 поступает также в блок 3 сопряжения на сброс режима работы блока 23. В случае результата Годен с блока 23 элемент И 54 подготовлен, и импульс 117с элемента 76 через элемент И 54 устанавливает триггер 67 в О, разрешая прохождение импульса с генератора 56 через элемент И 50 на добавление единицы в счетчик 69 адреса и

считывание информации из блоков 8, 10 и 17 - 21 дан следукщего ТН. В случае результата Брак с блока 23 (импульсы на выводы 26 не поступали или . поступили не все) элемент И 54 не

35 подготовлен и триггер 67 не устанавливается в О, в результате информация для следующего ТН с блоков 8, 10 и 17 - 21 памяти не считывается. Но в этом случае через элемент НЕ 61 подготавливается элемент И 49, импульс с которого по линии 134 поступает на запись результата из блока 23 в 16-й разряд регистра 95 через ключ 97 и в блок 3 сопряжения. Из

20

25

40

ляемого генератора 27 через подготов- блока 3 сопряжения этот импульс поступает в блок 1 и подготавливает его к приему результата. Кроме того, сигнал с выхода элемента И 49 устанавливает триггер 65 БУ 4 в 1. Сигнал

1„50 1 триггера 65 по линии 122 определяет направление сдвигг из регистра 95 через элемент 4И-4ИЛИ 96 в блокЗ.

ленный элемент И 34 проходят на те выводы 26, в которых замкнуты ключи 28, управляемые блоком 20 памяти признака вьщачи импульсов, и параллельно поступают на вычитающий вход счетчика 38. При достижении счетчиком 38 нулевого состояния через элемент ИЛИ 40 триггер 37 устанавливается в О, элемент И 34 закрывается, и прекращается выдача импульсов на выводы 26. Ранее сформированный элементом 77 задержки импульс считывания из блока 8 памяти тестов постуБлок 1 посылает команду Передача 55 результата в блок 3, которая поступает в блок 5, и по сигналу 123 и с его выхода триггер 64 БУ 4 устанавливается в 1, разрешая прохождение импульсов с генератора 55 через элеfO

) 29540118

пает на вход элемента 75 задержки, формирующего импульс на своем выходе через время, равное максимальному времени работы блока 23. Импульс 120 с элемента 75 задержки опращивает узел 41 фиксации результата, на второй вход которого поступает сигнал с триггера 37. Если триггер 37 устанавливается в О, на выходе узла 41 фиксации результата появляется сигнал Годен, в противном случае - Брак. Кроме того, импульс с элемента 75 задержки через элемент ИЛИ 60 устанавливает триггер 68 в О, разрешая прохождение импульса с генератора 56 через элемент И 51 на опрос дещифратора 16 результата и затем через задержку 76 на запись результатов с дещифратора 16 в блок 9 памяти результата. Импульс с элемента 75 поступает также в блок 3 сопряжения на сброс режима работы блока 23. В случае результата Годен с блока 23 элемент И 54 подготовлен, и импульс 117с элемента 76 через элемент И 54 устанавливает триггер 67 в О, разрешая прохождение импульса с генератора 56 через элемент И 50 на добавление единицы в счетчик 69 адреса и

считывание информации из блоков 8, 10 и 17 - 21 дан следукщего ТН. В случае результата Брак с блока 23 (импульсы на выводы 26 не поступали или . поступили не все) элемент И 54 не

35 подготовлен и триггер 67 не устанавливается в О, в результате информация для следующего ТН с блоков 8, 10 и 17 - 21 памяти не считывается. Но в этом случае через элемент НЕ 61 подготавливается элемент И 49, импульс с которого по линии 134 поступает на запись результата из блока 23 в 16-й разряд регистра 95 через ключ 97 и в блок 3 сопряжения. Из

20

25

40

Блок 1 посылает команду Передача 55 результата в блок 3, которая поступает в блок 5, и по сигналу 123 и с его выхода триггер 64 БУ 4 устанавливается в 1, разрешая прохождение импульсов с генератора 55 через эле19

менты И 52 и 46 по линии 105 в блок 3 для синхронизации приема результата последовательным кодом из регист- ра 95, а через элемент ИЛИ 57 по линии 106 - на сдвиговый вход регистра 95. После прохождения восьми импульсов со счетчика 70 байтов сигнал 124 поступает в блок 3, а оттуда - в блок I на сброс готовности к приему результата. Кроме того, этот сигнал через подготовленный элемент И 43 по линии 125 сопровождает передачу результата из блока 3 сопряжения в блок 1.

Состояние Е. Прием импульсного сигнала и контроль его длительности. В отличие от предьщущего состояние Е определяется появлением 1 в соответствующем разряде кода, считанного из блока 21 памяти признака измере- - ния длительности. Аналогично состоянию Д триггер 68 устанавливается в 1, определяя тем самым начало режима работы блока 23.

Блок 1 через блок 3 сопряжения и регистровый блок 6 передает информацию в блок 23. В регистры 30 и 31 по линии I32 заносятся коды нижней и верхней границ длительности контроируемого импульса на фоне команд 126 и 127. По команде 139 в управляеый генератор 27 по линии 132 записывается код частоты заполнения. Узел 42 выделения фронтов по команде 118 с блока 3 настраивается на вьщеление с одного из выводов 26 импульса, ко- торый поступает через соответствую- щий ключ 29. Замыкается тот ключ 29, на которьй поступает 1 с блока 21, по этому же сигналу обнуляется счетчик 39. После записи информации в блок 23 на выходе элемента 74 формируется сигнал 15 5 считывания с блоков 10 и 17 - 19 памяти, а через элемент 77 задержки - сигнал 135 считывания с блока 8 памяти тестов, Передний фронт импульса с ОК через узел 42 вьщеления фронтов устанавливает триггер 36 в 1, что обеспечивает прохождение импульсов запсшне- ния с управляемого генератора 27 через элемент И 35 на счетный вход счетчика 39.

29

Состояние счетчика 39 сравнивает- 55 яa. Блокировка, по которой счется первой 32 и второй 33 схемами сравнения с нижней и верхней границами, содержащимися в регистрах 30 и 31. В момент совпадения кодов

чик 38 устанавливается в состояние, отличное от нулевого, и закрывается по счетному входу. В это же время в управляемый генератор 27 по линии

-15

20

25

счетчика 39 и регистра 30 схема 32 формирует сигнал, который запоминается узлом 4 фиксации результата. Вторая схема 33 сравнения формирует 5 второй сигнал при совпадении кодов счетчика 39 и регистра 31, если к этому моменту времени задний фронт контролируемого импульса через узел 42 выделения фронтов не переключает триггер 36 в О и не отключает тем самым управляемый генератор 27 от входа счетчика 39. На выходе узла 41 фиксации результата появляется сигнал Годен в том спучае, если на него поступает только сигнал со схемы 32 сравнения. Если на узел 41 фиксации результата не поступает никаких сигналов, или поступает сигнал со схемы 33 сравнения, то на его выходе появляется сигнал Брак. Работа устройства после получения сигналов Годен или Брак аналогична работе в состоянии Д. Отличие заключается в том, что в случае формирования сигнала Брак, импульс с выхода элемента 75 задержки БУ 4 проходит не только на опрос узла 41, но установку триггера 36 в О, прекращая тем самым подачу импульсов на счетчик 39. С разрядов блоков 20, 17 и 18 памяти, соответствукядих выводу, находящемуся в состоянии-Е, считывается О. I

Состояние И. Вьщача на ОК через

i -й вывод непрерывной последовательности импульсов до момента прихода перепада напряжения заданной фазы на j-й вывод. На заданном адресе одновременно считываются сигналы 1 в разряде выходного кода блока 20 памяти, соответствующего i-му выводу, и в разряде выходного кода блока 21 памяти, соответствующего, j-му выводу. Этими сигналами через первую 28 и втоТ Ую 29 группы ключевых элементов i-й и j-й выводы соединяются соответственно с выходом элемента И 34 и входом узла 42 выделения фронтов им- Q пульсов, в дальнейшем работа i-ro вывода совпадает с работой в состоянии Д. Отличие заключается в том, что с блока 5 на счетчик 38 во время записи информации в блок 23 поступает ко30

35

40

45

яa. Блокировка, по которой счетчик 38 устанавливается в состояние, отличное от нулевого, и закрывается по счетному входу. В это же время в управляемый генератор 27 по линии

21

132 заносится код фазы импульсов, посылаемых через i-й вывод, а узел 42 по команде 118 с блока 5 настраивается на прием с j-ro вывода заданного перепада напряжения. С выхода элемента 74 формируется сигнал считывания из блоков.10 и 17 - 19, а через элемент 77 задержки - сигнал считывания из блока 8. Кроме того, сигнал с выхода элемента 74 по линии 115 поступает в блок 23 и устанавливает триггер 37 в 1, разрешая прохождение импульсов с г.енератора 27 через элемент И 34 и первую группу ключевых элементов 28 на i-й вывод. Импульсы поступают до появления на J-M выводе ОК ожидаемого перепада напряжения, который через один из ключей 29 и узел 42 вьвделения фронтов поступает на вход -элемента ИЛИ 40, сигнал с выхода которого устанавливает триггер 37 в О и закрывает элемент И 34. Если ожидаемый перепад напряжения в течение времени, определяемого элементом 75 задержки ВУ 4, не появится, по импульсу опроса с элемента 75 сигнал 120 поступает в узел 4 фиксации результата, который вырабатывает сигнал Брак, а триггер 37 через элемент ИЛИ 40 устанавливается в О, запрещая выдачу импульсов на i-й вывод. В дальнейшем работа в состоянии И совпадает с работой в состоянии Д.

Работа устройства на последующих ТН происходит аналогично указанной работе на первом ТН,

Считывание информации из блоков 8, 10 и 17 - 21 памяти и запись результатов в блок 9 памяти идет до совпадения содержимого счетчика 69 адреса и регистра 73 конечного адреса, после чего срабатьшает схема 71 сравнения, сигнал с которой поступает через элемент ИЛИ 58 на запись содержимого регистра 72 начального адреса в счетчик 69, через подготовленный элемент И 47 на установку триггера 65 в 1, а триггера 66 - в О. Состояние О триггера 66 запрещает прохождение импульсов с генератора 56 через элемент И 50 на считывание информации из блоков 8, 10 и 17 - 2 памяти и по линии 148 подготавливает блок 9 памяти результата к чтению. Кроме того, сигнал 130 со схемы 71 сравнения через блок 3 поступает в

95401

блок

22

1 и

10

20

подготавливает его к приему результата.

Состояние 1 триггера 65 по линии 122 определяет направление сдви ; га информацш из регистра 95 через элемент 4И-4ИЛИ 96 в блок 3. Кроме того, 1 с триггера 65 подготавливает элементы И 43 и 48. Блок 1 в случае задания программы одноразового нециклического контроля посыпает команду 108 Последний байт через бх(ок 5 дешифрации команд в БУ 4 на вход элемента И 48, С выхода элемента И 48 в регистр 95 поступает манда 133 на занесение в регистр 95 результата контроля по первому ТН из блока 9 памяти результата. Команда 108, кроме того, через элемент ИЛИ 59 увеличивает на единицу содержимое счетчика 69 адреса. Затем блок 1 посылает команду 123 Передача результата через блок 5 в БУ 4 на установку в 1 триггера 64, в результате запускается схема формирования восьми импульсов сдвига (триггер 64, генератор 55, элементы И 52 и 46, счетчик 70 байтов, элемент ИЛИ 57). После восьмого импульса сигнал с выхода счетчика 70 устанавливает в О триггер 64, запрещая формирование и myльcoв сдвига, и возбуждает элемент И 43, сигнал 125 с выхода которого поступгшт в блок 3 сопряжения в виде команды, сопровождающей пере35 дачу байта результата в блок 1. После того блок 1 снова посьтает команду Передача результата и так до тех пор, пока результаты контроля по первому ТН не передадутся из регистра 95 блока 6 в блок , Затем блок 1 посылает команду 108 Последний байт, по которой в регистр 95 записываются результаты по второму ТН из блока 9 памяти результатов, содержихмое счет чика 69 увеличивается на единицу, после чего опять посылается команда Передача результата и т.д., пока результаты по всем ТН не передадутся из блока 9 памяти в блок 1.

25

30

40

После передачи всех результатов сигнал I30 с выхода схемы 71 сравнения в БУ 4 устанавливает триггер 65 в О, через элемент ИЛИ 58 заносит в счетчик 69 адреса содержимое регистра 72 начального адреса и поступает через блок 3 сопряжения в блок 1, в результате прекращается передача результатов. Результаты 1 онтроля

высвечиваются на индикационном табло блока I.

Режим останова по номеру набора реализуется за счет записи в регистр 73 конечного адреса БУ 4 номера набора, на котором необходимо остановиться.

Циклический режим реализуется путем посылки команды 12 Цикл после занесения информации в блоки 8, 10 и 17 - 21 памяти, В этом случае устанавливается в 1 триггер 62, элемент И 47 закрывается, в результате после вьщачи всех ТН на ОК сигнал со схемы 71 сравнения через элемент 47 не проходит, а триггер 66 не обнуляется, т.е. нет запрета на прохождение импульсов с генератора 56 через элемент И 50. Поэтому происходит циклическое считывание ТН на ОК.

В режиме поиска неисправностей после записи информации в блоки 8, 10 и 17 - 21 памяти из блока 1 через блок 5 в БУ 4 посыпается команда МЗ Диагностика, которая устанавливает триггер 63 БУ 4 в 1. Сигнал с триггера 63 запрещает работу элемента И 48 и разрешает работу элемента И 53.

Режим диагностирования может быть организован двояко (задается переключателем 24 путем коммутации нулевого потенциала на входы 144 и 145 коммутатора 2) - получение 6-разрядной свертки - сигнатуры (О на линии 145 и 1 на линии 144) и получение кода сигналов с выбранного элемента ОК (О на линии 144 и 1 на линии 145)..

Для получения сигнатуры щуп 25 устанавливается на выход элемента ОК, с которого необходимо снять сигнатуру, после чего устройство запускается. Работа устройства протекает аналогично режиму одноразового тестового контроля. Отличие заключается в том, что сигнал с элемента 76 задержки проходит через элемент И 53 и через элемент ИЛИ 57 на сдвиговый вход регистра 95 блока 6. Сигнал с выхода элемента 76 задержки появляется с частотой считьюания ТН из блоков 8, iO и 17-21 памяти, и импульсы сдвига в регистр 95 поступают с такой же частотой. Сигналы со щупа 25 через сумматор 7 и элемент 2И- 2ИЛИ коммутатора 2 поступают на последовательный вход регистра 95. С

0

5

7-9-12- и 16-го разрядов регистра 95 заведены обратные связи на сумматор 7, где происходит их сложение, по модулю два с входной последовательно- 5 стью. По окончании вьщачи всех ТН в первых 16-ти разрядах регистра 95 образуется сигнатура. Затем по команде Передача результата сигнатура побайтно передается в блок 1. После того отыскивается адрес заданного элемента в списке связей и сравнивается эталонная сигнатура на выходе этого элемента с реальной, по- лучен ой-из устройства.

5 При несовпадении сигнатур щуп 25 устанавливается на входе указанного элемента. Снимается реальная сигнатура и сравнивается с эталонной. Совпадение сигнатур на входе элемента и имевшее перед этим несовпадение на выходе означает, что диагностируемый элемент неисправен. Сигнатура с высокой достоверностью позволяет установить был ли сбой в работе контролируемого элемента при подаче на него длинной последовательности 1 и О, что в большинстве случаев позволяет локализовать неисправный элемент. Но иногда необходимо установить на каком такте произошел сбой, например при отладке разрабатываемых логических блоков. Тогда надо запомнить без свертки всю последовательность логических состоя5 НИИ с вывода ОК. Рз этом случае применяют второй метод диагностирования. При этом входная последовательность со щупа 25 поступает не на сумматор 7, а непосредственно через элемент 2И-2ИЛИ коммутатора 2 - на последовательный информационный вход регистра 95. По окончании вьщачи ТН в регистре 95 записывается га-разрядная последовательность, где т- число ТН. . Затем происходит передача т-разряд- ной последовательности из регистра 95 через элемент 4И-4Ш1И 96 в блок 1, который выводит эту последовательность на индикационное табло.

0

0

Из регистра 95 в блок 3 сопряжения через элемент 4И-4ИЛИ 96 передается четыре вида информации: п-раз- рядный результат контроля ОК при наличии разрешающих сигналов 121, 122 и 141 на входах элемента 4И-4ИЛИ 96; одноразрядньпЧ результат контроля, поступающий из блока 23, при наличии разрешающих сигналов 122, 141 HJ42;

251295

16-разрядная сигнатура при наличии разрешающих сигналов 122, 144 и 140; т-разрядная последовательность логических состояний с вывода ОК при ка- личин разрешающих сигналов 122, 145 и 140.

Основньм преимуществом предлагаемого устройства является возможность которую оно предоставляет для охвата автоматизированным тестовым контролем более широкого класса логических блоков, а именно блоков, содержащих счетчики без установочных входов, а также блоков, содержащих элементы с выводами типа Магистраль, например микропроцессорные структуры, микросхемы КМОП серий.

Формула изобретения

1. Устройство для контроля и диагностики логических блоков, содержащее блок задания nporpaMMiii контроля, коммутатор, блок сопряжения, блок управления, блок дешифрации команд, регистр сдвига, сумматор, блок памяти тестов, блок памяти результатов, блок памяти входов-выходов 5 блок компараторов, дешифратор, блок коммутации, блок задания опорных напряжений, причем первый и второй информационные входы-выходы блока сопряжения соединены соответственно с инфopмaп oнI- ы ми входами-выходами блока задания программы контроля и регистра сдвига вход записи-чтения которого соединен с первым выходом блока управления, а выход параллельного кода - с информационными входами блоков памяти тестов и входов-выходов, входы чтения которых и вход чтения блока памяти результатов соединены с вторым выходом блока управления, а входы записи - с соответствующими выходами блока дешифрации команд, ипформащюн ный вход которого сое,цинен с информационным выходом блока сопряжения, управляющий вход-выход которого соединен с первым входом-выходом блокс1 управления, второй вход-выход которого соединен с входом опроса и группой выходов блока дешифрации команд, выход коммутатора соединен с входом последовательного кода регистра сдвига, выходы разрядов которого соединены с первым входом сумматора, второй вход которого и первый информационный вход коммутатора соединены с

5

0

5

выходом niyna, управляюш,и л вход KI:JM- мутатора через переключатель соединен с шиной нулевогс потенциала, выход блока памяти результата соединен с входом параллельного кода регистра сдвига, выход дешифратора соединен с управляющим входом блока коммутации, группа выходов которого является группой выходов устройства для подключения к выводам контролируемого блока, группа информационных входов блока коммутации соединена с выходом блока задания опорных напряжений и первой группой информационньтх входов блока компараторов, вторая группа информационных входов которого соединена с группой входов устройства для подключения к выводам контролируемого блока, первый и второй входы дешифратора соединены соответственно с выходами блоков памяти тестов и входов-выходов., отличающее с я тем. что, с целью расширения номенклатуры контролируемых блоков к расширения функциональных возможностей за счет организации дополнительшлх режимов контроля, устройство содержит блок задания нагрузок, деьшифратор результата, блоки памяти маски, состояний, структуры, блок памяти признака выдачи импульсов, блок памяти признака измерения длительности, элемент И.ПИ и блок контроля времяимпульсных параметров., причем входы записи и чтения блока памяти признака вьщачи импульсов, блока памяти признака измерения длительности, блока памяти состояний, блока памяти маски и блока памяти структуры соединены соответственно с выходами блока дешифра- 1ДИИ команды и вторым выходом блока управления, третий выход которого и выходы блоков памяти тестов, состояний и маски соединены с первьп, вторым, третьим и четвертым входами дешифратора, выход и пятьш вход которого соединеш-л соответственно с инфор- 1

;Q мациоппш-t ВХОДОМ блока памяти результата и выходом блока компараторов, yпpaвляюш й вход которого соединен с выходом блока памяти структуры, третьим входом дешифратора и первьпм

ij2 управляющим входом блока задания нагрузки, второй и третий управляющие , входы которого соединены соответственно с выходами блоков памяти тестов и входоз-Еьгходов, информационный

0

5

0

5

27

иход и выход блока задания нагрузок соединены соответственно с выходом блока задания опорных напряжений и с группой выходов устройства для подключения выводов контролируемого бло- 5 ка, информационные входы блока памяти признака вьщачи импульсов, блока памяти признака измерения длительности, блоков памяти маски, состояний и

и второго регистров образуют инфсул- а- ционный вход-выход блока, входы записи и сброса вычитающего счетчика,, вход установки фазы узла выделения фронтов импульсов, синхровходы первого и второго регистров, вход установки фазы импульса и синхровход управляемого генератора импульсов образуют стробирующий вход блока, вход

структуры соединены с выходом парал- Ю опроса узла фиксации результата, син- лельного кода регистра сдвига, вто- хровход первого триггера, установоч- рой информационный вход-выход которо- ный вход, второго триггера, первый

вход элемента ИЛИ и выход результата

.узла фиксации результата образуют J5

го соединен с информационным входом- выходом блока контроля времяимпульс- ных параметров, управляющий вход-выход которого соединен с третьим входом-выходом блока управления, выходы блоков памяти признака выдачи импульсов и измерения длительности соединены с первым и вторым коммутирующими входами блока контроля времяимпульс- ных параметров и входами элемента ИЛИ, выход которого соединен с входом блока управления, выход сумматора соединен с вторым информационным входом коммутатора, группа информационных входов и стробирующий вход блока контроля времяимпульсных параметров соединены соответственно с группой входов устройства для подключения выводов контролируемого блока и соответствующим выходом блока дешифрации команд. I

2. Устройство по П.1, отличающееся тем, что блок контроля времяимпульсных параметров содержит управляемый генератор импульсов, две группы ключевых элементов, два регистра, две схемы сравнения, два элемента И, два триггера, вычи- таюпщй и суммирующий счетчики, элемент ИЛИ, узел фиксации результата и узел вьщеления фронтов импульсов, причем информационные входы ключевых элементов первой и второй групп образуют группу информационных входов блока, управляющие входы ключевых .элементов первой и второй групп являются соответственно первым и вторым коммутирующими входами блока, выходы ключевых элементов первой группы и выходы первого элемента И объединены и подключены к счетному входу вычитающего счетчика, информационный вход которого, вход задания частоты управляемого генератора импульсов, выход узла фиксации результата и информационные входы первого

-20

25

управляющий вход-выход блока, вход разрешения счета суммирующего счетчика соединен с вторым коммутирующим входом блока, выходы ключевых элементов второй группы соединены с информационным входом узла выделения фронтов импульсов, первый и второй выходы которого соединены с единичным и нулевым входами первого триггера, а третий выход - к первому информаци30

онному входу узла фиксации результата и второму входу элемента ИЛИ, третий вход и выход которого соединены соответственно с выходом вычитающего счетчика и входом сброса второго триггера, выход которого соединен с первым входом первого элемента И и вторым информационным входом узла фикса1 и результата, третий и четвертый входы которого соединены с выхо- 35 дами первой и второй схем сравнения, первые входы которых соединены с выходами первого и второго регистров, а вторые входы соединены с выходом суммирующего счетчика, счетный вход которого соединен с выходом второго элемента И, первый и второй входы которого соединены соответственно с выходом первого триггера и первым выходом управляемого генератора импульсов, второй выход которого соединен с вторым входом первого элемента И,

40

45

3. Устройство поп.1,отли- 50 чающееся тем, что блок управления содержит элементы И, два генератора импульсов, элементы {.ШИ, элемент НЕ, триггеры, счетчик адреса, счетчик байтов, схему сравнения, ре- 55 гистр начального адреса, регистр конечного адреса, элементы задержки, причем выход первого элемента И, входы второго и третьего элементов И, входы сброса первого и второго триг

5540128

и второго регистров образуют инфсул- а- ционный вход-выход блока, входы записи и сброса вычитающего счетчика,, вход установки фазы узла выделения фронтов импульсов, синхровходы первого и второго регистров, вход установки фазы импульса и синхровход управляемого генератора импульсов образуют стробирующий вход блока, вход

Ю опроса узла фиксации результата, син- хровход первого триггера, установоч- ный вход, второго триггера, первый

.узла фиксации результата образуют 5

0

5

управляющий вход-выход блока, вход разрешения счета суммирующего счетчика соединен с вторым коммутирующим входом блока, выходы ключевых элементов второй группы соединены с информационным входом узла выделения фронтов импульсов, первый и второй выходы которого соединены с единичным и нулевым входами первого триггера, а третий выход - к первому информаци0

онному входу узла фиксации результата и второму входу элемента ИЛИ, третий вход и выход которого соединены соответственно с выходом вычитающего счетчика и входом сброса второго триггера, выход которого соединен с первым входом первого элемента И и вторым информационным входом узла фикса1 и результата, третий и четвертый входы которого соединены с выхо- 5 дами первой и второй схем сравнения, первые входы которых соединены с выходами первого и второго регистров, а вторые входы соединены с выходом суммирующего счетчика, счетный вход которого соединен с выходом второго элемента И, первый и второй входы которого соединены соответственно с выходом первого триггера и первым выходом управляемого генератора импульсов, второй выход которого соединен с вторым входом первого элемента И,

0

5

3. Устройство поп.1,отли- 50 чающееся тем, что блок управления содержит элементы И, два генератора импульсов, элементы {.ШИ, элемент НЕ, триггеры, счетчик адреса счетчик байтов, схему сравнения, ре- 55 гистр начального адреса, регистр конечного адреса, элементы задержки, причем выход первого элемента И, входы второго и третьего элементов И, входы сброса первого и второго триг

. 2912

геров, единичный выход третьего триггера, выход счетчика байтов, выход четвертого элемента И, первый вход первого элемента ИЛИ, выход схемь сравнения, синхровход четвертого триггера, первые входы пятого элемента И и второго элемента ИЛИ, информационные входы регистров начального и конечного адреса, выход четвертого триггера образуют первый йход-выход блока, единичные входы третьего и первого триггеров, выход третьего элемента И, первые входы шестого элемента И и третьего элемента ИЛИ, второй, третий и четвертый входы второ- го элемента ИЛИ, единичный вход пятого триггера, синхровходы регистров начального и конечного адреса и единичный вход второго триггера образу ют второй вход-выход блока, единичный вьгход третьего триггера, выходы эле- мента НЕ, шестого, седьмого элементов И, первого элемента ИЛИ, единичный и нулевой выходы второго триггера образуют первый вьгход блока, выход счетчика адреса соединен с первым входом схемы сравнения и является вторым выходом блока, выход седьмого элемента И соединен с единичным входом четвертого триггера, нулевой вход которого и нулевой вход пятого триггера соединены с выходом пятого элемента И, второй вкод которого соединен с выходом первого триггера, вы- ход пятого триггера соединен с первы- ми входами восьмого и девятого элементов И и третьим входом пятого элемента И, выход четвертого триггера соединен с первым входом первого элемента И и вторым входом шестого элемента И, выход второго элемента И соединен с входом сброса третьего триггера, синхровход которого и второй вход первого элемента И соединены с выходом счетчика байтов, выход третьего триггера соединен с первым входом десятого элемента И, второй вход которого соединен с выходом генератора импульсов, а вьгход соединен с вхо

дом счетчика байтов и первым входом четвертого элемента И, второй вход которого соединен с выходом переполнения счетчика байтов, выход регист

. 5

5

0

0

5

0

0130

ра конечного адреса соединен с вторым входом схемы сравнения, выход одиннадцатого элемента И соединен с вторым входом первого элемента ИЛИ,

выход третьего элемента ИЛИ соединен со счетным входом счетчика адреса, выход второго элемента ИЛИ соединен с входами эаписи регистра начального адреса и счетчика адреса, информационный вход которого соединен с выходом регистра начального адреса, вы- х:од восьмого элемента ИЛИ соединен с вторым входом третьего элемента ИЛИ, единичным входом шестого триггера, первым входом первого элемента задержки и соединен с вторым выходом блока, выход второго генератора им- мульсов соединен с вторыми входами

восьмого и девятого элементов И, 1

третьи входы которых соединены соответственно с нулевым и единичным выходами шестого триггера, вход сброса которого соединен с выходом двенадцатого элемента И, первый вход которого, вход элемента НЕ и первый вход четвертого элемента ИЛИ и выход второго элемента задержки образуют третий вход-выход блока, нулевой выход третьего триггера соединен с четвертым ВХОДОМ-девятого элемента И, выход которого является третьим выходом блока и через третий элемент задержки соединен с первым входом один- на;эдатого элемента И, вторым входом двенадцатого элемента И и вторым выходом блока, выход второго элемента задержки соединен с вторым входом четвертого элемента ИЛИ, выход которого соединен с первым входом седьмого элемента И и нулевым входом третьего триггера, единичный вход Koto- рого является входом блока, выход элемента НЕ соединен с вторым входом седьмого элемента И, единичный выход третьего триггера соединен с разрешающим входом первого элемента задержки, выход которого соединен с входом четвертого элемента задержки и с вторым выходом блока, выход четвертого элемента задержки соединен с входом первого элемента задержки и вторым выходом блока.

W «

5)Ш

(0/

130(3) 111(5}

Jlrs) .m(3)

Ш.2

I2в

te

щ

i li

37i

128 Tfff

27

Щ-{Щ(21)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения абонентов с ЭВМ | 1986 |

|

SU1410041A1 |

| Устройство для сопряжения ЭВМ с внешней памятью | 1987 |

|

SU1515166A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ СОПРЯЖЕНИЕМ АБОНЕНТОВ | 1993 |

|

RU2037196C1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| Устройство для сопряжения между абонентами | 1988 |

|

SU1594550A1 |

| Устройство для сопряжения процессора с устройствами вывода | 1984 |

|

SU1206788A1 |

| Устройство для обмена информацией | 1982 |

|

SU1118992A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Имитатор канала | 1985 |

|

SU1287160A1 |

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1980 |

|

SU962899A1 |

Изобретение относится к области вычислительной техники и предназначено для тестового контроля и диагностики логических блоков. Цель изобретения - расширение номенклатуры контролируемых блоков и расширение функциональных возможностей за счет организации дополнительных режимов контроля. Устройство содержит блок сопряжения, блок задания программы контроля, блок дешифрации команд, блок управления, блок задания опорных напряжений, регистр сдвига, коммутатор, сумматор, каналы по числу выводов проверяемого блока, дешифратор, блок коммутации, блок коммутаторов, блоки памяти тестов, результатов, входов- выходов. Введение в устройство 6jjoKa контроля времяимпульсных параметров, блоков памяти маски, структур состояния, признака измерения длительности, признака вьщачи импульсов, элемента ИЛИ, дешифратора результата и блока задания нагрузки позволяет контролировать -параметры входных и выходных сигналов, длительность импульсов, задавать различные рёжшш контроля и осуществлять диагностику методом сигнатурного анализа, подключаясь к контрольным точкам с помощью щупа 2 з.п. ф-лы, 5 ил. с (Л

(1) {т 2В

Редактор И.Шулла

Составитель А.Сиротская

Техред Л.Сердюкова Корректор М.Демчик

618/55

Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская на б., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

(9)

Фаг 5

| Устройство автоматического контроля электронных систем | 1981 |

|

SU980027A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-03-07—Публикация

1984-07-05—Подача