(5А) УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ

1

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах централизованного контроля и управления множеством технологическихили иных параметров, описываемых случайными процессами.

Известно устройство автоматического централизованного контроля процессов, описываемых множеством параметров, содержащее распределяющие и накапливающие схемы, дешифратор, знаковые распределители сигналов, накопительные счетчики, делители напряжения и управляемый ими выходной индикатор ij .

Недостатком известного устройства является низкое быстродействие.

Наиболее близким к изобретению по технической сущности является устройство допускового контроля, содержащее источники сигналов, первый, втооой и третий коммутаторы, блок преооразования, вычислительный блок, блок управления, а также матричный индикатор, к первым входам которого подключены выходы второго KOMMyr Voра, а к вторым - выходы третьего коммутатора, вход которого соединен с первым выходом блока управления, выход которого подключен к первому входу второго коммутатора, а третий - к одному из входов первого

to коммутатора, другие входы которого соединены с выходами источников сигналов, а выход - череаг блок преобразов ния и вычислительный блок - с вторым входом второго коммутатора .

Недостатком известного устройства, является низкое быстродействие, обус ловленное тем, что в каждом цикле обегания контролируемых параметров

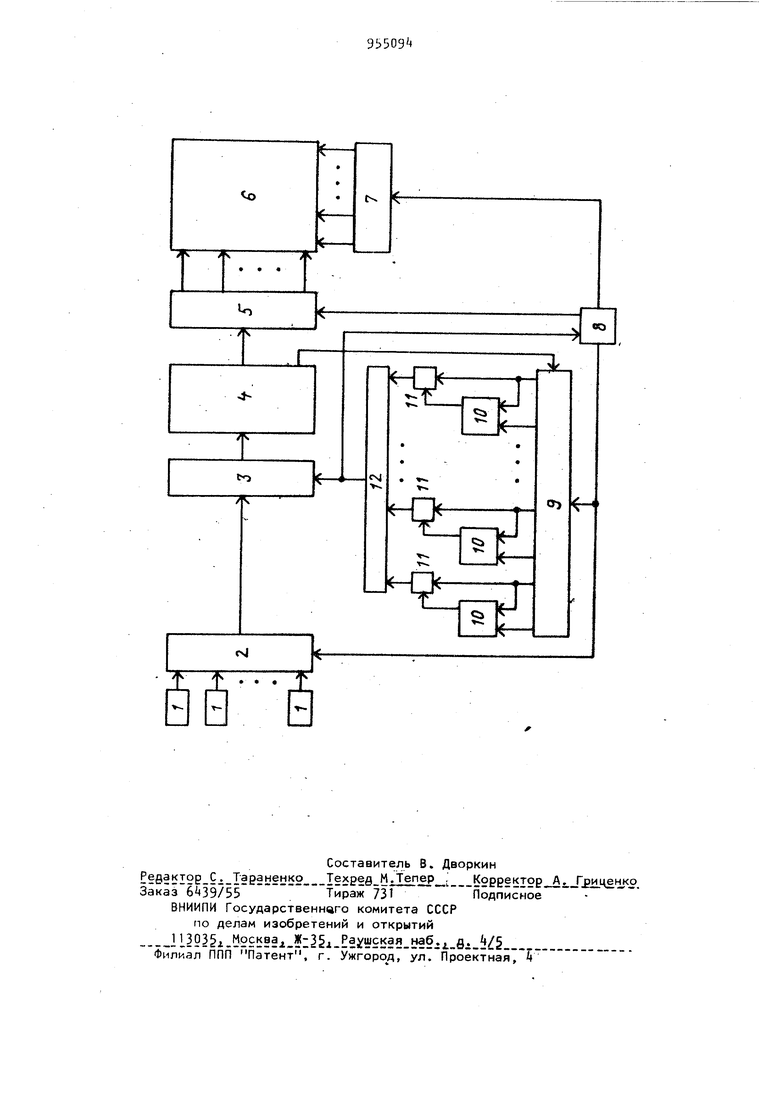

20 время непроизводительно тратится на контроль каждого из них, в том числе и на контроль тех, которые с вероятностью близкой к единице находятся к моменту контроля в состоянии норма из-за чего может задержаться контрол действительно нуждающихся в этом не благополучных параметров. Кроме тог известное устройство реагирует на изменение контрблируемых параметров, вышедших за пределы допуска при их корректировке с помощью управляющих воздействий для приведения их в нор му с большой задержкой вследствие контроля в каждом цикле как годных так и негодных параметров. Цель изобретения - повышение быст родействия устройства обегающего контроля. Поставленная цель достигается тем Что в устройство допуско.вого контроля, содержащее матричный индикатор, к первым входам которого подключены выходы первого коммутатора, а к вторым - выходы второго коммутатора; вход которого соединен с первым выходом блока управления, второй выход которого подключен к первому входу первого коммутатора, а третий - к первому входу третьего коммутатора, вторые входы которого соединены с вы ходами источников сигналов, а выход через преобразователь и вычислитель с вторым входом первого коммутатора, введены четвертый коммутатор,9тригге ры и ключи по Числу источников сигна лов и элемент ИЛИ, входы которого со динены с выходами ключей, а выход управляющим входом преобразователя и с входом блока управления, к третьему выходу которого подключен первый вход четвертого коммутатора, соедине ного вторым входом с дополниетльным выходом вычислителя, нулевой вход каждого триггера соединен с соответствующим выходом четвертого коммутатора, единичный вход - с соответствующим выходом четвертого коммутатора и информационным входом соответст вующего ключа, соединенного управляю щим входом с выходом триггера. На чертеже показана блок-схема устройства. Устройство содержит источники 1 сиганалов, третий коммутатор 2, преобразователь 3, вычислитель , первый коммутатор 5, матричный индикатор 6, второй коммутатор 7, блок 8 управления, четвертый коммутатоо Я, триггеры 10, ключи 11 и элемент-Ч ПИ 12. Устройство работает следующим об разом. В исходном состоянии все триггеры 10 установлены в единицу (единичное состояние i-ro триггера символизирует необходимость контроля i-ro параметра в текущем цикле обегания; в первом цикле контролируются все параметры без исключения), при этом все ключи 1 1 открыты. .Импульс, формируемый на третьем выходе блока 8 управления, подключает к входу преобразователя 3 (через коммутатор 2) выход первого из источников 1 сигнала, а также проходит через коммутатор 9 и первый из открытых ключей 11 на запускающий вход преобразователя 3 и на вход блока 8 управления. Получив этот импульс, блок 8 управления задерживает формирование очередного тактового импульса на своем третьемвыходе на время, достаточное для обработки сигнала первого. из источников 1 в блоках 3-6. Блок 3 обеспечивает преобразование аналогов1 1Х сигналов в код и работает в ждущем режиме - по сигналу с элемента ИЛИ 12, блок 4 сравнивает значения кодов, поступающих с блока 3 и выдает результат через коммутатор 5 на индикатор 6, коммутатор 7 обеспечивает развертку информации по столбцам индикатора б, а коммутатор 5 по колонкам, Если при сравнении текущего си1- нала с границами зоны допуска в блоке А будет получен результат норма, на дополнительном выхоДе блока k возникает импульс, поступающий через коммутатор 9 на нулевой вход первого триггера 10 (таким образом, в следующем цикле обегания первый параметр будет пропущен). После окончания контроля сигнала первого из источников 1 блок 8 управления формирует очередной импульс на третьем выходе, обеспечивающий (совершенно аналогично описанному) контроль выходного сигнала второго из источников 1 и т. п. После обегания всех источников 1 сигнала, т.е. после окончания первого цикла, в единичном состоянии окажутся только те из триггеров 10, номера которых совпадают с номерами источников 1, выходной сигнал которых в момент контроля находился вне нормы (в этом случае импульс на дополнительном выходе блока Ц не возникает) Когда в следующем цикле обегания сигнал такого источьм.жа (жазыпается 5 as снова подключенным к входу блока 3 устройство осуществляет его контроль точно так же, как в предыдущем цикле Если же.к входу блока 3 подключается выходной сигнал i-ro источника контроль которого в предыдущем цикле обеганиядал результат норма, т.е. соответствующий ему 1-й триггер 10 находится в нулевом состоянии, импульс .с первого входа коммутатора 9 не проходит через закрытый при этом i-й ключ 11, таким образом, этот импульс устанавливает i-й триггер 10 в единичное состояние, но на вход блока 3 не поступает, так как имеет дли тельность, меньшую чем время переклю чения триггера 10, не поступает он и на вход блока 8 управления, который в этом случае без задержки формирует на третьем выходе очередной из тактовых импульсов, частота которых ограничивается только быстродействием коммутаторов. Таким образом, в каждом цикле обе гения контролируются выходные сигналы только тех источников 1, триггеры 10 которых (т.е. триггеры 10 с те ми же номерами) находятся в единичном состоянии; в этом состоянии i-й триггер оказывается в трех случаях: в исходном состоянии; в предыдущем цикле сигнал этого источника 1 не контролировался, так как был в норме ;. в предыдущем цикле контроль это го источника 1 дал результат нет нормы. Ввиду того, что время переключения коммутатора 2 существенно меньше времени контроля (преобразования ана лог - код, сравнения с границами нор мы и т.д.), средняя длительность цик ла обегания оказывается существенно меньшей, чем при работе устройствапрототипа, в результате чего парамет ры, выходящие из зоны допуска, контролируются значительно чаще, что дае возможность устройству быстрее реаги ровать на изменение параметров негодных источников 1 и повышает его быстродействие. Формула изобретения Устройство допускового контроля, содержащее матричный индикатор, к первым входам которого подключены выходы первого коммутатора, а к вторым - выходы второго коммутатора, вход которого соединен с первым выходом блока управления, второй выхОд которого подключен к первому входу первого коммутатора, а третий - к первому входу третьего коммутатора, вторые входы которого соединены с выходами источников сигналов, а выход ерез преобразователь и вычислитель с вторым входом первого коммутатора, отличающееся тем, что с целью повышения быстродействия устройства, в него введены четвертый коммутатор, триггеры и кЛючи по числу источников сигналов и элеме :т ИЛИ, входы которого соединены с выходами ключей, а выход - с управляющим входом преобразователя и с входом блока управления, к третьему выходу которого подключен первый вход четвертого коммутатора, соединенного вторым входом с дополнительным выходом вычислителя, причем нулевой вход каждого триггера соединен с соответствующим выходом четвертого коммутатора, а единичный вход - с соответствующим выходом четвертого коммутатора.и информационным входом соответствующего ключа, соединенного управляющим 5 одом с выходом триггера. Источники информации, принятые во внимание при-экспертизе 1.Авторское свидетельство СССР ff 177175, кл. G 06 F 11/00, 1965. 2.Авторское свидетельство СССР № 363982, кл. G 06 F , 1972 (прототип).

JL

IT J

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство автоматизированного контроля | 1987 |

|

SU1525680A2 |

| Устройство автоматического контроля монтажа с радиоэлементами | 1984 |

|

SU1190312A1 |

| Устройство для контроля параметров | 1982 |

|

SU1091127A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ И КОНТРОЛЯ ПАРАМЕТРОВ | 1992 |

|

RU2029345C1 |

| Устройство для контроля и управления технологическими процессами испытаний и тренировки фотоэлектронных умножителей | 1988 |

|

SU1517041A1 |

| Устройство для контроля дискретного объекта | 1984 |

|

SU1218398A1 |

| Устройство допускового контроля параметров | 1991 |

|

SU1798719A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И НАСТРОЙКИ АМПЛИТУДНО-ЧАСТОТНЫХ ХАРАКТЕРИСТИК | 1989 |

|

RU2025899C1 |

| Телеметрическое устройство | 1987 |

|

SU1441433A1 |

| Устройство для допускового контроля параметров | 1977 |

|

SU666546A1 |

Авторы

Даты

1982-08-30—Публикация

1980-05-14—Подача