4

4

4i СО СО

1-1зобретение относится к техннке телекоцтроля и телеуправления и может быть использовано в аптоматизи- ровапгшх системах контроля и управ- лення.

Цель изобретения - повышение достоверности допускового контроля параметров при воздействии случайных импульс ых помех,

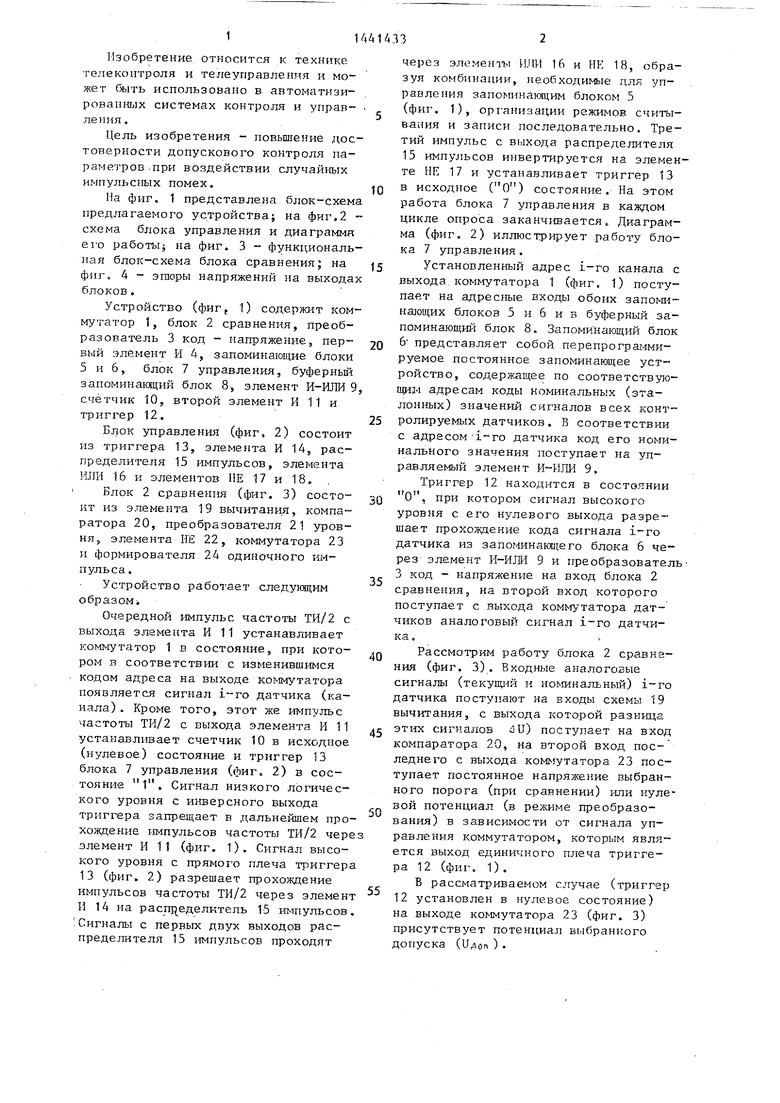

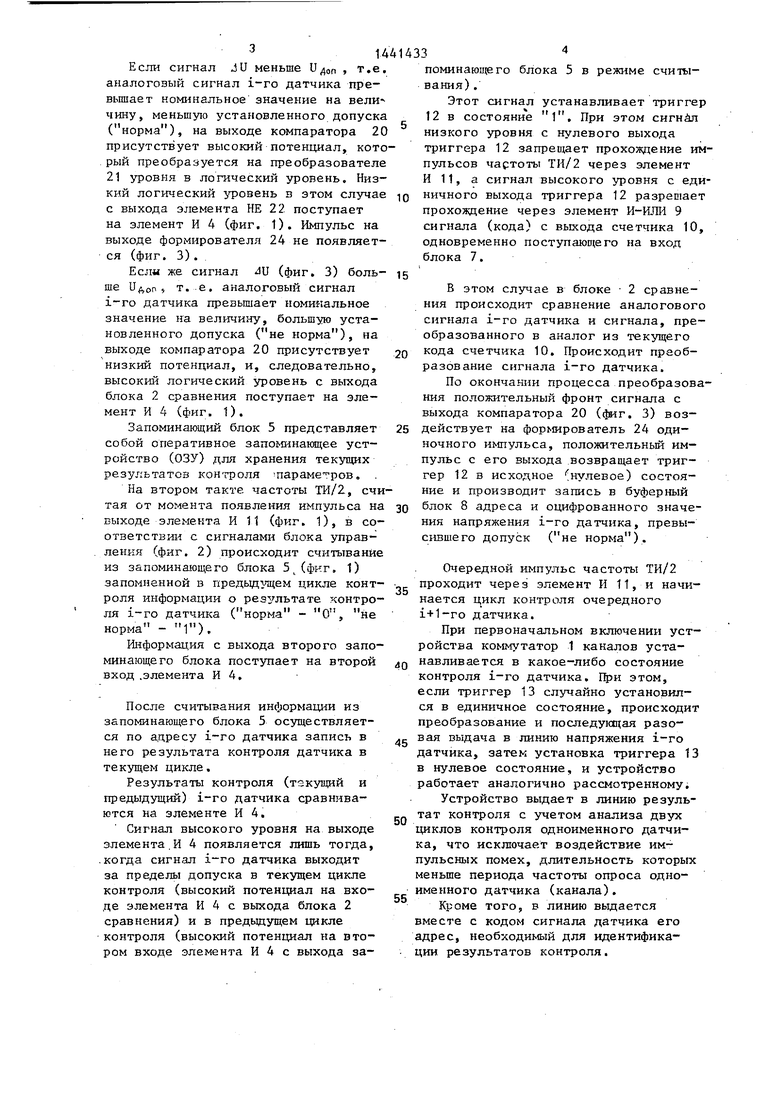

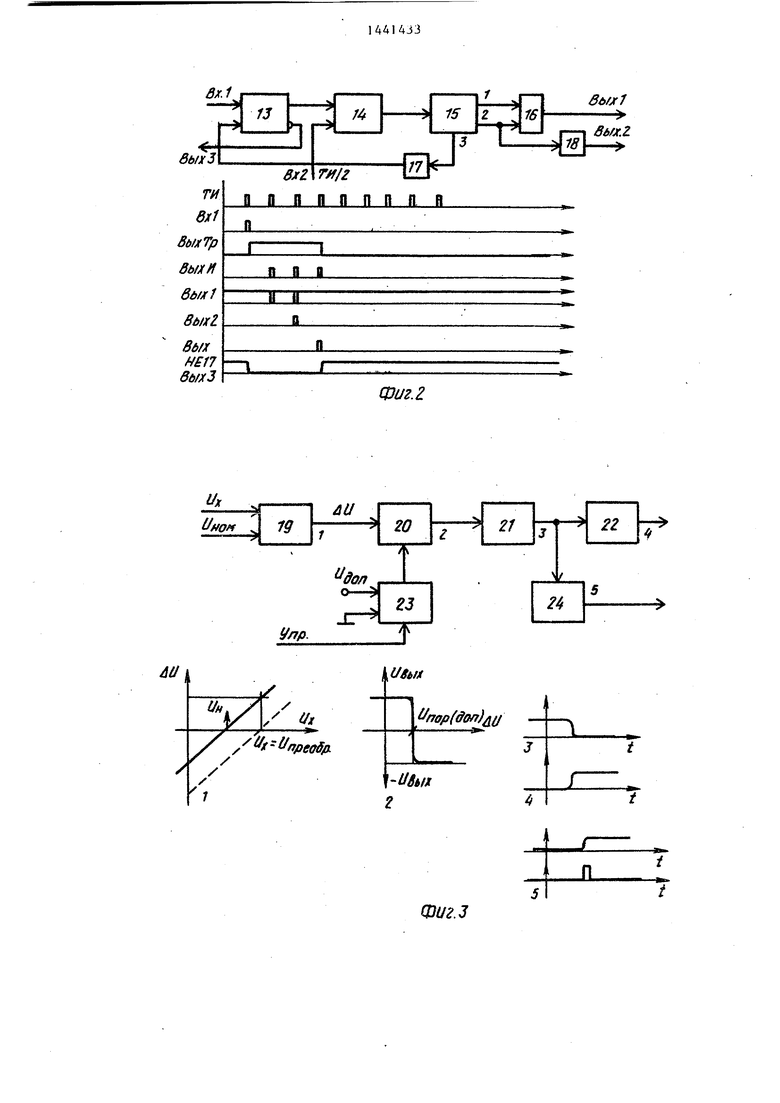

На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг,2 - схема блока управления и диаграммн его работыJ на фиг. 3 - функциональная блок-схема блока сравнения; на фиг, 4 - эпюры напряжений на выходах блоков.

Устройство (фиг, 1) содержит коммутатор 1, блок 2 сравнения, преобразователь 3 код - напряжение, пер- вый элемент И 4, запоминающие блоки 5 и 6, блок 7 управления, буферньй запоминагаций блок 8, элемент И-ИЛИ 9 счётчик 10,, второй элемент И 11 и триггер 12.

Блок управления (фиг, 2) состоит из триггера 13, элемента И 14,, распределителя 15 импульсов, элемента ИЛИ 16 и элементов НЕ 17 и 18. . Блок 2 сравнения (фиг. 3) состо- ит из элемента 19 вычитания, компаратора 20, преобразователя 21 уровня, элемента ИЕ 22, коммутатора 23 и формирователя 24 одиночного импульса.

Устройство работает следующим образом

Очередной импульс частоты ТИ/2 с выхода элемента И 11 устанавливает коммутатор 1 в состояние, при кото- ром в соответствии с изменившимся кодом адреса на выходе коммутатора появляется сигнал i-ro датчика (канала) . Кроме того, этот же импульс частоты ТИ/2 с выхода элемента И 11 устанавливает счетчик 10 в исходное (нулевое) состояние и триггер 13 блока 7 управления (фиг. 2) в состояние 1, Сигнал низкого логичес

кого уровня с инверсного выхода

триггера запрещает в дальнейшем прохождение импульсов частоты ТИ/2 чере элемент И 11 (фиг. 1). Сигнал высокого уровня с прямог о плеча триггера 13 (фиг. 2) разрешает прохождение импульсов частоты ТИ/2 через элемент И 14 на расщ еделктель 15 импульсов, Сигналы с первых двух выходов распределителя 15 импульсов проходят

Q

j

0 5

Q

,„ дс

5

50

через элементы ИЛИ 16 и ИР 18, образуя комбинации, необходимые для управления запоминающим блоком 5 (фиг. 1), орт анизации режимов считывания и записи последовательно. Третий импульс с выхода распределителя 15 импульсов инвертируется на элементе НЕ 17 и устанавливает триггер 13 в исходное (О) состояние. На этом работа блока 7 управления в каждом цикле опроса заканч1шается. Диаграмма (фиг. 2) иллюстрирует работу блока 7 управления.

Установленный адрес i-ro канала с выхода,коммутатора 1 (фиг, 1) поступает на адресные входы обоих запог ш- нающих блоков 5 и 6 и в буферный запоминающий блок 8. Запоминающий блок 6 представляет собой перепрогрш-1ми- руемое постоянное запоминающее устройство, содержащее по соответствую- адресам коды номинальных (эталонных) значений сигналов всех контролируемых датчиков, В соответствии с адресом -i-ro датчика код его номинального значения поступает на управляемый элемент И-ИЛИ 9.

Триггер 12 находится в состоянии О, при котором сигнал высокого уровня с его нулевого выхода разрешает прохождение кода сигнала i-ro датчика из запоминакзцего блока 6 через элемент И-ИЛИ 9 и преобразователь 3 код - напряжение на вход блока 2 сравнения, на второй вход которого поступает с выхода коммутатора датчиков аналоговый сигнал i-ro датчика .

Рассмотрим работу блока 2 сравнения (фиг. 3). Входные аналоговые сигналы (текущ1та и номинальный) i-ro датчика поступают на входы схемы 19 вычитания, с выхода которой разница этих сигналов dU) поступает на вход компаратора 20, на второй вход последнего с выхода коммутатора 23 поступает постоянное напряжение выбранного порога (при сравнении) или нулевой потенциал (в режиме преобразования) в зависимости от сигнала управления коммутатором, которым является выход единичного плеча триггера 12 (фиг. 1).

В рассматриваемом случае (триггер 12 установлен в нулевое состояние) на выходе коммутатора 23 (фиг. 3) присутствует потенциал выбранного допуска ().

Если сигнал JU меньше т.е. аналогозый сигнал i-ro датчика превышает номинальное значение на вели чину, меньшую установленного допуска (норма), на выходе компаратора 20 присутствует высокий потенциал, который преобразуется на преобразователе 21 уровня в логический уровень. Низкий логический уровень в этом случае с выхода элемента НЕ 22 поступает на элемент И 4 (фиг. 1). Импульс на выходе формирователя 24 не появляется (фиг. 3).

Есл« же сигнал V (фиг. 3) боль- ше т. е. аналоговый сигнал i-ro датчика превьшает номинальное значение на величину, большую установленного допуска (не норма), на выходе компаратора 20 присутствует низкий потенциал, и, следовательно, высокий логический уровень с выхода блока 2 сравнения поступает на элемент И 4 (фиг. 1).

Запоминающий блок 5 представляет собой оперативное запоьшнагацее устройство (ОЗУ) для хранения текущих результатов контроля параметров. .

На втором такте частоты ТИ/2, считая от момента появления импульса на выходе элемента И 11 (фиг. 1), в соответствии с сигналами блока управления (фиг. 2) происходит считывание из запоминающего блока 5(фиг. 1) запомненной в предьщущем цикле контроля информации о результате контроля i-ro датчика (норма - О, не норма - 1),

Информация с выхода второго запоминающего блока поступает на второй вход .элемента И 4.

После считывания информации из запоминающего блока 5 осуществляется по а,цресу i-ro датчика запись в него результата контроля датчика в текущем цикле.

Результаты контроля (текущий и предыдущий) i-ro датчика сравниваются на элементе И 4.

Сигнал высокого уровня на выходе элемента.И 4 появляется лишь тогда, .когда сигнал i-ro датчика выходит за пределы допуска в текущем цикле контроля (высокий потенциал на входе элемента И 4 с выхода блока 2 сравнения) и в предьвдущем цикле контроля (высокий потенциал на втором входе элемента И 4 с выхода за

поминаюп1его блока 5 в режиме считывания) .

Этот сигнал устанавливает триггер 12 в состояние 1. При этом сигнал низкого уровня с нулевого выхода триггера 12 запрещает прохождение импульсов частоты ТИ/2 через элемент И 11, а сигнал высокого уровня с единичного выхода триггера 12 разрешает прохол(дение через элемент И-ИЛИ 9 сигнала (кода) с выхода счетчика 10, одновременно поступающего на вход блока 7.

В этом случае в блоке 2 сравнения происходит сравнение аналогового сигнала i-ro датчика и сигнала, преобразованного в аналог из текущего кода счетчика 10. Происходит преобразование сигнала i-ro датчика.

По окончании процесса преобразования положительный фронт сигнала с выхода компаратора 20 ((|иг. 3) воз- действует на формирователь 24 одиночного импульса, положительный импульс с его выхода возвращает трИ1- гер 12 в исходное ;нулевое) состояние и производит запись в буферный блок 8 адреса и оцифрованного значения напряжения i-ro датчика, превы- С1шшего допуск (не норма).

О гередной импульс частоты ТИ/2 проходит через элемент И 11, и начинается цикл контроля очередного i+1-го датчика.

При первоначальном включении устройства коммутатор 1 каналов устанавливается в какое-либо состояние контроля i-ro датчика. При этом, если триггер 13 случайно установился в единичное состояние, происходит преобразование и последугацая разовая выдача в линию напряжения i-ro датчика, затек установка триггера 13 в нулевое состояние, и устройство работает аналогично рассмотренному.

Устройство выдает в линию результат контроля с учетом анализа двух циклов контроля одноименного датчика, что исключает воздействие импульсных помех, длительность которых меньше периода частоты опроса одноименного датчика (канала).

Кроме того, в линию вьщается вместе с кодом сигнала датчика его адрес, необходимый для идентификации результатов контроля.

Формула и

5 3 о

б р е т е н и я

1. Телеметрическое устройство, содержащее коммутатор, коды группы которого являются входами группы устройства, первьй и второй выходы соответственно соединены с входом первого запоъшнающего блока и первым входом блока сравнения, вход коммутатора подключен к выходу первого элеменгга И и объединен с первым входом счетчика, второй вход которого объединен с первым входом первого элемента И и является первым тактовым входом устройства, триггер, первый выход которого соединен с вторым входом первого элемента И и первым входом элемента И-ИЛИ, второй вход которого объединен с вторым входом блока сравнения и подключен к второму выходу триггера, выход счетчика соединен с третьим входом элемента И-ЮТИ, выход которого подключен через преобразователь код - напряжение к TpeTbeNii входу блока сравнения, первый выход которого соединен с первым входом триггера, выход первого запоминающего блока подключен к четвертому входу элe Jeнтa И-ИЛИ, отличающееся тем, что, с целью повышения достоверности допус-- кового контроля параметров при воздействии слут. и fflyльcныx помех, в него введены второй запоминающий блок, .блок управления, второй элемен И и б ферный запоминающий блок, выход и первый вход которого являются соответственно выходом и вторым тактовым входом устройства, второй вход буферного запоминающего блока соединен с выходом счетчика, третий вход с первым выходом блока сравнения, четвертый выход объединен с первЫхМ входом второго запоминающего блока и подключен к первому выходу коммутатора, выход второго запоминающего блока подютючен к первому входу второго элемента И, второй вход которого объединен с вторым входом второго запоминакядего блока и подключен к второму выходу блока сравнения, выход второго элемента И соединен, с вторым входом триггера, пер14А143 3

5

0

5

5

0

5

0

вый выход блока управления подключен к третьему входу первого элекента И,

второй и третий выходы - к треть ; :iy

и четвертому входам второго запомн- нающего блока соответственно, первый вход блока управления является первым тактовым входом устройства, второй вход соединен с выходом первого элемента И,

2,Устройство по п, 1, о т л и - чающееся тем, что блок сравнения содерлсит элемент вычитания, компаратор, преобразователь, уровня сигнала, элемент НЕ, коммутатор и фop шpoвaтeль одиночпого импульса, первый и второй входы элемента вычи- таьшя являются соответственно первым и третьим входами блока, выход элемента вычитания соединем с первым входом компаратора, выход которого через преобразователь уровня сигнала подключен к входам формирователя одиночного импульс-1 и элемента IiE, второй вход компаратора соединен с выходом коммутатора, первый ВГ ЮД которого подклочен к шине допускового потенциала, третий вход является вторым входом блока, выходы элемента НЕ и формирователя однночного нмпуЛ Ьса являются соответственно вторым и первым Быхо.дам 1 блока,

3.Устройство по п. 1, о т л и ч а ю щ е. е с я тем, что блок управления содержит триггер, элемент И, распределитель импульсов, элемент 1-ШИ и элементы FIE, первый .иьгход триггера подключен к перво1- гу входу элемента И, выход которого соединен с входом распределителя импульсов, первьгй выход которого подключен к перво1чу входу элемента ИЛИ, а второй выход - к входу первого элемента iK и второму входу элемента ИЛИ, третий выход - к входу второго элемента НЕ, выход которого соединен с первьим входом триггера, выхо.д элемента ИЛИ является первым выходом блока выход второго элемента НЕ является вторым выходом блока, второй выход триггера - третьим, вторые входы триггера и элемента И соответственно - вторым и первым входами блока.

Фиг. г

| название | год | авторы | номер документа |

|---|---|---|---|

| Телеметрическое устройство для сжатия информации | 1988 |

|

SU1562949A2 |

| ТЕЛЕМЕТРИЧЕСКОЕ УСТРОЙСТВО | 1991 |

|

RU2032228C1 |

| Устройство для распознавания образов | 1986 |

|

SU1361589A1 |

| Информационно-измерительное устройство | 1985 |

|

SU1256074A1 |

| Вероятностный преобразователь аналог-код | 1986 |

|

SU1363461A1 |

| Система телемеханики | 1984 |

|

SU1257686A1 |

| Цифроаналоговый преобразователь | 1990 |

|

SU1790030A1 |

| Устройство для измерения глубинных параметров нефтяной скважины | 1986 |

|

SU1423730A2 |

| Многоканальный анализатор электрофизиологических сигналов | 1991 |

|

SU1806603A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

Изобретение предназначено для допускового контроля параметров, относится к технике телеконтроля и телеуправления и может быть использовано в автоматизированных системах контроля и управления. Цель изобретения - повышение достоверности до- пускового контроля параметров при воздействии случайных импульсных помех. Устройство содержит коммутатор 1, блок сравнения 2, преобразователь код - напряжение 3, элементы И 4, 11, запоминающие блоки 5, 6, блок управления 7, буферный запоминающий блок 8, элемент И-ИЛИ 9 и счетчик 10, триггер 12. Устройство выдает параметры результата контроля с учетом анализа двух циклов контроля датчиков и адрес датчика, необходимый для идентификации результатов контроля. 2 з.п. ф-лы, 4 ип. g

AU

vlf их

/

/

/

x npeoSp.

Ugi,if

пдр(доп)ц

-иВш

г

Фиг.З

ти/г

6ЫХИ1

SbtxSyi

вшбуг.

вЫХбУЗ

вь(хгзв

.чпар выхмг

ёшТро

i/HOf

S{ /JfФO/f (Вых л. cpoS/f.J

| Устройство для допускового контроля | 1977 |

|

SU622059A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Телеметрическое устройство для сжатия информации | 1984 |

|

SU1188775A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1988-11-30—Публикация

1987-06-04—Подача