(21)4088016/24-24

(22)29.07.86

(46) 15.12.88. Вют. № 46

(72) В.А.Чистяков, Т.Ф.Шульга,

Л.Г.Багян, М.Д.Великовский,

М.Г.Биккулов и И.А.Смирнов

(53)681.327 (088.8)

(56)Авторское свидетельство СССР № 1215138, кп. С 29/00, 1984.

Авторское свидетельство СССР 934553, кл. G 11 С 29/00, 1980.

(54)УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ ПАМЯТИ

(57)Изобретение относится к вычислительной технике и может быть использовано при разработке устройств для контроля блоков оперативной памяти с произвольной выборкой. Целью

.изобретения является повышение достоверности контроля. Устройство содер- | жит блок задания тестов, коммутаторы, блок формирования сигналов записи-чтения, генератор тактовых импуль сов, блок задания адреса, блок синхронизации, блок пуска-останова, блок определения числа циклов обращений, блок управления, формирователи считанных сигналов, регистр числа, блок поразрядного сравнения, блок определения адреса ошибки, блок задания динамического режима питания с источниками напряжения питания, блок задания временной-«ыдержки и блок индикации. Устройство обеспечивает контроль блоков оперативной пямяты, выполненных из микросхем памяти, с помощью тестов Марш, Диагональ при.однократном или многократном повторении тестов и автоматическом переключении значений (номинал, максимум и Минимум) напряжений питания микросхем памяти. 14 ил., 1 табл.

S

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля оперативных накопителей | 1989 |

|

SU1705873A1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

| Устройство для контроля памяти | 1984 |

|

SU1236558A1 |

| Устройство для формирования тестов | 1988 |

|

SU1543408A1 |

| Устройство для отладки микроЭВМ | 1987 |

|

SU1553981A1 |

| Устройство для задания тестов | 1983 |

|

SU1168951A1 |

| Устройство для записи и коррекции программ | 1982 |

|

SU1149268A1 |

| Устройство для контроля полупроводниковой памяти | 1986 |

|

SU1403097A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1302281A1 |

4 4

00

со сь

)1зобретение относится к вычислительной технике н может быть использвано при разработке устройств для контроля блоков оперативной памяти с произвольной выборкой.

Целью изобретения является повышение достоверности контроля.

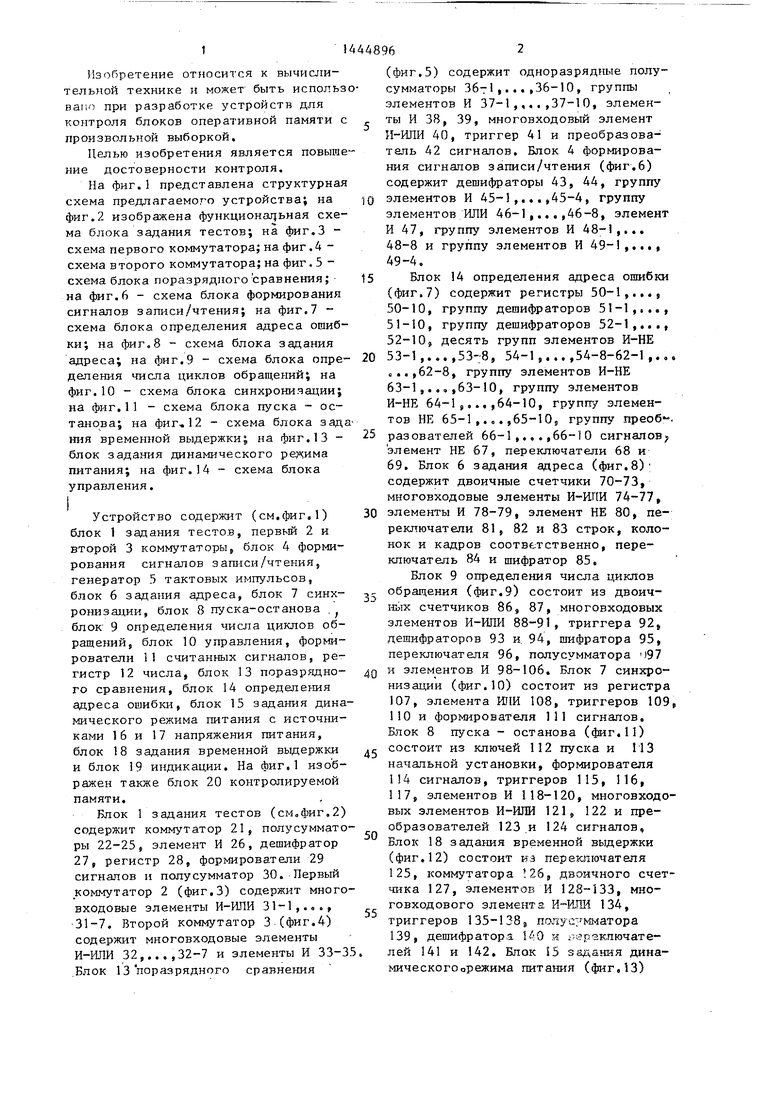

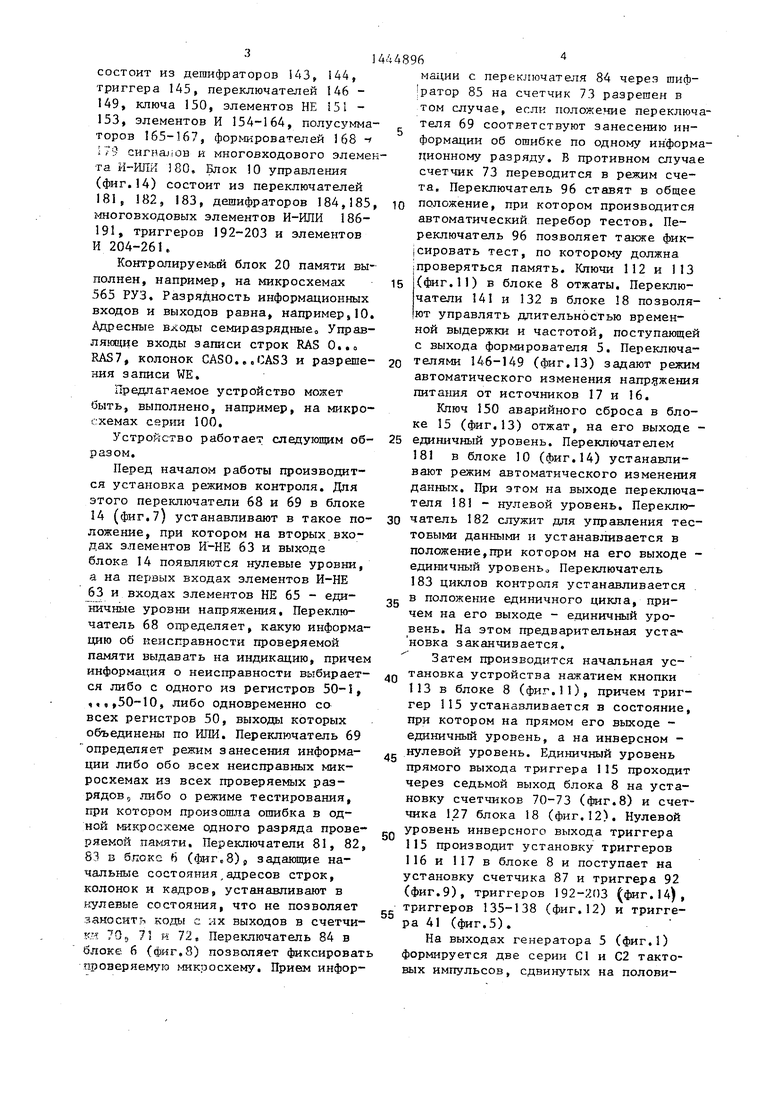

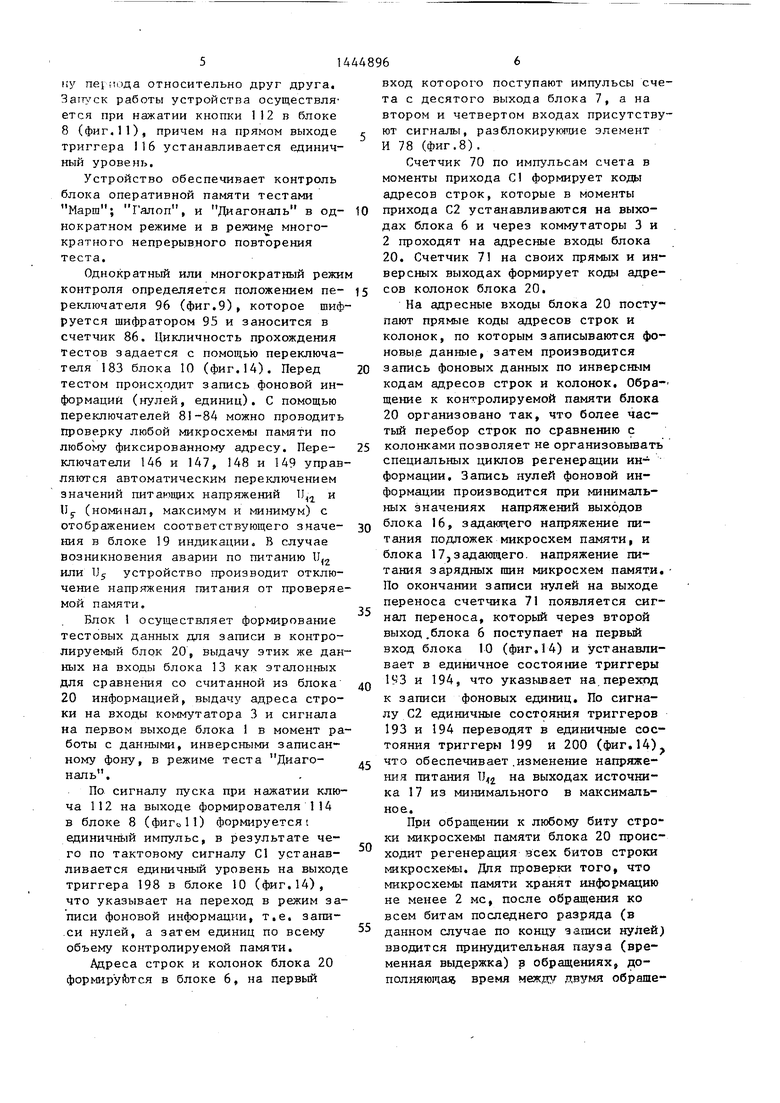

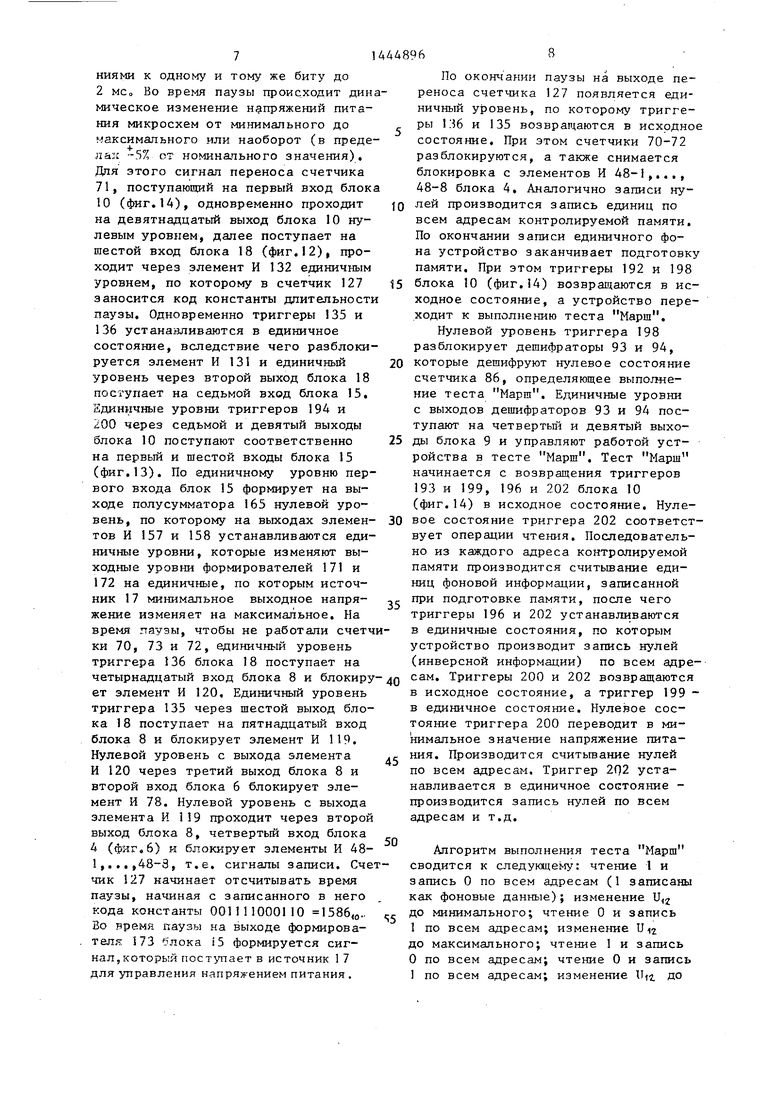

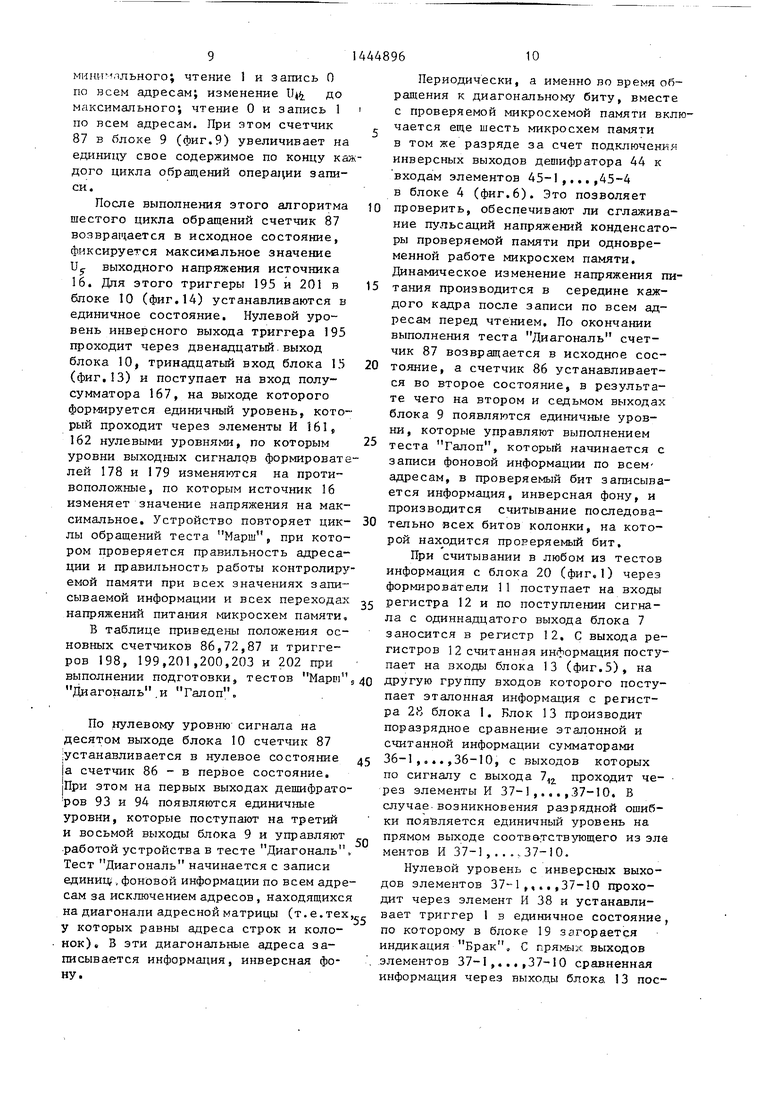

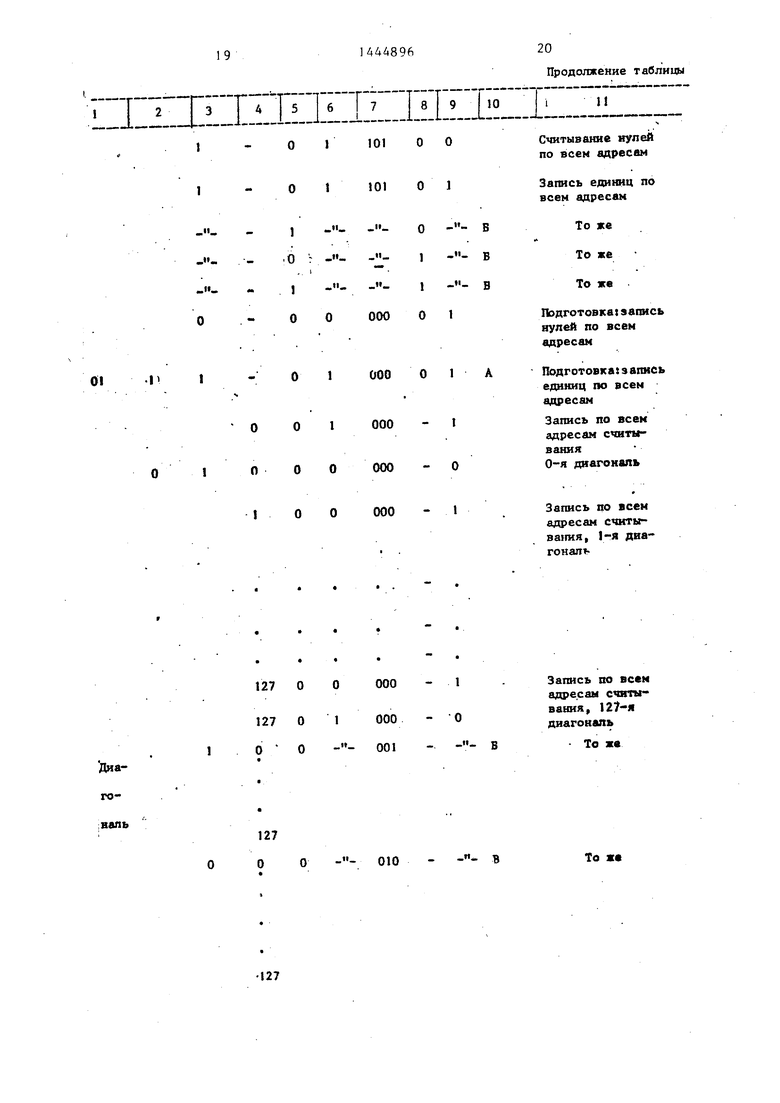

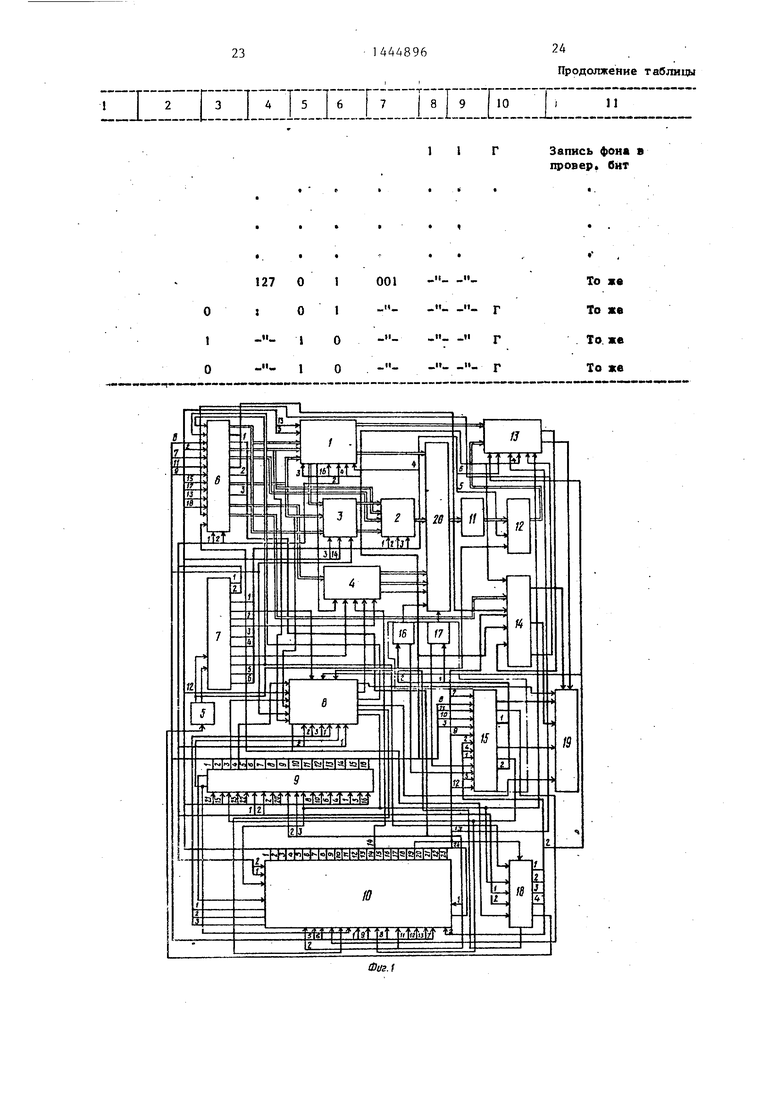

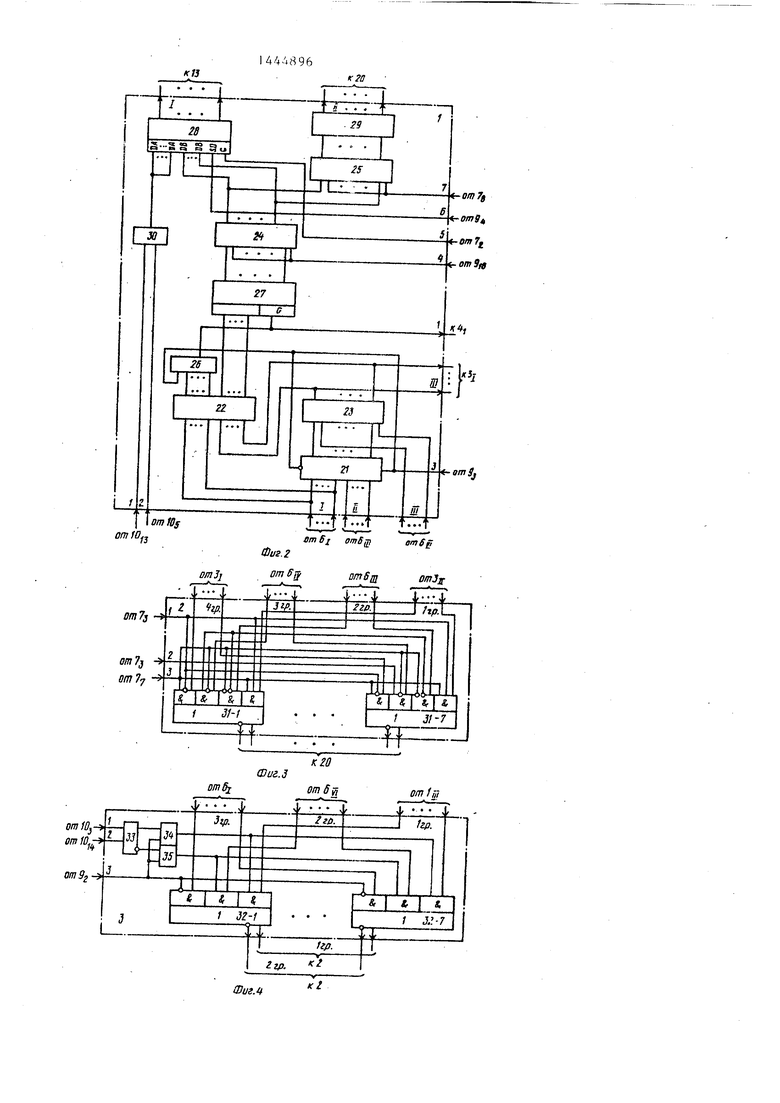

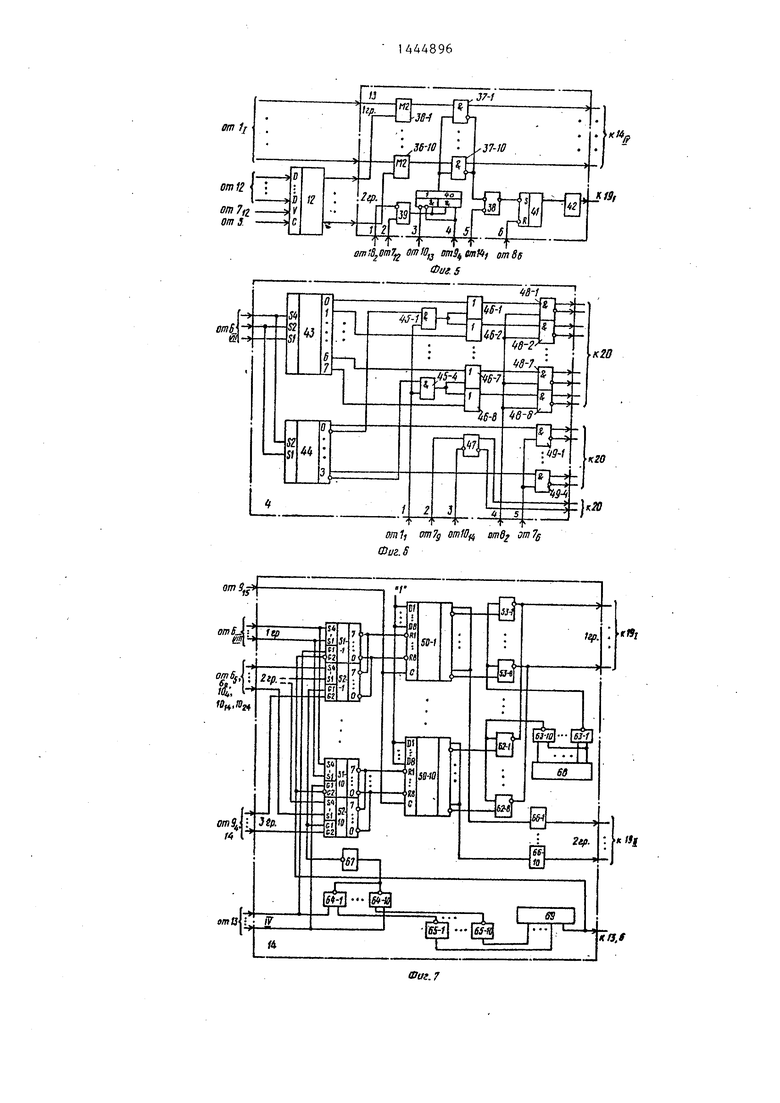

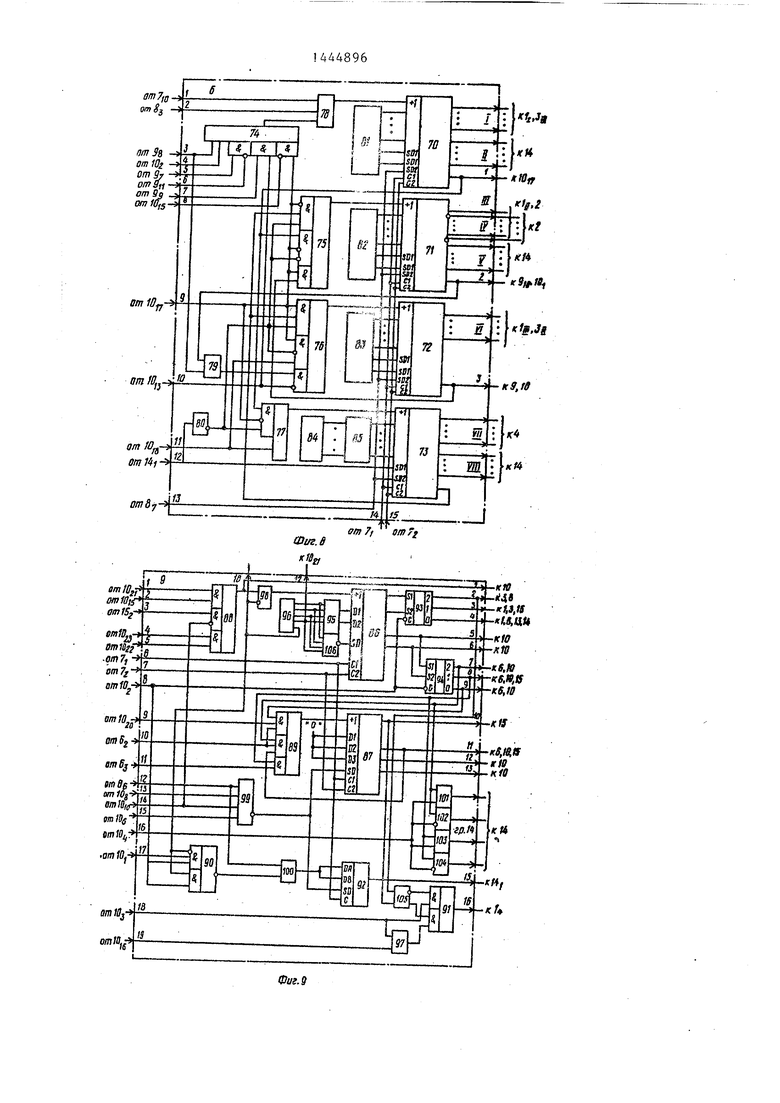

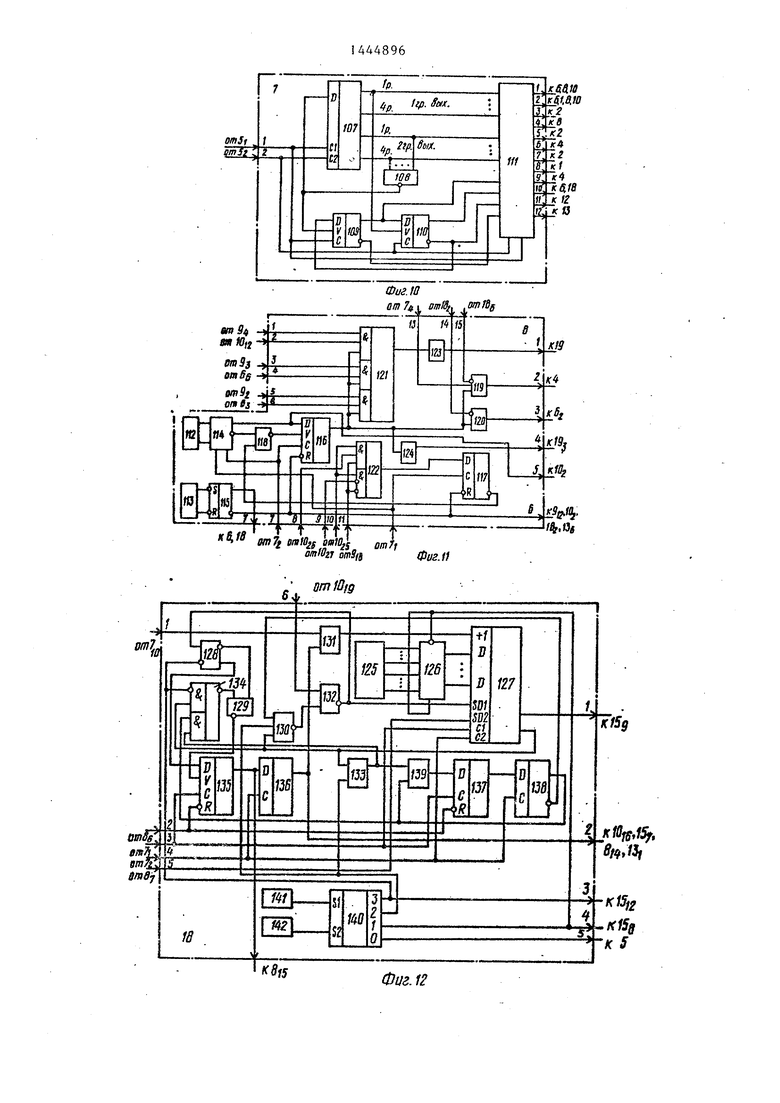

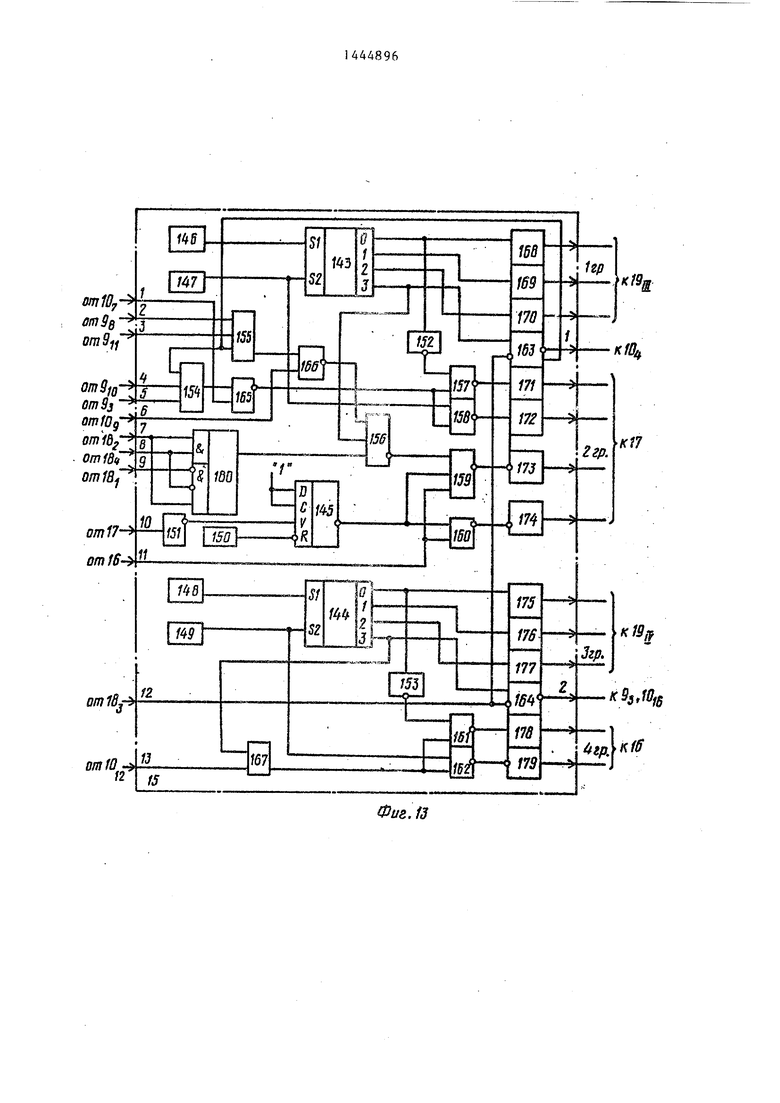

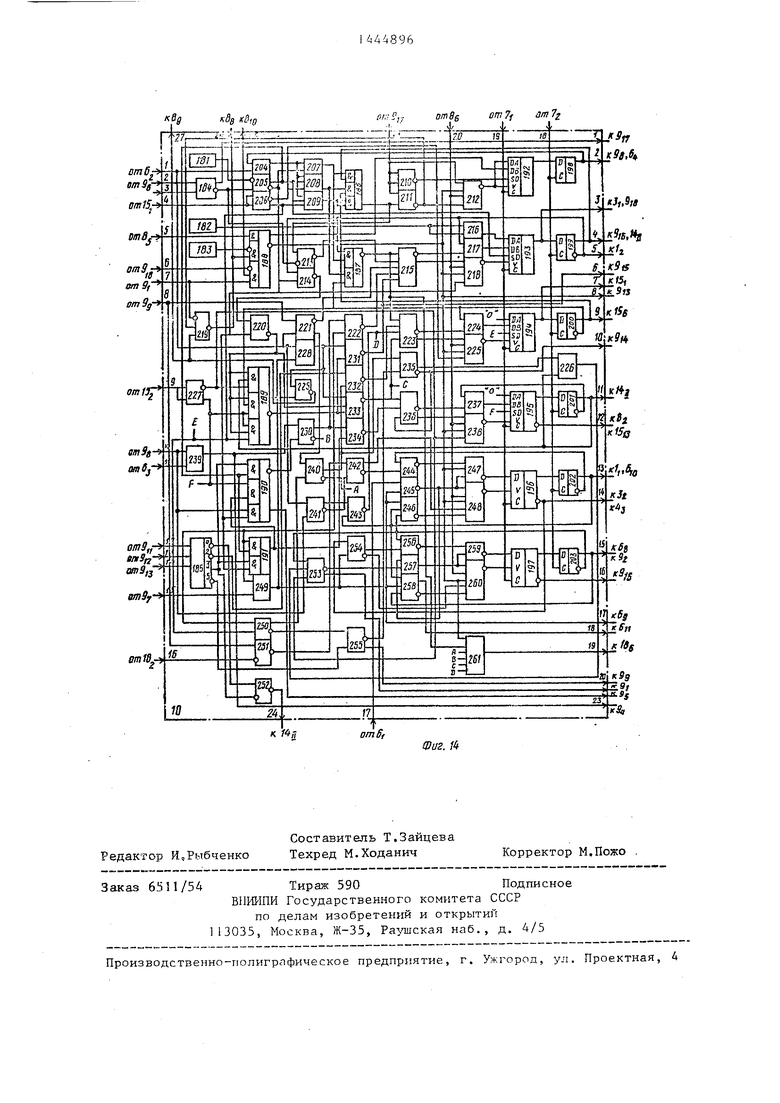

На фиг.1 представлена структурная схема предлагаемого устройства; на фиг.2 изображена функциональная схема блока задания тестов; на фиг.З - схема первого коммутатора; на фиг. 4 - схема второго коммутатора; на фиг. 5 - схема блока поразрядного сравнения; на фиг.6 - схема блока формирования сигналов записи/чтения; на фиг.7 - схема блока определения адреса ошибки; на фиг.8 - схема блока задания адреса; на фиг.9 - схема блока определения числа циклов обращений; на фиг.10 - схема блока синхронизации; на фиг.11 - схема блока пуска - останова; на фиг, 12 - схема блока задания временной выдержки; на фиг.13 - блок задания динамического режима питания; на фиг.14 - схема блока управления.

Устройство содержит (см.фиг.1) блок 1 задания тестов, первый 2 и второй 3 коммутаторыр блок 4 формирования сигналов записи/чтения5 генератор 5 тактовых импульсов, блок 6 задания адреса, блок 7 синхронизации, блок 8 пуска-останова . блок 9 определения числа циклов обращений, блок 10 управления, формирователи 11 считанных сигналов, регистр 12 числа, блок 13 поразрядного сравнения, блок 14 определершя адреса ошибки, блок 15 задания динамического режима питания с источниками 16 и 17 напряжения питания, блок 18 задания временной выдержки и блок 19 индикации. На фиг,1 изображен также блок 20 контролируемой памяти.

Блок 1 задания тестов (смофиг.2) содержит коммутатор 21, полусумматоры 22-25, элемент И 26, дешифратор 27, регистр 28, формирователи 29 сигналов и полусумматор 30. Первый коммутатор 2 (фиг.З) содержит много- входовые элементы И-ИЛИ 31-1,..., 31-7. Второй коммутатор 3 (фиг,4) содержит многовходовые элементы И-ИЛИ 32,..,,32-7 и элементы И 33-3 Блок 13 поразрядного сравне шя

(фиг.З) содержит одноразрядные полусумматоры 36т1...,36-10, группы элементов И 37-1,,..,37-10, элементы И 38, 39, многовходовый элемент Н-ИЛИ 40, триггер 41 и преобразователь 42 сигналов. Блок 4 формирования сигналов записи/чтения (фиг.6) содержит дешифраторы 43, 44, группу элементов И 45- ,,,,,45-4, группу

элементов ИЛИ 46-146-8, элемент

И 47, группу элементов И 48-1,.,. 48-8 и группу элементов И 49-,..., 49-4,

Блок 14 определения адреса ошибки (фиг.7) содержит регистры 50-1,..., 50-10, группу дешифраторов 51-1,..., 51-10, группу дешифраторов 52-1,..., 52-10 десять групп элементов И-НЕ

53-153-8, 54-1,...,54-8-62-1 ....

...,62-8, группу элементов И-НЕ 63-1,..,,63-10, группу элементов И-НЕ 64-164-10, группу элементов НЕ 65-1 ,.,. ,65-10, группу преоб.

разователей 66-1,...,66-1 О сигналов элемент НЕ 67, переключатели 68 и 69. Блок 6 задания адреса (фиг.8); содержит двоичные счетчики 70-73, многовходовые элементы И-ИПИ 74-77,

элементы И 78-79, элемент НЕ 80, переключатели 81, 82 и 83 строк, колонок и кадров соответственно, переключатель 84 и шифратор 85.

Блок 9 определения числа циклов

обращения (фиг.9) состоит из двоич- нь1х счетчиков 86, 87, многовходовых элементов И-ИЛИ 88-91, триггера 92 дешифраторов 93 и. 94, шифратора 95, переключателя 96, полусумматора )97 и элементов И 98-106. Блок 7 синхронизации (фиг.10) состоит из регистра 107, элемента ШШ 108, триггеров 109, ПО и формирователя 111 сигналов. Блок 8 пуска - останова (фиг.II)

состоит из ключей 112 пуска и 113 начальной установки, формирователя 114 сигналов, триггеров 115, 116, 117, элементов И 118-120, многовходовых элементов И-ИЛИ 121, 122 и преобразователей 123 и 124 сигналов. Блок 18 задания временной выдержки (фиг.12) состоит КЗ переключателя 125, коммутатора 126, двоичного счетчика 127, элементов И 128-133, мно- говходового элемента H IfflH 134, триггеров 135-138J полусумматора 139, дешифратора 140 к i -ерэкпючате- лей 141 и 142. Блок 15 задания динамического орежима питания (фиг,13)

состоит из дешифраторов 43, 144, триггера 145, переключателей 146 - 149, ключа 150, элементов НЕ 151 - 153, элементов И 154-164, полусумматоров 165-167, формирователей 168 - 179 cHrHajiOB и многовходового элемента И-ИЛИ 180, Блок 10 управления (фиг.14) состоит из переключателей 181, 182, 183, дешифраторов 184,185 ютоговходовых элементов И-РШИ 186- 191, триггеров 192-203 и элементов И 204-261е

Контролируемый блок 20 памяти выполнен, например, на микросхемах 565 РУЗ, Разрядность информационных входов и выходов равна, напримерj10. Адресные входы семиразрядные Управляющие входы записи строк RAS О,.о RAS7, колонок CASO.,,CAS3 и разрешения записи WE.

Предлагаемое устройство может быть, выполнено, например, на микросхемах серии 100.

Устройство работает следующим об- раэом.

Перед началом работы производится установка режимов контроля. Для этого переключатели 68 и 69 в блоке 14 (фиг.7) устанавливают в такое положение, при котором на вторых входах элементов И-НЕ 63 и выходе блока 14 появляются нулевые уровни, а на первых входах элементов И-НЕ 63 и входах элементов НЕ 65 - единичные уровни напряжения. Переключатель 68 определяет, какую информацию об 1шисправности проверяемой памяти выдавать на индикацию, причем информация о неисправности выбирается либо с одного из регистров 30-1, ,,,,50-10, либо одновременно са всех регистров 50, выходы которых объединены по ИЛИ. Переключатель 69 определяет режим занесения информации либо обо всех неисправных микросхемах из всех проверяемых разрядов, либо о режиме тестирования, при котором произошла ошибка в одной микросхеме одного разряда проверяемой памяти. Переключатели 81, 82, 83 в блоке в (фиг.З), задающие на- чальньш состояния,адресов строк, колонок и кадров, устанавливают в нулевые состояния, что не позволяет заносить коды с их выходов в счетчи- кч 70,, 71 и 72, Переключатель 84 в блоке 6 (фиг,8) позволяет фиксироват проверяемую микросхему. Прием инфор4896

нации с переключателя 84 через шиф- ратор 85 на счетчик 73 разрешен в том случае, если положение переключателя 69 соответствуют занесению инЦ

формации об ошибке по одному информационному разряду. В противном случае счетчик 73 переводится в режим счета. Переключатель 96 ставят в общее 10 положение, при котором производится автоматический перебор тестов. Переключатель 96 позволяет также фик- |сировать тест, по которому должна ;проверяться память. Ключи 112 и 113

15

(фиг.11) в блоке 8 отжаты. Переклю0

0

5

0

5

0

5

чатели 141 и 132 в блоке 8 позволяют управлять длительностью временной выдержки и частотой, поступающей с выхода формирователя 5. Переключателями 146-149 (фиг.13) задают режим автоматического изменения напряжения питания от источников 17 и 16.

Ключ 150 аварийного сброса в блоке 15 (фиг.13) отжат, на его выходе - 5 единичный уровень. Переключателем 181 в блоке 10 (фиг.14) устанавливают режим автоматического изменения данных. При этом на выходе переключателя 181 - нулевой уровень. Переключатель 182 служит для управления тестовыми данными и устанавливается в положение,при котором на его выходе - единичный уровеньо Переключатель 183 циклов контроля устанавливается в положение единичного цикла, причем на его выходе - единичный уровень. На этом предварительная уста новка заканчивается.

Затем производится начальная установка устройства нажатием кнопки 113 в блоке 8 (фиг.11), причем триггер 115 устанавливается в состояние, при котором на прямом его выходе - единичный уровень, а на инверсном - нулевой уровень. Единичный уровень прямого выхода триггера I15 проходит через седьмой выход блока 8 на установку счетчиков 70-73 (фиг.8) и счетчика 127 блока 18 (фиг.12). Нулевой уровень инверсного выхода триггера

115производит установку триггеров

116и 117 в блоке 8 и поступает на установку счетчика 87 и триггера 92 (фиг.9), триггеров 192-203 (фиг.14), триггеров 135-138 (фиг.12) и триггера 41 (фиг.5).

На выходах генератора 5 (фиг.1) формируется две серии С1 и С2 тактовых импульсов, сдвинутых на половипу периода относительно друг друга, Затп ск работы устройства осуществля ется при нажатии кнопки 112 в блоке 8 (фиг.11), причем на прямом выходе триггера 116 устанавливается единичный уровень.

Устройство обеспечивает контроль блока оперативной памяти тестами Галоп, и Диагональ в од- нократном режиме и в режиме многократного непрерывного повторения теста.

Однократный или многократный режи контроля определяется положением пе- реключателя 96 (фиг.9), которое шифруется шифратором 95 и заносится в счетчик 86. Цикличность прохождения тестов задается с помощью переключателя 183 блока 10 (фиг.14). Перед тестом происходит запись фоновой информации (нулей, единиц). С помощью переключателей 81-84 можно проводить проверку любой микросхемы памяти по любому фиксированному адресу. Пере- ключатели 146 и 147, 148 и 149 управляются автоматическим переключением значений питающих напряжений 11 и Uj- (номинал, максимум и минимум) с отображением соответствующего значе- ния в блоке 19 индикации. В случае возникновения аварии по питанию 11,2 или Uj устройство производит отключение напряжения питания от проверяемой памяти.

Блок 1 осуществляет формирование тестовых данных для записи в контролируемый блок 20, выдачу этик же данных на входы блока 13 как эталонных для сравнения со считанной из блока 20 информацией, выдачу адреса строки на входы коммутатора 3 и сигнала на первом выходе блока 1 в момент работы с данными, инверсными записан

ному фону, в режиме теста Диаго-

It

наль .

По сигналу пуска при нажатии ключа 112 на выходе формирователя 114 в блоке 8 (фигоП) формируется единичнЬ1Й импульс, в результате чего по тактовому сигналу С1 устанавливается единичный уровень на выход триггера 198 в блоке 10 (фиг.14), что указывает на переход в режим записи фоновой информации, т.е. запи- .си нулей, а затем единиц по всему объему контролируемой памяти.

Адреса строк и колонок блока 20 формируется в блоке 6, на первый

5 О

О

5

5

0

вход которого поступают импульсы счета с десятого выхода блока 7, а на втором и четвертом входах присутствуют сигналы, разблокирующие элемент И 78 (фиг.8).

Счетчик 70 по импульсам счета в моменты прихода G1 формирует коды адресов строк, которые в моменты прихода С2 устанавливаются на выходах блока 6 и через коммутаторы 3 и 2 проходят на адресные входы блока 20. Счетчик 71 на своих прямых и инверсных выходах формирует коды адресов колонок блока 20.

На адресные входы блока 20 поступают прямые коды адресов строк и колонок, по которым записываются фоновые данные, затем производится запись фоновых данных по инверсным кодам адресов строк и колонок. Обра- щение к контролируемой памяти блока 20 организовано так, что более частый перебор строк по сравнению с колонками позволяет не организовьюать специальных циклов регенерации информации. Запись нулей фоновой информации производится при минимальных значениях напряжений выходов блока 16, задаюР1его напряжение питания подложек микросхем памяти, и блока 17,задающего, напряжение питания зарядных шин микросхем памяти. По окончании записи 1-1улей на выходе переноса счетчика 71 появляется сигнал переноса, который через второй выход .блока 6 поступает на первый вход блока 10 (фиг.14) и устанавливает в единичное состояние триггеры 193 и 194, что указьшает на переход к записи фоновых единиц. По сигналу С2 единичные состояния триггеров 193 и 194 переводят в единичные состояния триггеры 199 и 200 (фиг.14) что обеспечивает.изменение напряжения питания и на выходах источника 17 из минимального в максимальное.

При обращении к любому биту стро ки микросхемы памяти блока 20 происходит регенерация всех битов строки микросхемы, Дпя проверки того, что микросхемы памяти хранят информацию не менее 2 мс, после обращения ко всем битам последнего разряда (в данном случае по концу записи нулей) вводится принудительная пауза (временная выдержка) в обращениях, дополняющая время между двумя обратениями к одному и тому же биту до 2 мс„ Во время паузы происходит динамическое изменение напряжений питания микросхем от минимального до максимального или наоборот (в преде- лак -5% от номинального значения). Для этого сигнал переноса счетчика 71, поступающий на первый вход блока 10 (фиг.14), одновременно проходит на девятнадцать выход блока 10 нулевым уровнем, далее поступает на шестой вход блока 18 (фиг.12), проходит через элемент И 132 единичным уровнем, по которому в счетчик 127 заносится код константы длительности паузы. Одновременно триггеры 135 и 136 устанавливаются в единичное состояние, вследствие чего разблокируется элемент И 131 и единичный уровень через второй выход блока 18 поступает на седьмой вход блока 15. Единичные уровни триггеров 19А и 200 через седьмой и девятый выходы блока 10 поступают соответственно на первый и шестой входы блока 15 (фиг.13). По единичному уровню первого входа блок 15 формирует на выходе полусумматора 165 нулевой уровень, по которому на выходах элемен- 30 вое состояние триггера 202 соответст35

тов и 157 и 158 устанавливаются единичные уровни, которые изменяют выходные уровни формирователей 171 и 172 на единичные, по которым источник 17 минимальное выходное напряжение изменяет на максимальное. На время паузы, чтобы не работали счетчики 70, 73 и 72, единичный уровень триггера 136 блока 18 поступает на четырнадцатый вход блока 8 и блокиру-49 Триггеры 200 и 202 возвращаются ет элемент И 120, Единичный уровень в исходное состояние, а триггер 199 вует операции чтения. Последовательно из каждого адреса контролируемой памяти производится считьшание единиц фоновой информации, записанной при подготовке памяти, после чего триггеры 196 и 202 устанавливаются в единичные состояния, по которым устройство производит запись нулей (инверсной информации) по всем адре

триггера 135 через шестой выход блока 18 поступает на пятнадцатый вход блока 8 и блокирует элемент И 119, Нулевой уровень с выхода элемента И 120 через третий выход блока 8 и второй вход блока 6 блокирует элемент И 78, Нулевой уровень с выхода элемента И 119 проходит через второй выход блока 8, четвертый вход блока А (флг.6) и блокирует элементы И 48- 1,...,, т.е. сигналы записи. Счечик 127 начинает отсчитывать время паузы, начиная с записанного в него кода константы 001111000110 1586,о., Во время паузы на выходе формирователя 173 блока i5 формируется сигнал,который поступает в источник 1 7 для управления напряжением питания .

ААД8968

По окончания паузы на выходе переноса счетчика 127 появляется единичный уровень, по которому триггеры 136 и 135 возвращаются в исходное состояние. При этом счетчики 70-72 разблокируются, а также снимается блокировка с элементов И Д8-1,..., 48-8 блока 4. Аналогично записи ну10 лей производится запись единиц по всем адресам контролируемой памяти. По окончании записи единичного фона устройство заканчивает подготовку памяти. При этом триггеры 192 и 198

iS блока 10 (фиг.14) возвращаются в исходное состояние, а устройство переходит к выполнению теста Марш. Нулевой уровень триггера 198 разблокирует дешифраторы 93 и 94,

20 которые дешифруют нулевое состояние счетчика 86, определяющее выполнение теста Марш. Единичные уровни с выходов дешифраторов 93 и 94 поступают на четвертьш и девятый выхо25 ды блока 9 и управляют работой устройства в тесте Марш. Тест Марш начинается с возвращения триггеров 193 и 199, 196 и 202 блока 10 (фиг.14) в исходное состояние. Нуле

Триггеры 200 и 202 возвращаются в исходное состояние, а триггер 199 вует операции чтения. Последовательно из каждого адреса контролируемой памяти производится считьшание единиц фоновой информации, записанной при подготовке памяти, после чего триггеры 196 и 202 устанавливаются в единичные состояния, по которым устройство производит запись нулей (инверсной информации) по всем адре

в единичное состояние. Нулевое состояние триггера 200 переводит в ми- нимальное значение напряжение питания. Производится считьгеание нулей по всем адресам. Триггер 2f)2 устанавливается в единичное состояние - производится запись нулей по всем адресам и т,д.

Апгоритм выполнения теста Марш сводится к следующему: чтение 1 и запись О по всем адресам (1 записаны как фоновые данные); изменение U, до минимального; чтение О и запись 1 по всем адресам; изменение Ui до максимального; чтение I и запись

0по всем адресам; чтение О и запись

1по всем адресам; изменение Uf до

мин.имлльного; чтение 1 и запись О по всем адресам; изменение . до максимального; чтение О и запись 1 по всем адресам. При этом счетчик 87 в блоке 9 (фиг.9) увеличивает на единицу свое содержимое по концу каждого цикла обращений операции записи.

После выполнения этого алгоритма шестого цикла обращений счетчик 87 возврагчается в исходное состояние, фиксируется максимальное значение

и

15

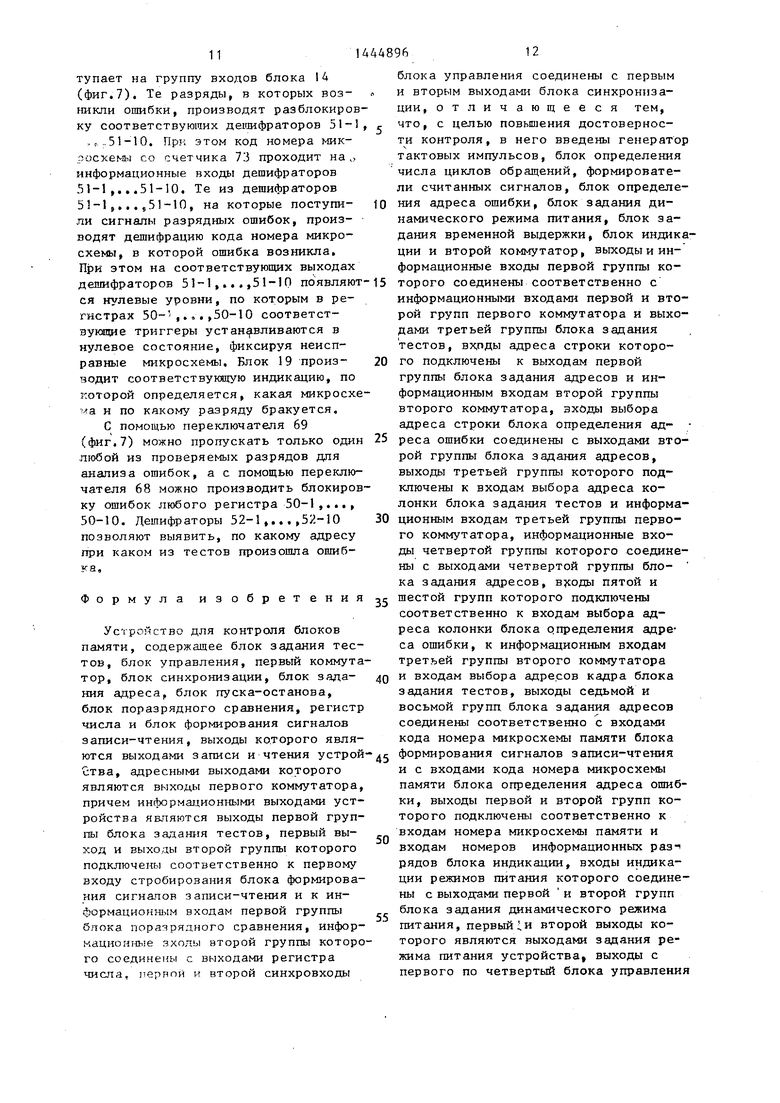

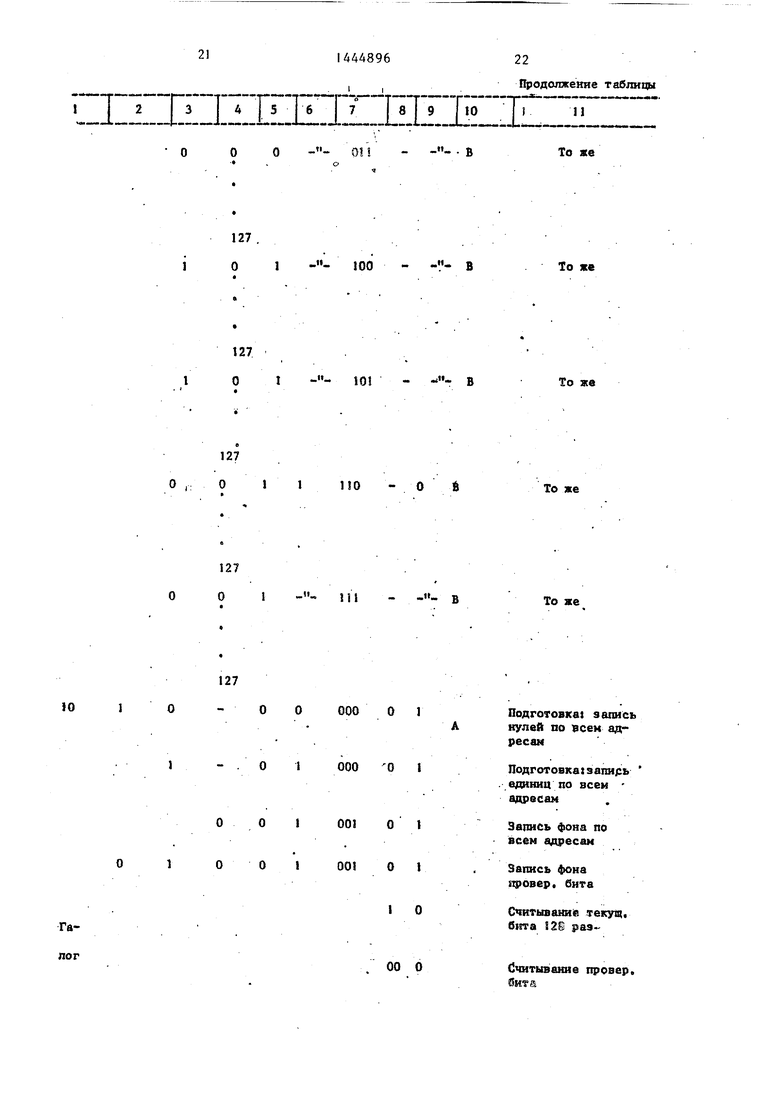

jj. выходного напряжения источника 16. Для этого триггеры 195 и 201 в блоке 10 (фиг,14) устанавливаются в единичное состояние. Нулевой уровень инверсного выхода триггера 195 проходит через двенадцатьй. выход блока 10, тринадцатый вход блока 15 (фиг,13) и поступает на вход полусумматора 167, на выходе которого форг-мруется единичный уровень, который проходит через элементы И 16I 162 нулевыми уровнями, по которым уровни выходных сигналов формировате лей 178 и 179 изменяются на противоположные, по которым источник 16 изменяет значение напряжения на максимальное. Устройство повторяет циклы обращений теста Марш, при котором проверяется правильность адресации и правильность работы контролируемой памяти при всех значениях записываемой информации и всех перекодах 5 напряжений питания микросхем памяти, В таблице приведены положения основных счетчиков 86,72,87 и триггеров 198, 199,201,200,203 и 202 при

Периодически, а именно во время обращения к диагональному биту, вместе I с проверяемой микросхемой памяти вкл чается еще шесть микросхем памяти в том же разряде за счет подключения инверсных выходов дешифратора 44 к входам элементов 45-1,,,,,45-4 в блоке 4 (фиг,6). Это позволяет to проверить, обеспечивают ли сглаживание пульсаций напряжений конденсаторы проверяемой памяти при одновременной работе микросхем памяти. Динамическое изменение напряжения пи тания производится в середине каждого кадра после записи по всем адресам перед чтением. По окончании выполнения теста Диагональ счетчик 87 возвращается в исходное сос20 тояние, а счетчик 86 устанавливается во второе состояние, в результате чего на втором и седьмом выходах блока 9 появляются единичные уровни, которые управляют выполнением

30

25 теста Галоп, который начинается с записи фоновой информации по всем адресам, в проверяемый бит записывается информация, инверсная фону, и производится считывание последовательно всех битов колонки, на которой находится проверяемый бит.

При считывании в любом из тестов информация с блока 20 (фиг.1) через формирователи 11 поступает на входы регистра 12 и по поступлении сигнала с одиннадцатого выхода блока 7 заносится в регистр 12, С выхода регистров 12 считанная информация поступает на входы блока 13 (фиг,5), на

выполнении подготовки, тестов MapDi 540 другую группу входов которого посту Диагональ.и Галоп.

По нулевому уровню сигнала на десятом выходе блока 10 счетчик 87 ;устанавливается в нулевое состояние 5 |а счетчик 86 - в первое состояние, | При этом на первых выходах дешифрато- ров 93 и 94 появляются единичные уровни, которые поступают на третий и восьмой выходы блока 9 и управляют .работой устройства в тесте Диагональ Тест Диагональ начинается с записи единиц;, фоновой информации по всем адресам за исключением адресов , находящихся

50

пает эталонная информация с регистра 28 блока 1. Блок 13 производит поразрядное сравнение эталонной и считанной информации сумматорами 36-1,,..,36-10, с выходов которых по сигналу с выхода 7,. проходит че-

рез элементы И 37-137-10. В

случае.возникновения разрядной ошибки появляется единичный уровень на прямом выходе соотватствующего из эла ментов И 37-1,...37-10.

Нулевой уровень с инверсных выходов элементов 37-1,,.,,37-10 проходит через элемент И 38 и устанавливает триггер 1 в единичное состояние, по которому в блоке 19 загорается индикация Брак, С прямых, выходов элементов 37-1,.,.,37-10 сравненная информация через выходы блока 13 посна диагонали адресной матрицы (т.е.тех,, у которых равны адреса строк и колонок), 3 эти диагональные адреса записывается информация, инверсная фону.

15

5

44489610

Периодически, а именно во время обращения к диагональному биту, вместе I с проверяемой микросхемой памяти вклю- чается еще шесть микросхем памяти в том же разряде за счет подключения инверсных выходов дешифратора 44 к входам элементов 45-1,,,,,45-4 в блоке 4 (фиг,6). Это позволяет to проверить, обеспечивают ли сглаживание пульсаций напряжений конденсаторы проверяемой памяти при одновременной работе микросхем памяти. Динамическое изменение напряжения питания производится в середине каждого кадра после записи по всем адресам перед чтением. По окончании выполнения теста Диагональ счетчик 87 возвращается в исходное сос

тояние, а счетчик 86 устанавливается во второе состояние, в результате чего на втором и седьмом выходах блока 9 появляются единичные уровни, которые управляют выполнением

теста Галоп, который начинается с записи фоновой информации по всем адресам, в проверяемый бит записывается информация, инверсная фону, и производится считывание последовательно всех битов колонки, на которой находится проверяемый бит.

При считывании в любом из тестов информация с блока 20 (фиг.1) через формирователи 11 поступает на входы регистра 12 и по поступлении сигнала с одиннадцатого выхода блока 7 заносится в регистр 12, С выхода регистров 12 считанная информация поступает на входы блока 13 (фиг,5), на

другую группу входов которого посту

пает эталонная информация с регистра 28 блока 1. Блок 13 производит поразрядное сравнение эталонной и считанной информации сумматорами 36-1,,..,36-10, с выходов которых по сигналу с выхода 7,. проходит че- рез элементы И 37-137-10. В

случае.возникновения разрядной ошибки появляется единичный уровень на прямом выходе соотватствующего из эла ментов И 37-1,...37-10.

Нулевой уровень с инверсных выходов элементов 37-1,,.,,37-10 проходит через элемент И 38 и устанавливает триггер 1 в единичное состояние, по которому в блоке 19 загорается индикация Брак, С прямых, выходов элементов 37-1,.,.,37-10 сравненная информация через выходы блока 13 поступает на группу входов блока 14 (фиг.7). Те разряды, в которых воз- никли ошибки, производят разблокировку соответствуютих дешифраторов 51-1

,,.51-10. Прк этом код номера мик- pocxeNttii со счетчика 73 проходит на ,, информационные входы дешифраторов 51-1 ,...51-10. Те из дешифраторов 51-1,...851-10, на которые поступи- ли сигналы разрядных ошибок, производят дешифрацию кода номера микросхемы, в которой ошибка возникла. При этом на соответствующих выходах дешифраторов 51-1,...,51-10 появляют ся нулевые уровни, по которым в регистрах 50-,.,.,50-10 соответст- вукяцие триггеры устанавливаются в нулевое состояние, фиксируя неисправные микросхемы. Блок 19 произ- водит соответствукнцую индикацию, по которой определяется, какая микросхема и по какому разряду бракуется.

С помощью переключателя 69 (фиг.7) можно пропускать только один из проверяемых разрядов дпя анализа ошибок, а с помощью переключателя 68 можно производить блокировку ошибок любого регистра 50-1,..., 50-10. Дешифраторы 52-1,.,. ,5ii-10

позволяют выявить, по какому адресу при каком из тестов произошла ошибка,

Формула изобретения

Устройство для контроля блоков памяти, содержащее блок задания тестов, блок управления, первый коммутатор, блок синхронизации, блок зада- ния адреса, блок пуска-останова, блок поразрядного сравнения, регистр числа и блок формирования сигналов записи-чтения, выходы которого являются выходами записи и чтения устрой Ства, адресными выходами которого являются выходы первого коммутатора, причем информагдионными выходами устройства являются выходы первой группы блока задания тестов, первый выход и выходы второй группы которого подключены соответственно к первому входу стробирования блока формирования сигналов записи-чтения и к информационным входам первой группы блока поразрядного сравнения, информационные зхолы второй группы которого соединены с выходами регистра числа, перяой и второй синхровходы

5 0

5 0

5

0

0

блока управления соединены с первым и вторым выходами блока синхронизации, отличающееся тем, что, с целью повышения достоверности контроля, в него введены генератор тактовых импульсов, блок определения числа циклов обращений, формирователи считанных сигналов, блок определения адреса ошибки, блок задания динамического режима питания, блок задания временной выдержки, блок индикации и второй коммутатор, выходы и информационные входы первой группы которого соединены соответственно с информационными входами первой и второй групп первого коммутатора и выходами третьей группы блока задания тестов, входы адреса строки которого подключены к выходам первой группы блока задания адресов и информационным входам второй группы второго коммутатора, входы выбора адреса строки блока определения ад- раса ошибки соединены с выходами второй группы блока задания адресов, выходы третьей группы которого подключены к входам выбора адреса колонки блока задания тестов и информационным входам третьей группы первого коммутатора, информационные входы четвертой группы которого соединены с выходами четвертой группы бло- ка задания адресов, пятой и шестой групп которого подключены соответственно к входам выбора адреса колонки блока определения адреса ошибки, к информационным входам третьей группы второго коммутатора и входам выбора адресов кадра блока задания тестов, выходы седьмой и восьмой групп, блока задания адресов соединены соответственно с входами кода номера микросхемы памяти блока формирования сигналов записи-чтения и с входами кода номера микросхемы памяти блока определения адреса ошибки, выходы первой и второй групп которого подключены соответственно к входам номера микросхемы памяти и входам номеров информационных раз- рядов блока индикации, входы индикации режимов питания которого соединены с выходами первой и второй групп блока задания динамического режима питания, первый.и второй выходы которого являются выходами задания режима питания устройства, выходы с первого по четвертый блока управления

подклю- ены соответственно к входу sanycica режима теста Марш, входу запуска режима записи фоновой информации, входу блокировки записи фоне- вой информации и входу данных числа циклов блока определения числа циклов обращений, первый выход которого соединен с входом сигнала окончания цикла контроля блока управления, вто рой и третий выходы которого подключены соответственно к перв)му входу разрешения счета блока задания адреса и к первому входу управления второго коммутатора, второй вход управления которого соединен с вторым выходом блока определения числа циклов обращений и первым входом признака рабочего состоя}шя устройства блока пуска-останова, второй и третий входы рабочего состояния устройства которого подключены соответственно к третьему и четвертому выходам блока определения числа циклов обращений, пятый и шестой выходы ко- торого соединены соответственно с первым и вторым входами задания номера теста блока управления, пятый и шестой выходы которого подключены соответственно к входу управления данными блока задания тестов и к входу задания числа обращений в режиме Диагональ блока определения числа циклов обращений, седьмой и восьмой выходы которого соедине -1ы соответственно с вторым и третьим входами разрешения счета блока задания адресов, четвертый вход разрешения счета которого подключен к девятому выходу блока определения числа циклов обращений, десятый и одиннадцатый выходы которого соединены соответственно с первым и вторым входами управления изменением напряжения питания блока задания динами- ческого режима питания, третий вход управления изменением напряжения питания которого подключен к седьмому выходу блока управления, входы режимов теста Галоп, теста Диаго- наль и теста Марш которого соединены соответственно с выходами с седьмого по девятый блока определени числа циклов обращений, выходы с один надцатого по тринадцатый которого подключены соответственно к пepвo ry, второму и третьему входам номера цикла контроля блока управления, восьмо выход которого соединен с входом

пуска блока определения числа циклов обращений, третий, восьмой выходы которого подключены соответственно к первому и второму входам режима теста Диагональ блока задания динамического режима питания, четвертый вход управления изменением напряже- ния питания которого соединен с девя тым выходом блока управления, деся тый выход которого подключен к входу сигнала окончания теста Марш блока определения числа циклов контроля, четвертый и четырнадцатый выходы которого соединены с входами признаков тестов блока определения адреса ошибки,синх- ровход которого подключен к пятнадцатому выходу блока определения числа циклов контроля, третий, четвертый и шестнадцатый выходы которого соединены соответственно с входом задания теста Диагональ, входом зада- теста Марш и входом у прав л е ния данными блока задания тестов, синхровход которого подключен к второму выходу блока синхронизации, первый и второй выходы которого подключены к синхровходам блока задания адресов, блока определения числа циклов обращений, блока задания временной выдержки и блока пуска- останова, четвертый вход признака рабочего состояния устройства кото- рого соединен с двенадцатым выходом блока управления, тринадцатый выход которого подключен к входам признака режима записи блока поразрядного сравнения, блока задания тестов и блока задания адресов, входы режима записи второго коммутатора и формирователей сигналов записи-чтения соединены с четырнадцатым выходом блока управления, пятнадцатый выход которого подключен к пятому входу разрешения счета блока задания адресов и входу запуска счета адреса строки блока определения числа циклов контроля, вход управления изменением данных которого соединен с шестнадцатым выходом блока управления, семнадцатый и восемнадцатый выходы которого подключены соответственно к входу угтравления изменением адреса и входу запуска счета номера микросхемы памяти блока задания адресов, вход задан дя адреса контролируемого разряда которого соединен с выходом блока определения адреса и входом установки

жима контроля по разрядам блока поразрядного сравнения, выходы группы которого соединены с входами кодов ошибок блока определения адреса ошиб .:Н|, вход разрешения выдачи резуль- ата блока поразрядного сравнения подключен к четвертому выходу блока определения числа циклов обращений, семнадцатый и восемнадцатый выходы которого соединены соответственно с входом режима записи фоновой информации блока управления и с первым входом разрешения выдачи сигнала пуска блока-останова и входом режима тестирования блока управления, левятнадцатьй выход которого подключен к входу управления временной выдержкой блока задания временной выдержки, первый вход начальной новки которого соединен с шестым }зыходом блока пуска-останова и вхо- ,:,ами начальной установки блока по- ,.;г-13рядного сравнения, блока определе НИН числа циклов контроля и блока управления, выходы с двадцатого по двадцать третий которого подключены соответственно к входу блокировки считывания теста Марш, входу управ Ленин счетом номера цикла обращений, входу конца теста Диагональ и входу счета циклов теста Диагональ блока определения числа циклов обращений, одиннадцатый выход которого соединен с шестым входом разрешения счета блока задания адресов, первый, второй и третий выходы которого подключен1э1 соответственно к входу адреса последней строки, входу адреса последней колонки и входу последнего адреса кадра, блока управления, четвертый, одиннадцатый и двадцать четвертый выходы которого соединены соответственно с входом данных, первым и вторым входами режима контроля питания блока определения адреса ошибки, второй и третий выходы блока задания адресов подключены соответст

зенно к входу адреса последней колонки и входу последнего адреса кадра блока определения числа циклов обращешет первый-и второй входы ре- жи.ма контроля питания блока управления соедине1 ы соответственно с первым, и вторым выходами блока задания динаш-пеского режима питания, второй которого подключен к входу рехсима контроля питания блока определения числа циклов обращений, тречД8961 6

тий и четвертый выходы блока синхронизации соединены соответственно с первым управляющим выходом первого коммутатора и входом стробирования

блока пуска-останова, первый и второй выходы которого подключены соответственно к входу индикации рабочего состояния блока индикации и к входу

0 запуска режима записи фоновой информации блока формирования сигналов записи-чтения, первый вход стробирования которого и второй управляющш вход первого коммутатора соединены

15 соответственно с шестым и пятым выходами блока синхронизации, седьмой и восьмой выходы которого подключены соответственно к третьему управляющему входу первого коммутатора и

20 входу стробирования данных блока задания тестов, девятый и десятый вы- ,ходы блока синхронизации соединены соответственно с вторым входом стробирования блока формирования сигна25 лов записи-чтения и с входом запуска счета адреса блока задания адресов и входом запуска счета длительности ззыдержки блока задания временной выдержки, первый выход которого подклю30 чен к входу управления вьщержкой блока задания динамического режима питания, пятый вход изменения напряжения питания которого подключен к двенадцатому выходу блока управления, один надцатый и двенадцатый выходы блока синхронизации соединены соответствен- ро с управляющим входом регистра чис- ла и с входом стробирования блока поразрядного сравнения выход и вход блокировки которого соединены соответственно с входом наличия ошибки, блока индикации и с вторым выходом блока задания временной выдержки и входами режима временной выдержки блока управления и блока задания динa ичecкoгo режима питания, первый и второй входы установки длительности временной выдержки которого со,единены соответственно с третьим и четвертым выходами блока задания 0 временной выдержки, пятый выход которого соединен с входом запуска генератора тактовых импульсов, первый и второй выходы которого подключены к тактовым входами блока синхрони- зации, первый выход генератора тактовых имщгльсов соединен с тактовым входом регистра числа, информационные входы которого подключены к

40

45

гмходам формирователей считанных сиг- чапов, входы которых являются информационными входами устройства, тре- тий и четвертый выходы блока пуска- останова подключены соответственно к входу блокировки счета адреса блока задания адресов и к входу индикации включения устройства блока индикации, пятый выход блока пуска-останова соединен с входом пуска блока управления, выходы с двадг{нть пятого по двадцать седьмой которого подключены соответственно к второму, третьему, четвертому входам разрешения выдачи сигнала пуска блока пуска-останова, входы блокировки режима записи которого соединены соответственО О000 ОI

00

О i000 OJ

О 1000 о о

01000 о I

о о001 о о

о о001 0. 1

о I010 о о Б

О .

о 1010 о I

о г 011 00

Марш

011 01

о оit 00 00

о о шо о 1

но с вторым и шестым выходами блока задания временной выдержки, первый и второй входы начальной установки

которого подключены соответственно к шестому выходу блока пуска-остана- ва, входам начальной установки блока управления, блока определения числа циклов обращений и блока поразрядного сравнения и к седьмому выходу блока пуска-останова, входу начальной установки блока задания адресов, один из выходов третьей группы и один из выходов шестой группы которого соединены соответственно с пятым и шестым входами признаков рабочего состоянии устройства блока пуска-останова.

Подготовка: запись нулей по всем адресам

Подготовка: запись единиц по всем адресам

Считывание единиц по всем адресам

Запись нулей по всей

адресам

Считывание нулей по всем адресам

Запись единиц по вс адресам

Считывание единиц по всем адресам

Запись кулей гю всем адресам

Считывание нулей по всем адресам

Запись единиц по всем адресам

Считывание единиц по всем адресам.

Запись нулей по в сем адресам

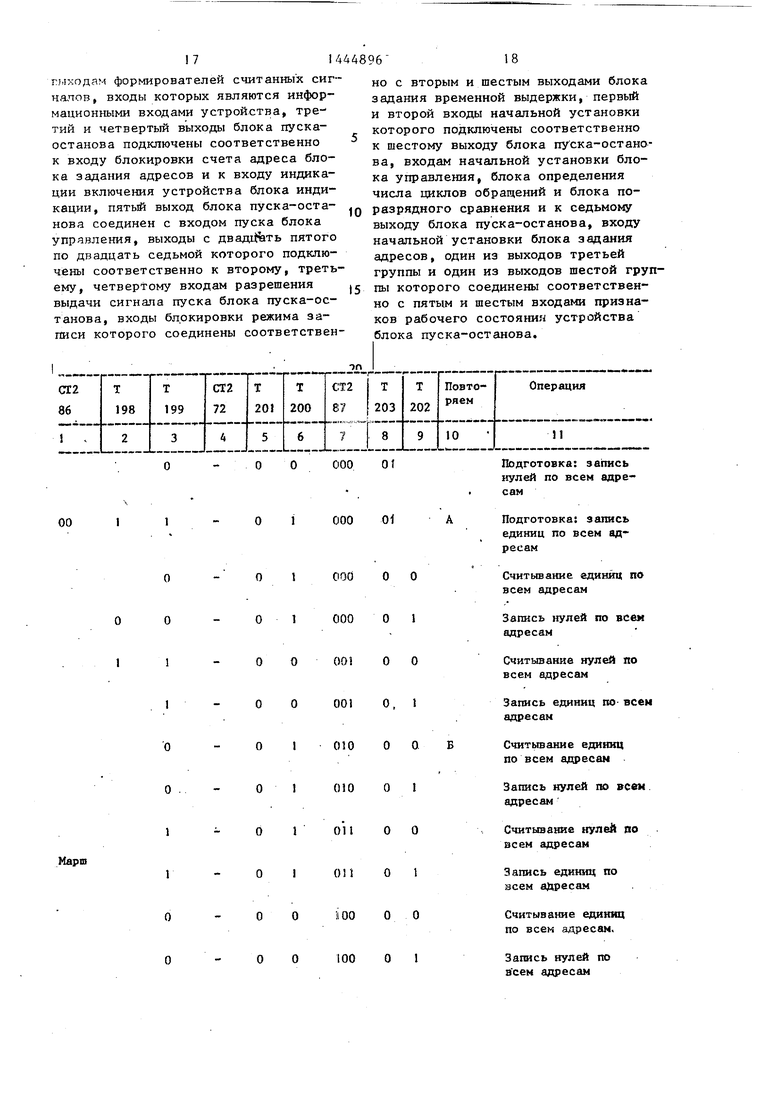

19 44А89620

Продолжение таблицы

2 l/i4A89622

Продолжение таблицы

I I

I I

I r I E -i. J „. 1°IL11

000 0 - ВTo «e

0 1 100 - - ВTo же

127

ОI 101 - - ВTo же

127 О ,: О11ПО - О 6То же

127

ОI lil - вТо же

127

10 1 О - О О 000 О I Подготовка запись

.А кулей по 9сен адресам

- . О 1 000 О 1 Подготовка«запнрь

. едннип по всем адресам

00 1 001 01 Запись фона по

всем адресам

О 1 00 I 00 01 , Запись фоиа

провер. бита

I ОOmTbfflaHHiB текуш

,бита 2i разлогл л-«

. 00 О Считываиие проаер.

бита

I I

к IS

K2S

Фиг. 2 om3j. w %

fm 6I omSjjiamSf

smSajomJf

к го

Фиг.З omBiот Bfi

CD иг л

Ki

OIU fffi

Д77 //

от 12

от 7 11 от 5

-W -52 -S/

45

О,

S2 «

«4

OirtW j im9i,cmVif от8в Фиг. 5

t

м-}

Ш-2.

lS-7

8-2

.

к20

4И

8-5т

.И9-1

иго

1

:)«Л7

ffmlj Ул7д mW отв om7g 03иг. 5

ftSj

ат7,д

omSg

т SB omIOf от gj от 9,1 от So omifffs

am

am W,

amio, dm

от 8

emtOi omWfg omK

шда,з

umJOff j om7j- om7f

amtO:

отЩ

t.Ja

да вт/.

xjsfna

KfWD

2Ж

%

74

gf (gi«w

n. к IZ

Г%.«.

ЙУ«,/З,

«%

.

. f

Фи&,13

Авторы

Даты

1988-12-15—Публикация

1986-07-29—Подача