(54) УСТРОЙСТГВО УПРАВЛЕНИЯ РЕГУЛЯТОРОМ

ПЕРЕМЕННОГО НАПРЯЖЕНИЯ СО ЗВЕНОМ ПОВЫШЕННОЙ ЧАСТОТЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для фазового управления преобразователем | 1976 |

|

SU690602A1 |

| Устройство для фазового управления тиристорным инвертором | 1977 |

|

SU680138A1 |

| Устройство для дуговой сварки с поперечными колебаниями сварочной горелки | 1983 |

|

SU1133059A1 |

| Устройство для управления преобразователем частоты | 1981 |

|

SU966842A1 |

| Устройство для управления инвертором тока | 1979 |

|

SU855929A1 |

| Устройство для регулирования скорости электродвигателя | 1984 |

|

SU1267375A1 |

| Устройство для обработки и передачи информации учета товарной нефти | 1983 |

|

SU1129625A1 |

| Устройство для управления инвертором с @ резонансными нагрузками | 1986 |

|

SU1410242A1 |

| Устройство для стабилизации вакуума | 1983 |

|

SU1149060A1 |

| Формирователь сложного сигнала с частотной и частотно-фазовой манипуляцией | 1982 |

|

SU1136323A1 |

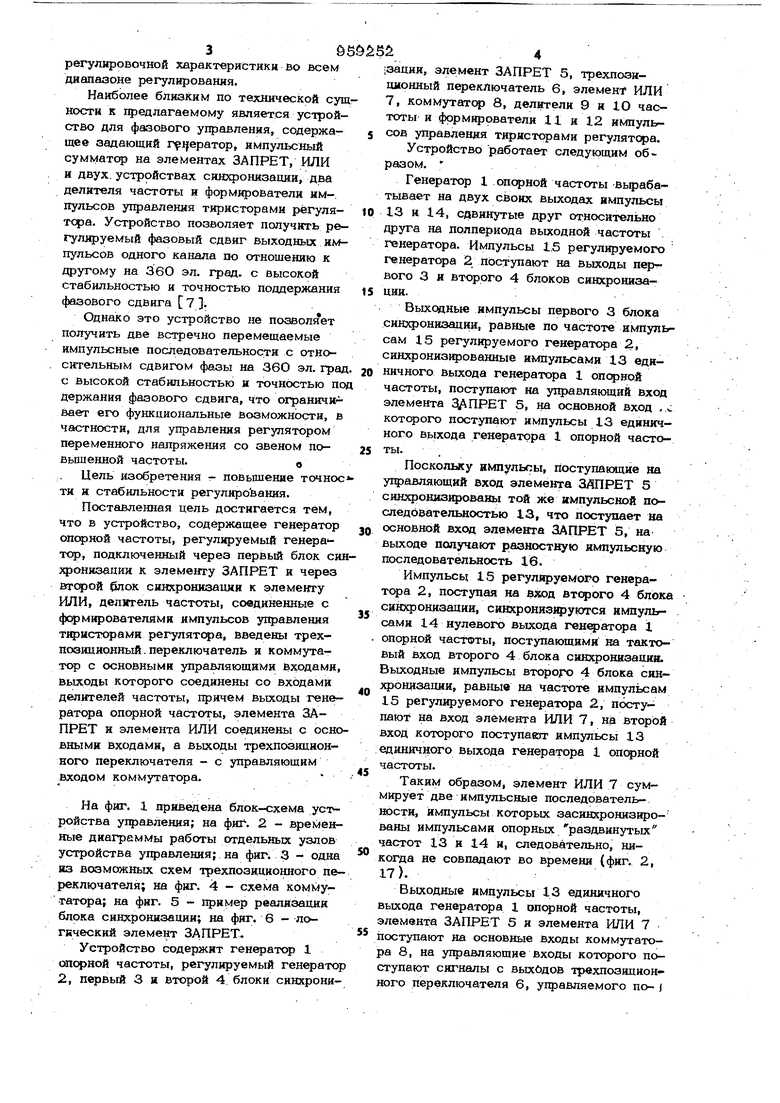

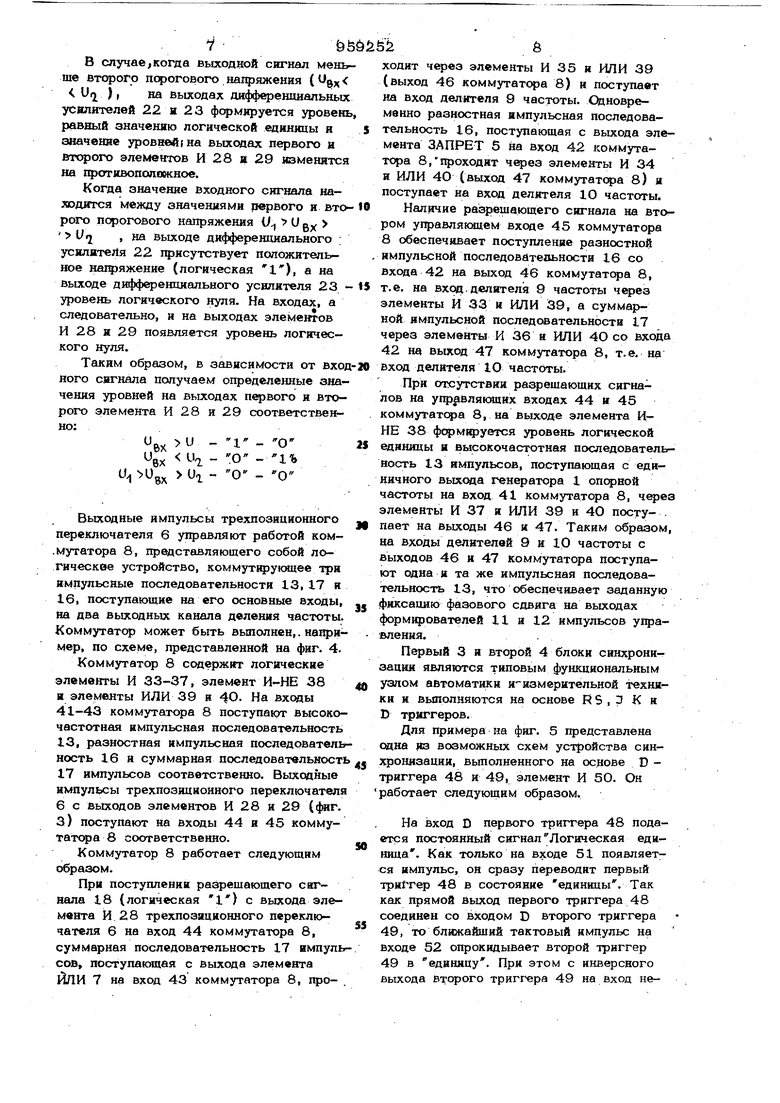

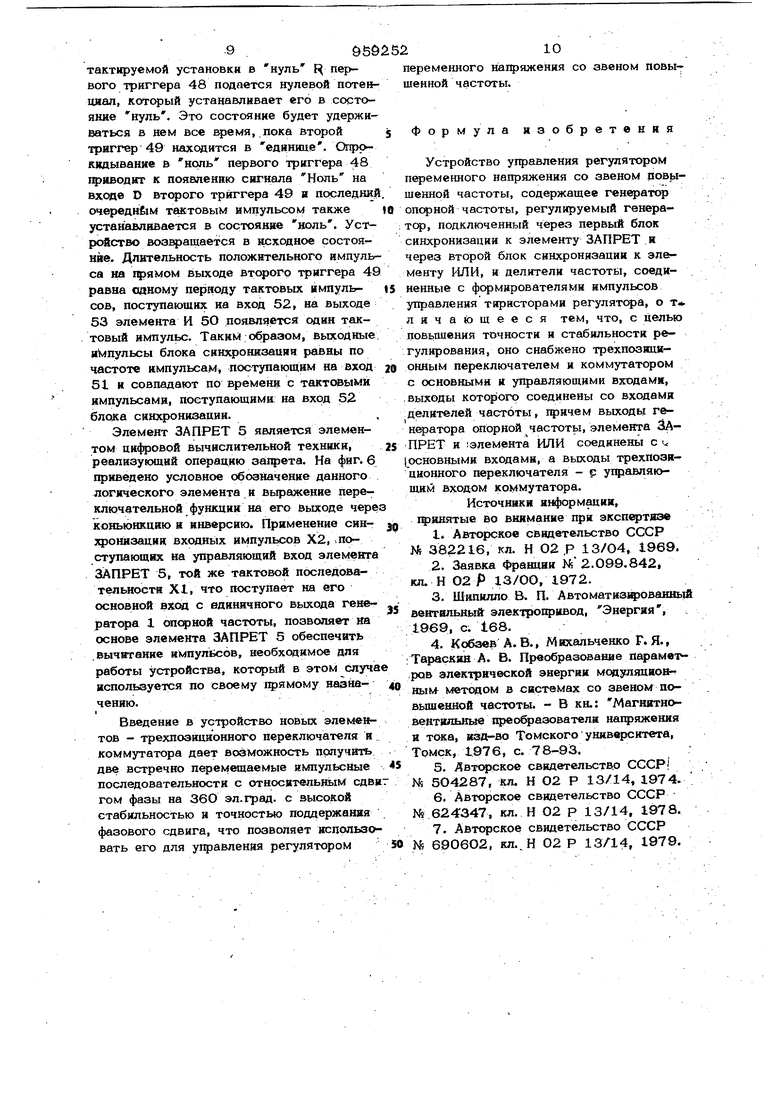

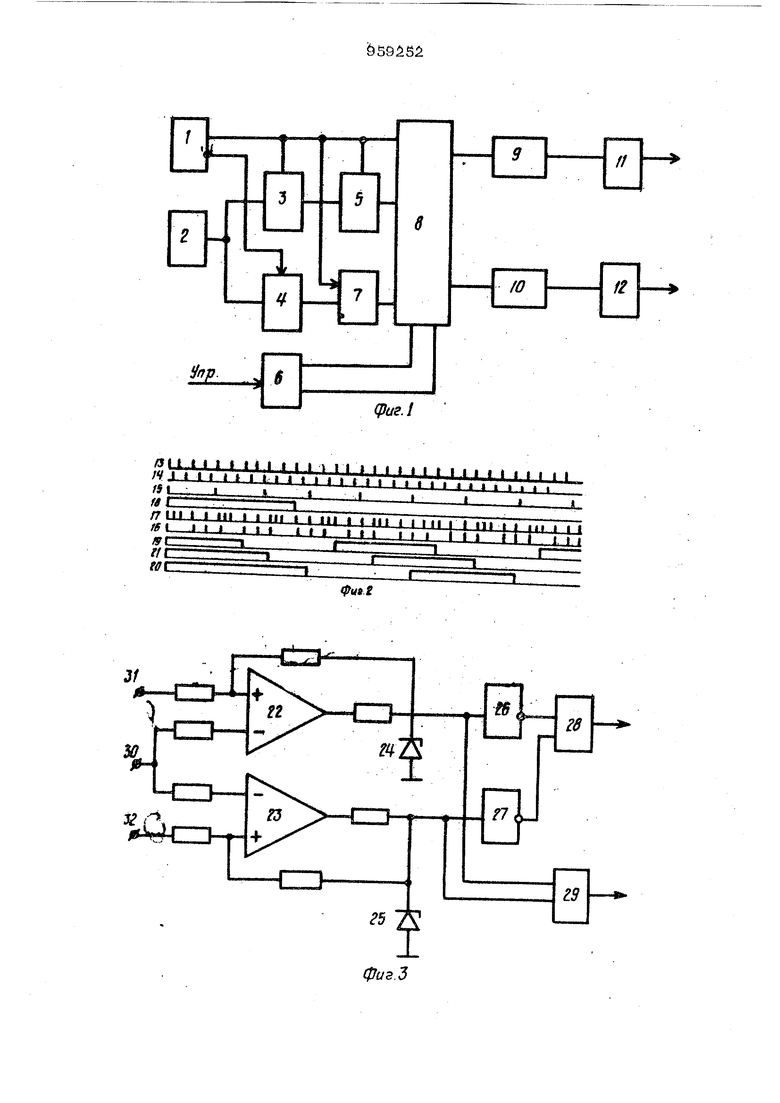

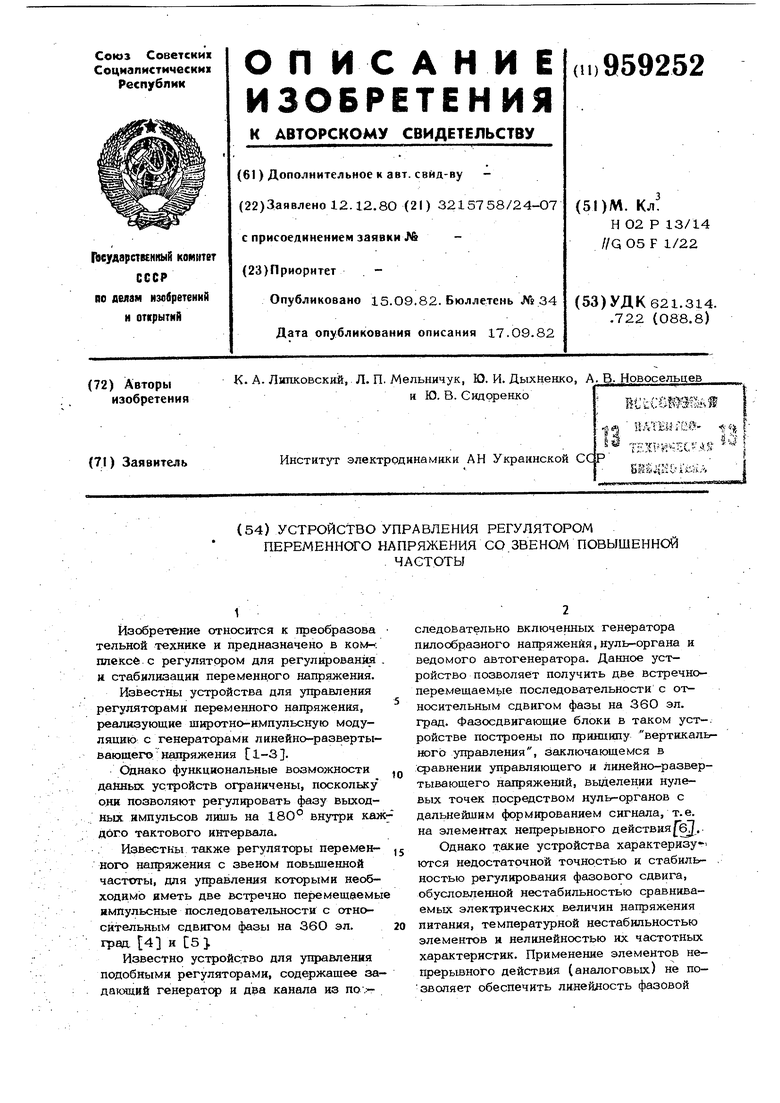

. .1- , , Изобретение относится к преобразова тельной технике и предназначено в ком--, плексб с регулятором для регулщэованйл и стабилизации переменного напряжения. Известны устройства для управления peгyлятqpaми переменного напряжения, реализующие широтно-импульсную модуляцию с генераторами линейно-развертывающего напряжения С1-3 }. Однако функциональные возможности данных устройств ограничены, поскольку они позволяют регулировать фазу выходных импульсов лишь на 180° внутри каж дого тактового интервала. Известны также регуляторы переменного напряжения с звеном повышенной частоты, для управления которыми необходимо иметь две встречно перемещаемы импульсные последовательности с относительным сдвигом фазы на 36О эл. град 4 и 5. Известно устройство для управления подобными регуляторами, содержащее задающий генератсф и два канала из по .:следовательно включенных генератора пилообразного напряжения, нуль-органа и ведомого автогенератора. Данное устройство позволяет получить две встречнопере.мещаемые последовательности с относительным сдвигом фазы на 360 эл. град. Фазосдвигаюшие блоки в таком уст-, ройстве построены по принципу вертикалььюго управления, заключающемся в сравнении управляющего и линейно-развертывающего напряжений, выделении нулевых точек посредством нуль-органов с дальнейшим формированием сигнала, т.е. на элементах непрерывного действия.. Однако тажие устройства характеризуются недостаточной точностью и стабильностью регулирования фазового сдвига, обусловленной нестабильностью сравниваемых электрических величин напряжения питания, температурной нестабильностью элементов и нелинейностью их частотных характеристик. Применение элементов непрерывного действия (аналоговых) не позволяет обеспечить линейлость фазовой регулировочной характеристики во всем диапазоне регулирования. Наиболее близким по технической сущ ности к предлагаемому является устройство для фазового управления, содержащее задающий r ijepaTop, импульсный сумматор на элементах ЗАПРЕТ, ИЛИ и двух.устройствах синхронизации, два делителя частоты и формирователи им-, пульсов управления тиристорами регулятора. Устройство позволяет получить ре- гуляруемый фазовый сдвиг выходных импульсов одногю канала по отношению к щзутому на 36О эл. град, с высокой стабильнсютью и точностью поддержания фазового сдвига 7 . Однако это устройство не позволяет получить две встречно перемещаемые импульсные последовательности с относительным сдвигом фазы на 360 эл, град с Высокой стабильностью и точностью по Держания фазового сдвига, что ограничи вает его функциональные возможности, в частности, для управления регулятором переменного напряжения со звеном повышенной частоты.о Цель изобретения - повышение точное ти и стабильности регулирования. Поставленная цель достигается тем, что в устройство, содержащее генератор частоты, регулируемый генератор, подключенный через первый блок си ;фонизации к элементу ЗАПРЕТ к через втсрой блок синзсроннзашси к элементу ИЛИ, делитель частоты, соединенные с импульсов управления Т1фнсторами регулятора, введены трехпозиционный. переключатель и коммутатор с основными управляющими входами, выходы которого соединены со входами делителей частоты, причем выходы генератора опорной частоты, элемента ЗАПРЕТ и элемента ИЛИ соединены с осно вными входами, а выходы трехпозиционуправляющимного переключателя - с входом коммутатора. На фиг. 1 приведена блок-схема устройства у1Ч5авления; на фиг. 2 - времен ные диаграммы работы отдельных узлов устройства управления; на фиг. 3 - одна КЗ возможных схем трехпозкдионного пе реключателя; на фйг. 4 - схема коммутатора; на фиг. 5 - пример реализации блока синхронизации; на фиг. 6 - логический элемент ЗАПРЕТ. Устройство содержит генератор 1 опорной частоты, регулируемый генерато 2, первый 3 и второй 4 блоки синхрони зации, ЗАПРЕТ 5, трехпозицнонный переключатель 6, элемент ИЛИ 7, коммутатор 8, делители 9 и 1О частоты и формирователи 11 и 12 импульсов управления тиристорами регулятора. Устройство работает следующим образом. Генератор 1 опфной частоты вырабатывает на двух своих выходах импульсы 13 и 14, сдвинутые друг относительно друга на полпериода выходной частоты генератора. Импульсы 15 регулируемого генератора 2 поступают на выходы пер вого 3 и второго 4 блоков синхронизации. Выходные импульсы первого 3 блока сиюфонизаци;и, равные по частоте импульсам 15 регулируемого генератора, синхронизированные импульсами 13 единичного выхода генератора 1 опорной частоты, поступают на управляющий вход элемента 5, на основной вход .с которого поступают импульсы 13 единичного выхода генератора 1 опорной частоты. Поскольку импульсы, поступающие на управляющий вход элемента ЗАПРЕТ 5 сиюфошсзированы той же импульсной по.следовательностью 13, что поступает на основной вход элемента ЗАПРЕТ 5, на выходе получают разностную импульсную последовательность 16. Импульсы 15 регулируемого генератора 2, поступая на вход второго 4 блока синхронизации, синхрониз1фукггся импульсами 14 нулевого выхода генератора 1 опорной частоты, поступающими на тактовый вход второго 4 блока синхронизации. Выходные импульсы второго 4 блока синхронизации, равные на частоте импульсам 15 регулируемого генератора 2, поступают на вход элемента ИЛИ 7, на второй вход которого поступавзт импульсы 13 единичного выхода генератора 1 oпqpнoй частоты. Таким образом, элемент ИЛИ 7 суммирует две импульсные последовательности, импульсы которых засинхронизйрованы импульсами опорных раздвинутых частот 13 и 14 и, следовательно, никогда не совпадают во времени (фиг. 2, 17). Выходные импульсы 13 единичного выхода генератора 1 оперной частоты, элемента ЗАПРЕТ 5 и элемента ИЛИ 7 поступают на основные входы коммутатора 8, на управляющие входы которого поступают сигналы с выходов трехпозиционного переключателя 6, управляемого по- j

средством внешнего сигнала. Выходные имцульсы коммутатора 8 через делители 9 и Ю частоты поступают на входы соответствующих формирователей 11 и 12 импульсов управления тиристорами регулятора.

Коммутатор 8 представляет собой логическое устройство коммутирующее три импульсные последовательности 13, 17 и 16, поступающие на его основные входы, на два выходных канала, в зависимости от управляющих сигналов трехпозиционного переключателя 6.

Наличие разрещающего сигнала 18 (логическая i) на первом выходе трехпозиционного переключателя 6 обеспечивает поступление суммарной последовательности 17 импульсов, с вь1хода элемента ИЛИ 7 на вход делителя 9 частоты и разностной импульсной последовательности 18 с выхода элемента ЗАПРЕТ 5 на вход делителя 10 частоты.

Элементарный сдвиг фазы между выходными сигналами формирователей импульсов управления тиристорами регулятара появляется при добавлении или вычитании импульса с импульсной последовательности 13 и равен irep иод у выходной частоты генератора I опорной частоты.

Поскольку на входы делителей 9 и 10 частоты поступают суммарная 17 и разностная 16 импульсные последовательности соответственно, на выходах делителей частоты а, следовательно, и на выходах формирователей 11 и 12 импульсов управления получают две встречно перемещаемые импульсные последовательности 19 и 2О (для наглядности приведены совместно с импульсной последовательностью 21, соответствующей совпадению фазы на выходах формирователей 11 и 12 импульсов управления).

Наличие разрешающего сигнала на втором утфавляющем входе коммутатора 6 обеспечивает поступление разностной импульсной последовательности 16 на вход делителя 9 частоты и суммарной импульсной последовательности 17 на вход делителя 10 частоты. Это приводит к фазовому сдвигу двух встречно перемещаемых импульсных последовательностей на выходах формщэователей 11 и 12 импульсов управления тиристорами регулятора в противоположную сторону.

При отсутствии разрешающих сигналов на управляющих входах коммутатора 6 на входы делителей 9 и 1О частоты поступает одна и та же импульсная по следовательность 13 единичного выхода генератора 1 опорной частоты, что обеспечивает заданную фиксацию фазового сдвига.

Частотой генератора 1 опфной частоты определяется величина элементарного фазового сдвига. Для повышения точности регулирования фазового сдвига, генератср 1 опорной частоты работает на высокой частоте (порядка 10-10 Гц). Для понижения частоты опорного генератора до промежуточной частоты регулятора, используются делители 9 и 1О частоты.

Изменение частоты 1.5 регулируемого генератора 2 задает скорость изменения фазового сдвига между двумя встречно перемещаемыми импульсными последовательностями.

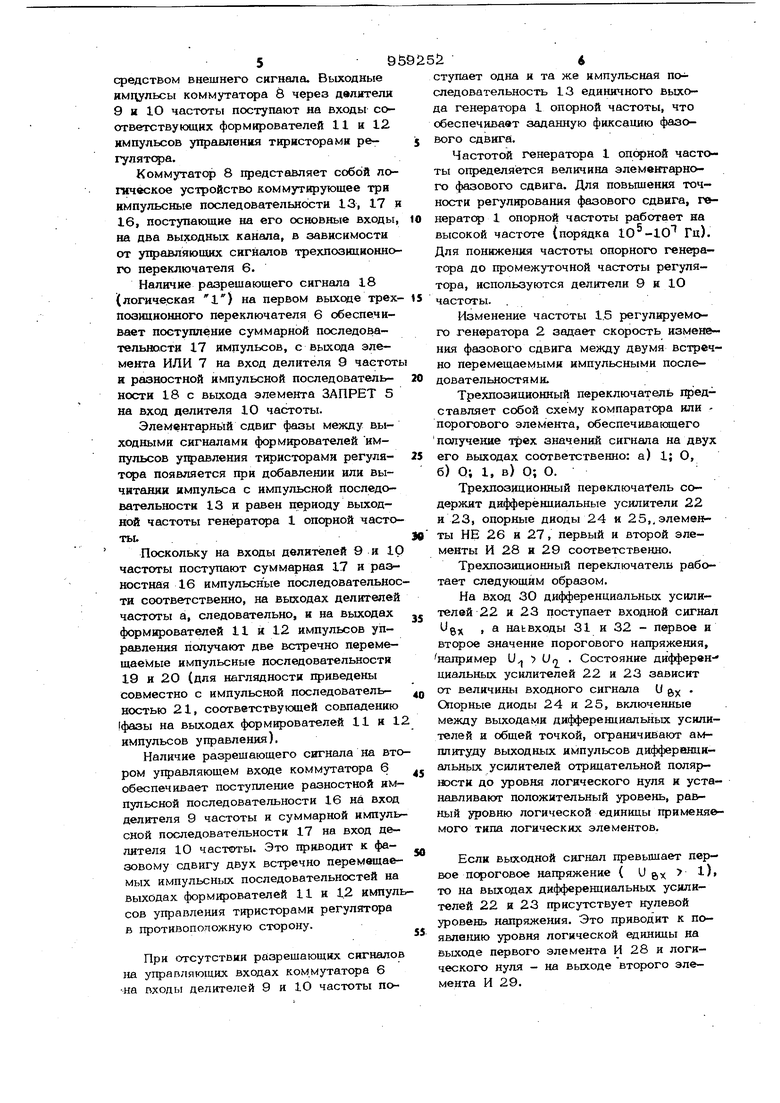

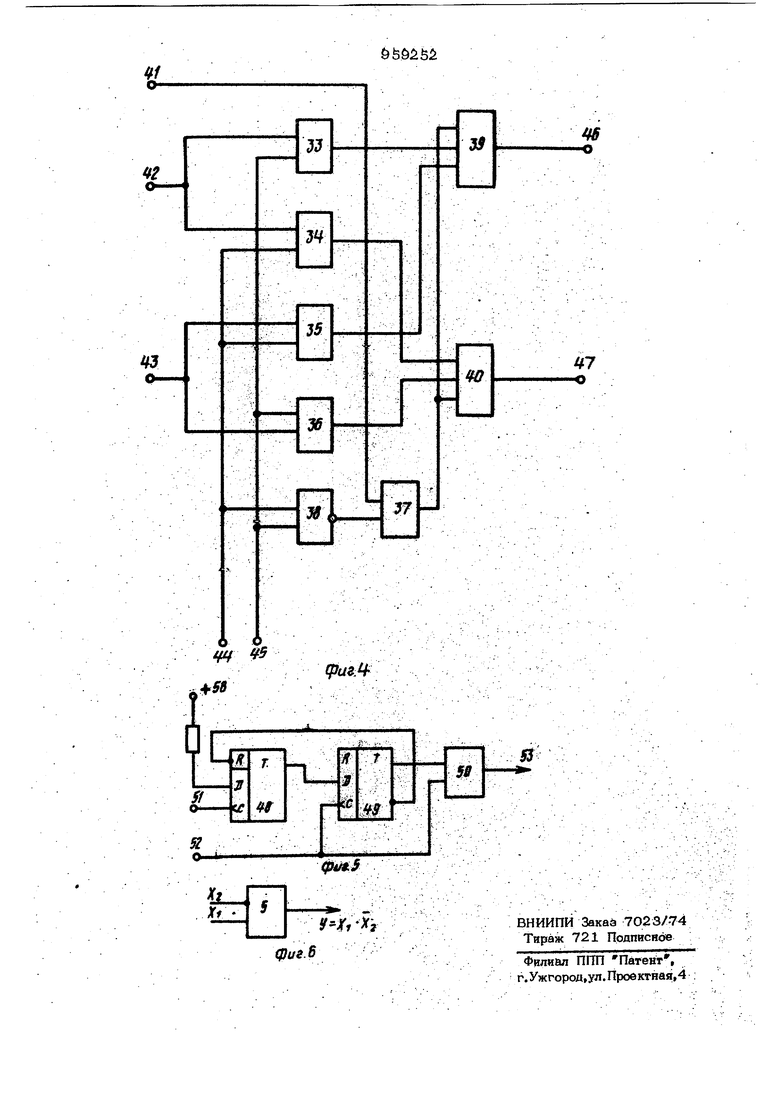

Трехпозиционный переключатель 1федставляет собой схему компаратсра или порогового элемента, обеспечивающего получение трех значений сигнала на двух его выходах соответственно: а) 1; О, б) О; 1, в) О; О.

Трехпозиционный переключатель содержит дифференциальные усилители 22 и 23, опорные диоды 24 и 25,.элементы НЕ 26 и 27, первый и второй элементы И 28 и 29 соответственно.

Трехпозиционный переключатель работает следующим образом.

На вход 30 дифференциальных усилителей 22 и 23 поступает входной сигнал Ug , а наьвходы 31 и 32 - первое и второе значение порогового напряжения, например U U . Состояние дифферен- циальных усилителей 22 и 23 зависит от величины входного сигнала U g,,, . Опорные диоды 24 и 25, включенные между выходами дифференциальных усилителей и общей точкой, ограничивают амплитуду выходных импульсов диффервнциальнь1х усилителей отрицательной полярности до уровня логического нуля и устанавливают положительный уровень, равный уровню логической единицы применяемого типа логических элементов.

Если Выходной сигнал превышает первое пороговое нагфяжение ( U gx то на вьисодах дифференциальных усилителей 22 я 23 присутствует нулевой уровень напряжения. Это приводит к появле1шю уровня логической единицы на выходе первого элемента И 28 и логического нуля - на выходе вторюго элемента И 29. i &ё в случае,когда выходной сигнал меньше второго порогового нагфяжения (Ug U) , на выходах диффврешшальных усилителей 22 и 23 формируется уровень равный значению логической единицы и значение уровней)на выходах первого и второго элементов И 28 и 29 изменится на противопопоисное. Когда значение входного сигнала находится между значениями рврвого и второго порогового напряжения U U п у , на выходе дифференциального : усилителя 22 присутствует положительное напряжение (логическая ), а на выходе дифференциального усилителя 23уровень логического нуля. На входах, а следовательно, и на выходах элеме гов И 28 и 29 появляется уровень логического нуля. Таким образом, в зависимости от вход ного сигнала получаем определенные значения уровней на выходах первого и второго элемента И 28 и 29 соответственно: - О Ug U - О 1Л ВХ 1 - О- - О Выходные импульсы трехпозиционного переключателя 6 управляют работой ком.мутатора 8, представляющего собой логические устройство, коммупфуюшее три импульсные последовательности 13, 17 и 16, поступающие на его основные входы, на два вьшодных канала деления частоты. Коммутатор может быть вьшолнен,. например, по схеме, представленной на фиг. 4. Коммутатчр 8 содержит логические элементы И 33-37, элемент И-НБ 38 и элементы ИЛИ 39 и 4О. На входы 41-43 коммутатора 8 поступают высокочастотная импульсная последовательность 13, разностная импульсная последовательность 16 и суммарная последовательность 17 импульсов соответственно. Выходные импульсы трехпозиционного переключателя 6 с выходов элементов И 28 и 29 (фиг. З) поступают на входы 44 и 45 коммутатора 8 соответственно. Коммутатор 8 работает следующим образом. При поступлении разрещающего сигнала 18 (логическая ) с выхода элемента И 28 трехпозяционного переключателя 6 на вход 44 коммутатора 8, суммарная последовательность 17 импуль сов поступающая с выхода элемента ИЛИ 7 на вход 43 коммутатора 8, про- . 26 ходит через элементы И 35 я ИЛИ 39 (выход 46 коммутатс а 8) и поступает на вход делителя 9 частоты. (Ипновременно разностная импульсная последовательность 16, поступающая с выхода элемента ЗАПРЕТ 5 на вход 42 коммутатора 8,1фоходит через элементы И 34 и ИЛИ 40 (выход 47 коммутатора 8) и поступает на вход делителя 1О частоты. Наличие ра;зрешаюшего сигнала на втаром управляющем входе 45 коммутатора 8 обеспечивает поступление разностной импульсной последовательности 16 со входа 42 на выход 46 коммутатс а 8, т.е. на вход.делителя 9 частоты через элементы И 33 и ИЛИ 39, а суммарной импульсной последовательности 17 через элементы И 36 и ИЛИ 40 со входа 42 на выход 47 коммутатора 8, т.е. на вход делителя 10 частоты, При отсутствии разрешающих сигналов на упр|1Вляющих входах 44 и 45 коммутатора 8, на вьрьоде элемента ИНЕ 38 формируется уровень логической единицы и высокочастотная последовательность 13 импульсов, поступающая с единичного выхода генератора 1 оперной частоты на вход 41 коммутатора 8, через элементы И 37 и ИЛИ 39 и 40 посту- . пает на выходы 46 и 47. Таким образом, на входы делителей 9 и 10 частоты с выходов 46 и 47 коммутатора поступают одна и та же импульсная последовательность 13, что обеспечивает заданную фиксацию фазового сдвига на выходах формирователей 11 и 12 импульсов управления.. Первый 3 и второй 4 блоки синхронизааии являются типовым функциональным УЗЛОМ автоматики и-измерительной техники и выполняются на основе RS , К и D триггеров. Для примера на фиг. 5 представлена сщна из возможных схем устройства синхронизации, вьтолненного на основе D триггера 48 и 49. элемент И 50. Он работает следующим образом. На вход D первого триггера 48 подается постоянный сигнал Логическая единица. Как только на входе 51 появляется импульс, он сразу переводит первый триггер 48 в состояние единицы. Так как прямой Выход первого триггера 48 соединен со входом D второго триггера 49, то ближайший тактовый импульс на входе 52 опрокидывает второй триггер 49 в единицу . При этом с инверсного выхода второго триггера 49 на вход не9959215тактируемой установки в нуль f первого триггера 48 подается нулевой потенциал, который устанавливает его в состояние нуль. Это состояние будет удерживаться в нем все время, пока второй 5 триггер 49 находится в единице. Опр кидывание в ноль первого триггера 48 Щ)явоаит к появлению сигнала Ноль на входе D второго триггера 49 и последний. очередном тактовым импульсом также «а устанавливается в состояние ноль. Уст-л ройство воз ащается в исходное состоя нйе. Длительность положительного импульса на Ц)ямом выходе триггера 49 равна одному периоду тактовых импуль- |5 сов, поступающих на вход 52, на выходе 53 элемента И 5О появляется один тактовый импульс. Таким образом, выходные иКшульсы блока синхронизации равны по частоте импульсам поступающим на вход 29 51 и совпадают по времени с тактсжыми импульсами, поступающими- на вход 52 блока синхронизации. Элемент ЗАПРЕТ 5 является элементом цифровой вычислительной техники, реализующий операцию за прета. На фиг. 6 приведено условное обозначение данного логического элемента и выражение переключательной фушсции на его выходе чере кояыонкцию и инверсию. Применение син. хронизации входнь1х импульсов Х2, .поступающих на управляющий вход элемента ЗАПРЕТ 5, той же тактовой последовательности Xt, что поступает на его основной вход с единичного выхода генератс а 1 опс)ной частоты, позволяет на основе элемента ЗАПРЕТ 5 обеспечить .вычитание импульсов, необходимое для работы устройства, котсрый в этом случа используется по своему прямому назиачению. I. Введение в устройство новых элементов - трехпоэиционного переключателя и коммутатора дает возможность получить две встречно перемещаемые импульсные последовательности с относительньхм сдви гом фазы на 36О эл.град. с высокой стабильностью и точностью поддержания фазового сдвига, что позволяет использо вать его для управления регулятором50 10 переменного напряжения со звеном повы шенной частоты, формула изобретвняя Устройство управления регулятором переменного напряжения со звеном ровышенной частотьг, содержащее генератор оперной частоты, регулируемый генераор, подключенный через первый блок синхронизации к элементу ЗАПРЕТ и через второй блок синхронизации к элементу ИЛИ, и делители частоты, соединенные с формирователями импульсов управления тиристорами регулятсра, о т личающееся тем, что, с целью цовьпиения точности и стабильности регулирования, оно снабжено трехпозицнонным переключателем и коммутатором с основными и управляющими вхтщами, .выходы которого соединены со входами делителей частоты, гфичем выходы ген ратора опорной частоты, элемента ЗАПРЕТ и iэлемента ИЛИ соединены с основнь1ми входами, а выходы трехпозицнонного переключателя - р угфавляющим входом коммутатора. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР л«. , . № 382216, кл. И 02 .Р 13/04, 1969. 2.Заявка Фрашаи М2.099.842, кл. Н 02 Р 13/ОО, 1972. 3.Шипилло В, П. Автоматизированньй авнтнлЬ|Ный электрогфивод, Энергия, 1969, с. 168, 4.Кобаев А.В., Михальченко Г.Я., Тараскин А. В. Преобразование параметров электрической энергии модулящион ным методом в системах со звеном повьшенной частоты. - В кн.: Магнитновентильные преофазователи на1ц яжеш1я в тока, кзд-во Томского университета, Томск, 1976, с. 78-93, 5.Автсфское свидетельство СССР; 3 5О4287, кл. Н О2 Р 13/14, 1974. 6.Авторское свидетельство СССР № 624347, кл. И 02 Р 13/14, 1978. 7.Авторское свидетельство СССР Jsfe 6906О2, кл.Н 02 Р 13/14, 1979.

М f LlJi 1 f ГЧ t У

/у J I А I t J t j I t I I I t I I j i I A I ij t

/# 1 : .,I If .. .. i

/yi ; ,1

/7 ill t I M MP t IJM I t t 1 1 Ml I t l|l 1 i 111 i |1

ff I I I I i If ft i t i I t i j.M

/УС f/C Й7С

фиг.З

f

vffi

yt T

SS

Si

Авторы

Даты

1982-09-15—Публикация

1980-12-12—Подача