. 1 . Изобретение относится к радиотехнике и может использоваться для пере дачи дискретной информации по каналам с изменяющимися во времени характеристиками. . . Известно адаптивное устройство радиосвязи, содержащее в передающей части последовательно соединенные мультиплексор и кодер и последовател но соединенные модулятор и передат чик, а также блок управления скоростью передачи, в приемной части последовательно соединенные приемник демодулятор и последовательно соёдиненные декодер и демультиплексор, а также блок управления скоростью приема , причем выход демодулятора через последовательно соединенные блок контроля и блок адаптации падключён к входу мультиплексора, а еторой выход декодера подключён к второму вхо ду блока контроля, при этом соответствующие выходы демультиплексора непосредственно подключены к $ходу блока управления скоростью приема и через блок управления скоростью передачи к второму входу мультиплексора 113Однако известное устройство обла;дает недостаточной скоростью переда ЧИ. - , Цель изобретения - повышение скорости передачи. Цель достигается тем, что в адап- . тивное устройство радиосвязи, содержащее а передающей части пocлeдoвa тельно соединенные мультиплексор и кодер и последовательно соединен мые модулятор и передатчик, а такжй блок управления скоростью передачи, в приемной части последовательно соединенные приемник и демодулятор и последовательно соединенные декодер и дёмодумультиплексор, а также блок управления скоростью приема, причем выход демодулятора через последовательно .соединенные б/ток контроля и блок адаптации подключен к входу 3 95 мультиплексора, а второй выход деко7 дера подключен к второму входу блока контроля, при этом соответствующие выходы Демультиплексора непосредственно подключены к входу блока управления скоростью приема и через блок управления скоростью передачи второму входу мультиплексора, введены в передающей части последовательно соединенные буферный накопитель, элемент ИЛИ и блок элементгов И выходы которого подключены к входам модуляторов, а также два распределителя и блок управления отключением каналов по передаче, вход которого соединен с входом блока управления скоростью передачи «а выход подключен к входу Первого распределителя,второй вход которого сбединен соответственно с вторым выходом блока управле- ния скоростью передачи и входом второго распределитеяя, другие выходы которого подклймены к входам бУФерного накопителя, другие входы которого соединены с выходами кодера, при этом

выходы первого распределителя подключены к ДРУГИМ йхояам блока элеентов И, в приемнсй части введены последо вательт соединенные блок элементов И, элемент ИЛИ и буферный накопитель , выходы которого угодлючены к входам декодера, а также ва распределителя и блок отключения каналов по приему, вход которого соединен с выходом демультиплексора, а выход подключен k входу первого распределителя, второй вход которого соединен соответственно с выходом блока управления скоростью приема и входом второго распределителя,выходы которого подключены к другим входам буферного накопителя, а выходы первого распределигеля подключены к другим входам блока элементов И. Буферный накопитель состоит из накопительнь1х узлов по числу каналов и управляющего узла, причем каждый накопительный узел выполнен в виде регистра сдвига, разрядные выходы которого через соответствующие элементы И подключены к входам элемента ИЛИ, а управляющий узел выполнен в виде регистра сдвига, разрядные выходы которого через элемент И подключены к входам регистра сдвига накапливающего узла, при Этом элементы И управляющего узла соединены последовательно, а другие входы регистра сдвига управляющего узла подключенйем каналов по приему.

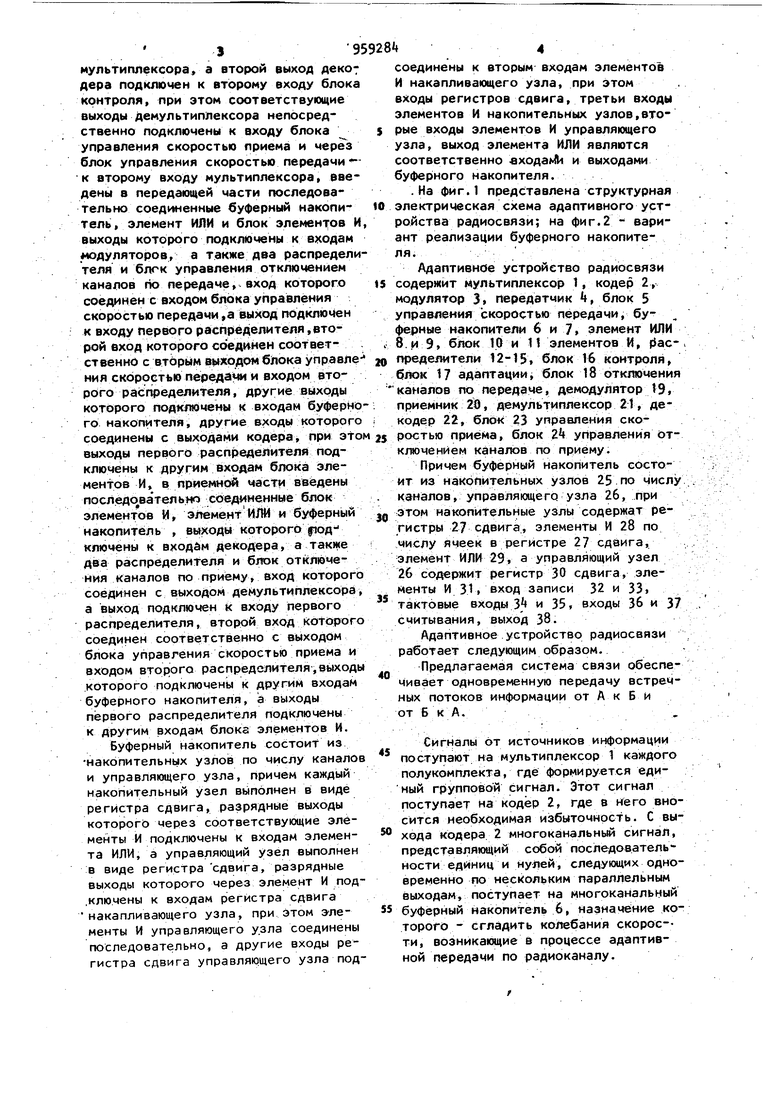

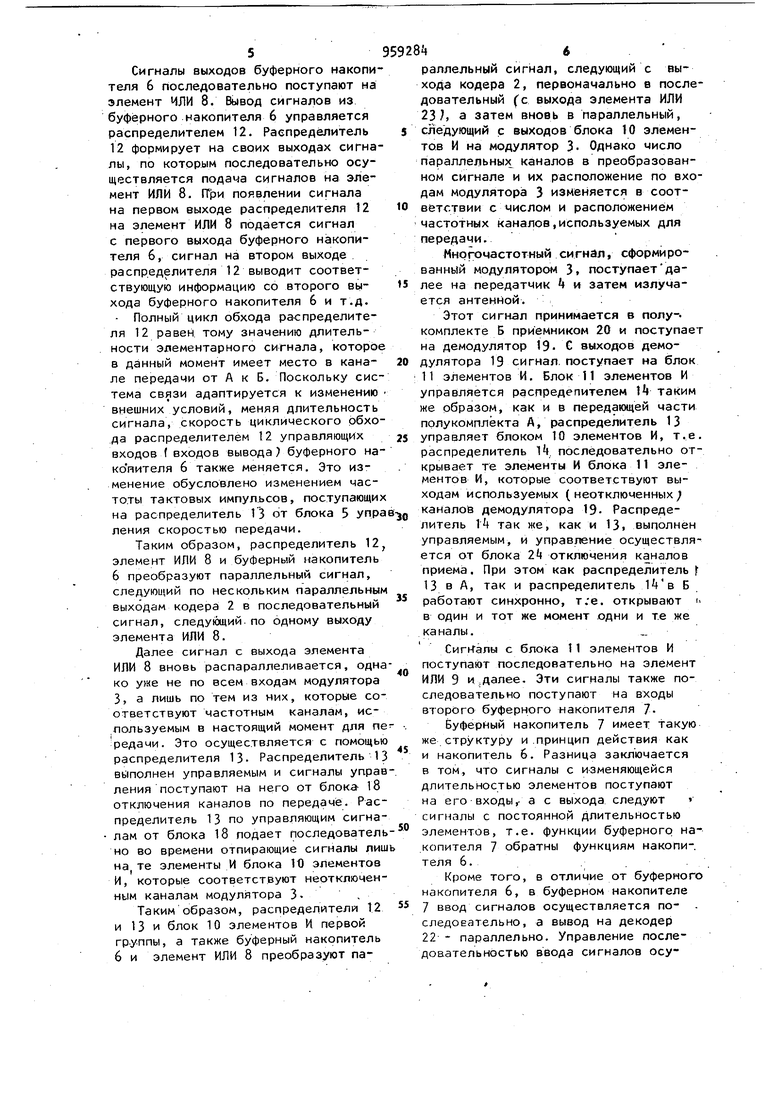

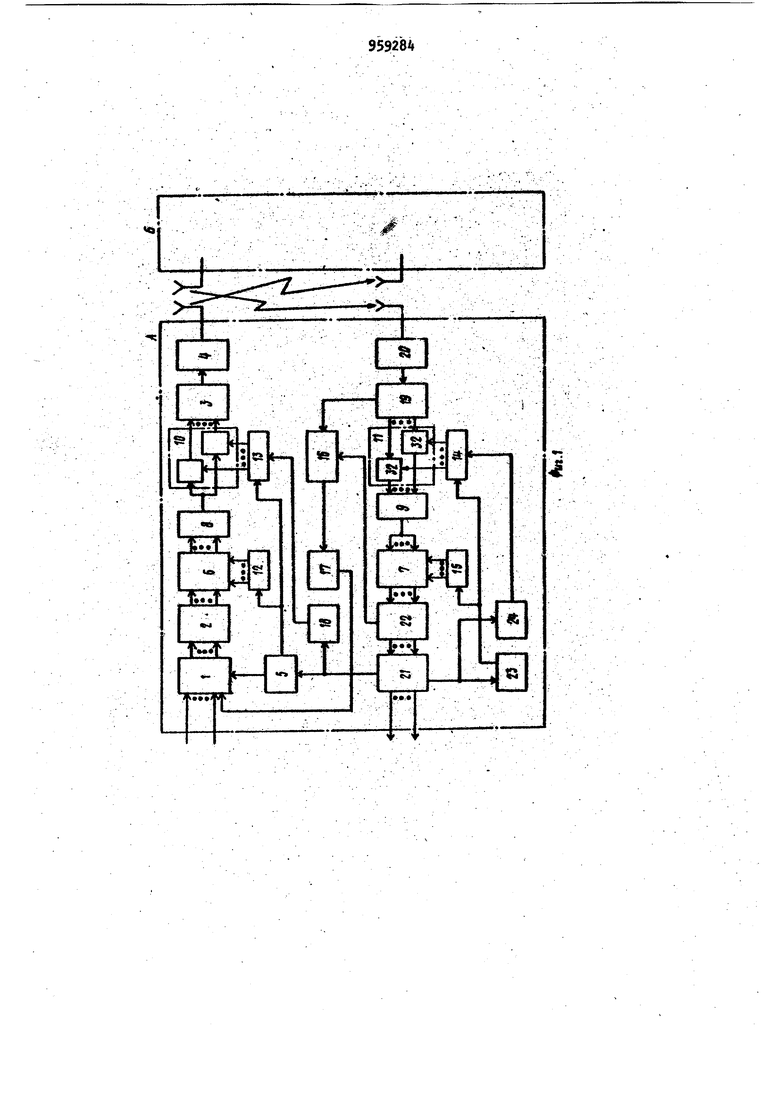

Причем буферный накопитель состоит из накопительных узлов 25 по числу каналов, управляющего узла 26, При этом накопительные узлы содержат регистры 27 сдвига, элементы И 28 по числу ячеек в регистре 27 сдвига, элемент ИЛИ 29, а управляющий узел 26 содержит регистр 30 сдвига, элементы И 31, вход записи 32 и 33. тактовые входы З и 35, входы 36 и 37 считывания, выход 38.

Адаптивное устройство радиосвязи работает следующим образом.

Предлагаемая система связи обеспечивает одновременную передачу встречных потоков информации от А к Б и от Б к А.

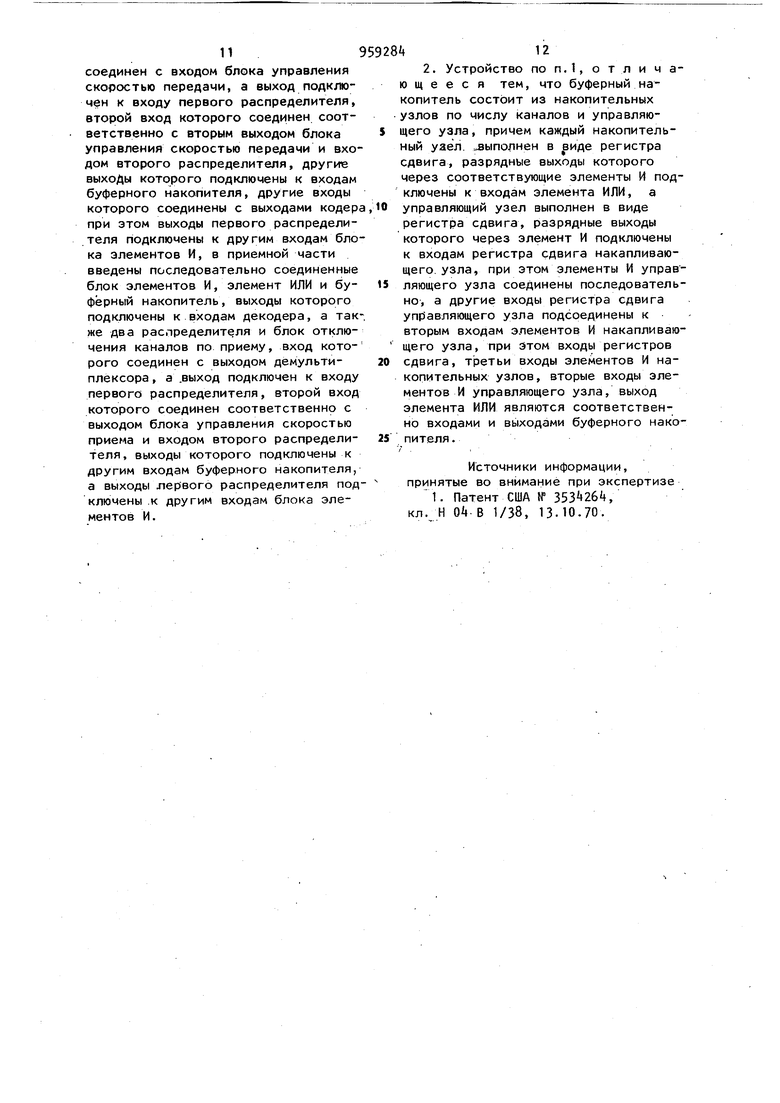

Сигналы от источников информации поступают на мультиплексор 1 каждого полукомплекта, где формируется единый групповой сигнал. Этот сигнал поступает на кодер 2, где в него вносится необходимая и;збыточнрсТь. С выхода кодера 2 многоканальный сигнал, представляющий собой последовательности единиц и Нулей, следующих одновременно по нескольким параллельным выходам, поступает на многоканальный буферный накопитель 6, назначение которого - сгладить колебания скорое-ти, возникающие в процессе адаптивной передачи по радиоканалу. соединены к вторым входам элементов И накапливающего узла, при этом входы регистров сдвига, третьи входы элементов И накопительных узлов,вторые входы элементов И управляющего узла, выход элемента ИЛИ являются соответственно аходак й и выходами буфер ногр накопителя. . На фиг.1 представлена структурная электрическая схема адаптивного устройства радиосвязи; на фиг.2 - вариант реализации буферного накопителя. . -,-.. , . Адаптивное устройство радиосвязи содержит мультиплексор 1, кодер 2, модулятор 3. передатчик k, блок 5 управления скоростью передачи, буферные накопители 6 и 7, элемент ИЛИ 8 и 9, блок 10 и П элементов И, jiacлредепители 12-15, блок 16 контроля, блок 17 адаптацииi блок 18 отключения каналов по передаче, демодулятор 19. приемник 20, демультиплексор 21, декодер 22, блок 23 управления скоростью приема, блок 2k уИравления от5Сигналы выходов буферного накопителя 6 последовательно поступают на элемент ИЛИ 8. Вывод сигналов из буферного накопителя 6 управляется распределителем 12. Распределитель 12 формирует на своих выходах сигналы, по которым последовательно осуществляется подача сигналов на элемент ИЛИ 8, (Три появлении сигнала на первом выходе распределителя 12 на элемент ИЛИ 8 подается сигнал с первого выхода буферного накопителя 6, сигнал на втором выходе распределителя 12 выводит соответствующую информацию со второго выхода буферного накопителя 6 и т.д. Полный цикл обхода распределителя 12 равен тому значению длительности элементарного сигнала, которое в данный момент имеет место в канале передачи от А к Б. Поскольку система связи адаптируется к изменению внешних условий, меняя длительность сигнала, скорость циклического обхода распределителем 12 управляющих входов ( входов вывода) буферного накопителя 6 также меняется. Это изменение обусловлено изменением частоты тактовых импульсов, поступающих на распределитель Г5 от блока 5 ynpa ления скоростью передачи. Таким образом, распределитель 12, элемент ИЛИ 8 и буферный накопитель 6 преобразуют параллельный сигнал, следующий по нескольким параллельным выходам кодера 2 в последовательный сигнал, следующий.по одному выходу элемента ИЛИ 8. Далее сигнал с выхода элемента ИЛИ 8 вновь распараллеливается, одна ко уже не по всем входам модулятора 3, а лишь по тем из них, которые соответствуют частотным каналам, используемым в настоящий момент для пе редачи. Это осуществляется с помощью распределителя 13. Распределитель 13 выполнен управляемым и сигналы управ ления поступают на него от блока- 18 отключения каналов по передаче. Распределитель 13 по управляющим сигналам от блока 18 подает последователь но во времени отпирающие сигналы лиш на, те элементы И блока 10 элементов И, которые соответствуют неотключенным каналам модулятора 3 Таким образом, распределители 12 и 13 и блок 10 элементов И первой гр-уппы, а также буферный накопитель 6 и элемент ИЛИ 8 преобразуют параллельный сигнал, следующий с выхода кодера 2, первоначально в последовательный (с выхода элемента ИЛИ 231, а затем вновь в параллельный, следующий с выходов блока 10 элементов И на модулятор 3- Однако число параллельных каналов в преобразованном сигнале и их расположение по входам модулятора 3 изменяется в соответствии с числом и расположением частотных каналов,используемых для передачи. Мнргчэчастотный сигнал, сформированный модулятором 3, поступаетдалее на передатчик и затем излучается антенной. ; Этот сигнал принимается в полу-. комплекте Б приемником 20 и поступает на демодулятор 19. G выходов демодулятора 19 сигнал, поступает на блок 11 элементов И. Блок 11 элементов И управляется распредепителем таким же образом, как и в передающей части полукомплёкта А, распределитель 13 управляет блоком 10 элементов И, т.е. распределитель ТЧ последовательно открывает те элементы И блока 11 элементов И, которые соответствуют выходам используемых ( неотключенных; каналов демодулятора 19- Распределитель 1 так же, как и 13, И 13, выполнен управляемым, и управление осуществляется от блока 2 отключения каналов приема. При этом как распределитель f 13 в А, так и распределитель 4в Б работают синхронно, т.е. открывают в один и тот же момент одни и те же каналы. СигиГалы с блока 11 элементов И поступают последовательно на элемент ИЛИ 9 И;Далее. Эти сигналы также последовательно поступают на входы второго буферного накопителя 7. Буферный накопитель 7 имеет taкyю же структуру и .принцип действия как и накопитель 6. Разница заключается в том, что сигналы с и-зменяющейся длительностью элементов поступают на его входы,- а с выхода следуют сигналы с постоянной Длительностью элементов, т.е. функции буферного накопителя 7 обратны функциям накопи-, теля 6... Кроме того, в отличие от буферного накопителя 6, в буферном накопителе 7 ввод сигналов осуществляется последоеательно, а вывод на декодер 22 - параллельно. Управление последовательностью ввода сигналов осуществляется от распределителя 15 также, как распределитель 13 управляет последовательностью вывода из буферного накопителя 6 Таким образом, буферный накопите 7 сглаживает колебания технической скорости, возникающие в процессе адаптации системы, и не дает им проявиться на выходе системы. Кроме того, блок 11 элементов И, управляемый распределителем И, элемент ИЛ 9 и буферный накопитель 7, управляе мый распределителем 15, выполняют последовательность операций, обратную той, которую выполняют блоки 6,3 и 10 в передающей части полукомплекта А, т.е. преобразуют параллельный демодулированный сигнал на выходах демодулятора 19 с изменяющимся расположением и числом каналов в параллельный сигнал, имею щий постоянное число каналов, посту пающий одновременно на все входы декодера 22. Параллельный синхронный сигнал с выхода буферного накопителя 7 поступает на декодер 22, где производится декодирование, flartee декодированный сигнал поступает на демуль типлексор 21, в котором осуществляется разделение декодированнсА-о гру пового сигнала по выходам, соответствующим каждому источнику. Одновременно сигналы с демодулятора 19 и с декодера 22 поступают н бло1$ 16 контроля качества принимаемой информации, который по степени искажения принимаемых сигналов от . демсэдулятора и числу обнаруженных ошибок от декодера 22 орределя ет качество каждого из частотных каналов, используемых модулятором 3 полукомплекта А эдля передачи и демодулятором 19 полуком плекта Б на. приеме. Результаты оцен качества каналов от блока 16 контро поступают на блок 17 адаптации, кот рый принимает решение о том, какие из используемых каналов непригодны для передачи информации с требуемым качеством, и, следовательно, должны быть отключены, и kaждaя длительнос элемента должна быть установлена в остальных каналах. Сформированный сигнал о принятом решении от блока 17 адаптации полукомплекта Б поступает на мультиплексор 1 этого полукомплекта и обычным путем через тра передачи от Б к А проходит до демул 8 типлексора 21 полукомплекта А. Здесь информация о том, какова должна быть длительность элементарного сигнала ( техническая скорость опознается воспринимается блоком 5 управления скоростью передачи, а информация о том, какие каналы должны быть отключены, воспринимается блоком 18 управления, отключением каналов по передаче . Блок 5 устанавливает частоту тактовых импульсов, определяющих величину технической скорости (длительности сигнала) такой, которая соответствует принятому сообщению. Эти импульсы поступают на тактовые входы распределителя 12 и 13. где определяют скорость развертки, осуществляемой этими распределителями. Блок 18 управления сигналами, подаваемыми на распределитель 13, определяет, по каким именно входам модулятора 3 должны поступать сигналы. При этом частота импульсов,, поступающих на распределители 12 и 13, должна быть больше технической скорости. Одновременно сигнал о том, что передающая часть полукомплекта А перешла на новую скорость передачи, от блока 5 управления скоростью передачи подается на мультиплексор 1, проходит через весь тракт передачи вплоть до демультиплексора 21 полукомплекта Б. На выходе демультиплексора 21 эта информация опознается и воспринимается блоками 23 управления скоростью приема и блоком 2k отключения каналов по приему. Первый из них, подобно блоку 5 в передающей части, определяет скорость развертки , осуществляемой pacпpeдeлиteлями и 15. Блок сигналами, подава.емыми на {распределитель Т определяет с каких выходов демодулятора 19 отвечающих . неотключенным каналам) осуществляется съем информации. Таким образом, система переходит на новую скорость и осуществляет переДаЧу на этой скорости вплоть до момента, когда блок 16 контроля укажет на необходимость изменения скорости, отключения каналов либб включения их. . При этом буферный накопитель работает следующим образом. От кодера 2 на вход записи 32 накопительных узлов 25 каждого из каналов поступает очередной символ (нуль или единица), а в левую ячейку регистра 31 всегда записывается нуль, что симво лически изображено заземлением вх дов записи регистра. Затем на такто вые входы 3 регистров 27 сдвига на тактовый вход 35 регистра 30 сдвига поступает тактовый импульь. Этот им пульс продвигает зна(с, записанный в левую ячейк; регистров 27 и 30 на одну ячейку вправо, тактовые импуль сы на входы З и 35 поступают от.де кодера 22, причем частота поступлени тактовых импульсов равна средней ско рости передачи по каждому каналу. На входы считывания 36 и 37 накопительных узлов и управляющего узла 2б последовательно во времени поступают сигналы от распределителя 12. Регистр 30 выполнен таким образом, что в правой ячейке всегда записана единица. Предположим, что во всех ячейках регистров 27, кроме последней, записаны двоичные знаки, поступающие из декодера 2. В крайней правой ячейке регистров 27 записан нуль. Во всех ячейках регистра 30, кроме двух последних, также записаны нули, В двух правых ячейках этого регистра записаны единицы. Сигнал с первой позиции распределителя 12 поступает на вход считывания Зб накопительного элемента 25. Этот сигнал с входа Зб поступает на входы элементов 28. Элементы И 28, связаннь1е с выходами двух правых ячеек регистра 27, открыты единичными сигналами с выходов двух правых ячеек управляющего регистра 30. остальные элементы И 28 в на-.. копительном узле 25 закрыты нулевыми сигналами, поступающими на них с выходов соответствующих ячеек регистра 30. Поэтому сигнал с входа Зб через элементы И 28 осуществляет вывод знаков, записанных только в двух правых ячейках регистра 27. Поскольку, как условлено,в крайней правой ячейке регистра 27 записан нуль, на выходе 38 элемента ИЛИ 29 появляется знак ( нуль или единица), записанный во второй справа ячейке, регистра 27. Далее единичный сигнал переходит на следующую позицию распределит.еля 12 и появивишись на входе 3& второго сверху накопительного узла 25., выводит таким же образом на выход 38 зна из второй справа его Ячейки. Анало410гичным образом осуществляется вывод из едедующей ячейки и т.д. Таким образом, в передающем накопителе 6 одновременно идут два; процесса - процесс записи информации из кодера 2, идущий постоянным темinoM и распространяющийся слева направо и процесс вывода информации, идущий с переменной скоростью и расг. пространяющийся в противоположную сторону. Если скорость вывода превышает скорость записи, количестйо пустых ячеек в правой части регистров 27 возрастает. Если скорость вывода ниже скорости Записи, то регистры 27 постепенно заполняются. .Предложенное устройство обладает более высокой средней скоростью передачи информации, приходящейся на один канал, что позволит уменьшить вероятность отключения каналов до величины, определяемой емкостью буферных накопителей. Формула изобретения 1. Адаптивное устройство радиосвязи, содержащее в передающей части последовательно соединенные мультиплексор и кодер и последовательно соединенные модулятор и передатчик, а также блок управления скоростью передачи, в приемной части последовательно соединенные приемник и демодулятор и последовательно соединенные декодер и демультиплексор, а также блок управления скоростью приема Причем выход демодулятора через последовательно соединенные блок контроля и блок адаптации подключен к входу мультиплексора, а второй выход декодера , подключен к второму входу блока контроля, при этом соответствующие выходы демультйплексора непосредственно подключены к входу блока управления скоростью приема и через блок управления скоростью передачи - к второму входу мультиплексора, о т л и ч аю щ е е с я тем, что,с целью повышения скорости передачи, в него введены в передающей части последовательно соединенные буферный накопитель, элемент И.ЛИ и блок элементов И, выходы которого подключены к входам. модуляторов, а также два распределителя и блок управления отключением каналов По передаче, -вход которого,.

соединен с входом блока управления скоростью передачи, а выход подключен к входу первого распределителя, второй вход которого соединен соответственно с вторым выходом блока управления скоростью передачи и входом второго распределителя, другие выходы которого подключены к входам буферного накопителя, другие входы которого соединены с выходами кодера при этом выходы первого распределителя подключены к дру гим входам блока элементов И, в приемной части введены последовательно соединенные блок элементов И, элемент ИЛИ и буфёрный накопитель, выходы которого подключены к входам декодера, а также два распределителя и блок отключения каналов по приему, вход которого соединен с выходом демультиплексора, а .выход подключен к входу первого распределителя, второй вход которого соединен соответственно с выходом блока управления скоростью приема и входом второго распределителя, выходы которого подключены к другим входам буферного накопителя, а выходы лервого распределителя подключены .к другим входам блока элементов И,

2. Устройство по п.1, о т л и ч аю щ е е с я тем, что буферный накопитель состоит из накопительных узлов по числу каналов и управляющего узла, причем каждый накопительный узел, выполнен в виде регистра сдвига, разрядные выходы которого через соответствующие элементы И подключены к входам элемента ИЛИ, а управляющий узел выполнен в виде регистра сдвига, разрядные выходы которого через элемент И подключены к входам регистра сдвига накапливающего, узла, при этом элементы И управляющего узла соединены последовательно, а другие входы регистра сдвига управляющего узла подсоединены к вторым входам элементов И накапливающего узла, при Этом входы регистров сдвига, третьи входы элементов И накопительных узлов, вторые входы элементов И управляющего узла, выход элемента ИЛИ являются соответственно входами и вь1ходами буферного накопителя .

/ .1

Источники информации, принятые во внимание при экспертизе

1. Патент США № , кл. Н Ok В 1/38, 13.10.70.

| название | год | авторы | номер документа |

|---|---|---|---|

| РАДИОМОДЕМ | 2024 |

|

RU2830959C1 |

| Многоканальная адаптивная цифровая система связи | 1984 |

|

SU1220133A1 |

| АДАПТИВНОЕ УСТРОЙСТВО ПЕРЕДАЧИ ДАННЫХ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2008 |

|

RU2356171C1 |

| Система для передачи информации с двукратной фазовой манипуляцией сверточным кодом | 1982 |

|

SU1027748A1 |

| МОДЕМ ДЛЯ МНОГОНАПРАВЛЕННОЙ СВЯЗИ | 2018 |

|

RU2700392C1 |

| Многоканальная адаптивная цифровая система связи | 1982 |

|

SU1083381A1 |

| УСТРОЙСТВО МНОГОКАНАЛЬНОЙ РАДИОСВЯЗИ | 2023 |

|

RU2809552C1 |

| Устройство памяти на телевизионный кадр | 1987 |

|

SU1559430A1 |

| СПОСОБ ФОРМИРОВАНИЯ И ПЕРЕДАЧИ ДВУХКАНАЛЬНЫХ, В ТОМ ЧИСЛЕ СТЕРЕОФОНИЧЕСКИХ, СИГНАЛОВ ЗВУКОВОГО СОПРОВОЖДЕНИЯ, РАДИОВЕЩАНИЯ, ДАННЫХ И КОМАНД УПРАВЛЕНИЯ В СЕТЯХ ЭФИРНОГО И КАБЕЛЬНОГО ВЕЩАНИЯ (ВАРИАНТЫ), СИСТЕМА ПЕРЕДАЧИ СИГНАЛОВ МНОГОКАНАЛЬНОГО ЗВУКОВОГО СОПРОВОЖДЕНИЯ, РАДИОВЕЩАНИЯ, ДАННЫХ И КОМАНД УПРАВЛЕНИЯ В СЕТЯХ ЭФИРНОГО И КАБЕЛЬНОГО ВЕЩАНИЯ | 1999 |

|

RU2163420C2 |

| Система передачи неподвижных изображений | 1979 |

|

SU907870A1 |

Авторы

Даты

1982-09-15—Публикация

1981-02-02—Подача