вые выходы которых подключены соответственно через первый и второй буферные регистры к первым информационным входам четвертого и пятого коммутаторов, вторые выходы второго и третьего коммутаторов подключены соответственно через третий и четвертый буферные регистры к вторым информационным входам четвертого и пятого коммутаторов, выходы которых соединены соответственно с первым и вторым информационными входами управляемого переключателя, первый и второй выходы управляемого переключателя подключены к информационным входам соответственно первого и второго ключей, выходы которых подключены к информационным входам соответственно шестого и седьмого коммутаторов, первые и вторые выходы которых соединены соответственно с первыми и вторыми информационными входами коммутатора и управляемого распределителя импульсов, третий информационный вход которого подключен к выходу первого коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Кодек блочных кодов | 1987 |

|

SU1473088A1 |

| Система передачи информации перфорированным сверточным кодом с восьмифазной модуляцией | 1990 |

|

SU1795499A1 |

| МНОГОКАНАЛЬНОЕ ПРИЕМНО-ДЕМОДУЛИРУЮЩЕЕ УСТРОЙСТВО ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ СИСТЕМ СВЯЗИ | 2005 |

|

RU2305375C2 |

| Устройство для устранения неопределенности дискретнофазовой модуляции | 1983 |

|

SU1095428A1 |

| Кодек для системы связи с многократной фазовой модуляцией | 1987 |

|

SU1629992A1 |

| ЦИФРОВОЙ МОДЕМ КОМАНДНОЙ РАДИОЛИНИИ ЦМ КРЛ | 2013 |

|

RU2548173C2 |

| УСТРОЙСТВО ВЫЧИСЛЕНИЯ МЕТРИК ПУТЕЙ ДЕКОДЕРА ВИТЕРБИ | 1990 |

|

RU2022473C1 |

| УСТРОЙСТВО И СПОСОБ КАНАЛЬНОГО КОДИРОВАНИЯ/ДЕКОДИРОВАНИЯ | 1999 |

|

RU2204199C2 |

| СИСТЕМА СВЯЗИ | 2003 |

|

RU2249914C2 |

| Кодек несистематического сверточного кода | 1990 |

|

SU1714812A1 |

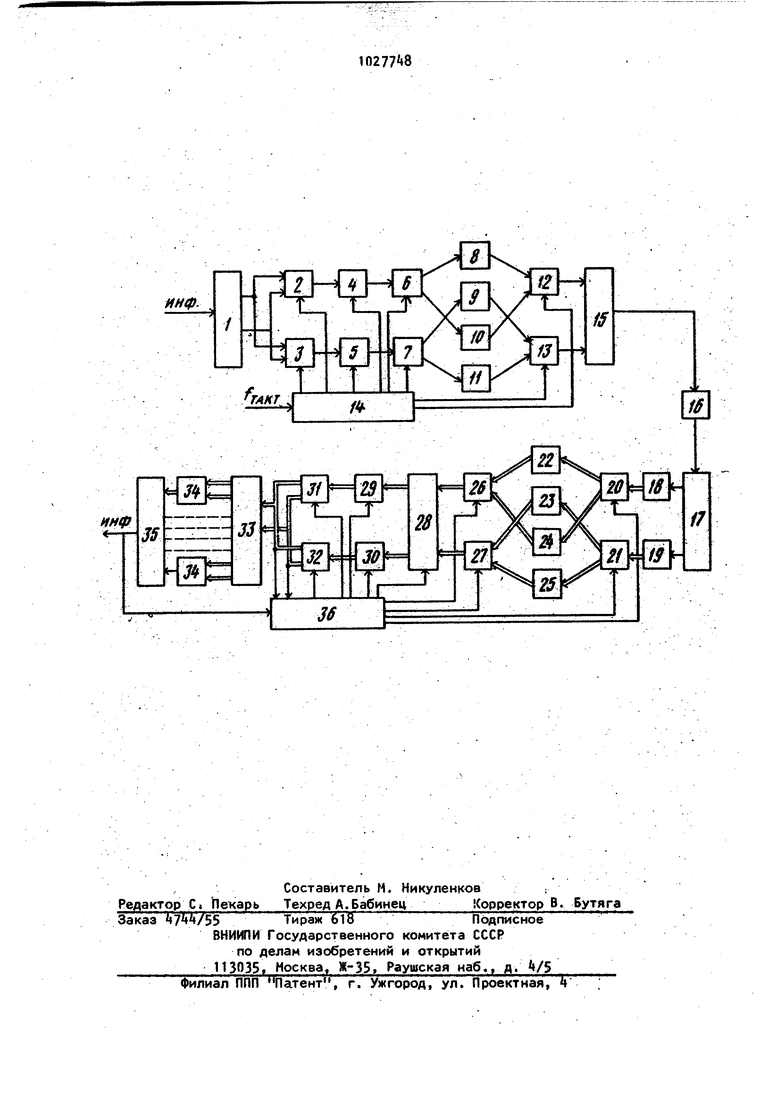

Изобретение относится к технике передачи и приема информации, кодируемой сверточным кодом в одно- или многоканальных системах связи с двукратной фазовой манипуляцией (ДФМ), и может быть использовано для уменьшения энергетических потерь, связанных с фазовым сдвигом вектора принимаемого сигнала относительно опорных сигналов. Известна система передачи кодовой информации в канале с ДФМ, содержащая два кодирующих устройства модулятор , каждая орта которого манипулируется последовательностью сим волов с одного кодирующего устройства, демодулятор ДФМ| первый и etoрой выходы которого соответственно соединены с двумя декодерами К недостаткам данной системы можно отнести то, что она предназначена только для двухканальной передачи информации, причем каждый канал занимает одну орту ДФМ. Нарушение ортогональности опорных сигналов или разворот вектора принимаемого сигнала относительно них приводит к межканальным помехам, которые ухуд шают помехоустрйчивость системы. Наиболее близкой по технической сущности к предлагаемой является сис тема, содержащая К сверточных кодеро с кодовой скоростьй на К каналов, выходы которых через коммутатор передаются на перемежитель и затем на модуляторр на приемной стороне выходы с демодулятора, квантованные на t -разрядов, последовательно коммутируются на устройство интерфейса, с которого параллельно подаются на К декодеров, выходы которых последовательно коммутируются на общую шину Г2. Недостатками данной системы является то, что, во-первых, она рассчитана только на кодовую скорость сверточнЪго кода и, во-вторых, формируемая последовательность кодовых символов образована таким образом, что кодовые символы от одного кодера никогда вместе не поступают на модулятор, что при фазовом сдвиге вектора принимаемого сигнала относительно опорных сигналов (при ДФМ) приводит к большим потерям в декодере за счет отсутствия взаимной компенсации, получаемой при обработке в целом, если бы вектор сигнала в системе с ДФМ переносил два символа, принадлежащих одному декодеру. Цель изобретения - повышение помехоустойчивости информации, передаваемой со скоростью R MV за счет уменьшения влияния фазовых погрешностей относительно опорных сигналов вектора сигнала. Поставленная цель достигается тем, что в систему, содержащую на передающей стороне многоканальный кодер сверточного кода, вход которого подключен к входу системы, модулятор, выход которого соединен с входом канала связи, на приемной стороне демодулятор, вход которого подключен к выходу канала связи, первый и второй выходы демодулятора соединены е входами соответственно первого и вто рого аналого-цифрового преобразовате лей, кольцевой коммутатор, первая и вторая группы выходов которого соединены соответсвенно с первыми и вто рыми входами соответствующих декодеров Оберточного кода, выходы которых подключены соответственно к входам первого коммутатора, выход которого соединен с выходом системы, введены на передающей стороне коммутаторы, ключи, буферные регистры и распределитель импульсов, вход которого под ключен к синхронизирующему входу сис темы, выходы соединены соответствен но с управляю1цими входами коммутаторов и ключей, первый и второй выходы многоканального кодера сверточного кода подключены соответственно к пер вым и вторым информационным входам первого и второго коммутаторов, выхо ды которых соединены с информацио ными входами соответственно первого и второго ключей, выходы которых сое динены с информационными входами соответственно третьего и четвертого коммутаторов, первые выходы которых подключены соответственно через первый и второй буферные регистры к пер вым информационным входам пятого и шестого коммутаторов, вторые выходы третьего и четвертого коммутаторов соединены соответственно через третий и четвертый буферные регистры с вторыми информационными входами пято го и шестого коммутаторов, выходы которых подключены соответственно к первому и второму входам модулятора, на приемной стороне введены коммутаторы, ключи, буферные регистры, управляемый переключатель и управляемый распределитель импульсов, выходы которого подключены к управляющим входам коммутаторов, буферных регист ров, ключей, управляемого переключателя, выходы первого и второго аналого-цифровых преобразователей соеди нены с информационными входами ссютветственно второго и третьего коммутаторов , п.ервые выходы которых подключены соответственно через первый и второй буферные регистры к первым информационным входам четвертого и пятого коммутаторов, вторые выходы второго и третьего коммутаторов подключены соответственно через третий и четвертый буферные регистры к вторым информационным входам четвертого и пятого коммутаторов, выходы которых соединены схэответственно с первым и вторым информационными входами управляемого переключателя, первый и второй выходы управляемого переключателя подключены к информационным входам соответственно первого и второго ключей, выходы которых подключены к информационным входам соответственно шестого и седьмого коммутаторов, первые и вторые входы которых соединены соответственно с первыми и вторыми информационнь1ми входами кольцевого коммутатора и управляемого распределителя импульсов, третий информационный вход которого подключен к выходу первого коммутатора. На чертеже представлена блок-схе-. ма предлагаемой системы.. Система содержит многоканальный кодер 1 сверточного кода, коммутаторы 2 и 3, ключи k и 5 коммутаторы 6 и 7 буферные регистры 8-11, коммутаторы Т2 и 13, распределитель 1 импульсов, модулятор t5 ЛФМ, канал 16 связи, демодулятор 17 ЛW, аналого-цифровые преобразователи 18 и 19 коммутаторы 20 и 21, буферные регистры 22-25, коммутаторы 26 и 27, управляемый переключатель 2В, ключи 29 и 30, коммутаторы 31 и 32, кольцевой 0--ичный коммутатор 33, декодер 3 сверточного кода, коммутатор 35 и управляемый распределитель 3 импульсов. Управляемый распределитель 36 импульсов включает кодер сверточного кода, вход которого объединен с входом выделения тактовой частоты и подключен к третьему входу управляемого распределителя импульсов, выход кодера сверточного кода соединен с первым входом схемы совпадения, второй и третий входы которой подключены соответственно к первому и второму входам управляемого распределителя импульсов, выход схемы совпадения через пороговый блок соединен с первым входом ключа, второй вход ключа подключен к выходу блока выделения тактовой частоты, выход ключа соединен с входом кольцевого регистра, выходы кольцевого регистра соединены с соответствующими входами коммутационной матрицы, выходы которой являются выходами управляемого распределителя импульсов.

Система работав следующим образом.

Кодер 1 сверточного кода с кодовой скоростью формирует К независимых канальных последовательностей, каждая из которых соответствует одной из К разрядным информационным последовательностям. На выход кодера 1 в каждый данный момент времени поступают два символа от какой-либо одной последовательности. Распределитель 14 импульсов путем соответствующего управления коммутаторами и ключами на передающей стороне, во-первых, формирует выколотый свертрмный код с заданной скоростью R не пропуская определенные кодовые символы на входы буферных регистров 8-11, и, во-вторых, заполняет поочередно первые буферные регистры 8 и 9 и вторые буферные регистры 10 и 11 таким образом, чтобы кодовые символы, находящиеся в обоих регистрах, например, в i разряде, принадлежали одной кодовой последовательности, в следующем (i+1) разря- де - другой кодовой последовательности и т.д. В то время, как одна пара буферных регистров заполняется, с другой пары буферных регистров производится параллельное считывание символов на модулятор ДФМ. Длина буферного регистра Lf для фиксированW м-,

НОИ КОДОВОЙ скорости R «tvrt опрв деляется как .

Lj (ra+nlik, где п - число кодированных символов

или кодовых полиномов; п - число сдвигов информационного сигнала.

На приемной стороне заполнение и считывание буферных регистров 22-25 производится по той же самой программе, что и на передающей стороне с тем только отличием, что буферные регистры представляют не двоичные .регистры, а (-ичные регистры, которые заполняются параллельным ()-разрядным двоичным кодом, с выходом преобразователей 18 и 19 аналог-цифра в моменты опроса последними выходных сигналов с демодулятора 17 ДФМ.

При подаче сигналов с подавленной несущей из-за неоднозначности фазы принимаемого сигнала введен управляемый переключатель 28 (блок раскры тия фазовой неопределенности), который в случае,, если фаза сигнала сдвинута на , осуществляет перекоммутацию входных потоков. Если фаза сигнала сдвинута на ТЬ, то вместо

перекоммутации входных потоков производится инверсия знака символов. Управление данным блоком осуществляется на основе сравнения и анализа выходной информации с декодеров З

сверточного кода и поступающих на их вход кодовых последовательностей с коммутаторов 31 и 32, аналогично как это делается для установления узловой синхронизации.

При четырехфазной манипуляции операции уст анавления узловой синхронизации и раскрытия фазовой неопределенности, как правило, совмещаются. При правильном выполнении указанных

операций на каждый из К декодеров 3 поступает независимая q-ичная последовательность канальных символов.

Таким образом, за счет того, что каждая пара символов, передаваемых по каналу связи в данный момент времени, принадлежит одной кодовой последовательности, так называемые межканальные помехи, приводящие к перекачке энергии из одного канала в другой, при фазовом сдвиге принимаемого вектора сигнала относительно опорнь1Х сигналов, при обработке данных символов в целом в одном декодере приводят к существенно меньшим потерям, что и отличает предлагаемую систему передачи информации сверточным кодом с кодовой скоростью R ii.

fl Т

ОТ прототипа.

Авторы

Даты

1983-07-07—Публикация

1982-03-03—Подача