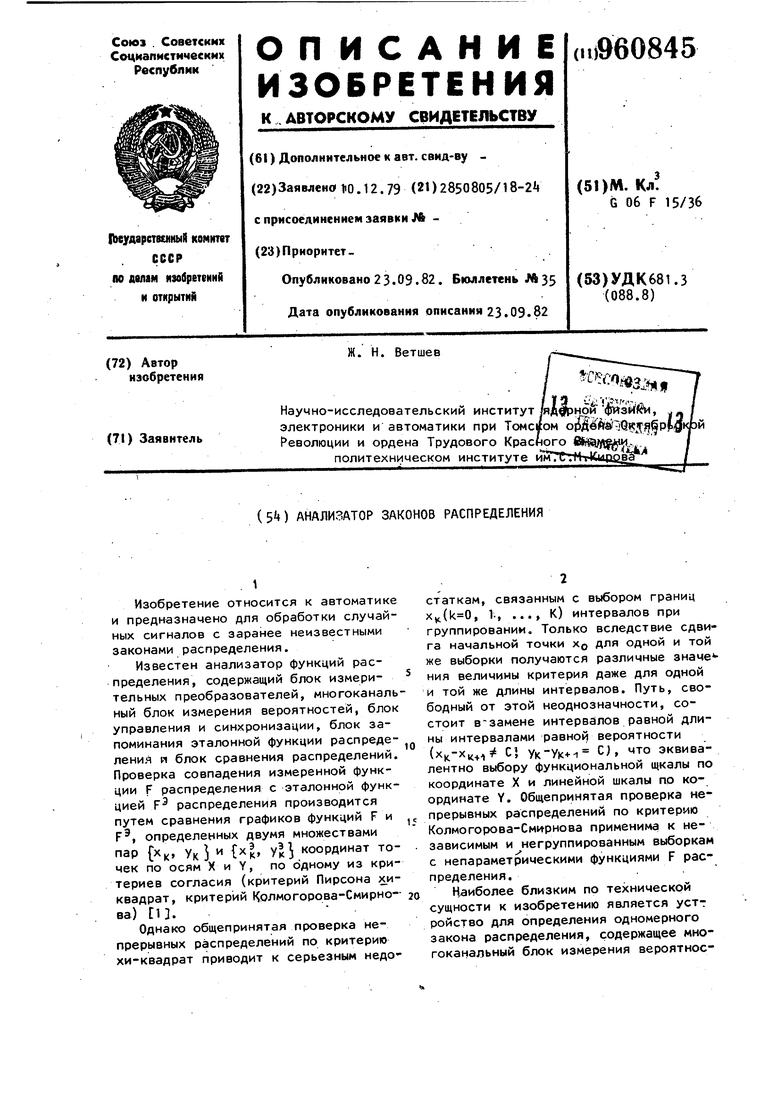

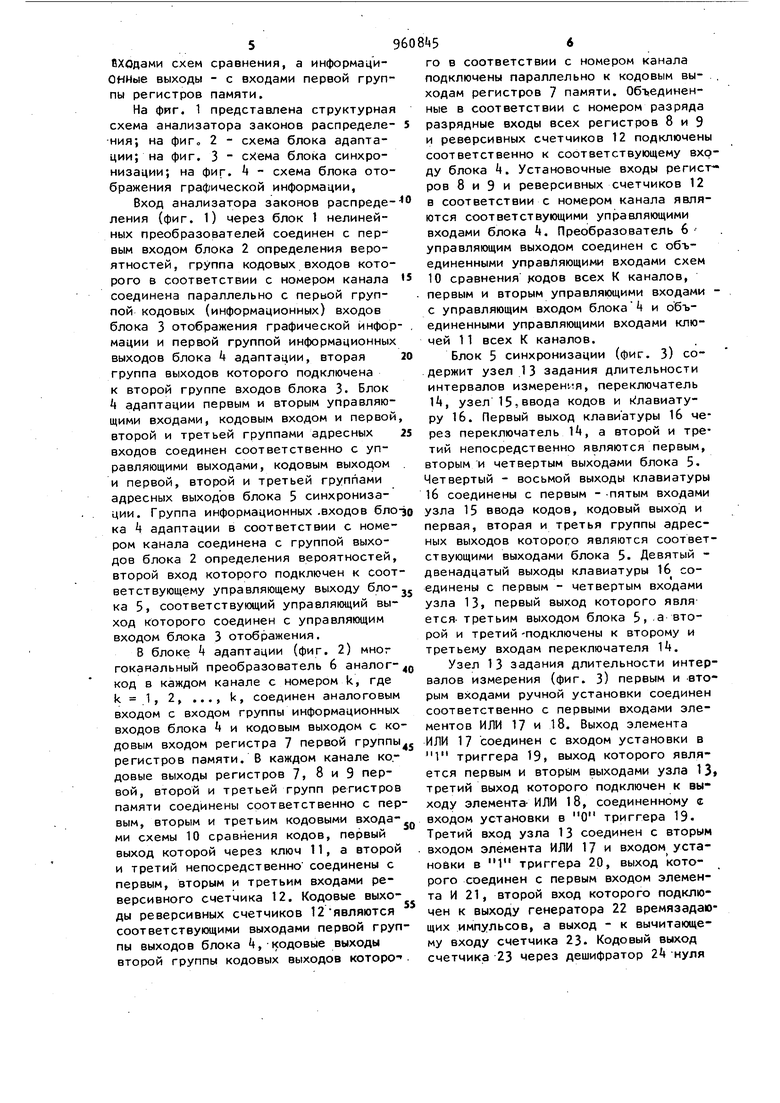

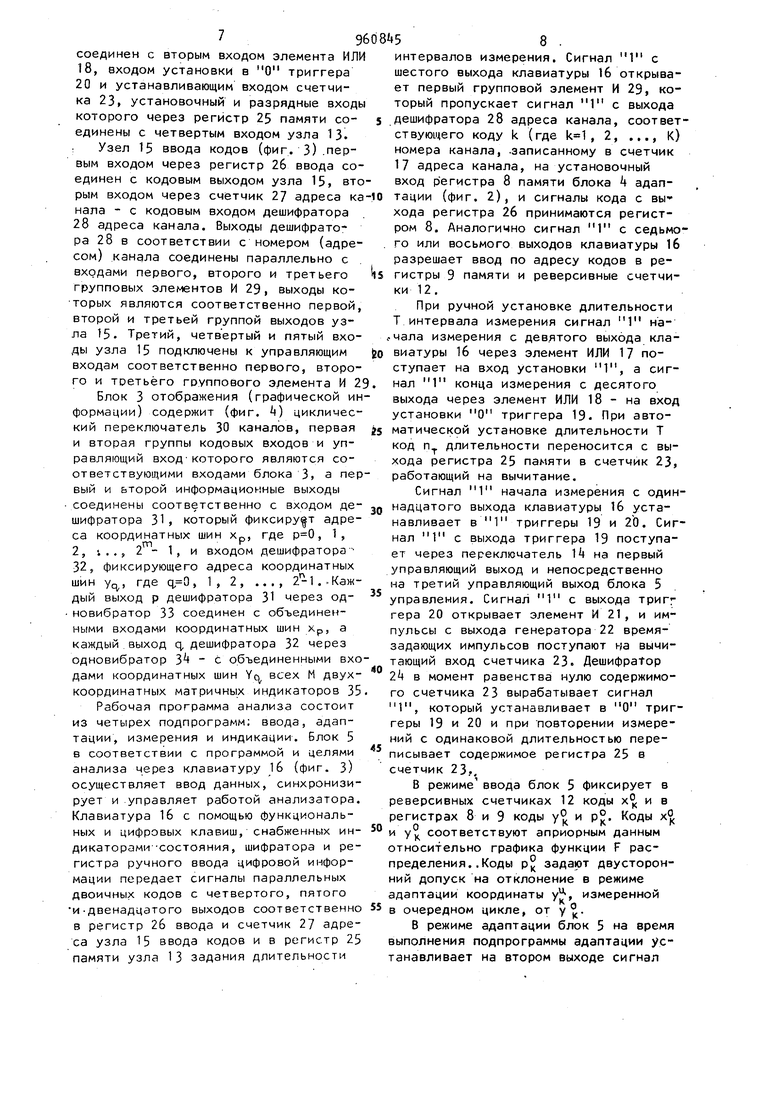

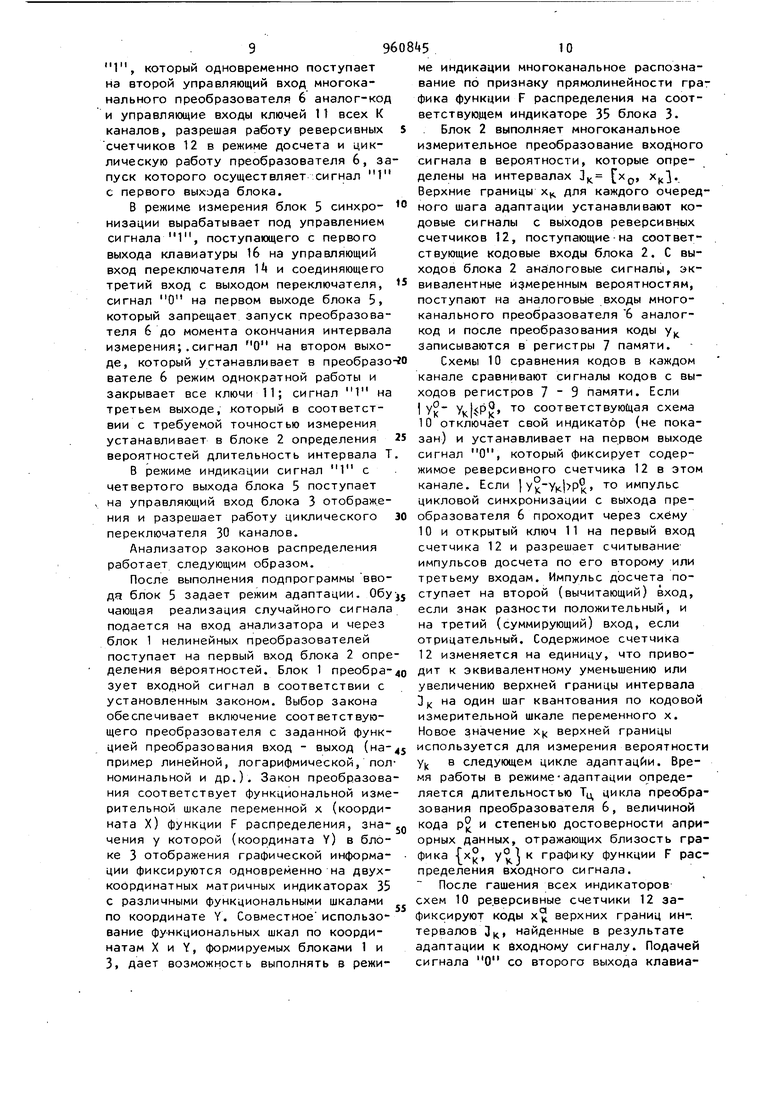

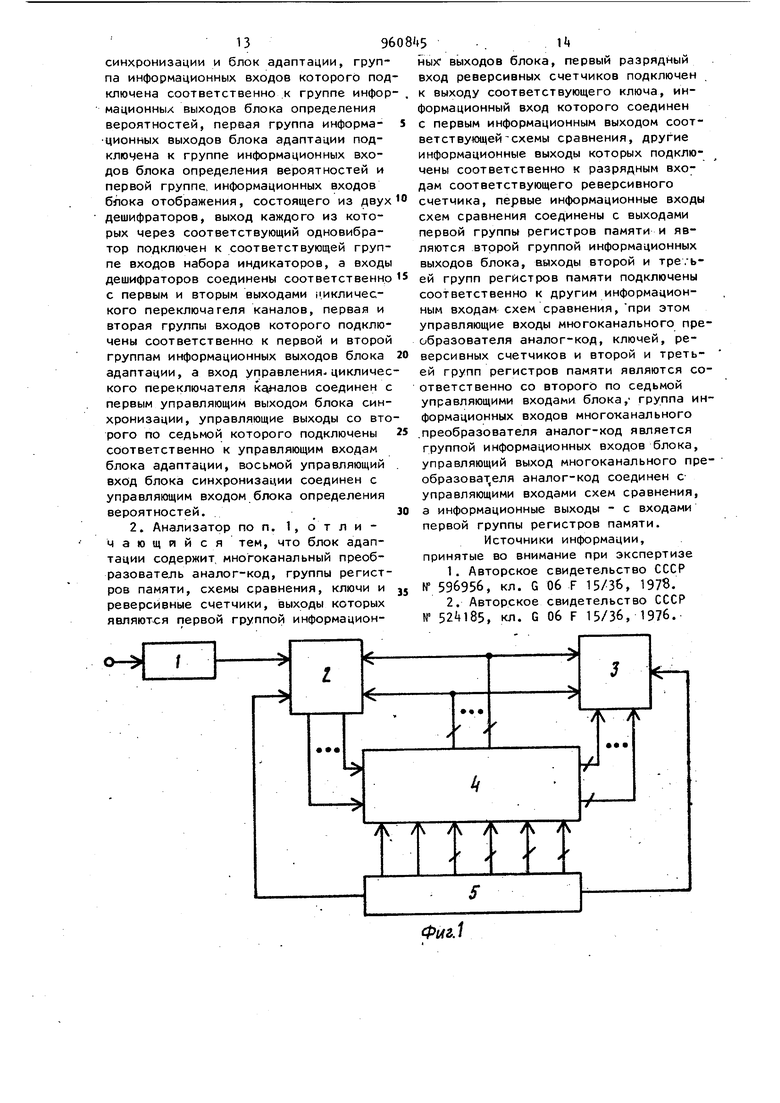

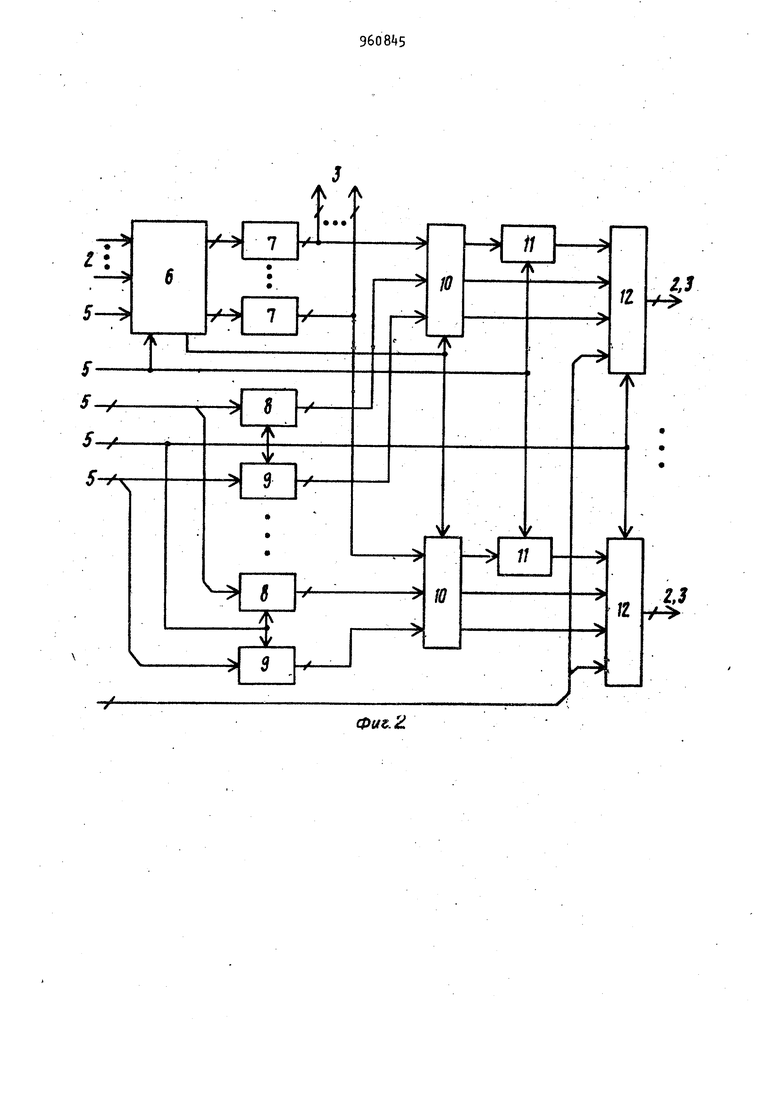

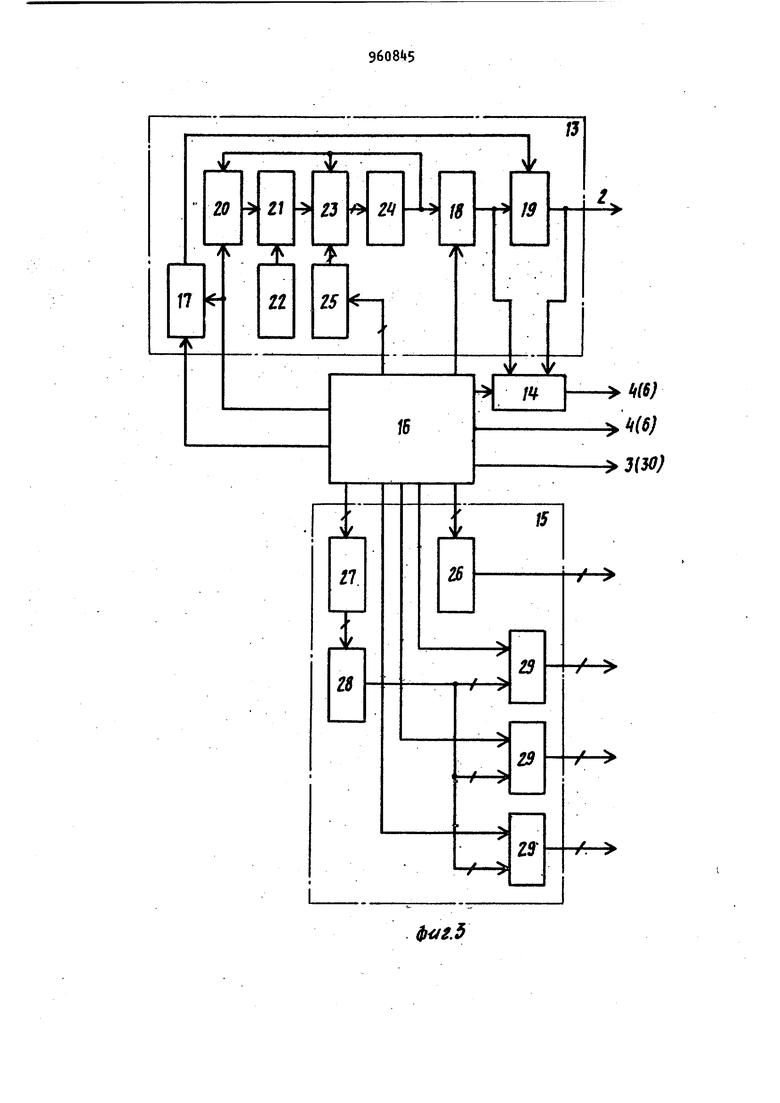

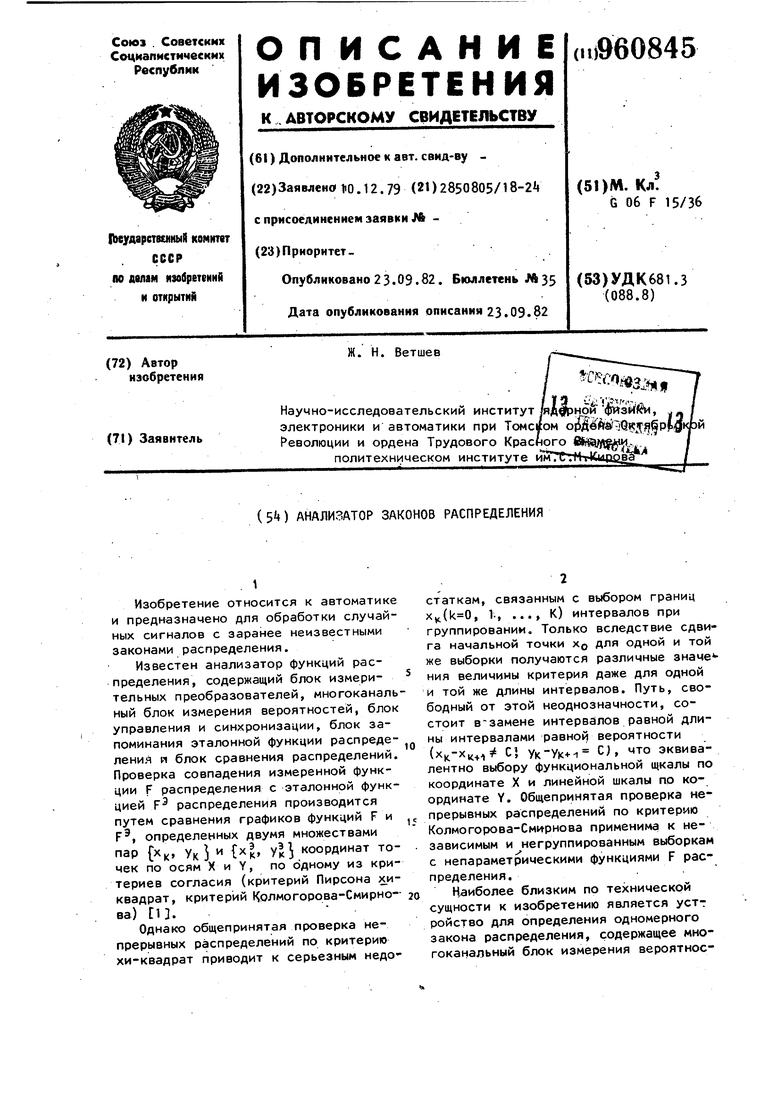

Изобретение относится к автоматике и предназначено для обработки случайных сигналов с заранее неизвестными законами распределения. Известен анализатор функций распределения, содержащий блок измерительных преобразователей, многоканаль ный блок измерения вероятностей, блок управления и синхронизации, блок запоминания эталонной функции распределения и блок сравнения распределений. Проверка совпадения измеренной функции F распределения с эталонной функцией F распределения производится путем сравнения графиков функций F и F, определенных двумя множествами пар xjj, УК 5 и {х, у| координат точек по осям X и Y, по одному из критериев согласия (критерий Пирсона хиквадрат, критерий Колмогорова-Смирно- ва) 1. Однако общепринятая проверка непрерывных распределений по критерию хи-квадрат приводит к серьезным недостаткам, связанным с выбором границ (, 1., ..., к) интервалов при группировании. Только вследствие сдвига начальной точки Хд для одной и той же выборки получаются различные значе ния величины критерия даже для одной и той же длины интервалов. Путь, свободный от этой неоднозначности, состоит в-замене интервалов равной длины интервалами paBHofj вероятности ( С} эквивалентно выбору функциональной щкалы по координате X и линейной шкалы по координате Y. Общепринятая проверка непрерывных распределений по критерию Колмогорова-Смирнова применима к независимым и негруппированным выборкам с непараметрическими функциями F распределения. Наиболее близким по технической сущности к изобретению является устт ройство для определения одномерного закона распределения, содержащее многоканальный блок измерения вероятноетем, первыми выходом и входом соединенного с блоком измерительных преоб разователей, информационный вход которого является входом устройства, вторым и третьим выходами - с блоком отображения графической информации, четвертым и пятым выходами - с арифметическим блоком, выход которого подключен к третьему входу блока отображения графической информации 2}. - Однако в известном устройстве границы х задают интервалы равной дли ны, на которых измеряются вероятности соответствующие границам у интервалов неравной длины. График фуИкции F распределения отображается на одном индикаторе в прямоугольной системе координат X иу с линейными шкалами X и у, функциональные законы которых не согласованы с видом всех функций F распределения, кроме линейной. Всле ствие такого представления кривых рас пределения точность анализа графиков функций F распределения суцественно занижена . Известное устройство с небольшим количеством каналов () при анализе функций F распределения, принадлежащих к известным в теории вероятностей идентифицируемым статистимеским структурам (например, семей ства распределений экспоненциального или масштабно-сдвигового типа), работает со значительными потерями точнос ти из-за неоптимального выбора верхних границ Х| интервалов группирования. Так, например, при оценке параметра сдвига нормального закона распределения с известным параметром мас штаба потери точности превышают 5 относительно точности оценки максимального правдоподобия по негруппированной выборке того же объема..Потери точности анализа в условиях, при которых закон распределения заранее неизвестен, еще выше. Целью изобретения является повышение точности анализа. Указанная цель достигается тем, что анализатор законов распределения, содержащий блок отображения, блок нелинейных преобразователей, вход которого является входом анализатора, а выход соединен с информационным входом блока определения вероятностей, содержит блок синхронизации и блок адаптации, группаинформационных входов которого подключена соответственно к группе информационных выходов блока определения вероятностей, первая группа информационных выходов блока адаптации подключена к группе информационных входов блока определения вероятностей и первой группе информационных входов блока отображения, состЬящего из двух дешифраторов, выход каждого из которых через соответствующий одновибратор подключен к соответствующей группе входов набора индикаторов, а входы дешифраторов соединены соответственно с первым и вторым выходами циклического переключателя каналов, первая и вторая группы входов которого подключены соответственно к первой и второй группам информационных выходов блока адаптации, а вход управления циклического переключателя каналов соединен с первым управляющим выходом блока синхронизации, управляющие выходы со второго по седьмой которого подключены соответственно к управляющим входам блока адаптации, восьмой управляющий вход блока синхронизации соединен с управляющим входом блока определения вероятностей. Кроме того, блок адаптации содержит многоканальный ггреобразоватёль анало -код, группы регистров памяти, схемы сравнения, ключи и реверсивные счетчики, выходы которых являются первой группой информационных выходов блока, первый разрядный вход реверсивных счетчиков подключен к выходу соответствующего ключа, информационный вход которого соединен с первым информационным выходом соответствующей схемы сравнения, другие информационные выходы которых подключены соответственно к разрядным входам соответствующего реверсивного счетчика, первые информационные входы схем сравнения соединены с выходами первой группы регистров памяти и являются второй группой информационных выходов блока, выходы второй и третьей групп регистров памяти подключены соответственно к другим информационным входам схем сравнения, при этом управляющие входы многоканального преобразователя анало -код, ключей, реверсивных счетчиков и второй и третьей групп регистров памяти являются соответственно со второго по седьмой управляющими входами блока, группа информационных входов многоканального преобразователя аналог-код является группой информационных входов блока, управляющий выход многоканального преобразователя аналог-код соединен с управляющими входами схем сравнения, а информационные выходы - с входами первой группы регистров памяти. На фиг. 1 представлена структурная схема анализатора законов распределения; на фиг„ 2 - схема блока адаптации; на фиг. 3 - схема блока синхронизации; на фиг. схема блока отображения графической информации, Вход анализатора законов распределения {фиг. 1) через блок 1 нелинейных преобразователей соединен с первым входом блока 2 определения вероятностей , группа кодовых входов которого в соответствии с номером канала соединена параллельно с первой группой кодовых (информационных) входов блока 3 отображения графической инфор мации и первой группой информационных выходов блока t адаптации, вторая группа выходов которого подключена к второй группе входов блока 3. Блок А адаптации первым и вторым управляющими входами, кодовым входом и первой второй и третьей группами адресных входов соединен соответственно с управляющими выходами, кодовым выходом и первой, второй и третьей группами адресных выходов блока 5 синхронизации. Группа информационных .входов бло ка 4 адаптации в соответствии с номером канала соединена с группой выходов блока 2 определения вероятностей, второй вход которого подключен к соот ветствующему управляющему выходу блока 5, соответствующий управляющий выход которого соединен с управляющим входом блока 3 отображения. В блоке k адаптации (фиг. 2) мног гоканальный преобразователь 6 аналогкод в каждом канале с номером k, где k 1, 2, ..., k, соединен аналоговым входом с входом группы информационных входов блока и кодовым выходом с ко довым входом регистра 7 первой группы регистров памяти. В каждом канале ко.довые выходы регистров 7, 8 и 9 первой, второй и третьей групп регистров памяти соединены соответственно с пер вым, вторым и третьим кодовыми входами схемы 10 сравнения кодов, первый выход которой через ключ 11, а второй и третий непосредственно соединены с первым, вторым и третьим входами реверсивного счетчика 12. Кодовые выходы реверсивных счетчиков 12являются соответствующими выходами первой груп пы выходов блока 4, кодовые выходы второй группы кодовых выходов которо- го в соответствии с номером канала подключены параллельно к кодовым вы- , ходам регистров 7 памяти. Об единенные в соответствии с номером разряда разрядные входы всех регистров 8 и 9 и реверсивных счетчиков 12 подключены соответственно к соответствующему входу блока Ц. Установочные входы регистров 8 и 9 и реверсивных счетчиков 12 в соответствии с номером канала являются соответствующими управляющими входами блока k. Преобразователь 6 управляющим выходом соединен с объединенными управляющими входами схем 10 сравнения кодов всех К каналов, первым и вторым управляющими входами с управляющим входом блока и объединенными управляющими входами ключей 11 всех К каналов. Блок 5 синхронизации (фиг. 3) содержит узел 13 задания длительности интервалов измерен я, переключатель 1А, узел 15,ввода кодов и к лавиатуру 16. Первый выход клавиатуры 16 через переключатель 1, а второй и третий непосредственно являются первым, вторым и четвертым выходами блока 5. Четвертый - восьмой выходы клавиатуры 16 соединены с первым - -пятым входами узла 15 ввода кодов, кодовый выход и первая, вторая и третья группы адресных выходов которого являются соответствующими выходами блока 5. Девятый двенадцатый выходы клавиатуры 16 соединены с первым - четвертым входами узла 13, первый выход которого явля ется- третьим выходом блока 5, .а второй и третий -подключены к второму и третьему входам переключателя 1. Узел 13 задания длительности интервалов измерения (фиг. 3) первым и -вторым входами ручной установки соединен соответственно с первыми входами элементов ИЛИ 17 и 18. Выход элемента ИЛИ 17 соединен с входом установки в 1 триггера 19, выход которого является первым и вторым выходами узла 13 третий выход которого подключен к выходу элемента- ИЛИ 18, соединенному е входом установки в О триггера 19. Третий вход узла 13 соединен с вторым входом элемента ИЛИ 17 и входом установки в 1 триггера 20, выход которого соединен с первым входом элемента И 21, второй вход которого подключен к выходу генератора 22 времязадающих импульсов, а выход - к вычитающему входу счетчика 23. Кодовый выход счетчика 23 через дешифратор 2 нуля 79 соединен с вторым входом элемента ИЛИ 18, входом установки в О триггера 20 и устанавливающим входом счетчика 23, установочный и разрядные входы которого через регистр 25 памяти соединены с четвертым входом узла 13. : Узел 15 ввода кодов (фиг. 3) .первым входом через регистр 26 ввода соединен с кодовым выходом узла 15, вто рым входом через счетчик 27 адреса ка нала - с кодовым входом дешифратора 28 адреса канала. Выходы дешифратора 28 в соответствии с номером (адресом) канала соединены параллельно с входами первого, второго и третьего групповых элементов И 29, выходы которых являются соответственно первой, второй и третьей группой выходов узла 15. Третий, четвертый и пятый входы узла 15 подключены к управляющим входам соответственно первого, второго и третьего группового элемента И 2 Блок 3 отображения (графической ин формации) содержит (фиг. А) циклический переключатель 30 каналов, первая и вторая группы кодовых входов и управляющий входкоторого являются соответствующими входами блока 3, а пер вый и второй информационные выходы соединены соответственно с входом дешифратора 31, который фиксирует адреса координатных шин Хр, где , 1, 2, ..., 1, и входом дешифратора 32, фиксирующего адреса координатных шин Yq, где q,0, 1, 2, ..., 2-1.. Каждый выход р дешифратора 31 через одновибратор 33 соединен с объединенными входами координатных шин Хр, а каждый выход q, дешифратора 32 через одновибратор З - с объединенными вхо дами координатных шин Yq всех М двухкоординатных матричных индикаторов 35 Рабочая программа анализа состоит из четырех подпрограмм; ввода, адаптации, измерения и индикации. Блок 5 в соответствии с программой и целями анализа через клавиатуру 1б (фиг. З) осуществляет ввод данных, синхронизирует и управляет работой анализатора. Клавиатура 16 с помощью функциональных и цифровых клавиш, снабженных индикаторами -состояния, шифратора и регистра ручного ввода цифровой информации передает сигналы параллельных двоичных кодов с четвертого, пятого и-двенадцатого выходов соответственно в регистр 2б ввода и счетчик 27 адреса узла 15 ввода кодов и в регистр 25 памяти узла 13 задания длительности 58 . интервалов измерения. Сигнал 1 с шестого выхода клавиатуры 16 открывает первый групповой элемент И 29, который пропускает сигнал 1 с выхода дешифратора 28 адреса канала, соответствующего коду k (где , 2, ..., К) номера канала, .записанному в счетчик 17 адреса канала, на установочный вход регистра 8 памяти блока k адаптации (фиг. 2), и сигналы кода с вы хода регистра 26 принимаются регистром 8. Аналогично сигнал 1 с седьмого или восьмого выходов клавиатуры 16 разрешает ввод по адресу кодов в регистры 9 памяти и реверсивные счетчики 12, При ручной установке длительности Т интервала измерения сигнал 1 на.чала измерения с девятого выхода клавиатуры 16 через элемент ИЛИ 17 поступает на вход установки 1, а сигнал 1 конца измерения с десятого выхода через элемент ИЛИ 18 - на вход установки О триггера 19. При автоматической установке длительности Т код п длительности переносится с выхода регистра 25 памяти в счетчик 23, работающий на вычитание. Сигнал 1 начала измерения с одиннадцатого выхода клавиатуры 16 устанавливает в 1 триггеры 19 и 20. Сигнал 1 с выхода триггера 13 поступает через переключатель 1 на первый управляющий выход и непосредственно на третий управляющий выход блока 5 управления. Сигнал 1 с выхода тригг гера 20 открывает элемент И 21, и импульсы с выхода генератора 22 времязадающих импульсов поступают на вычитающий вход счетчика 23. Дешифратор 2 в момент равенства нулю содержимого счетчика 23 вырабатывает сигнал 1, который устанавливает в О триггеры 19 и 20 и при повторении измерений с одинаковой длительностью переписывает содержимое регистра 25 в счетчик 23,. В режимеввода блок 5 фиксирует в реверсивных счетчиках 12 коды х°, и в регистрах 8 и 9 коды у и р°. Коды х и у соответствуют априорным данным относительно графика функции F распределения. .Коды р задают двусторонний допуск на отклонение в режиме адаптации координаты у, измеренной g очередном цикле, от у°. В режиме адаптации блок 5 на время выполнения подпрограммы адаптации устанавливает на втором выходе сигнал 1, который одновременно поступает на второй управляющий вход многоканального преобразователя 6 аналог-код и управляющие входы ключей П всех К каналов, разрешая работу реверсивных счетчиков 12 в режиме досчета и циклическую работу преобразователя 6, за пуск которого осуществляет сигнал 1 с первого выхода блока. В режиме измерения блок 5 синхронизации вырабатывает под управлением сигнала 1, поступающего с первого выхода клавиатуры 16 на управляющий вход переключателя 1 и соединяющего третий вход с выходом переключателя, сигнал О на первом выходе блока 5, который запрещает запуск преобразователя б до момента окончания интервала измерения;.сигнал О на втором выходе, который устанавливает в преобразо вателе 6 режим однократной работы и закрывает все ключи 11; сигнал 1 на третьем выходе, который в соответствии с требуемой точностью измерения устанавливает в блоке 2 определения вероятностей длительность интервала Т В режиме индикации сигнал 1 с четвертого выхода блока 5 поступает на управляющий вход блока 3 отображения и разрешает работу циклического переключателя 30 каналов. Анализатор законов распределения работает следующим образом. После выполнения подпрограммы ввода блок 5 задает режим адаптации. Обу чающая реализация случайного сигнала подается на вход анализатора и через блок 1 нелинейных преобразователей поступает на первый вход блока 2 опре деления вероятностей. Блок 1 преобразует входной сигнал в соответствии с установленным законом. Выбор закона обеспечивает включение соответствующего преобразователя с заданной функцией преобразования вход - выход (например линейной, логарифмической, пол номинальной и др.). Закон преобразова ния соответствует функциональной изме рительной шкале переменной х (координата Х) функции F распределения, значения у которой (координата Y) в блоке 3 отображения графической информации фиксируются одновременно на двухкоОрдинатных матричных индикаторах 35 с различными функциональными шкалами по координате Y. Совместное использование функциональных шкал по координатам X и Y, формируемых блоками 1 и 3, дает возможность выполнять в режиме индикации многоканальное распознавание по признаку прямолинейности графика функции F распределения на соответствующем индикаторе 35 блока 3. Блок 2 выполняет многоканальное измерительное преобразование входного сигнала в вероятности, которые определены на интервалах 3 хр, х. Верхние границы Хц. для каждого очередного шага адаптации устанавливают кодовые сигналы с выходов реверсивных счетчиков 12, поступающиена соответствующие кодовые входы блока 2. С выходов блока 2 аналоговые сигналы, эквивалентные измеренным вероятностям, поступают на аналоговые входы многоканального преобразователя 6 анало - код и после преобразования коды у записываются в регистры 7 памяти. Схемы 10 сравнения кодов в каждом канале сравнивают сигналы кодов с выходов регистров 7 9 памяти. Если I ° соответствующая схема 10 отключает свой индикатор (не показан) и устанавливает на первом выходе сигнал О, который фиксирует содержимое реверсивного счетчика 12 в этом канале. Если . ° импульс цикловой синхронизации с выхода преобразователя 6 проходит через схему 10 и открытый ключ 11 на первый вход счетчика 12 и разрешает считывание импульсов досчета по его второму или третьему входам. Импульс досчета поступает на второй (вычитающий) вход, если знак разности положительный, и на третий (суммирующий) вход, если отрицательный. Содержимое счетчика 12 изменяется на единицу, что приводит к эквивалентному уменьшению или увеличению верхней границы интервала 3)( на один шаг квантования по кодовой измерительной шкале переменного х. Новое значение хц верхней границы используется для измерения вероятности YIJ в следующем цикле адаптации. Время работы в режиме-адаптации определяется длительностью Тц цикла преобразования преобразователя 6, величиной кода р и степенью достоверности априорных данных, отражающих близость графика {х°, у к графику функции F распределения входного сигнала. После гашения всех индикаторов схем 10 реверсивные счетчики 12 заиксируют коды х верхних границ ин-. тервалов 3ц, найденные в результате даптации к йходному сигналу. Подачей игнала О со второго выхода клавиа113608туры 16 устанавливается режим измерёния. Случайный сигнал с входа анализатора через блок 1 поступает на первый вход блока 2, на второй вход которого поступает сигнал 1 длительное- 5 ти Т. В момент окончания интервала Т измерения сигнал 1 с выхода элемента ИЛИ 18 блока 5 поступает на первый управляющий вход преобразователя 6 аналог-код и разрешает выполнить цикл преобразования, в конце которого регистры 7 памяти зафиксируют коды Уц вероятностей, определенных на интервалах Зц(х0, xJ). Мнох{ество пар кодов у фиксирует график из- 15 меренной функции F распределения, и блок 5 задает режим индикации. В режиме индикации коды х и у, где k циклически пробегает все значе- ния от 1 до К, являются кодами адреса о соответствующих шин по координатам X и Y двухкоординатных матричных индикаторов 35. В блоке 3 отображения цик-. лический переключатель 30 чаналов осуществляет с заданной тактовой частотой поочередное соединение в соответствии с номером К канала выхода реверсивного счетчика 12 с входом дешифратора адреса координатных шин Хр и выхода регистра 7 памяти с входом дешифратора 32 адреса координатных 9шин Yq,. Сигналы 1 с выходов дешифраторов 31 и 32 (номер выхода соответствует принятому коду адреса х° и у) запускают свои одновибраторы, которые формируют импульсы возбуждения своих координатных шин. Импульсы с выходов одновибраторов 33 и 3, выбранных по адресам р и q, поступают одновременно на индикаторные ячейки, расположённые на пересечении координатных шин с номерами р и q, всех М двухкоординатных матричных индикаторов 35 и устанавливают их в рабочее состояние. Отображение графика , у Годной функции F распределения на экранах всех М индикаторов.35 производится за один цикл работы переключателя 30. На экране соответствующего индикатора 35 график функции F изображается.в виде прямой линии, если он совпадает с законом распределения, по которому построены функциональные шкалы этого индикатора что позволяет при М-канальном распознавании классифицировать наблюдаемую функцию F распределения, а затем идентифицировать ее в выбранном классе путем оценки величины параметров, опигы8г1Ю1дих функцию F. Сигналы кодов xJ и с выходов переключателя 30 могут быть выведены на внешнее вычислительное устройство для совместной с.данными визуального анализа обработки измерительной информации. Предлагаемый.анализатор законов распределения существенно уменьшает погрешность анализа сигналов с заранее неизвестными функциями F распределения. Точность анализа по сравнению с известными повышена за счет соответствующего уменьшения методической, аппаратурной и статистической составляющих погрешностей анализа, При небольшом числе каналов измерения вероятностей ( - 16) методическая погрешность анализа уменьшена за счет оптимального выбора верхних границ х интервалов группирования, Аппаратурная и статистическая погрешности анализа уменьшена за счет того, что неравномерное изменение графика функции F распределения вдоль координатных осей X и Y компенсируется выбором вида функции преобразования, задаваемой блоком 1 измерительных преобразователей (по координате Х), и выбором функциональной шкалы (по координате Y), задаваемой координатной сеткой соответствующего индикатора 35 входящего в состав блока 3 отображе-; ния графической информации, что обеспечивает высокую точность классификации и идентификации известных в математической статистике идентифицируемых статистических структур, к которым, в частности, принадлежат следующие модели законов распределения: равномерный, экспоненциальный, арксинуса нормальный, логарифмически нормальный, Вейбулла, Коши, Релея, Накагами. Таким образом, технико-экономический эффект предлагаемого изобретения . заключается-в повышении достоверности измерительной информации за счет высокой точности.анализа. Формула изобретения 1. Анализатор законов распределения, содержащий блок отображения, блок нелинейных преобразователей, вход которого является входом анализатораj а выход соединен с информационным входом блока определения вероятностей, отличающийся тем, что, с целью повышения точности, он содержит блок синхронизации и блок адаптации, группа информационных входов которого под ключена соответственно .к группе инфор мационных выходов блока определения вероятностей, первая группа информационных выходов блока адаптации подключена к группе информационных входов блока определения вероятностей и первой группе, информационных входов блока отображения, состоящего из двух дешифраторов, выход каждого из которых через соответствующий одновибратор подключен к соответствующей группе входов набора индикаторов, а входы дешифраторов соединены соответственно с первым и вторым выходами 11.иклического переключателя каналов, первая и вторая группы входов которого подключены соответственно к первой и второй группам информационных выходов блока адаптации, а вход управления-цикличес кого переключателя ка налов соединен с первым управляющим выходом блока синхронизации, управляющие выходы со вто рого по седьмой которого подключены соответственно к управляющим входам блока адаптации, восьмой управляющий вход блока синхронизации соединен с управляющим входом блока определения вероятностей. 2. Анализатор по п. 1, от л и чающийся тем, что блок адаптации содержит, многоканальный преобразователь анало -код, группы регистров памяти, схемы сравнения, ключи и реверсивные счетчики, выходы которых являются первой группой информационнык выходов блока, первый разрядный вход реверсивных счетчиков подключен к выходу соответствующего ключа, информационный вход которого соединен С первым информационным выходом соответствующей схемы сравнения, другие информационные выходы которых подключены соответственно к разрядным входам соответствующего реверсивного счетчика, первые информационные входы схем сравнения соединены с выходами первой группы регистров памяти и являются второй группой информационных выходов блока, выходы второй и тре.-ьей групп регистров памяти подключены соответственно к другим информационным входам-схем сравнения,при этом управляющие входы многоканального преобразователя анало -код, ключей, реверсивных счетчиков и второй и третьей групп регистров памяти являются соответственно со второго по седьмой управляющими входами блока, группа информационных входов многоканального .преобразователя аналог-код является группой информационных входов блока, управляющий выход многоканального преобразоват еля аналог-код соединен с управляющими входами схем сравнения, а информационные выходы - с входами первой группы регистров памяти. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР №596956, кл. G Об F 15/36, 1978. 2.Авторское свидетельство СССР N , кл. G Об F 15/36, 1976.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный статистический анализатор | 1980 |

|

SU955090A1 |

| Преобразователь сигналов с адаптивной дельта-модуляцией со слоговым компандированием в сигналы с нелинейной импульсно-кодовой модуляцией | 1990 |

|

SU1762411A1 |

| Устройство для моделирования случайных процессов | 1984 |

|

SU1223227A1 |

| Генератор случайных чисел | 1977 |

|

SU664185A1 |

| Устройство определения конца блока циклического кода | 1982 |

|

SU1061279A1 |

| Устройство для моделирования канала передачи дискретной информации | 1983 |

|

SU1088006A1 |

| Вероятностное устройство для решения уравнения Лапласа | 1983 |

|

SU1091172A1 |

| Генератор случайных чисел | 1979 |

|

SU798770A1 |

| Устройство для непрерывного экспресс-анализа потоков случайных чисел | 1983 |

|

SU1101839A1 |

| Статистический анализатор | 1983 |

|

SU1144120A1 |

./

г.г

h

г.г .

z

zo

/j

Ж, IE

17

гг

25

П

и

W

ь

- Ш)

/ W

(30}

f

15 f

2Ь

1-У

-У

23

У-

У-

2

г-/-

25У-

/.

ФигЛ

Авторы

Даты

1982-09-23—Публикация

1979-12-10—Подача