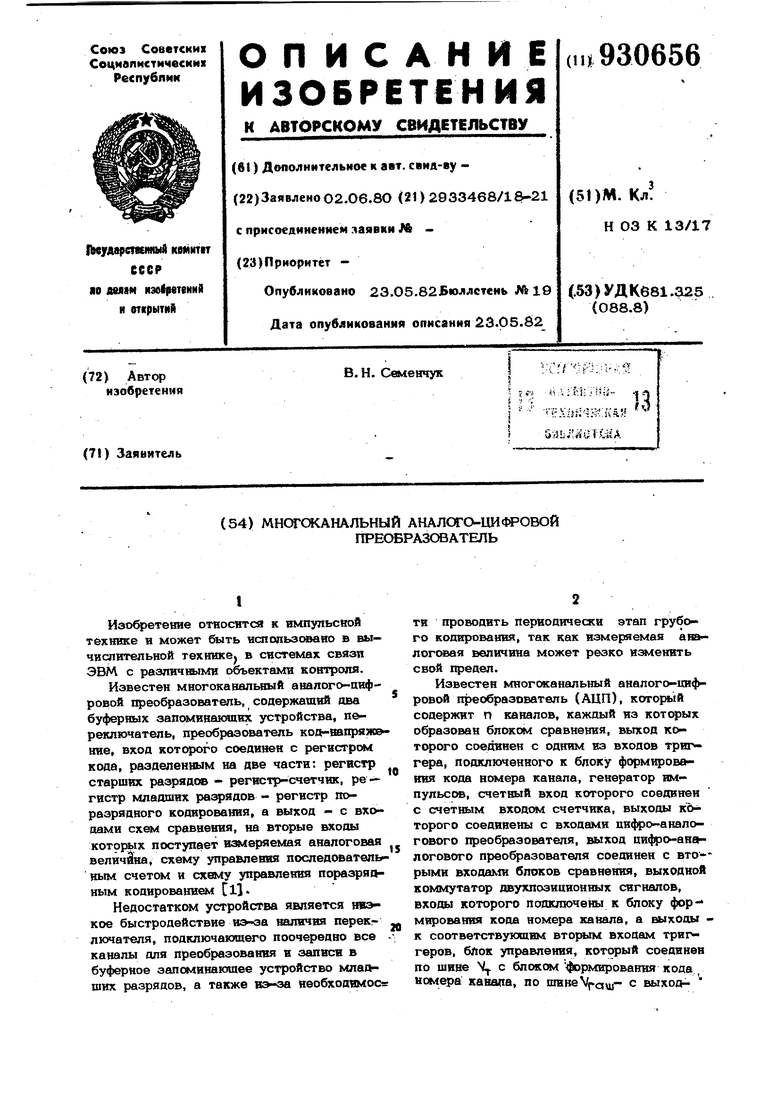

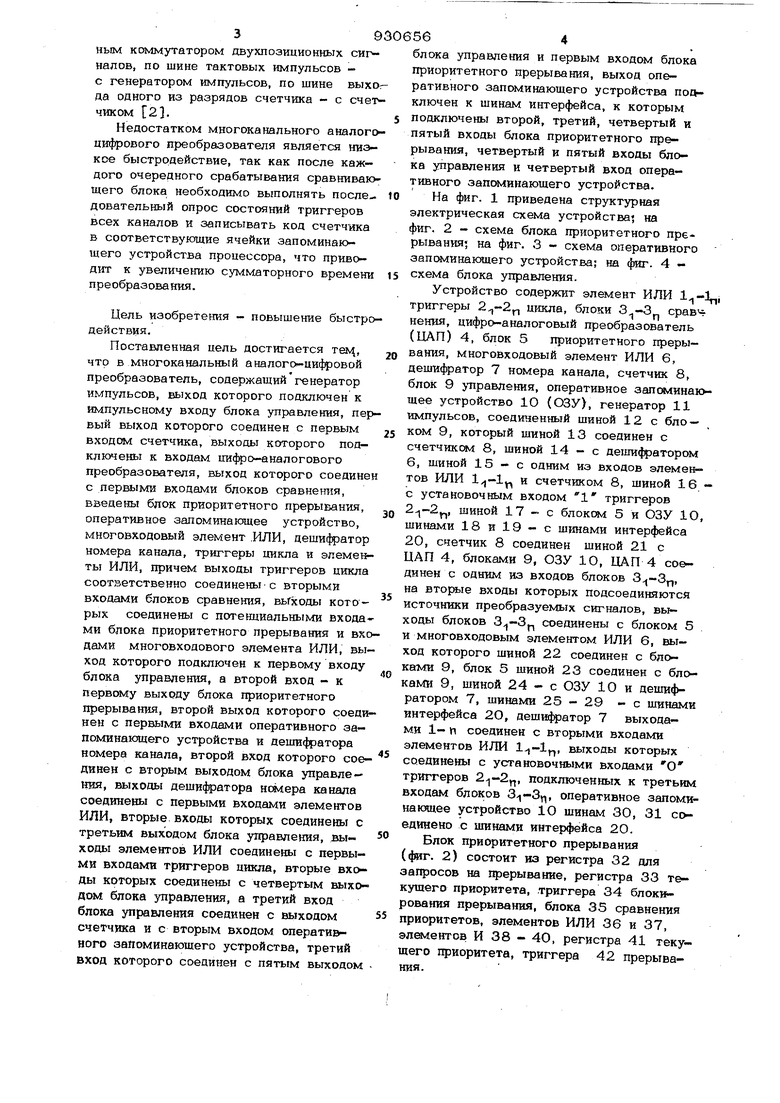

Изобретение относится к импульсной техшосе в может быть нспопьзсюано в вычислительной технике в системах связи ЭВМ с рвзличолми объектами контроля. Известен многоканальный аналого-цифровой преобразователь, содержащий два буферных запоминающих устройства, п&реключатель, преобразователь коо-есапряж ние, вход которого соединен с регистрсм кода, разоеленшлм на две части: регистр старших разрядов - регистр-счетчик, регистр младших - регистр поразрядного кодирования, а выход - с входами схем сравнения, на вторые входы KOTpfbix поступает и; еряемая аналоговая велич11на, схему управления последователь ным счетом и схему управления поразрядным кодированием Недостатком устройства является низкое быстродействие иэ-за наличия переключателя, подключающего поочередно все каналы для преобразования и записи в буферное запоминающее устройство млаоших разрядов, а также вэ-за необходимое ти проводить периодически этап грубого кодирования, так как измеряемая аналоговая величина может резко ия енить свой 1федел. Известен многоканальный аналого-цифровой преобразователь (АЦП), которь1й содержит п каналов, каждый из которых образован блоком сравнения, выход которого соединен с одним из входов триггера, подключенного к блоку формирования кода номера канала, генератор им- пульсе, счетный вход которого соединен с счетным входом счетчика, выходы которого соединены с входами цифро-аналогового преобразователя, выход цифро-анеелогового преобразователя соединен с вто- рыми входак{и блоков сравнения, выходной коммутатор двухпозиционных сигналов, входы которого подключены к блоку формирования кода номера канала, а выходы к соответствующим вторым входам триг геров, блок управления, который соединен по шине i с блоком формирования кода номера канала, по с шлхогьмым коммутатором двухпозиционных сиг налов, по шине тактовых импульсов с генератором импульсов, по шине выхо да одного из разрядов счетчика - с счет чиком 2. Недостатком многоканального аналого цифрового преобразователя является низкое быстродействие, так как после каждого очередного срабатывания сравнивак щего блока необходимо выполнять после-. довательный опрос состояний триггеров всех каналов и записывать код счетчика в соответствующие ячейки запоминающего устройства процессора, что приводит к увеличению сумматорного времени преобразования. Цель изобретения - повышение быстро действия. Поставленная цель достигается тец, что в многоканальный аналого-ци ОБой преобразователь, содержащий генератор импульсов, выход которого подключен к импульсному входу блока управления, пер вый выход которого соединен с первым вхоцом счетчика, выходы которого подключены к входам ци Ч о-аналогового преобразователя, выход которого соедине с первыми входами блоков сравнения, введены блок приоритетного прерывания, оперативное запоминающее устройство, многовходовый элемент .ИЛИ, аештифратор номера канала, триггеры цикла и элементы ИЛИ, причем выходы триггеров цикла соответственно соединены с вторыми входами блоков сравнения, выходы которых соединены с потенциальными входа ми блока приоритетного прерывания и вхо дами многовходового элемента ИЛИ, выход которого подключен к первому входу блока управления, а второй вход - к первому выходу блока приоритетного прерывания, второй выход которого соеди нен с первыми входами оперативного запоминающего устройства и дешифратора номера канала, второй вход которого соединен с вторым выходом блока управления, выходы дешифратора номера канала соединены с первыми входами элементов ИЛИ, вторые входы которых соединены с третьим выходом блока управления, выходы элементов ИЛИ соединены с первыми входами триггеров цикла, вторые входы которых соединены с четвертым выходом блока управления, а третий вход блока управления соединен с выходом счетчика и с вторым входом оперативного запоминающего устройства, третий вход которого соединен с пятым выходом блока управления и первым входом блока приоритетного прерывания, выход оперативного запоминающего устройства подключен к шинам интерфейса, к которым подключены второй, третий, четвертый и пятый входы блока приоритетного прерывания, четвертый и пятый входы блока управления и четвертый вход оперативного запоминающего устройства. На фиг. 1 приведена структурная электрическая схема устройства на фиг. 2 - схема блока приоритетного прерывания; на фиг. 3 - схема оперативного запсминающего устройства; на фиг. 4 - схема блока управления. Устройство содержит элемент ИЛИ триггеры цикла, блоки сравчнения, цифро-аналоговый преобразователь (ЦАП) 4, блок 5 приоритетного прерывания, многовходовый элемент ИЛИ 6, дешифратор 7 номера канала, счетчик 8, блок 9 управпе тя, оперативное запоминан щее устройство Ю (ОЗУ), генератор 11 импульсов, соединенный шиной 12 с блоком 9, который шиной 13 соединен с счетчиком 8, шиной 14 - с дешифратором 6, шиной 15 - с одним из входов элементов ИЛИ 1х)-1, и счетчиком 8, шиной 16 с установочным входом I триггеров 2-,-2, шиной 17 - с блoк(Лv 5 и ОЗУ 1О, шинами 18 и 19 - с шинами интерфейса 20, счетчик 8 соединен шиной 21 с ЦАП 4, блоками 9, ОЗУ 1О, ЦАП 4 соединен с одним на входов блоков , на BTOfftie входы которых подсоединяются источники преобразуемых сигналов, вътходы блоков соединены с блоком 5 и многовходовым элементом ИЛИ 6, выход которого шиной 22 соединен с блоками 9, блок 5 шиной 23 соединен с блоками 9, шиной 24 - с ОЗУ 10 и дешифратором 7, шинами 25-29 - с шинами интерфейса 2О, аеш фратор 7 выходами 1- и соединен с вторыми входами элементов ИЛИ , выходы которых соединены с установочными входами О триггеров , подключенных к третьим входам блоков , оперативное запоминающее устройство 1О шинам 30, 31 соединено с шинами интерфейса 20. Блок приоритетного прерывания («}иг. 2) состоит из регистра 32 для запросов на прерывание, регистра 33 текущего приоритета, .триггера 34 блокирования прерывания, блока 35 сравнения приоритетов, элементов ИЛИ 36 и 37, элементов И 38 - 40, регистра 41 текущего приоритета, триггера 42 прерывания.

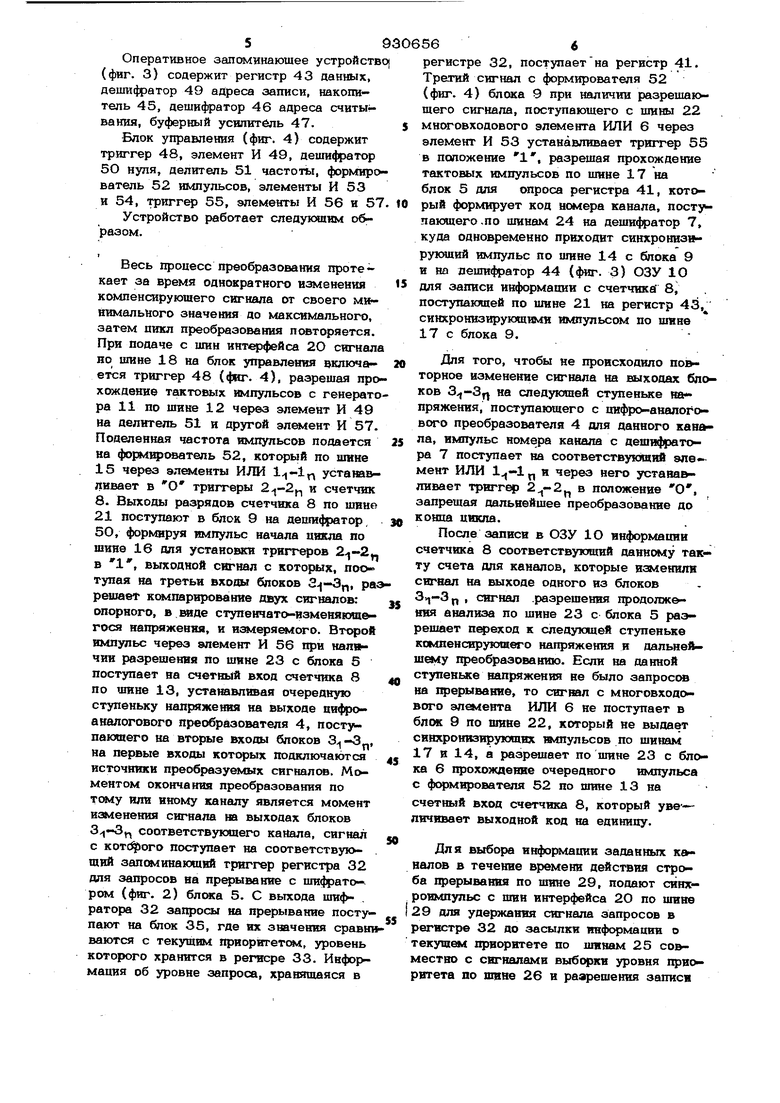

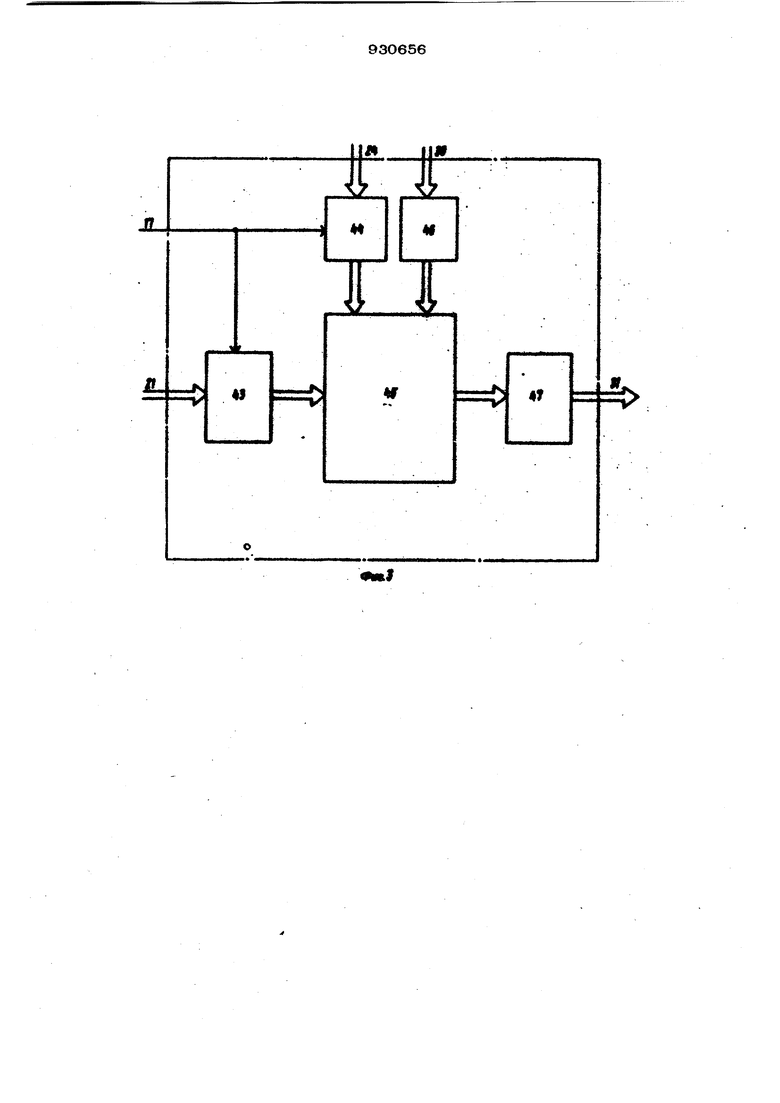

OneparviBHoe запоминающее устройство (фиг. 3) содержит регистр 43 данных, дешифратор 49 адреса записи, накопитель 45, дешифратор 46 адреса считы;вания, буферный усилитель 47.

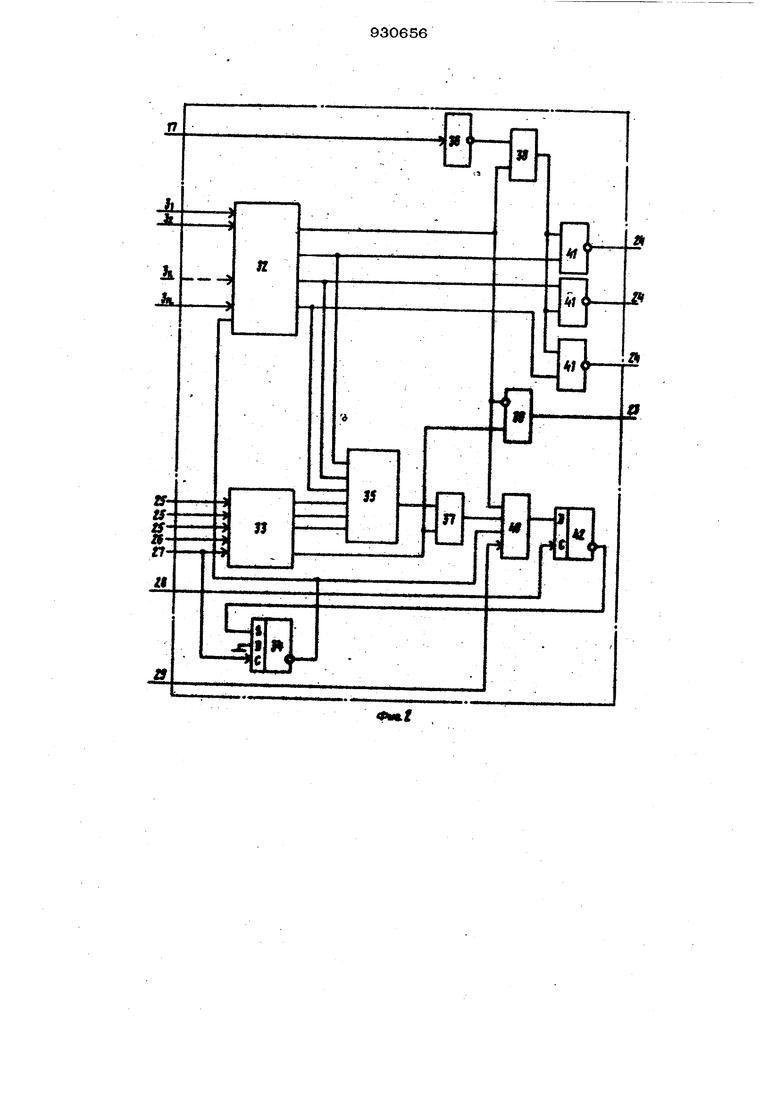

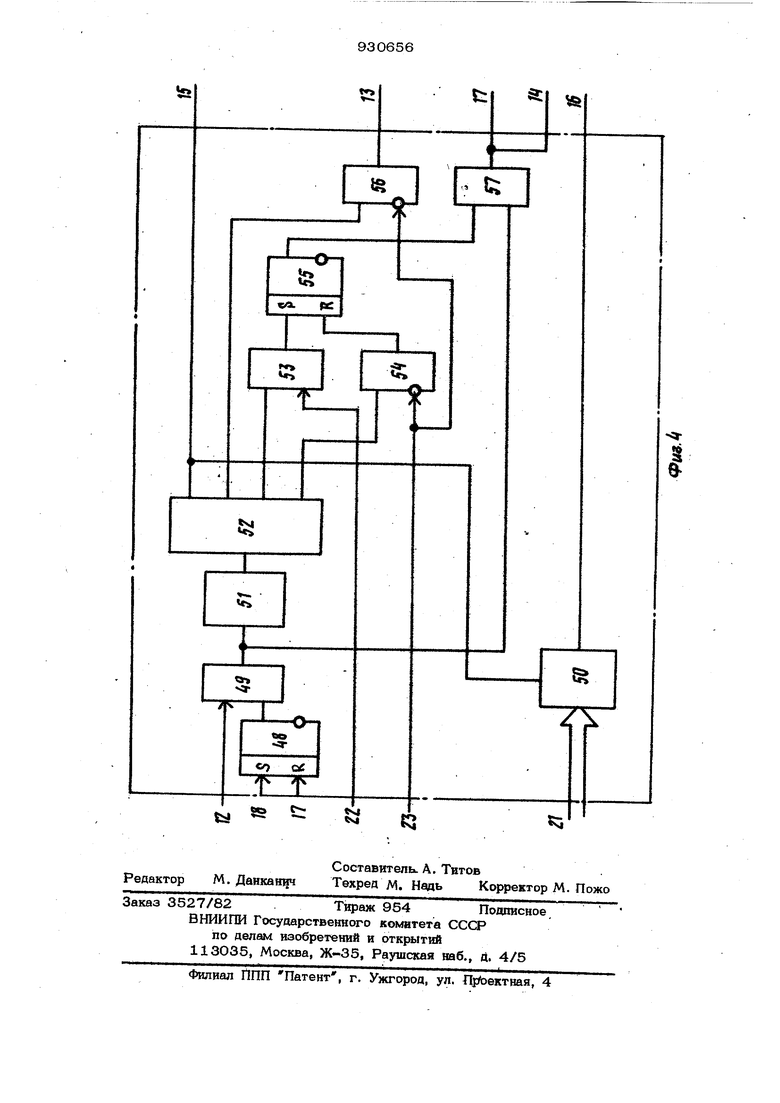

Блок управления (фиг. 4) содержит триггер 48, элемент И 49, дешифратор 5О нуля, делитель 51 частоты, формирователь 52 импульсов, элементы И 53 и 54, триггер 55, элементы И 56 и 57

Устройство работает следующим образом.

I

Весь процесс преобразования протекает за время однократного изменения компенсирующего сигнала от своего минимального значения до максимального, затем пшсл преобразования повторяется. При подаче с шин инт зфейса 2О сигнала но шине 18 на блок управления включается триггер 48 (фиг. 4), разрешая прохождение тактовых импульсов с генератора 11 по шине 12 через элемент И 49 на делитель 51 и другой (ент И 57. Поделенная частота импульсов подается на форм ователь 52, который по шине 15 через элементы ИЛИ г устат&ливает в О триггеры и счетчше 8. Выходы разрядов счетчика 8 по шине 21 поступают в блок 9 на дешифратор, 50, формируя импульс начала цикла по шине 16 для установки триггеров в , выходной сигнал с которых, поступая на третьи входы блоков , раэреиюет кс {парирование двух сигналов: опорного, в виде ступенчато-изменяюшегося напряжения, и измеряемого. Второй импульс через элемент И 56 при разрешения по шине 23 с блока 5 поступает на счетный вход счетчика 8 по шине 13, устанавливая очередную ступеньку напряжения на выходе цифроаналогового преобразователя 4, посту пающего на вторые входы блоков , на первые входы которых подключаются источники преобразуемых сигналов. Моментом окончания преобразования по тому или иному каналу является момент изменения сигнала на выходах блоков , соответствующего канала, сигнал с которого поступает на соответствуют щий запоминающий триггер регистра 32 для запросов на прерывание с шифратором (фиг. 2) блсжа 5. С выхода , ратора 32 запросы на прерывание поступают на блок 35, где их значения сравниваются с текущим приоритете, уровень которого хранится в регисре 33. Инфо{ маиия об уровне запроса, хранящаяся в

регистре 32, поступает на регистр 41. Третий сигнал с формирователя 52 (фиг. 4) блока 9 при наличии разрешающего сигнала, поступающего с шины 22 мнмовходового элемента ИЛИ 6 через элемент И 53 устанавливает триггер 55 в положение , разрешая прохождение Т61КТОВЫХ импульсов по шине 17 на блок 5 для опроса регистра 41, который формирует код номера канала, посту паютаего.по шинам 24 на дешифратор 7, куда одновременно приходит синхрониз руюший импульс по шине 14 с блока 9 и на дешифратор 44 (фиг. 3) ОЗУ 10 для записи информации с счетчике 8, поступающей по шине 21 va регистр 43, синхронизирующими импульсом по шине 17 с блока 9.

Для того, чтобы не происходило по&торное изменение сигнала на выходах блоков на следующей ступенысе напряжения, поступающего с цифро-аналого всчо преобразователя 4 для данного канала, импульс номера канала с дешифратора 7 поступает на соответствунявий элемент ИЛИ „ и через него устанавливает триггер в положение О, запрешбл дальнейшее преобразование до конца цикла.

После записи в ОЗУ 1О информации счетчика 8 соответствующий данному такту счета для каналов, которые изменили сигнал на выходе одного из блоков (, , сигнал .разрешения продолжения анализа по шине 23 с блока 5 разрешает переход к следующей ступеньке компенсируюшего напряжения и дальнейшему преобразованию. Если на данной ступеньке напряжения не было запросе на щэерывание, то сигнал с многовходового элемента ИЛИ 6 не поступает в бЛ1Ж 9 по шине 22, который не выдает синхронизирующих импульсов по шинам 17 и 14, а разрешает по шине 23 с блока 6 прохождение очередного импульса с фсфмирователя 52 по шине 13 на

счетный вход счетчика 8, который уве-- личивает выходной код на единицу.

Для выбора информации заданных кенналов в течение времени действия строба прерывания по шине 29, подают синхроимпульс с шин интерфейса 2О по шине I 29 для удержания сигнала запросов в регистре 32 до засылки информации о текуш ъ приоритете по цшнам 25 со местно с сигналами выборки уровня приоритета по отне 26 и разрешения записи по шине 27. Информация данного канала записанная в оперативное запоминающее устройство 10 по сигналу, подаваеки му по шине 17, считывается по адресу на lUHHax 30 и передается по шинам 31 через шины интерфейса 20 на входные инфс мационные шины npoueccqpa ЭВМ. Конец преобразования наступает по си налу, поступающему с шин интерфейса 20 по шине 19 на триггер 48 блока 9. Таким o6pa3c vt, отпадает необходи мость опрашивать все каналы на данном такте счета, а только те, которые кам.ннли сигнал на выходе блока сравнения и появляется возможность контроля и мерения только определенной группы каналов в зависимости от приоритета и возможность обращения ЭВМ к оперативному запоминающему устройству в любое для считывания информации по любой группе каналов. Формула изобретения 1 Многоканальный аналого-цифровой пре образователь, содержащий генератор им пульсов, выход которого подключен к им пульсному входу блсжа управления, пер вый выход котсфого соединен с первым входсил счетчика, вьпсоды которого поск ключены к входам цифро-аналогового преобразователя, выход которого соединен с первыми входами блоков сравнения отличающийся тем, что, с целью повышения быстродействия, введены блоки приоритетного прерывания, мвоговходовой элемент ИЛИ, операти йое запоминаюшее устройство, дешифратор номера канала, триггеры цикла и менть) ИЛИ, причен выходы триггеров цикла соответственно соединены с вторыми входами блоков сравнения, выходы которых соединены с потенциальными входами- блока приоритетного прерывания и входами многовходового элемента ИЛИ, выход которого подключен к первому входу блока управления, а второй вход к первому выходу блока приоритетного прерывания, второй выход которого соединен с первыми входами оперативного запоминающего устройства и дешифратора номера канала, второй вход которого соединен с вторым выходом блока ynpai ления, выходы дешифратора номера канала соединены с первыми входами элементов ИЛИ, вторые входы которых соединены с третьим выходом блока управления, выходы элементов ИЛИ соединены с первыми входами триггеров цикла, вторые входы соединены с четвертым выходом блока управления, . третий вход блока управления соединен с выходом счетчика и с вторым входом оперативного .запоминающего устройства, третий вход которого соединен с пятым выходом блока управления и первым входом блока присфитетного прерывания, выход оперативного запоминающего устройства подключен к шинам интерфейса, к которым подключены второй, третий, четвертый и пятый входы блока приоритетного преры-вания, четвертый и пятый входы блока управления, и четвертый вход оперативного запоминающего устройства. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 229О57, кл. Н ОЗ К 13/17, 1967. 2.Каган Б.М. Воителев А. И., Лукьянов Л.М. Системы связи УВМ с объектами управления в АСУ ТП. М., Советское радио. 1978, с. 166, рис. 4.25 (прототип).

4f

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство внешних каналов | 1988 |

|

SU1695313A1 |

| МУЛЬТИПЛЕКСОР ТЕЛЕКОММУНИКАЦИОННЫЙ МНОГОФУНКЦИОНАЛЬНЫЙ | 2004 |

|

RU2269154C1 |

| РЕГИСТРАТОР ПАРАМЕТРОВ АВАРИЙНЫХ СИТУАЦИЙ В ЭЛЕКТРИЧЕСКИХ СЕТЯХ ПОВЫШЕННОЙ ТОЧНОСТИ (ВАРИАНТЫ) | 2008 |

|

RU2376625C1 |

| Устройство для сигнализации | 1986 |

|

SU1481824A1 |

| Ультразвуковой уровнемер | 1992 |

|

SU1838765A3 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Мультиплексный канал | 1977 |

|

SU656048A1 |

| УСТРОЙСТВО КОНТРОЛЯ ПРОЧНОСТИ КРЫЛА ВОЗДУШНОГО СУДНА | 2011 |

|

RU2469289C1 |

| Измеритель частоты | 1989 |

|

SU1691768A1 |

| Устройство для сопряжения цифровой вычислительной машины с линиями связи | 1983 |

|

SU1166123A1 |

«I

4Г

Авторы

Даты

1982-05-23—Публикация

1980-06-02—Подача