3961

жит триггер, вход которого подключен к выходу элемента ИЛИ предыдущего канала деления, вход резервного триггера подключен к выходу элемента ИЛИ последнего канала деления, а выходы через избирательный каскад к выходам триггера последнего канала деления, а каждый канал деления состоит из дифференцирующих цепей, дополнительного элемента ИЛИ и элемента ИЛИ-НЕ, при этом в каждом- канале деления выход дополнительного

элемента ИЛИ через первую дифференцирующую цепь подключен к одному из входов элемента ИЛИ, выход элемента

ИЛИ-НЕ через вторую дифференцирующую цепь - к второму входу элемента ИЛИ, прямой выход триггера соединен с первым входом дополнительного элемента ИЛИ своего канала деления и с вторым входом дополнительного элемена ИЛИ последующего канала деления, а инверсный выход - с первым входом элемента ИЛИ-НЕ своего канала деления и с вторым входом элемента ИЛИНЕ другого канала деления, первый дополнительный вход дополнительного элемента ИЛИ всех каналов деления, кроме первого, соединен с перрой входной шиной, а остальные дополнительные входы дополнительного элемента ИЛИ в каналах деления, начиная с третьего, - с прямыми выходами триггеров всех предыдущих каналов деления, первый дополнительный вход элемента ИЛИ-НЕ всех каналов деления, кроме первого, соединен с второй входной шиной, а остальные дополнительные входы элемента ИЛИ-НЕ в каналах деления, начиная с третьего, с инверсными выходами триггеров всех| предыдущих каналов деления, при этом выходы триггера предпоследнего канала деления подключены к дополнительным входам избирательного каскада,

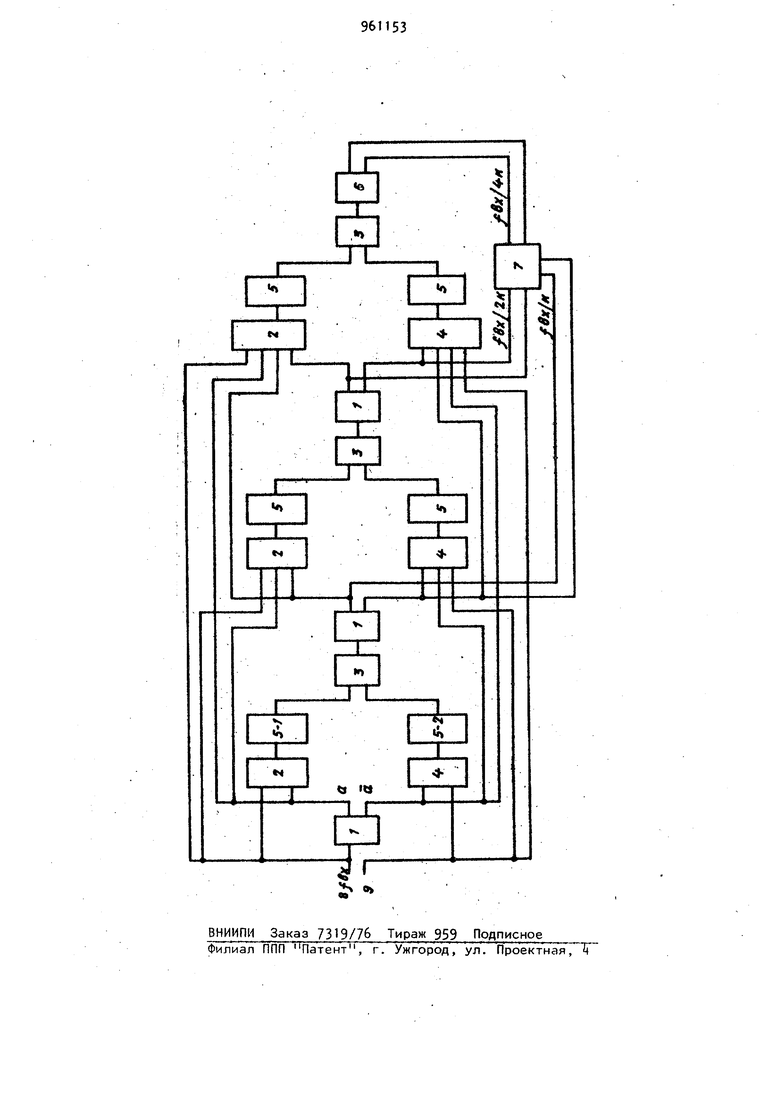

На чертеже представлена структурая схема резервированного триггерого делителя частоты для случая вукратного резервирования.

Устройство в каждом канале деления одержит триггер 1, элемементы ИЛИ 2 и 3. элемент ИЛИ-НЕ k, дифференирующие цепи 5-1 и , а также содержит резервный триггер 6, избирательный каскад 7, первую входную ину 8, на которую подается прямая импульсная последовательность, и вторую входную шину 9. на которую пода34

ется инвертированная импульсная последовательность.

Устройство работает следующим образом.

Прямой сигнал с каждого триггера 1 поступает одновременно на один из входов элемента ИЛИ 2 собственного канала деления и на один из входов всех элементов ИЛИ 2 последующих каналов деления. Инверсный сигнал с каждого триггера 1 поступает одновременно на один из входов элемента ИЛИ-НЕ k собственного канала деления и на один из входов всех элементов

ИЛИ-НЕ последующих каналов деления, Выходные импульсы элементов ИЛИ 2 и ИЛИ-НЕ 4 поступают на дифференцирующие цепи соответственно 5-1 и и далее на элемент ИЛИ 3, на выходе

которого формируются узкие импульсы, запускающие последующий триггер 1 или 6, На вход избирательного каскада 7, который выделяет сигнал требуемой частоты, поступают сигналы с триггера

1 предпоследнего канала деления

1 Вх / - триггера 1 последнего канала деления f и с резервного триггера 6 f fg,, где К - коэффициент деления,

Пусть одновременно триггеры 1 в первом и втором каналах деления остановились в положении Q . 1, Тогда на выходе элементов ИЛИ 2 обоих каналов деления присутствует сигнал логической единицы, а на выходе элемента

ИЛИ-НЕ 4 присутствуют импульсы входной частоты, и делитель в целом продолжает функционировать нормально, . так как на выходе резервного триггера 6, нагруженного на избирательный каскад 7 присутствуют импульсы требуемой частоты fex/l - Если триггеры 1 в первом и втором каналах деления одновременно остановились в положении Q О, сигнал логической единицы будет на выходах элементов ИЛИ-НЕ в обоих каналах деления, на выходе элемента ИЛИ 2 второго канала деления будут присутствовать импульсы входной частоты и делитель в целом

продолжает функционировать нормально, так как на выходе резервного триггера 6 присутствуют импульсы требуемой частоты ..

Одновременный отказ двух любых

элементов в соседних каналах деления также не приводит к каким-либо сбоям и переходным процессам в рассматриваемом делителе частоты. Это достигается тем, что в каждом канале деления прямой выход триггера 1 соединен не только с одним из входов элемента ИЛИ 2 собственного и следу щего каналов деления, но и с одним из входов элемента ИЛИ 2 всех после дующих каналов деления, а инверсный выход триггера соединен не только с одним из входов элемента ИЛИ-НЕ k собственного и следующего каналов, но и с одним из входов элемента ИЛИ НЕ k всех последующих каналов деления. Характерной особенностью устройства является то, что повышение надежности делителя достигается без дополнительных аппаратурных затрат. Формула изобретения Резервированный триггерный делитель частоты по ав. св. № , отличающийся тем, что. 36 с целью повышения надежности работы, первый дополнительный вход дополнительного элемента ИЛИ всех каналов деления, кроме первого, соединен с первой входной шиной, а остальные дополнительные входы дополнительного элемента ИЛИ в каналах деления, начиная с третьего, - с прямыми выходами триггеров всех предыдущих каналов деления, первый дополнительный вход элемента ИЛИ-НЕ всех каналов деления, кроме первого, соединен с второй входной, шиной, а остальные дополнительные входы элементов ИЛИ-НЕ в каналах деления, начиная с третьего с инверсными выходами триггеров всех предыдущих каналов деления, при этом выходы триггера предпоследнего канала деления подключены к дополнительным входам избирательного каскада. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 7507 3, кл: Н 03 К 23/02, 1977.

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированный триггерный делитель частоты | 1977 |

|

SU750743A1 |

| РЕЗЕРВИРОВАННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 2022 |

|

RU2785274C1 |

| Резервированный делитель частоты | 1990 |

|

SU1780187A1 |

| Устройство для контроля резервированного генератора | 1980 |

|

SU892740A2 |

| Резервированный делитель частоты | 1983 |

|

SU1163473A1 |

| Дублированный счетчик импульсов | 1981 |

|

SU984090A1 |

| Резервированный делитель частоты | 1983 |

|

SU1109910A1 |

| Резервированный делитель частоты | 1985 |

|

SU1330756A1 |

| Резервированное многоканальное устройство для формирования тактовых импульсов | 1978 |

|

SU767764A1 |

| Резервированный делитель частоты следования импульсов | 1981 |

|

SU953744A1 |

Авторы

Даты

1982-09-23—Публикация

1980-11-11—Подача