(54) МНОГОКАНАЛЬНОЕ УСТРОЙСТВО СВЯЗИ ДЛЯ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство связи для вычислительной системы | 1983 |

|

SU1101809A2 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Устройство для обмена | 1980 |

|

SU907539A1 |

| Многоканальное устройство для сопряжения абонентов с цифровой вычислительной машиной | 1986 |

|

SU1310831A2 |

| Устройство для сопряжения | 1980 |

|

SU926645A2 |

| Устройство для обмена информацией | 1983 |

|

SU1142824A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1985 |

|

SU1305698A1 |

| Устройство для обмена информацией между ЦВМ и внешними устройствами | 1980 |

|

SU907537A1 |

| Устройство для сопряжения ЦВМ с внешними устройствами | 1989 |

|

SU1784840A1 |

| Устройство для сопряжения | 1978 |

|

SU742920A1 |

Устройство относится к вычислительнай технике и может быть исполь зовано для связи нескольких вычислительных машин, образующих систему кольцевой структуры.

Известно устройство связи, содержащее элементы И, ИЛИ, формиррвате-. ли импульсов,; триггер и регистр и выполняющее функции сопряжения ЦВМ с внешними устройствами, например, с другими ЦВМ fl .

Недостатком указанного устройства является ниэгкое быстродействие, обус-. ловленное тем, что переключение триггеров осуществляется посредством формирователя, длительность импульса которого должна выбираться, асходя из худших сочетаний параметров элементов и паразитных задержек . ;

Наиболее близким к предлагаемому по технической сущности и достигаемому эффекту является устройство связи для вычислительной системы, содержащей два элемента ЗАПРЕТ, два триггера, два регистра, два элемента И и два элемента ИЛИ 2 .

. Недостатком известного устройства является низкое быстродействие, обусловленное тем, что ограничения на

длительность сигналов установки триггеров в единичное и нулевое состояния должны выполняться для худших сочетаний параметров элементов и паразитных задержек.

Цель изобретения - повышение быстродействия.

Поставленная цель достигается тем, что в многоканальное устройство связи

10 для вычислительной системы, содержащее в каждом канале два подканала, каждый из которых содержит триггер, элемент ЗАПРЕТ, регистр, два элемента И, два элемента ИЛИ, причем

15 выход элемента ЗАПРЕТ подканала соединен с первым входом первого элемента И подканала и с первым управляющим входом регистра подканала, выход первого элемента И подканала

20 соединен с единичным входом триггера подканала, первый режимный вход подканала и выход второго элемента И подканала соединены с входами первого элемента ИЛИ подканала, второй ре25жимный вход подканала соединен с первым входом второго элемента И подканала, прямой выход триггера одного подканала соединен с вторым входом второго элемента И другого

30 подканала, выход регистра первого

подкар ала соединен с первым информационным--входом регистра второго подканала, прямой выход.триггера подканала соединен с управляющим выходом подканала, установочный вход подканала соединен с первьм входом второго элемента ИЛИ подканала, вы(ход регистра подканала сое цинен с информационным выходом подканала, вторые информационный и управляющий входы регистра второго подканала соединены соответственно с кодовьгм входом и входом разрешения приема канала, выход первого элемента ИЛИ второго подканала соединен с информационным входом элемента ЗАПРЕТ второ го подканала канала, прямой.выход триггера второго подканала канала соединен с информационным входом элемента ЗАПРЕТ первого подканала последукнцего канала, выход регистра второго подканала канала соединен с информационным входом регистра первого подканала последующего ка- . нала, в каждый подканал введены третий, четвертый элементы И, третий элемент ИЛИ и блок формирования признака состояния, причем выход триггера подканала соединен с первыми входами третьего элемента И подканала и третьего элемента ИЛИ подканала, выход четвертого элемента И подканала соединен с вторыми входами второго и третьего элементов ИЛИ подканала, выход второго элемента ИЛИ подканала соединен с вторым входом третьего элемента Иподканала, выход третьего элемента И подканала соединен с н шевым входом триггера подканала, установочный вход С подканала соединен,с третьим, входом третьего элемента ИЛИ подканала, выход третьего элемента ИЛИ подканала соединен с управляющим входом элемета ЗАПРЕТ подканала,первый и вторрй выходы блока формирования признака- состояния подканала соединены соответственно с вторым входом первого элемента И подканала и с первым входом четвертого элемента И подканала, вход блока формирования признака состояния подканала соединен с выходом регистра подканала, .выход первого элемента ИЛИ первого подканала соединен с вторым входом чeт вертого элемента И первого подканала и с вторым управляющим входом регист pa первого цодканала, второй вход чевертого элемента И второго подканала канала и третий управляющий вход регистра второго подканала канала соединены с прямым выходом триггера первого подканала следующего канала.

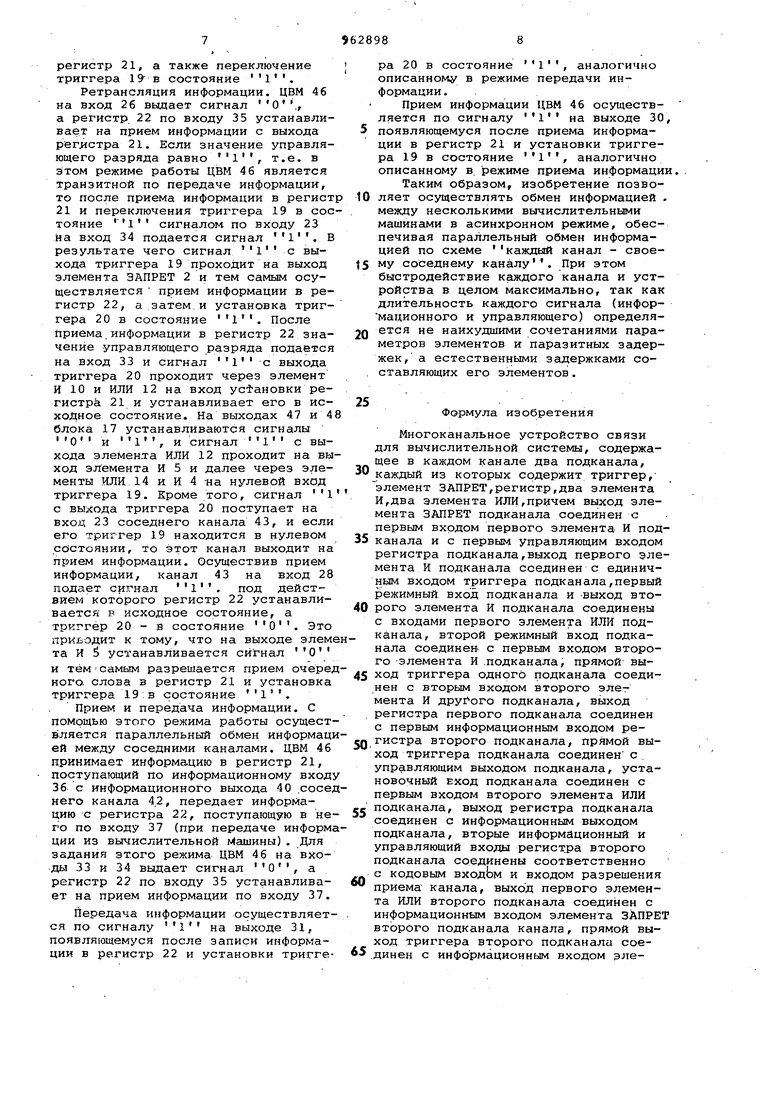

На чертеже представлена структурная схема устройстваi

Устройство содержит в каждом к пГнале элементы ЗАПРЕТ 1 и 2 , элементы И 310, элементы ИЛИ 11-16, блоки 17

к 18 формирования признака состояния триггеры 19 и 20, регистры 21 и 22, инфррмационный вход 23 элемента ЗАПРЕТ первого-подканала, первый режимный вход 24 первого подканала, установочными вход 25 первого подканала первый режимный вход 26 второго подканала, установочный вход

27 второго подканала, третий управляющий вход 28 регистра второго подканала, выход 29 триггера первого подканала, управляющий выход 30 первого подканала, выход 31 триггера второго подканала, управляющий ыход 32 второго подканала, второй режимный вход 33. первого подканала,

iвторой режимный вход 34 второго подканала, вход 35 разрешения приема канала, инфор1у1ационный вход 36 регистра первого подканала, информационный вход 37 канала, информаци|онный выход 38 первого подканала,ин фЪрмационный выход39 второго подканала, информационный выход 40 регистра второго подканала, на чертеже показаны каналы 41-43 устройства, первый 44 и второй 45 подканалы соответственно, ЦВМ 46, первый 47 и 48 и второй 49 и 50 выходы блоков формирования признака состояния первого и второго подканалов соответственно. Каждый из блоков 17 и 18 реализу.ет следующие функции:

)

а-ь.,

(2)

где 2: к Z.- выходные двоичные

переменные соответственно на первом (47 и 49) и втором (48 и 50) выходах блоков 17 и 18;

а. и Ь - входные двоичные переменные;

И, .- разрядно-сть слова. Значения сигналов а. и используются следующим образом.

.Если a.j 1 и , то это означает, что 1-й элемент памяти (i 1, п регистра 21 (22) находится в состоя0; Ь,1, то

а если а.:

нии

i-й элемент памяти находится в состоянии О . При значениях сигналов а: 0.; Ь 0 1-й элемент памяти находится в.исходном состоянии. Установк элементов памяти регистра 21 в исходное состояние осуществляется выходным сигналом элемента ИЛИ 12, а установка регистра 22 в исходное состояние осуществляется по входу 28. Из выражений (1) и (2) следует, что если, регистр находится в исходном состоянии, то , а если в-регистр записана информации, то zJ| 1 и Z7.b. Устройство работает следующим об разом. Передача информации. ЦВМ 46 является передающей. На вхоД 34 ЦВМ выдает сигнал О, на вход 26 сигнал , а по входу 35 устанавливает регистр 22 на прием-;.. информации с информационного входа 37. Перед началом работы триггеры 19 и 20 всех устройств связи устанавливаются в нулевое состояние сиг налами по входу 25 и 27. На выходе элемента ЗАПРЕТ 2 после подачи сиг-: нала на вход 26 устанавливается сигнал , под действием которого осуществляется запись информации в регистр 22. После приема информации в регистр 22 на выходах 49 и 50 блока 18 устанавливаются соответственно сигналы а триггер 20 переключается в состоя ние Ч выходным сигналом элемента И 6. Сигнал с выхода триггера 20 поступает.на выход 32 и ЦВМ 46 устанавливает сигнал О на входе 26. Кроме того, сигнал выхода 31 поступает на вход 23 кана ла 43 и, если триггер 19 этого канала находится в состояние О, то этот канаА выходит на прием информации. После записи информации в регистр 21 канал 43 выдает на управляющий вход 28 сигнал , под действием которого осуществляется установка элементов памяти регистра 22 в исходное состояние. На выхо дах 49 и 50 блока 18 устанавливаютО и ся соответственно сигналы с входа 28 пр , и сигнал ходит на выход элемента И 8 и далее на выход элемента И 7. и переключает триггер 20 в состояние . После установки триггера 20 в О блокируется прохождение сигнала Ч на нулевой вход этого триггера. На выходе 32 устанавливается сигнал О для ЦВМ 46 и возможности передачи в регистр 22 очередного слова. По сигналу О на входе 32 ЦВМ 46 выдает на вход 26 сигнал Ч, а на вход 37 - оче редное слово, которое будет записано в регистр 22 тогда, когда на вхо де 28 установится сигнал О. Пока на входе 28 имеется сигнал Ч запрещается прохождение сигнала Ч с входа 26 на выход элемента ЗАПРЕТ 2, так как сигнал Ч с входа 28 поступает через элементы И 8 и ИЛИ 15 на управляющий вход элемента ЗАПРЕТ 2. По сигналу О на входе осуществляется прием очередного сло ва э регистр 22, после чего блок 18 разрешает прохождение сигнала Ч с выхода элемента запрета 2 на выход элемента И 6 и триггер 20 устанавливается в состояние Ч.. После переключения триггера 20 в i« блокируется прохождение сигнала 1 на единичный вход этого триггера ... Прием информации. По сигналу Ч с выхода элемента ЗАПРЕТ 1, появляющемуся при подаче на вход 23 сигнала Ч (предполагается, что триггер 19 находится в состоянии О, а на выходе элемента И 5 и на входе 25 имеются сигналы о) осуществляется прием информации в регистр 21. После записи, информации в регистр 21 блок 17 выраб.атывает на выходах 47 и 48 сигналы Ч и О, и сигнал Ч с выхода элемента ЗАПРЕТ 1 проходит через элемент И 3 на единичный вход триггера 19. Сигнал,, Ч с выхода триггера 19 поступает на вход 3Q и запускает ЦВМ 46 на прием ин-г формации по выходу 38 регистра 21. Кроме того, сигнал Ч с выхода 29 поступает на вход 28 соседнего канала 42 и устанавливает регистр 22 в исходное-состояние. Сигнал Ч с выхода триггера 19 поступает также на управлякиций вход элемента ЗАПРЕТ, в результате чего блокируется прохождение сигнала Ч на единичный вход триггера 19. Один из разрядов информационного слова (управляющий разряд) служит для задания режима работы канала устройства. Если значение эт.ого разряда рав.но 1, то канал-, после приема информаЦии в регистр 21 переключается на ретрансляцию информации. Для этого на вход 34 подается сигнал Ч, а на вход 26 - сигнал О, причем регистр 22 по входу 35 устанавливается на прием информации с выхода регистра 21. Если значение управляющего разряда равно О, то и на вход 34 выдается сигнал О, а регистр 22 устанавливается на. прием информации по входу 37. Пусть значение управлякнцего разряда равно О, тогда после переключения триггера 19 в состояние . сигналом по входу 23 и приема инфррмации в регистр 21 осуществляется запись содержимого регистра 21 в ЦВМ 46, которая после приема инфорна вход 24, мации выдает сигнал под действием которого регистр 21 устанавливается в исходное состояние, и на выходах 4.7 и 48 блока 17 устанавливаются сигна ш О и Ч , в результате чего сигнал Ч с входа 24 проходит через элементы И 5, ИЛИ 14,и. И 4 на нулевой вход триггера 19 и переключает его в состояние О. По сигналу О на выходе 30 ЦВМ 46 устанавливает сигнал О на входе 24 и тем самым разрешает прием очередного слова в регистр 21, а также переключение триггера 19 в состояние . Ретрансляция информации. ЦВМ 46 на вход 26 выдает сигнал О,, а регистр 22 по входу 35 устанавливает на прием информации с выхода регястра 21. Если значение управляющего разряда равно 1, т.е. в этом режиме работы ЦВМ 46 является транзитной по передаче информации, то после приема информации в регист 21 и переключения триггера 19 в сое сигналом по входу 23 тояние на вход 34 подается сигнал 1 с вырезультате чего сигнал хода триггера 19 проходит на выход элемента ЗАПРЕТ 2 и тем самым осуществляется прием информации в регистр 22, а затем и установка триггера 20 в состояние . После Приема.информации в регистр 22 значение управляющего разряда подается на вход 33 и сигнал i с выхода триггера 20 проходит через элемент И 10 и ИЛИ 12 на вход установки регистра 21 и устанавливает его в исходное состояние. На выходах 47 и 4 блока 17 устанавливаются сигналы О и 1 , и сигнал 1 с выхода элемента ИЛИ 12 проходит на вы ход элемента И 5 и далее через элементы ИЛИ 14 и И 4 -на нулевой вход триггера 19. Кроме того, сигнал с выхода триггера 20 поступает на вход 23 соседнего канала 43, и если его триггер 19 находится в нулевом состоянии, то этот канал выходит на прием информации. Осуществив приём информации, канал 43 на вход 28 под дейстподает сигнал вием которого регистр 22 устанавливается в исходное состояние, а триггер 20 в состояние О. Это приводит к тому, что на выходе элем та И S устанавливается сигнал О и темсамым разрешается прием очеред ного, слова в регистр 21 и установка триггера 19 в состояние . Прием и передача информации. С помощью этого режима работы осущест вляется параллельньлй обмен информац ей между соседними каналами. ЦВМ 46 принимает информацию в регистр 21, поступающий по информационному вход 36 с информационного выхода 40 .сосе него канала 42, передает информацию с регистра 22, поступающую в не го по входу 37 (при передаче информ ции из вычислительной Машины). Для задания этого режима ЦВМ 46 на входы 33 и 34 выдает сигнал О, а регистр 22 по входу 35 устанавливает на прием информации по входу 37. Передача информации осуществляет ся по сигналу i на выходе 31, появляющемуся после записи информации в регистр 22 и установки тригге ра 20 в состояние Ч, аналогично описанному в режиме передачи информации. Прием информации ЦВМ 46 осуществляется по сигналу на выходе 30, появляющемуся после приема информации в регистр 21 и установки триггера 19 в состояние , аналогично описанному в. режиме приема информации. Таким образом, изобретение позволяет осуществлять обмен информацией . между несколькими вычислительными машинами в асинхронном режиме, обеспечивая параллельный обмен информацией по схеме каждый канал - своему соседнему каналу . При этом быстродействие каждого канала и устройства в целом максимально, так как длительность каждого сигнала (информационного и управляющего) определяется не наихудшими сочетаниями параметров элементов и паразитных задержек, а естественными задержками составляющих его элементов. Формула изобретения Многоканальное устройство связи для вычислительной системы, содержащее в каждом канале два подканала, каждый из которых содержит триггер,элемент ЗАПРЕТ,регистр,два элемента И,два элемента ИЛИ,причем выход элемента ЗАПРЕТ подканала соединен с первьом входом первого элемента И подканала и с первым управляющим входом регистра подканала,выход первого элемента И подканала соединен с единичным входом триггера подканала,первый режимный вход подканала и выход второго элемента И подканала соединены с входами первого элемента ИЛИ подканала, второй режимный вход подканала соединен, с первым входом второго -элемента И .подканала, прямой выход триггера одного подканала соединен с вторым Входом второго элег мента И подканала, выход регистра первого подканала соединен с первым информационным входом регистра второго подканала, прямой выход триггера подканала соединен с. управляющим выходом подканала, установочный вход подканала соединен с первым входом второго элемента ИЛИ подканала, выход регистра подканала соединен с информационным выходом подканала, вторые информационный и управляющий входы регистра второго подканала соединены соответственно с кодовым входом и входом разрешения приема канала, выход первого элемента ИЛИ второго подканала соединен с информационным входом элемента ЗАПРЕТ второго подканала канала, прямой выход триггера второго подканала соединен с информационным входом эле

Авторы

Даты

1982-09-30—Публикация

1980-12-05—Подача