вого,второго и третьего формирователей сигналов управления обменом соединены соответственно с девятым , десятым и одиннадцатым входами анализатора состояний, четвертый выход которого соединен с седьмым выходом устройства и седьмым входом блока коммутации, восьмой вход которого соединен с вторым выходом первого формирователя сигналов управления обменом, выходы второго счетчика соединены соответственно с восьмым выходом устройства, девятым входом блока.коммутации и пятым входом анализатора командной информации, шестой и седьмой входы которого соединены с вторыми выходами соответственно второго и третьего формирователей сигналов управления обменом, первый выход анализатора состояний соединен с пятыми входами формирователей сигналов управления обменом и с третьими входами блоков адресации, первые выходы которых соединены с десятым входом блока коммутации и вторым входом третьего регистра, другие входы которого соединены с вторыми выходами формирователей сигналов управления обменом, четвертые входы и вторые выходы блоков адресации соединены соответственно с.двенадцатым входом и девятым выходом устройства, анализатор командной информации содержит три регистра, дешифратор, приоритетный узел, два элемента ИЛИ, шесть элементов И три элемента НЕ, причем первый и второй входы анализатора соединены соответственно с входами первого и второго элементов И и через третий и четвертый элементы И - с входами первого элемента ИЛИ, выход которого через соединенные последовательно первый регистр и дешифратор соединен с первым выходом анализатора, пятьш вход которого через второй элемент ИЛИ соединен с входом пятого элемента И, с едьмой, шестой и четвертьй входы анализатора через первьй, второй и пятьй элементы И соответственно соединены.с входами второго регистра, выходы которого через соединенные последовательно приоритетный узел и третий регистр соединены вторым выходом анализатора, входами третьего и четвертого элементов И и через соответствующие элементы НЕс входами шестого элемента И, через

которьй третий вход анализатора соединен с входом первого регистра, первый формирователь сигналов управления обменом содержит два регистра, три триггера, два элемента ИЛИ,/ шесть элементов И, элемент задержки, причем первый вход формирователя соединен с входами первого и второго элементов И, пятьй вход формирователя соединен с входами третьего элемента И, первого регистра и первого элемента ИЛИ и через второй элемент ИЛИ - с входами первого и второго триггеров и второго регистра, вькод которого соединен с входами четвертого и пятого элементов И, первого элемента ИЛИ и первого триггера, выходы которого непосредственно и через первый элемент-И соединены с входами третьего триггера, выход которого через соединенные последовательно элемент задержки и второй элемент И соединен с первым выходом .формирователя, четвертый вход которого соединен с входом третьего элемента И и через шестой элемент И с входом второго элемента ИЛИ, третий вход формирователя соединен с входами первого регистра, шестого элемента И, первого триггера и второго триггера, выходы которого .соединены с входами четвертого и пятого элементов И, выходы которых, первого и второго триггеров и второго регистра являются вторым выходом формирователя, второй вход которого является входом второго регистра, выходы первого регистра, первого и второго элементов ИЛИ и третьего элемента И являются третьим выходом формирователя, второй и третий формирователи сигналов управления обменом содержат три регистра, два триггера, три элемента ИЛИ, десять элементов И, элемент НЕ, элемент задержки, причем первый вход формирователя через первый элемент И соединен с входом первого триггера и входом второго элемента И, выход которого соединен с первым выходом формирователя и входом первого регистра, второй вход формирователя соединен с входом третьего элемента И и через первьй регистр с входами четвертого элемента И, десятого

элемента И и второго регистра, один из выходов которого через третий эле мент И соединён с входом первого

триггера, выход которого через элемент задержки соединен с входом второго элемента И, третий вход формирователя соединен с входами третьего регистра, восьмого, шестого и седьмого элементов И, второго регистра и через второй триггер - с входами десятого триггера и четвертого элемента И, четвертый вход формирователя через восьмой и девятый элементы И, через пятьй, шестой и седьмой элементы И соединены соответственно с входами первого, второго и третьего элементов ИЛИ, пятый вход формирователя соединен с входами третьего элемента ИЛИ и третьего регистра, второго триггера и через соответственно девятый и пятый элементы И - с входами первого и второг элементов ИЛИ и через элемент НЕ - с входом первого элемента И, выход третьего элемента ИЛИ соединен с входами первого и второго регистров, выходы которых, третьего, четвертого и десятого элементов И, второго триггера соединены с вторым выходом формирователя, третий вьрсод которого соединен с выходами третьего регистра и первого элемента И и всех элементов ИЛИ, анализатор состояний содержит девять триггеров, пять элементов ИЛИ, четьфе элемента И, элемент задержки, причем первьй вход анализатора соединен с входом первого элемента И и через второй элемент И - с входами третьего элемента И и первого триггера, выход которого через соединенные последовательно элемент задержки, третий элемент И, первый элемент ИЛИ и второй триггер соединен с входами третьего триггера и первого элемента И, выход которого через четвертый триггер соединен с входами соответственно второго элемента ИЛИ и четвертого элемента И, третий вход анализатора через соединенные последовательно пятый триггер и второй элемент ИЛИ соединен с входами второго элемента И и

2824

шестого триггера, выход которого соединен с входом третьего элемента ИЛИ и через соединенные последовательно четвертые элементы И и ИЛИ с входами третьего и седьмого триггеров, четвертый вход анализатора соединен с входами первого элемента ИЛИ и восьмого триггера, входы которого и шестого триггера соединены с восьмым входом анализатора, девятой, десятый и.одиннадцатый входы анализатора соединены с входами первого элемента ИЛИ и через соединенные последовательно пятый элемент ИЛИ и девятый триггер соединены с входом седьмого триггера и вторым выходом анализатора, десятый и одиннадцатый входы которого соединены с входами первого, четвертого и пятого триггеров и через третий элемент ИЛИ - с

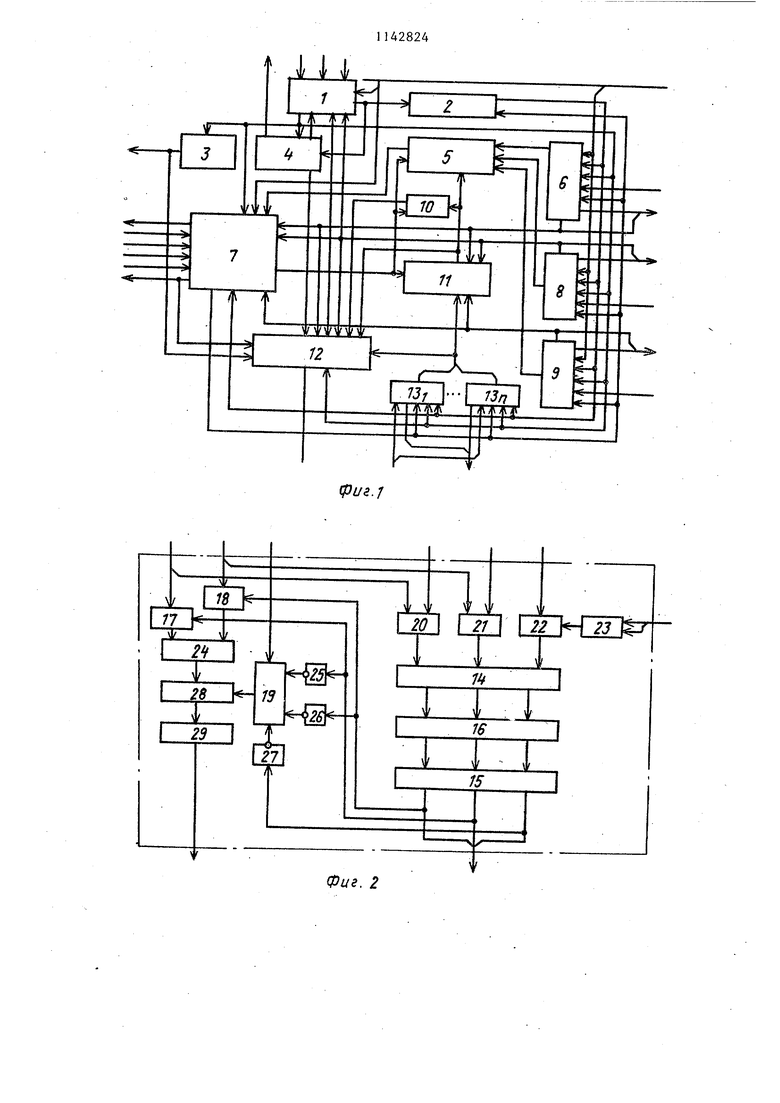

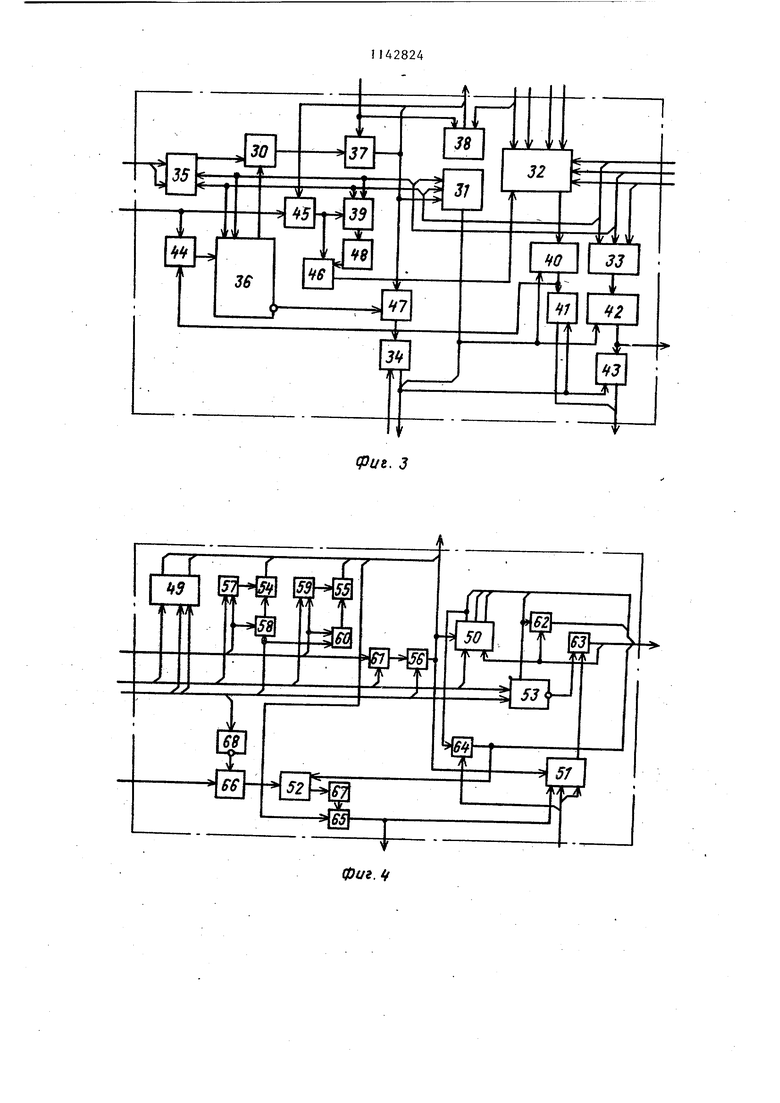

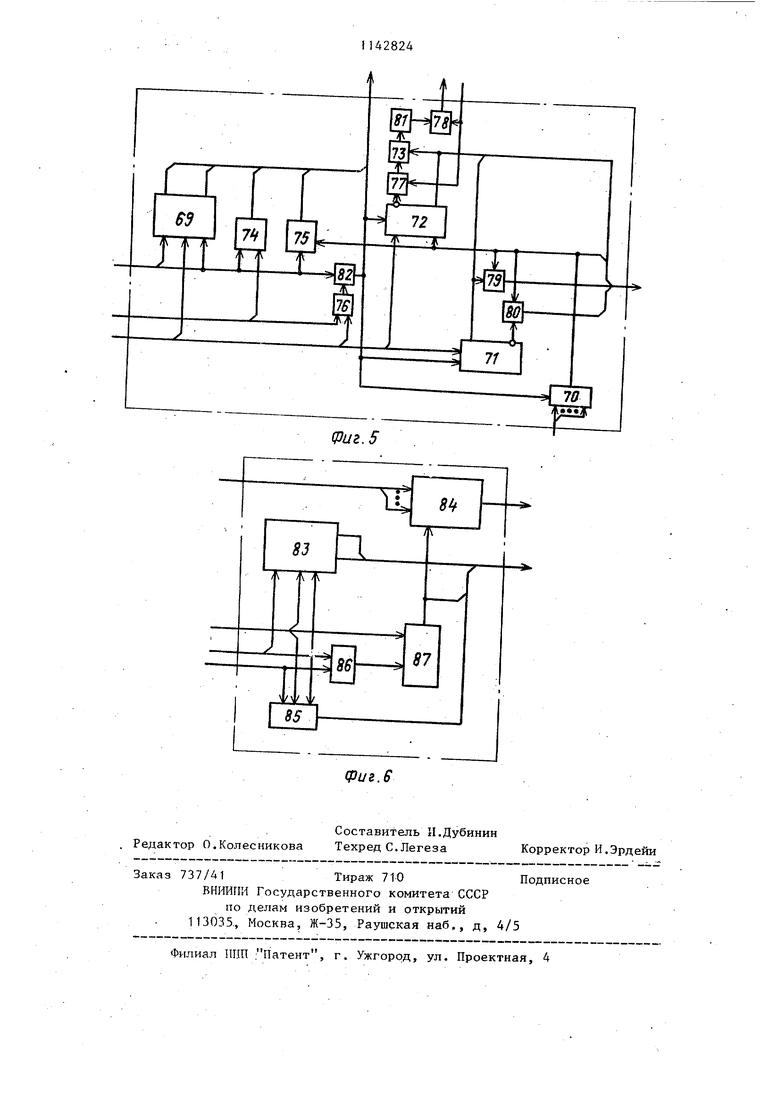

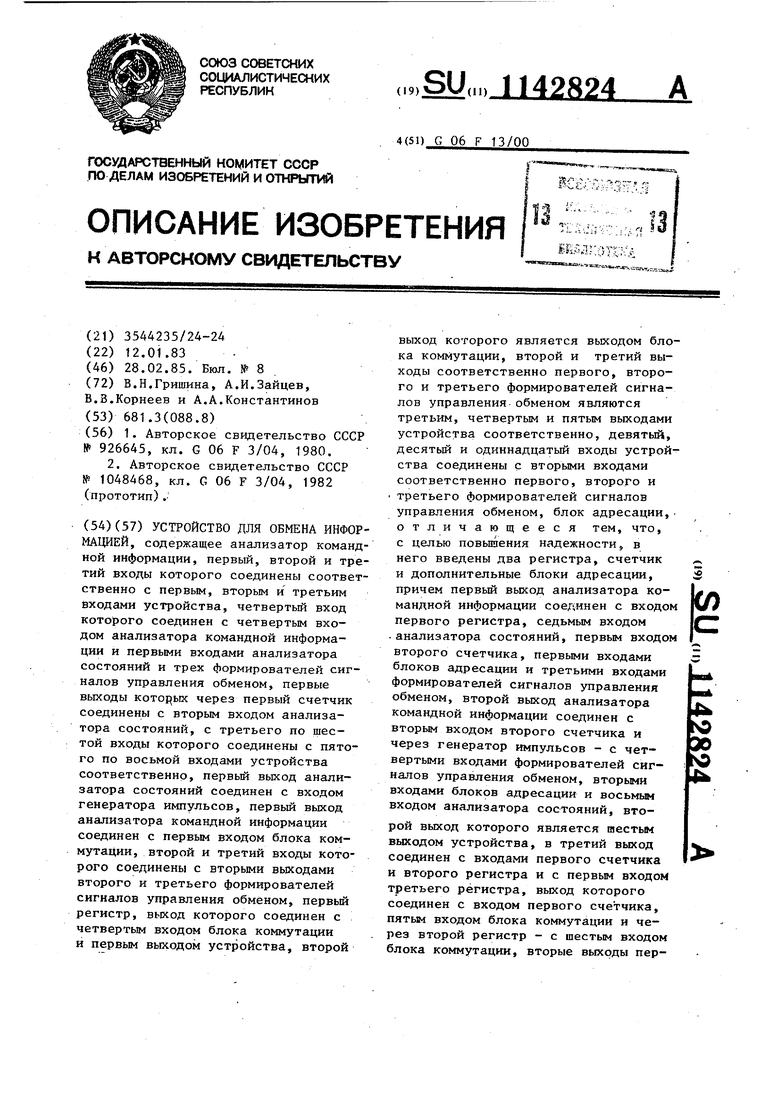

- входами второго- и девятого триггеров, второй, пятый и шестой входы анализатора соединены с входами первого элемента ИЛИ, выходы второго элементов ИЛИ, шестого и восьмого триггеров являются первым выходом анализатора, седьмой вход которого соединен с входом четвертого элемента ИЛИ, выходы которого и третьего элемента ИЛИ являются третьим выходом анализатора, четвертый выход которого является выходами третьего и седьмого триггеров, каждый блок адресации содержит два регистра, два элемента И элемент ИЛИ, причем четвертый вход блока через первый регистр соединен с первым выходом блока, первый вход которого соединен с входом второго регистра и через первый элемент И - с входом элемента ИЛИ, второй вход блока соединен с входами первого и второго элементов И, третий вход блока соединен с входом элемента ИЛИ и через втойые регистр и элемент И - с вто- рым выходом блока, выход элемента ИЛИ соединен с входом первого регистра и вторь1м выходом блока. 1 Изобретение относится к вычислительной технике и может быть исполь зовано при создании ЦВМ повышенной надежности, имеющих возможность работы в вычислительных комплексах, состоящих из нескольких параллельно работающих ЦВМ, Известно устройство для сопряжения, содержащее подканалы абонента блок приоритета, блок синхронизации, регистр готовности программы, коммутатор информации, блок контроля по модулю, два регистра неисправ ности, три элемента ИЛИ, блок элементов ИЛИ, триггер неисправности передачи и регистробмена, первые вход и выход которого являются соот ветственно первыми информационными входом и вьибодом устройства, блок управления обменом, первые вход и выход которого являются соответственно первыми управляюпц1ми входом и выходом устройства, а вторые вход и выход подключены соответственно к первым выходу и входу-блока синхрон зации, второй и третий выходы которого соответственно подключены к пе вым входам подканалов абонента и управляющему входу блока приоритета, входы запросов и выходы разреше ния которого соединены соответственно с первыми выходами и вторыми входами соответствующих подканалов абонента, третьи входы которьк подключены к управляющим выходам регистра Готовности программы, подклю ченного информационными входами и выходами соответственно к вторым выходу и входу регистра обмена, а управляющим входом - к четвертому выходу блока .синхронийации, пятьй выход которого соединен с третьим входом блока контроля по модулю, подключенного первым входом и выходом соответственно к третьим выходу и входу регистра обмена, а вторым входом - к третьему выходу блока управления, четвертый выход которого подключен к пятому входу регистра обмена, четвертые выход и вход которого соединены соответственно с информационными входом и выходом коммутатора информации, упра ляющий вход которого подключен к шестому выходу блока синхронизации J. выходы и входы группы информацио ных входов и выходов и входы группы ад ресньк входов соединены соответствен 4 с четвертыми входами, вторыми и третьи-ми выходами соответствующих подканалов абонентов, информационные входы и выходы и управляющие входы и выходы которых являются соответственно вторыми информационнь1ми входами и выходами устройства, а каждый подканал абонента содержит узел управления, регистр служебных сигналов, первые вход и выход которого соединены соответственно с первыми выходом и входом узла управления, а вторые выход и вход являются соответственно управляющими выходом и входом подканала, коммутатор типа передачи, первые вход и выход которого соединены соответственно с первым входом и выходом регистра обмена подканала, а вторые вход и выход являются соответственно информационными входом и выходом подканала, вторые вход и выход регистра обмена являются соответственно четвертьм входом и вторым вьпсодом подканала, элемент И, первый вход которого является третьим входом подканала, а выход соединен с вторым вхо-дом узла управления, третий и четвертьй выходы которого соединены соответственно с третьими входами KOI мутатора типа передачи и регистра обмена подканала, а пятьш выход - с третьим выходом подканала, триггер готовности, соединенньй входом и выходом соответственно с щестым выходом узла управления и с перрым выходом подканала, и элемент ИЖ, входы которого являются соответственно первым и вторым входами подканала, а выход соединен с вторым входом элемента И jj . Недостатком известного устройства является то, что в нем не предусмотрена аппаратная реакция на выявленные сигналы неисправности и, в частности, отсутствуют аппаратные возможности исключения из состава устройства неисправных узлов устройства и подканалов обмена для предотвращения последствий сбоя. Наиболее близким техническим решением к предлагаемому является устройство для обмена информациейi содержащее анализатор командной информации, первый - третий входы которого соединены соответственно с первым - третьим входами устройства, четвертый вход которого соединен с .четвертым входом анализатора командной информации и первыми входами анализатора состояний и трех формиро вателей сигналов управления обменом, первые выходы которых через первый счетчик соединены с вторым входом анализатора состояний, с третьего по шестой входы которого соединены с пятого по восьмой входами устройства соответственно, первьй выход анализатора состояний соединен с входом генератора импульсов, первый выход анализатора командной информации соединен с первым входом блока коммута ции, второй и третий входы которого соединены с вторыми выходами второго и третьего формирователей сигналов управления обменом, первьй регистр, выход которого соединен с четвертым входом блока коммутации и первым выходом, устройства, второй выход коi торого является выходом блока коммутации, второй и третий выходы соответственно первого - третьего формирователей сигналов управления обмено являются третьим - пятым выходами устройства соответственно, девятый одиннадцатый входы устройства соединены с вторыми входами соответственн первого - третьего формирователей сигналов управления обменом, блок адресации 2 . Недостатком устройства является низкая достоверность обмена информацией ввиду отсутствия контроля передачи информации по каналам межмашинного обмена, обмена параллельным и ,последовательным кодами и отсутст:вие аппаратных средств контроля отдельных блоков и устройства в целом. Цель изобретения - повьш1ение надежности. Поставленная цель достигается тем,, что в устройство для обмена информацией, содержащее анализатор командной информации, первый, второй и третий входы которого соединены соответственно с первым, вторым и третьим входами устройства, четвертый вход которого соединен с четвер- 50 с

тым входом анализатора командной информации и первыми входами анализатора состояний и трех формирователей сигналов управления обменом, первые выходы которых через первьй счетчик соединены с вторым входом а 1ализатора состояний, с третьего по шестой входы которого соединены

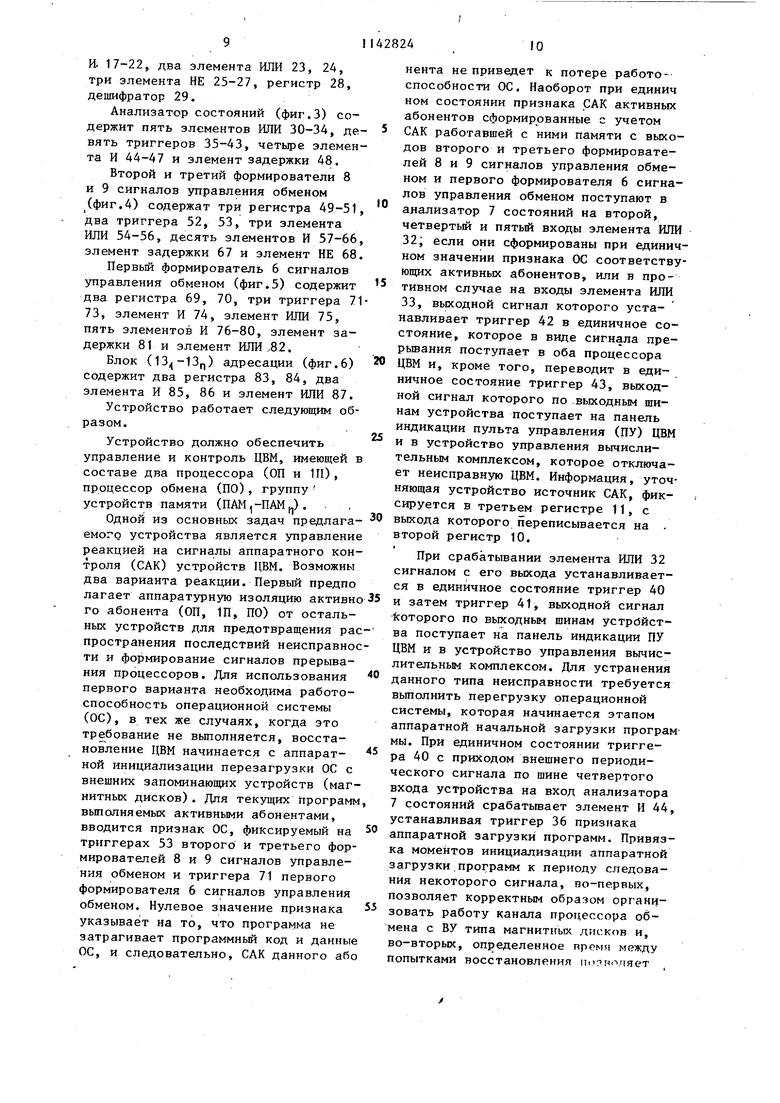

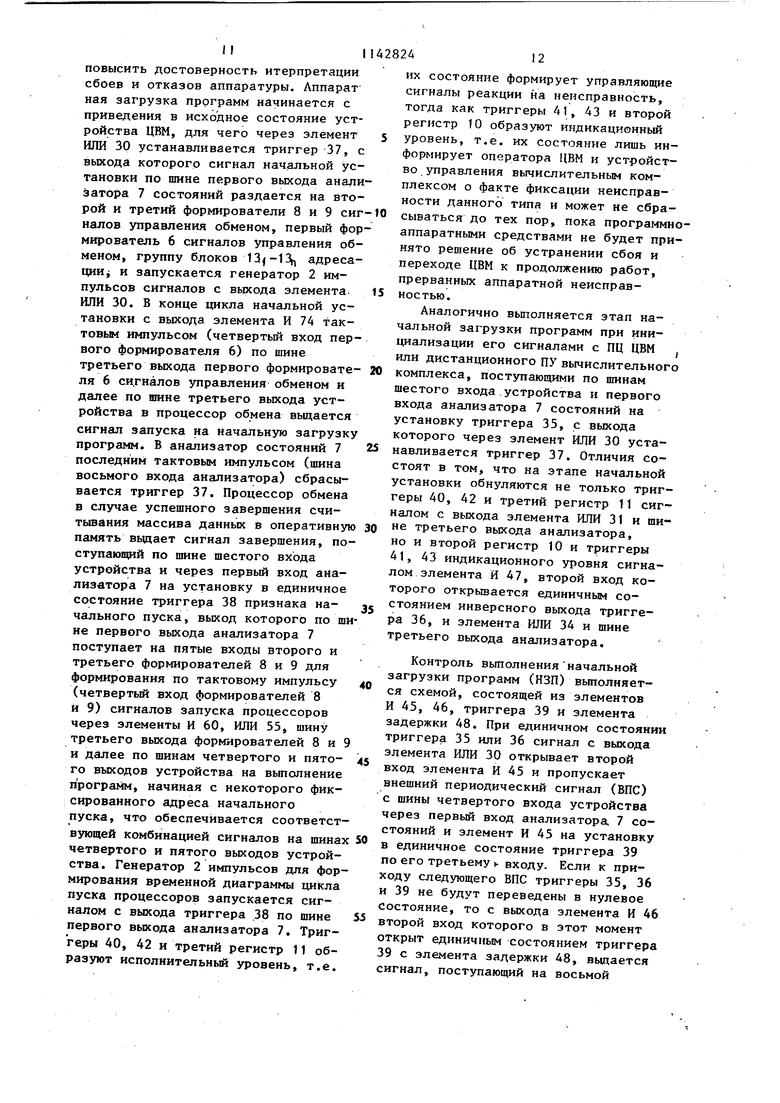

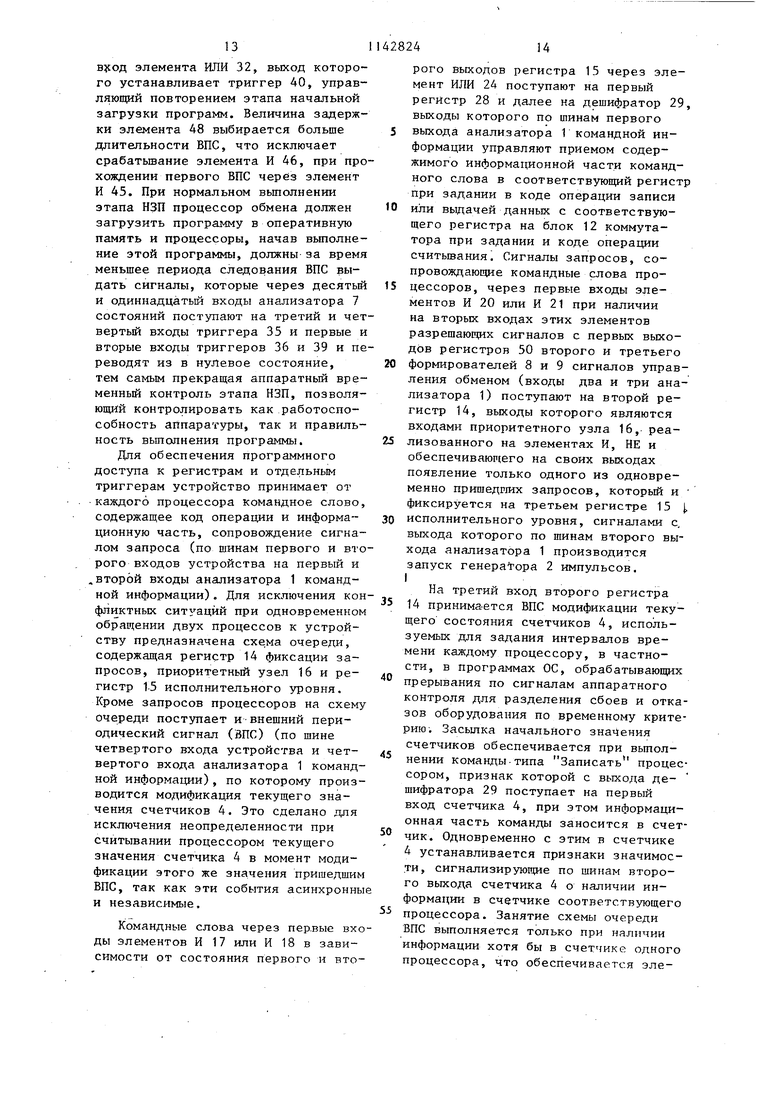

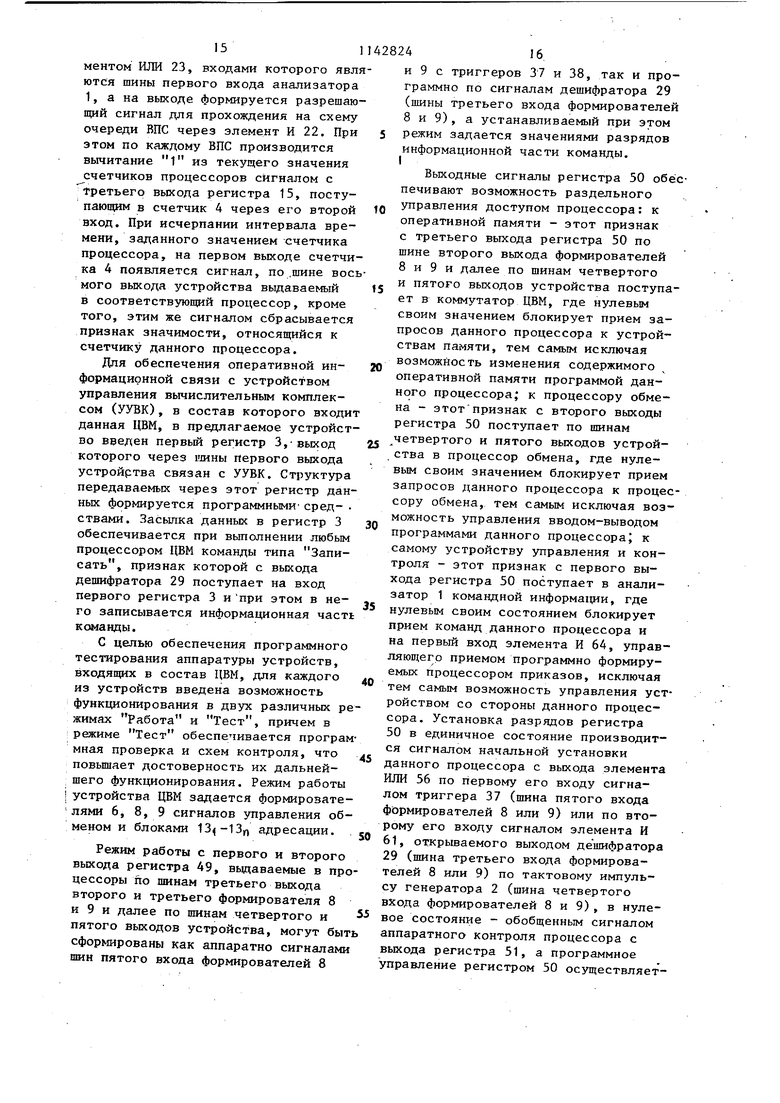

вторые выходы первого, второго и третьего формирователей сигналов управления обменом соединены соответственно с девятым, десятым и одиннадцатым входами анализатора состояний, четвертьй выход которого соединен с седьмым выходом устройства и седьмым входом блока коммутации. 244 с пятого по восьмой входами устройства соответственно, первый выход анализатора состояний соединен с : входом генератора импульсов первый выход анализатора командной информации соединен с первым входом блока коммутации, второй и третий входы которого соединены с вторыми выходами второго и третьего формирователей сигналов управления обменом, первый регистр, выход которого соединен с четвертым входом блока коммутации и первым выходом устройства, второй выход которого является выходом блока коммутации, второй и третий выходы соответственно первого, второго и третьего формирователей сигналов управления обменом являются третьим, четвертым и пятым выходами устройства соответственно,, девятьй, десятьй и одиннадцатьй входы устройства соединены с вторьми входами соответственно первого, второго и третьего формирователей сигналов управления обменом, блок адресации, введены два регистра, счетчик и дополнительные блоки адресации, причем первый выход анализатора командной информации соединен с входом первого регистра, седьмым входом анализатора состояний, первым входом второго счетчика, первыми входами блоков адресации и третьими входами формирователей сигналов управления обменом, второй выход анализатора командной информации соединен с вторым входом второго счетчика и через генератор импульсов с четвертыми входами формирователей сигналов управления обменом, вторыми входами блоков адресации и восьмым входом анализатора состояний, второй выход которого является шестым выходом устройства., а . третий вькод соединен с входами счетчика и второго регистра и с первым входом третьего регистра, выход которого соединен с входом первого счетчика, пятым входом блока коммутации и через второй регистр шестым входом блока коммутации. в.осьмой вход которого соединен с вторым выходом первого формирователя сигналов управления обменом, вы ходы второго счетчика соединены соо ветственно с восьмым выходом устрой ства, девятым входом блока коммутации и пятым входом анализатора командной информации, шестой и седьмо входы которого соединены с вторыми выходами соответственно второго и третьего формирователей сигналов управления обменом, первый выход ан лизатора состояний соединен с пятым входами формирователей сигналов управления обменом и с третьими входами блоков адресации, первые вы ходы которых соединены с десятым входом блока коммутации и вторым входом третьего регистра, другие входы которого соединены с вторыми вькодами формирователей сигналов управления обменом, четвертые входы и вторые вькоды блоков адресации соединены соответственно с двенадцатым входом и девятым выходом устройства, что анализатор командной информации содержит три perHCTpaj д шифратор, приоритетный узел, два эл мента ИЛИ, шесть элементов И, три элемента НЕ, причем первый и.второй входы анализатора-соединены соответственно с входами первого и вто рого элементов И и через третий и четвертый элементы И - с входами первого элемента ИЛИ, выход которо го через соединенные последователь первый регистр и дешифратор соединен с первым выходом анализатора, пятый вход которого через второй элемент ИЛИ соединен с входом пято го элемента И, седьмой, шестой и четвертый входы анализатора через первьй, второй и пятьй элементы И соответственно соединены с входами второго регистра, выходы которого через соединенные последовательно приоритетньш узел и третий регистр соединены с вторым выходом анализа тора, входами третьего и четвертог элементов И и через соответствующи элементы НЕ - с вхюдами шестого элемента И, через который третий вход анализатора соединен с входом первого регистра, первый формирова тель сигналов управления обменом с держит два регистра, три триггера, два элемента ИЛИ, шесть элементов элемент задержки, причем первый 8246 вход формирователя соединен с входами первого и второго элементов И, пятьм вход формирователя соединен с входами третьего элемента И, первого регистра и первого элемента ИЛИ и через второй элемент ИЛИ - с входами первого и второго триггеров и второго регистра, выход которого соединен с входами четвертого и пятого элементов И, первог.о элемента ИЛИ и первого триггера, выходы которого непосредственно и через первый элемент И соединены с входами третьего триггера, выход которого через соединенные последовательно элемент задержки и второй элемент И соединен с первым выходом формирователя, четвертьш вход которого соединен с входом третьего элемента Ни через шестой элемент И - с входом второго элемента {-ШИ, третий вход формирователя соединен с входами первого регистра, шестого элемента И, первого триггера и второго триггера, выходы которого соединены с входами четвертого и пятого элементов И, выходы которых, первого и второго триггеров и второго регистра являются вторым выходом формирователя, второй вход которого является входом второго ре-, гистра, выходы первого регистра, первого и второго элементов ИЛИ и третьего элемента И являются третьим выходом формирователя, второй и третий формирователи сигналов управления обменом содержат три регистра, два триггера, три элемента ИЛИ, десять элементов И, элемент НЕ, элемент задержки, причем первый вход формирователя через первый элемент И соединен с входом первого триггера и входом второго элемента И, выход которого соединен с первым выходом формирователя и входом первого регистра, второй вход формирователя соединен с входом третьего элемента И и через первьй регистр с входами четвертого элемента И, десятого элемента И и второго регистра, один из выходов которого через третий элемент И соединен с входом первого триггера, выход которого через элемент задержки соединен с входом второго элемента И, третий вход формирователя соединен с входами третьего регистра, восьмого, шестого и седьмого элементо з И, второго регистра и через второй триггер - входами десятого триггера и четвертого элемента И, четвертый вход формирователя чере восьмой и девятый элементы И, через пятый, шестой и седьмой элементы И соединены соответственно с входами первого, второго и третьего элементов ИЛИ, пятый вход формирователя соединен с входами третьего элемента ИЛИ и третьего регистра, второго триггера и через соответственно девятый и пятый элементы И - с входами первого и второго элементов ИЛИ, и через элемент НЕ - с входом первого элемента И, выход третьего элемента ИЛИ соединен с входами первого и вто- IS рого регистров, выходы которых, третьего, четвертого и десятого элементов И, второго триггера соединены с вторым выходом формирователя, третий выход которого соединен с выходами третьего регистра и первого элемента И и всех элементов ИЛИ, анализатор состояний содержит девять триггеров, пять элементов ИЛИ, четыре жлемента И, элемент задержки причем первый вход анализатора соеди нен с входом первого элемента И и через второй элемент И - с входами третьего элемента И и первого триггера, выход которого через соединенные последовательно элемент задержки, третий элемент И, первый элемент ИЛИ и второй триггер соединен с входами третьего триггера и первого элемента И, выход которого через чет вертый триггер соединен с входами соответственно второго элемента ИЛИ и четвертого элемента И, третий вход анализатора через соединенные последовательно пятый триггер и второй элемент ИЛИ соединен с входами второго элемента И и шестого триггера, выход которого соединен с входом третьего элемента ИЛИ и через соединенные последовательно четвертые элементы И и ИЛИ - с входами третье го и седьмого триггеров, четвертый вход анализатора соединен с входами первого элемента ИЛИ и восьмого триггера, входы которого и шестого триггера соединены с восьмым входом анализатора, девятый, десятый и одиннадцатый входы анализатора соединены с входами первого элемента ИЛИ и через соединенные последовательно пятый элемент ИЛИ и девятый триггер соединены с входом седьмого триггера и вторым выходом анализатоИ48 ра, десятый и одиннадцатый входы которого соединены с входами первого, четвертого и пятого триггеров и через третий элемент ИЛИ - с входами второго и девятого триггеров, второй, пятый и шестой входы анализатора соединены с входами первого, элемента ИЛИ, выходы второго элементов ИЛИ, шестого и восьмого триггеров являются первым выходом анализатора, седьмой вход которого соединен с входом четвертого элемента ИЛИ, выходы которого и третьего элемента ИЛИ являются третьим выходом анализатора, четвертый выход которого является выходами третьего и седьмого триггеров, каждый блок адресации содержит два регистра, два элемента И, элемент ИЛИ, причем четвертый вход блока через первьй регистр соединен с первым выходом блока, первый вход которого соединен с входом второго регистра и через первый элемент И - с входом элемента ИЛИ, второй вход блока соединен с входами первого и второго элементов И, третий вход блока соединен с входом элемента ИЛИ и через вторые регистр и элемент И - с вторым выходом блока, выход элемента ИЛИ соединен с входом первого регистра и вторым выходом блока. На фиг.1 представлена блок-схема устройства для обмена информацией; на фиг.2 - функциональная схема анализатора командной информации на фиг.3 - функциональная схема анализатора состояний, на фиг.4 функциональная схема второго и третьего формирователей сигналов управления обменом, на фиг.5 - функциональная схема первого формирователя сигналов управления обменом, на фиг.6 функциональная схема блока адресации. Устройство (фиг.1) включает анализатор 1 командной информации, генератор 2 импульсов, первый регистр 3, второй счетчик 4, первый счетчик 5, первый формирователь 6 сигналов управления обменом, анализатор 7 состояний, два идентичных формирователя 8 и 9 сигналов управления обменом, второй регистр 10, третий регистр 11, б.лок 12 коммутатора и группу блоков адресации. Анализатор 1 командной информации (фиг.2) содержит регистры 14, 15, риоритетный узел 16, шесть элементов И. 17-22, два элемента ИЛИ 23, 24, три элемента НЕ 25-27, регистр 28, дешифратор 29. Анализатор состояний (фиг.З) содержит пять элементов ИЛИ 30-34, девять триггеров 35-43, четыре элемента И 44-47 и элемент задержки 48. Второй и третий формирователи 8 и 9 сигналов управления обменом (фиг.4) содержат три регистра 49-51, два триггера 52, 53, три элемента ИЛИ 54-56, десять элементов И 57-66, элемент задержки 67 и элемент НЕ 68. Первый формирователь 6 сигналов управления обменом (фиг,5) содержит два регистра 69, 70, три триггера 71 73, элемент И 74, элемент ИЛИ 75, пять элементов И 76-80, элемент задержки 81 и элемент ИЛИ .82. Блок () адресации (фиг.6) содержит два регистра 83, 84, два элемента И 85, 86 и элемент ИЛИ 87. Устройство работает следующим образом. Устройство должно обеспечить управление и контроль ЦВМ, имеющей в составе два процессора (ОП и 1П), процессор обмена (ПО), группу устройств памяти (). Одной из основных задач предлага емого устройства является управление реакцией на сигналы аппаратного контроля (САК) устройств ЦВМ. Возможны два варианта реакции. Первый предпо лагает аппаратурную изоляцию активн го абонента (ОП, 1П, ПО) от остальных устройств для предотвращения рас пространения последствий неисправно ти и формирование сигналов прерывания процессоров. Для использования первого варианта необходима работоспособность операционной системы (ОС), в тех же случаях, когда это требование не выполняется, восстановление ЦВМ начинается с аппаратной инициализации перезагрузки ОС с внешних запоминающих устройств (маг нитных дисков). Для текущих программ выполняемых активными абонентами, вводится признак ОС, фиксируемый на триггерах 53 второго и третьего фор мирователей 8 и 9 сигналов управления обменом и триггера 71 первого формирователя 6 сигналов управления обменом. Нулевое значение признака указывает на то, что программа не затрагивает программньй код и данны ОС, и следовательно, САК данного аб нента не приведет к потере работоспособности ОС. Наоборот при единич ном состоянии признака САК активных абонентов сформированные с учетом САК работавшей с ними памяти с выходов второго и третьего формирователей 8 и 9 сигналов управления обменом и первого формирователя 6 сигналов управления обменом поступают в анализатор 7 состояний на второй, четвертый и пятый входы элемента ИЛИ 32, если они сформированы при единичном значении признака ОС соответствующих активных абонентов, или в противном случае на входы элемента ИЛИ 33, выходной сигнал которого устанавливает триггер 42 в единичное состояние, которое в виде сигнала прерьюания поступает в оба процессора ЦВМ и, кроме того, переводит в единичное состояние триггер 43, выходной сигнал которого по .выходным шинам устройства поступает на панель индикации пульта управления (ПУ) ЦВМ и в устройство управления вычислительным комплексом, которое отключает неисправную ЦВМ. Информация, уточняющая устройство источник САК, фиксируется в третьем регистре 11, с выхода которого переписывается на . второй регистр 10. При срабатывании элемента Ш1К 32 сигналом с его выхода устанавливается в единичное состояние триггер 40 и затем триггер 41, выходной сигнал koToporo по выходным шинам устрбйства поступает на панель индикации ПУ ЦВМ и в устройство управления вычислительным комплексом. Для устранения данного типа неисправности требуется выполнить перегрузку операционной системы, которая начинается этапом аппаратной начальной загрузки программы. При единичном состоянии триггера 40 с приходом внешнего периодического сигнала по шине четвертого входа устройства на вход анализатора 7 состояний срабатьгоает элемент И 44, устанавливая триггер 36 признака аппаратной загрузки программ. Привязка моментов инициализации аппаратной загрузки.программ к периоду следования некоторого сигнала, но-первых, позволяет корректным образом организовать работу канала процессора обмена с ВУ типа магнитных дисков и, во-вторых, определенное премя между попытками восстановления .1яет повысить достоверность итерпретации сбоев и отказов аппаратуры. Аппарат ная загрузка пррграмм начинается с приведения в исходное состояние устройства ЦВМ, для чего через элемент ИЛИ 30 устанавливается триггер 37, с выхода которого сигнал начальной установки по шине первого выхода анаци затора 7 состояний раздается на второй и третий формирователи 8 и 9 сиг налов управления обменом, первый фор мироватепь 6 сигналов управления обменом, группу блоков 13f-13f, адресации и запускается генератор 2 импульсов сигналов с выхода элемента ИЛИ 30. В конце цикла начальной установки с выхода элемента И 74 тактовьм импульсом (четвертый вход первого формирователя 6) по шине третьего выхода первого формирователя 6 сигналов управления обменом и далее по шине третьего выхода устройства в процессор обмена выдается сигнал запуска на начальную загрузку программ. В анализатор состояний 7 последним тактовым импульсом (шина восьмого входа анализатора) сбрасывается триггер 37. Процессор обмена в случае успешного завершения считьюания массива данных в оперативную память вьщает сигнал завершения, поступаювдй по шине шестого входа устройства и через первый вход анализатора 7 на установку в единичное состояние триггера 38 признака начального пуска, выход которого по ши не первого выхода анализатора 7 поступает на пятые входы второго и третьего формирователей 8 и 9 для формирования по тактовому импульсу (четвертый вход формирователей 8 И 9) сигналов запуска процессоров через элементы И 60, ИЛИ 55, шину третьего выхода формирователей 8 и 9 и далее по шинам четвертого и пятого выходов устройства на выполнение программ, начиная с некоторого фиксированного адреса начального пуска, что обеспечивается соответствующей комбинацией сигналов на шинах четвертого и пятого выходов устройства. Генератор 2 импульсов для формирования временной диаграммы цикла пуска процессоров запускается сигналом с выхода триггера 38 по шине первого выхода анализатора 7, Триггеры 40, 42 и третий регистр 11 образуют исполнительный уровень, т.е. их состояние формирует управляющие сигналы реакции на неисправность, тогда как триггеры 41, 43 и второй регистр 10 образуют индикационный уровень, т.е. их состояние лишь информирует оператора ЦВМ и устройство управления вычислительным комплексом о факте фиксации неисправности данного типа и может не сбрасываться до тех пор, пока программноаппаратными средствами не будет принято решение об устранении сбоя и переходе ЦВМ к продолжению работ, прерванных аппаратной неисправностью. Аналогично выполняется этап начальной загрузки программ при инициализации его сигналами с ПЦ ЦВМ , или дистанционного ПУ вычислительного комплекса, поступающими по шинам шестого входа устройства и первого входа анализатора 7 состояний на установку триггера 35, с выхода которого через элемент ИЛИ 30 устанавливается триггер 37. Отличия состоят в том, что на этапе начальной установки обнуляются не только триггеры 40, 42 и третий регистр 11 сигналом с выхода элемента ИЛИ 31 и шине третьего выхода анализатора, но и второй регистр 10 и триггеры 41, 43 индикационного уровня сигналом элемента И 47, второй вход которого открьшается единичным состоянием инверсного выхода триггера 36, и элемента ИЛИ 34 и шине третьего выхода анализатора. Контроль вьшолненияначальной загрузки программ (НЭП) выполняется схемой, состоящей из элементов И 45, 46, триггера 39 и элемента задержки 48. При единичном состоянии триггера 35 или 36 сигнал с выхода элемента ИЛИ 30 открывает второй вход элемента И 45 и пропускает внешний периодический сигнал (ВЦС) с шины четвертого входа устройства через первый вход анализатора, 7 состояний и элемент И 45 на установку в единичное состояние триггера 39 по его третьему ь входу. Если к приходу следующего ВПС триггеры 35, 36 и 39 не будут переведены в нулевое остояние, то с выхода элемента И 46 второй вход которого в этот момент ткрыт единичным состоянием триггера 9 с элемента задержки 48, выдается игнал, поступающий на восьмой 13 вуод элемента ИЛИ 32, выход которого устанавливает триггер 40, управляющий повторением этапа начальной загрузки программ. Величина задержки элемента 48 выбирается больше длительности ВПС, что исключает срабатьшание элемента И 46, при про хождении первого ВПС через элемент И 45. При нормальном вьшолнении этапа НЗП процессор обмена должен загрузить программу в оперативную память и процессоры, начав выполнение этой программы, должны за время меньшее периода следования ВПС выдать сигналы, которые через десятьй и одиннадцатый входы анализатора 7 состояний поступают на третий и чет вертьй входы триггера 35 и первые и вторые входы триггеров 36 и 39 и пе реводят из в нулевое состояние, тем самым прекращая аппаратный временньй контроль этапа НЗП, позволяющий контролировать как работоспособность аппаратуры, так и правильность вьтолнения программы. Для обеспечения программного доступа к регистрам и отдельным триггерам устройство принимает от каждого процессора командное слово содержащее код операции и информационную часть, сопровождение сигналом запроса (по шинам первого и вто рого входов устройства на первый и .второй входы анализатора 1 командной информации). Для исключения ко фликтных ситуаций при одновременном обращении двух процессов к устройству предназначена схема очереди, содержащая регистр 14 фиксации запросов, приоритетный узел 16 и регистр 1-5 исполнительного уровня. Кроме запросов процессоров на схем очереди поступает ивнешний периодический сигнал (ВПС) (по шине четвертого входа устройства и четвертого входа анализатора 1 команд ной информации), по которому произ водится модификация текущего значения счетчиков 4. Это сделано для исключения неопределенности при считывании процессором текущего значения счетчика 4 в момент модификации этого же значения пришедши ВПС, так как эти события асинхронн и независимые. Командные слова через пер.выс вх ды элементов И 17 или И 18 в зависимости от состояния первого и вто 4 рого выходов регистра 15 через элемент ИЛИ 24 поступают на первый регистр 28 и далее на дешифратор 29, выходы которого по шинам первого выхода анализатора Г командной информации управляют приемом содержимого информационной части командного слова в соответствующий регистр при задании в коде операции записи или выдачей данных с соответствующего регистра на блок 12 коммутатора при задании и коде операции считьгоания. Сигналы запросов, сопровождающие командные слова процессоров, через первые входы элементов И 20 или И 21 при наличии на вторых входах этих элементов разрешающих сигналов с первых выходов регистров 50 второго и третьего формирователей 8 и 9 сигналов управления обменом (входы два и три анализатора 1) поступают на второй регистр 14, выходы которого являются входами приоритетного узла 16, реализованного на элементах И, НЕ и обеспечивающего на своих выходах появление только одного из одновременно пришедиих запросов, который и фиксируется на третьем регистре 15 J. исполнительного уровня, сигналами с, выхода которого по шинам второго выхода анализатора 1 производится запуск генератора 2 импульсов. I На третий вход второго регистра 14 принимается ВПС модификации текущего состояния счетчиков 4, используемых для задания интервалов времени каждому процессору, в частности, в программах ОС, обрабатывающих прерывания по сигналам аппаратного контроля для разделения сбоев и отказов оборудования по временному критерию; Засылка начального значения счетчиков обеспечивается при вьтолнении команды-типа Записать процессором, признак которой с выхода дешифратора 29 поступает на первый вход счетчика 4, при этом информационная часть команды заносится в счетчик. Одновременно с этим в счетчике 4 устанавливается признаки значимости, сигнализирующие по шинам второго выхода счетчика 4 о наличии информации в счетчике соответствующего процессора. Занятие схемы очереди ВПС выполняется только при наличии информации хотя бы в счетчике одного процессора, что обеспечивается элементом ИЛИ 23, входами которого явля ются шины первого входа анализатора 1, а на выходе формируется разрешающий сигнал для прохождения на схему очереди ВПС через элемент И 22, При этом по каждому ВПС производится вычитание 1 из текущего значения счетчиков процессоров сигналом с третьего выхода регистра 15, поступающим в счетчик 4 через его второй вход. При исчерпании интервала времени, заданного значением счетчика процессора, на первом выходе счетчика 4 появляется сигнал, по .шине вось мого выхода устройства вьщаваемый в соответствующий процессор, кроме того, этим же сигналом сбрасывается признак значимости, относящийся к счетчику данного процессора. Для обеспечения оперативной информационной связи с устройством управления вычислительным комплексом (УУВК), в состав которого входит данная ЦВМ, в предлагаемое устройство введен первый регистр 3,выход которого через шины первого выхода устройртва связан с УУВК. Структура передаваемых через этот регистр данных формируется программными-сред- ствами. Засылка данных в регистр 3 обеспечивается при вьшолнении любым Процессором ЦВМ команды типа Записать, признак которой с выхода дешифратора 29 поступает на вход первого регистра 3 и при этом в него записывается информационная часть команды. С целью обеспечения программного тестирования аппаратуры устройств, входящих в состав ЦВМ, для каждого из устройств введена возможность функционирования в двух различных ре жимах Работа и Тест, причем в : режиме Тест обеспечивается програм мная проверка и схем контроля, что повьш1ает достоверность их дальнейшего функционирования. Режим работы устройства ЦВМ задается формировате- лями 6, 8, 9 сигналов згправления об меном и блоками адресации. Режим работы с первого и второго регистра 49, вьздаваемые в пр цессоры по шинам третьего выхода второго и третьего формирователя 8 и 9 и далее по шинам четвертого и пятого выходов устройства, могут бы сформированы как аппаратно сигналами шин пятого входа формирователей 8 и 9 с триггеров 37 и 38, так и программно по сигналам дешифратора 29 (шины третьего входа формирователей 8 и 9), а устанавливаемый при этом режим задается значениями разрядов информационной части команды. I Вькодные сигналы регистра 50 обеспечивают возможность раздельного управления доступом процессора: к оперативной памяти - этот признак с третьего выхода регистра 50 по шине второго выхода формирователей 8 и 9 и далее по шинам четвертого и пятого выходов устройства поступает в коммутатор ЦВМ, где нулевым своим значением блокирует прием запросов данного процессора к устройствам памяти, тем самым исключая возможность изменения содержимого оперативной памяти программой данного процессора; к процессору обмена - этотпризнак с второго выходы регистра 50 поступает по шинам четвертого и пятого выходов устройства в процессор обмена, где нулевым своим значением блокирует прием запросов данного процессора к процессору обмена, тем самым исключая возможность управления вводом-выводом программами данного процессораJ к самому устройству управления и контроля - этот признак с первого выхода регистра 50 поступает в анализатор 1 командной информахщи, где нулевым своим состоянием блокирует прием команд данного процессора и на первый вход элемента И 64, управляющего приемом программно формируемых процессором приказов, исключая тем самым возможность управления устройством со стороны данного процессора. Установка разрядов регистра 50 в единичное состояние производится сигналом начальной установки данного процессора с выхода элемента ИЛИ 56 по первому его входу сигналом триггера 37 (шина пятого входа формирователей 8 или 9) или по второму его входу сигналом элемента И 61, открываемого выходом дешифратора 29 (шина третьего входа формирователей 8 или 9) по тактовому импульсу генератора 2 (шина четвертого входа формирователей 8 и 9), в нулевое состояние - обобщенным сигналом аппаратного контроля процессора с выхода регистра 51, а программное правление регистром 50 осуществляетeg сигналами дешифратора 29 (шины третьего входа формирователей 8 и 9) при этом записываемые значения разря дов регистра определяются информационной частью команды. Сигналы аппаратного контроля процессора поступают по шинам десятого и одиннадцатого входов устройства и далее по шинам второго входа формирователей 8 или 9 на регистр 51, с вькода которого обобщенный сигнал по шине второго выхода формирователя 8 или 9 поступает на третий регистр 11 и в зависимости от состояния триггера 52 признака ОС через элементы И 62 или И 63 формиру ет сигнал на шинах второго выхода формирователя в анализатор 7 состояний. При единичном состоянии триггер 53 срабатывает элемент И 61, при ну.левом состоянии - элемент И 63, второй вход которого открывается инверс ным выходом триггера 53. Установка триггера 53 в единичное состояние выполняется сигналом триггера 37 на этапе начальной установки устройства ЦВМ, а программное управление осуществляется сигналами вькодов дешифратора 29 (шины третьего входа формиро вателя 8 или 9), причем устанавливаемое состояние триггера 53 определяется значением информационной части команды. В формирователях 8 и 9 формируются и выдаются в процессоры по шинам третьего выхо.а формирователя с выходов элементов ИЛИ. 54-56 три управляюш;их сигнала, комбинация позволяет осуществить внешнее управление запуском процессора на вьшолнение программ, начиная с трех различных фиксированных адресов. Первый из этих сигналоь выполняет начальную установку схем процессора и формируется по первому входу элемента ИЛИ 56 при единичном состоянии триггера 37 (шина пятого входа форми рователя) или по второму входу элемента иЛи 56 при программной начальной установке, задаваемой выходом злемерта И 61, срабатывающего от сиг налов дешифратора 29 (шина третьего входа формирователя) в момент поступ ления на его первьй вход тактового импульса по шине четвертого входа формирователя. Второй управляющий сигнал с элемента ИЛИ 54 формируется по первому его входу через элемент 1 4 18 И 58 сигналом триггера 38 (шина пятого входа формирователя) в момент тактового импульса или по второму входу элемента ИЛИ 54 выходом элемента И 57, первый вход которого шиной третьего входа формирователя подключен к выходу дешифратора 29, а второй вход шиной четвертого входа формирователя соединен с генератором 2 импульсов. Третий управляющий сигнал выполняет соответственно пуск процессора И формируется по второму входу элемента ИЛИ 55 через элемента И 60 выходом триггера 38 в момент тактового импульса генератора 2 или по первому входу элемента ИЛИ 55 через элемент И 59 выходом дешифратора 29 в момент тактового импульса генератора 2. При этом обеспечивается йозможность как аппаратного формирования комбинации указанных трех управляющих сигналов, так и программного при выполнении предлагаемым устройством команд, поступающих от какого-либо процессора. Одна из составляющих сигнала аппаратного контроля процессоров формируется в формирователях 8 и 9 на выходе элемента И 65 схемой, включающей, кроме того, элемент И 66, триггер 52, элемент задержки 67 и элемент НЕ 68. Данная схема контролирует реакцию процессора на внешний периодический сигнал (ВПС) логического прерывания, причем время реакции должно быть не более периода следования этого сигнала. Схема работает следующим образом. ВПС, поступающий в устройство по шине четвертого входа на первые входы формирователей 8 и 9 через элемент И 66, устанавливает в единичное состояние триггер 52. и вьщается в виде сигнала прерывания в процессор по шине третьего выхода формирователя и далее по шинам четвертого и пятого выходов устройства. Если к моменту прихода следующего ВПС процессор не выполнил обработку прерывания по предьщущему сигналу, признаком чего является сигнал на шине второ- , го входа формирователя, поступающий от процессоров по шинам десятого и одиннадцатого входов устройства и обнуляющий через элемент И 64 триггер 52 по его второму входу, то появляется сигнал на выходе элемента И 65, первый вход которого в этот момент открыт сигналом с выхода элемента И 66, а второй - единич ным состоянием выхода триггера 52, поступающим через элемент задержки 67. Величина задержки элемента 67 выбрана большей длительности ВПС, ч не позволяет сработать элементу И 65 по приходу первого ВПС, Кроме фиксации в регистре 51, этот сигнал аппаратного контроля поступает через первый выход формирсгвателя на третий иди четвертьй входы первого счетчика 5, увеличивая на единицу его показания. Работа данной схемы блокируется на этапе начальной загрузки программ, признак которого с элемента ИЛИ 30 по шине пятого входа формирователя поступает на элемент НЕ 68 и закрывает второй вход элемента И 66, прекращая прием ВПС. Необходимо отметить, что данная схема позволяет контролировать как работоспособность аппаратуры, так и программы, выполняемых процес сорами . , Режимы работы процессора обмена на первом и втором выходах регистра 69 могут быть сформированы как аппа ратно сигналами по шинам пятого вхо да формирователя 6 сигналов управления обменом с триггеров 37 и 38, так и программно по сигналам дешифр тора 29 (шины третьего входа формиро вателя б), причем в этом случае уста навливаемый режим задается значения ми разрядов информационной части ко манды. Регистр 70 управляет доступом процессора обмена к оперативной памяти этот признак по шине второго выхода формирователя 6 и далее по пшне третьего выхода устройства поступает в коммутатор ЦВМ, где нулевым своим значением блокирует прием запросов процессора обмена к устрой ствам оперативной памяти, тем самым исключая возможность модификации ее содержимого программами ввода-вы вода. Установка регистра 70 в единичное состояние производится сигна лом начальной установки процессора обмена с выхода элемента ИЖ 82, на первый вход которого поступает сигнал с триггера 37, а второй вход обеспечивает программное,формирование этого сигнала выходами дешифратора 29 (шина третьего входа формирователя 6) в момент тактового им1420 пульса генератора 2 (шина четвертого входа формирователя 6) через элемент И 76. Кроме того, сигнал начальной установки процессора обмена обеспечивает установку в единичное состояние триггера 71 признака ОС по второму его входу, сброс регистра 70 по первому его входу и по шине третьего выхода формирователя 6 и далее по шине третьего выхода устройства вьщается в процессор обмена для приведения его схем в исходное состояние. Программное управление состоянием регистра 70 обеспечивается сигналом, поступающим на первый его вход с дешифратора 29, при этом устанавливаемое значение задается значением разрядов информационной части команды. Программное управление состоянием триггера 71 обеспечивается сигналом, поступающим на пер вый его вход с выхода дешифратора 29, при этом устанавливаемое значение задается значением разряда информационной части команды. Сигналы аппаратного контроля процессора обмена по шинам девятого входа устройства и шинам второго входа формирователя 6 поступают на группу входов регистра 70, с выхода которого обобщенный сигнал по шине второ- го выхода формирователя 6 поступает на второй вход третьего регистра 11, и, кроме того, в самом формирователе 6: на входы элементов И 79, 80, с выходов которых формируются сигналы аппаратного контроля с учетом признака ОС процесса обмена (триггер 71), при единичном состоянии триггера 71 срабатывает элемент И 79, при нулевом состоянии - элемент И 80, открываемый единичным состоянием инверсного выхода триггера 71, сигналы с выходов элементов И 79, 80 по шинам второго выхода формирователя 6 поступают через девятьй вход в анализатор 7 состояний на элементы ИЛИ 32 и 33, на третий вход регистра 70 и переводит его в нулевое состояние, тем самым изолируя процессор обмена от оперативной памяти, на элемент ИЛИ 75, по выходному сигналу которого процессор обмена разрьгаает логическую связь с подключенными к нему в данный момент внешними устройствами. Для процессора обмена формируется ременной сигнал аппаратного контроля, фиксирующий время, в течение которого процессор обмена отключен от оперативной памяти, признаком чего является нулевое состояние регистра 70. После установки в нулевое состояние регистра 70 первьй пришедший временной сигнал по первому входу формирователя 6 через второй вход элемента И 77 устанавливает триггер 73, так как второй вход элемента И 77 в этот момент открыт единичным состоянием инверсного выхода регистра 70. Если к приходу следующего временного сигнала триггер 73 не обнулен единичным состоянием регистра ,70, то временной сигнал через элемент И 78 вьщает сигнал аппаратного контроля. Сигнал с выхода элемента И 78 через первый выход формирователя 6 поступает на пятьй вход первого счетчика 5, увеличивая на единицу его показания. Тем самым обеспечивается контроль программной реакции на сигнал аппаратного контроля процессора обмена и соответственно работоспособность операционной системы, так как программы обработки сигналов аппаратного контроля являются ее составной частью. Соответственно каждый последующий временной сигнал при единичном состоянии триггера 73 увеличивает показания счетчика 5, :при переполнении сигналом с его выхода через второй вход анализатора 7 состояний, элемент ИЛИ 32 установит триггер 40, управляющий аппаратной перегрузкой операционной системы.

Сигналы аппаратного контроля (САК) устройств памяти поступают на шины двенадцатого входа устройства и шины четвертого входа соответствующего блока 13,-13fj адресации на вход регистра 84, с выхода которого обобщенный сигнал через первьй выход блока 13 поступает в третий регистр 11 по шинам его второго входа.

Из устройства памяти поступают два типа САК: первый тип включает САК схем регенерации данных, появление его является признаком недостоверности рсех данных, хранившихся в накопителе этого устройства памяти; второй тип включает САК схем, работоспособность которых не влияет на сохранность данных в накопителе

устройства памяти. I

Сбой, связанньй с появлением САК первого типа для устройства памяти, в которых разрешаются программный код и данные операционной системы, требует обновления этой информации с внешних носителей (типа магнитных дисков). Для этого САК устройств памяти через седьмой и восьмой входы устройства и пятьй и шестой входы анализатора 7 состояний, элемент ИЛИ 32 устанавливают триггер

40, обеспечивающий аппаратную перезагрузку операционной системы с использованием режима начальной загрузки программ. В тестовом режиме после программной проверки-схем аппаратного контроля устройства памяти необходимо вьтолнить приведение их а исходное состояние без потери данных в самом накопителе. Для этого блок 13 формирует два сигнала начальной установки на шинах второго выхода: первьй выполняет начальнзло установку схем устройства памяти с потерей данных в накопителе и въща ется с выхода элемента И 85, на первый вход которого поступает сигнал по шине третьего входа блока 13 с триггера 37 признака начальной установки, на второй вход - сигнал с элемента ИЛИ 30 признака начальной

загрузки программ, на третий вход тактовьй сигнал по шине второго входа блока с выхода генератора 2 импульсов, второй сигнал начальной установки устройства памяти, не затрагивающий схем регенерации данных в накопителе, может формироваться как аппаратно, при этом элемент ИЛИ 87 срабатывает по своему первому входу от сигнала триггера 37 (шина

третьего входа блока 13), так и программно, при этом элемент ИЛИ 87 срабатьшает от своего второго входа, связанного с выходом элемента И 86, на первый вход которого поступает

сигнал по шине первого входа блока 13 с выхода дешифратора 29, а на второй вход - тактовьй сигнал генератора 2 импульсов.

Режим работы устройства памяти, вьщаваемые по шинам второго выхода блока 13 могут быть заданы как аппаратно сигналами по щинам третьего входа блока 13 с триггеров 37, 38, так и программно сигналом дешифратора 29 (шина первого входа блока 13), причем устанавливающий режим задается значениями информационной части команды. 23 Для сбора диагностической информации устройства памяти (регистры 84), процессоров (регистры 51), про цессора обмена (регистр 70), третье го регистра 11 и второго регистра 10, для проверки работоспособности регистров в тестовом режиме, для определения текущего состояния (например, первого регистра 3, второго счетчика 4) обеспечивается возможность программного считывания содер жимого регистров и отдельных тригге ров предлагаемого устройства через блок 12 коммутатора. Считываемые данные с выхода блока 12 коммутатора далее по шинам второго выхода устройства через коммутатор ЦВМ поступают в процессор, вьптолняющий команду считывания. Кроме того, выход блока 12 коммутатора шинами вта рого выхода устройства связан с индикационной панелью пульта управления ЦВМ, данные на которую выбираются управляюищми сигналами, поступающими по пшнам третьего входа уст ройства на третий вход анализатора 1 командной информации. При этом на регистре 28 устанавливается код команды считьшания соответствующего регистра, причем выдача на индикацию обеспечивается в моменты незанятости регистра 28 обработкой команд какого-либо процессора, что обеспечивается элементом И 19., на первый вход которого поступают сигналы управления индикацией с пул rd управления ЦВМ, а на второй, третий и четвертый входы - сигналы регистра 15 через элементы НЕ 25-27 что является признаком незаня-гости предлагаемого устройства обработкой команд. Блок 12 коммутатора представляет собой группу элементов И, на первые входы которых поступают данные с регистров и триггеров пред лагаемого устройства по шинам второ го-девятого входов блока 12 коммута тора, а на вторые - соответствующие выходы дешифратора 29 по шинам первого входа блока 12 коммутатора. Выходы групп элементов И через элемент ИЖ подключены к шинам выхода блока 12 коммутатора. По сравнению с прототипом в данном устройстве случайный сбой является следствием изменения параметров вычислительной системы, таких как температура кристаллов микро24схем, напряжение питания, времязадержки на элементах, контактные явления и т.д., которые проявляются в течение некоторого промежутка времени, большего времени вьшолнения процессором одной.или нескольких команд. Следовательно, немедленная обработка сбоя может привести к неверной интерпретации сбоя и отказа. В предлагаемом устройстве по сигналу аппаратного контроля активный абонент (ЦП, ПО) исключается из системы с помощью регистров связи, что с .одной стороны, препятствует распространению ошибки, а с другой позволяет начать обработку сбоя через интервал времени, определяемый про- ; граммными средства ш. При неудачных повторениях возможны последующие повторения. По сравнению с прототипом предлагаемое устройство обеспечивает аппаратурную перегрузку ОС в случае ее недостоверности. Время нахождения ЦВМ в состоянии с исключением активным абонентом контролируется схемами, формирующими сигнал аппаратного контроля через некоторое время, если процессоры ЦВМ не успевают выполнить за это время определенных действий, и счетчиком, увеличивающим свои показания при каждом срабатывании данных схем. При его переполнении осуществляется перегрузка операционной системы. При хранении программ ОС в оперативной памяти возможна потеря этой информации при сбое схемы регенерации данных в накопителях полупроводниковой памяти. Появление САК схем регенерации определенных накопителей, вьщеленных для хранения программ и данньк ОС, также приводит к необходимости устранения последствий этого сбоя с помощью аппаратной перезагрузки ОС. Если текущая программа затрагивает программный код или данные ОС, то любой сбой в текущей программе приводит к недостоверности ОС, что может быть устранено только перегрузкой ОС, В предлагаемом устройстве для идентификации подобных программ введены триггеры, при наличии игналов которых сигнал аппаратного онтроля соответствукнцего устройства ызывает аппаратную перезагрузку ОС.

UZ.f

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1981 |

|

SU1003066A1 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Устройство для сопряжения цифровой вычислительной машины с линиями связи | 1979 |

|

SU864276A1 |

| Устройство для сопряжения двух вычислительных машин | 1983 |

|

SU1179312A1 |

| Мультиплексный канал | 1980 |

|

SU868743A1 |

| Устройство для обмена информацией между аналоговой и цифровой вычислительными машинами | 1990 |

|

SU1755372A1 |

| Устройство для управления обменом информацией между управляющим процессором и внешним устройством | 1988 |

|

SU1594552A1 |

| Устройство для сопряжения вычислительной машины с магистралью | 1981 |

|

SU980088A2 |

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1981 |

|

SU976437A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

УСТРОЙСТВО ДЛЯ ОБМЕНА ИНФОРМАЦИЕЙ, содержащее анализатор командной информации, первый, второй и третий входы которого соединены соответственно с первым, вторым и третьим йходами устройства, четвертый вход которого соединен с четвертым входом анализатора командной информации и первыми входами анализатора состояний и трек формирователей сигналов управления обменом, первые выходы KOTOi bix через первый счетчик соединены с вторым входом анализатора состояний, с третьего по шестой входы которого соединены с пятого по восьмой входами устройства соответственно, первый выход анализатора состояний соединен с входом генератора импульсов, первый выход анализатора командной информации соединен с первым входом блока коммутации, второй и третий входы которого соединены с вторыми выходами второго и третьего формирователей сигналов управления обменом, первьй регистр, выход которого соединен с . четвертым входом блока коммутации и первым выходом устройства, второй выход которого является выходом блока коммутации, второй и третий выходы соответственно первого, второго и третьего формирователей сигналов управления обменом являются третьим, четвертым и пятым выходами устройства соответственно, девятый, десятый и одиннадцатый входы устройства соединены с вторыми входами соответственно первого, второго и . третьего формирователей сигналов управления обменом, блок адресации, отличающееся тем, что, с целью повышения надежности, в него введены два регистра, счетчик и дополнительные блоки адресации, причем первый выход анализатора ко(Л мандной информации соединен с входом с первого регистра, седьмым входом .анализатора состояний, первым входом второго счетчика, первыми входами блоков адресации и третьими входами формирователей сигналов управления обменом, второй выход анализатора $ командной информации соединен с о вторым входом второго счетчика и 70 через генератор импульсов - с чето вертыми входами формирователей сиг«аь налов управления обменом, вторыми входами блоков адресации и восьмьм входом анализатора состояний, второй выход которого является шестым выходом устройства, в третий выход соединен с входами первого счетчика и второго регистра и с первым входом третьего регистра, выход которого соединен с входом первого счетчика, пятым входом блока коммутации и через второй регистр - с шестым входом блока коммутации, вторые выходы пер

Фиг. 2

(put. 3

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для сопряжения | 1980 |

|

SU926645A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-02-28—Публикация

1983-01-12—Подача