Изобретение относится к вычислительной и измерительной технике, а именно к цифровым приборам для измерения действующего значения сигнала, и может быть использовано в технике связи, в производстве и испытаниях различных радиоэлектронных приборов и систем, а также в процессе научных исследований.

Известны цифровые коррелометры, работающие в режиме измерения действующего значения сигнала. Этот измеритель содержит входной усилитель , генератор псевдослучайных чисел с коммутатором, два цифроаналоговых преобразователя, два компаратора, генератор тактовых импульс;ов, умножитель, интегратор, схему считывания и регистрирующее . устройство Ij.

Известен также коррелометрический измеритель, действующего значения сигнала, работающий на принципе стохастатического аналого-цифрового преобразователя сигналов, имеющий входной усилитель, два компаратора, генератор тактовых импульсов, генератор псевдослучайных чисел, цифроаналоговый преобразователь, источник постоянного напряжения, аналоговый сумматор, логический инвертор, две группы вентилей, решающий блок и регистрирующее устройство 2. Недостатком таких измерителей является ограниченное быстродействие, определяемое временем установления цифро-аналогового преобразователя.

Наиболее близким техническим ре10шением к изобретению является устройстЬо для измерения действующего значения сигнала, содержащее входной . усилитель , два компаратора, источник постоянного напряжения, ана15логовый сумматор, генератор тактовых импульсов, цифро-аналоговый преобразователь , два генератора псевдослучайных чисел, блок вычитания и переключатель, два накапливающих

20 алгебраических сумматора, два последовательных регистра сдвига, четыре элемента И, два элемента ИЛИ, три реверсивных счетчика, суммирующий счетчик, решающий блок и регистрирующий блок .

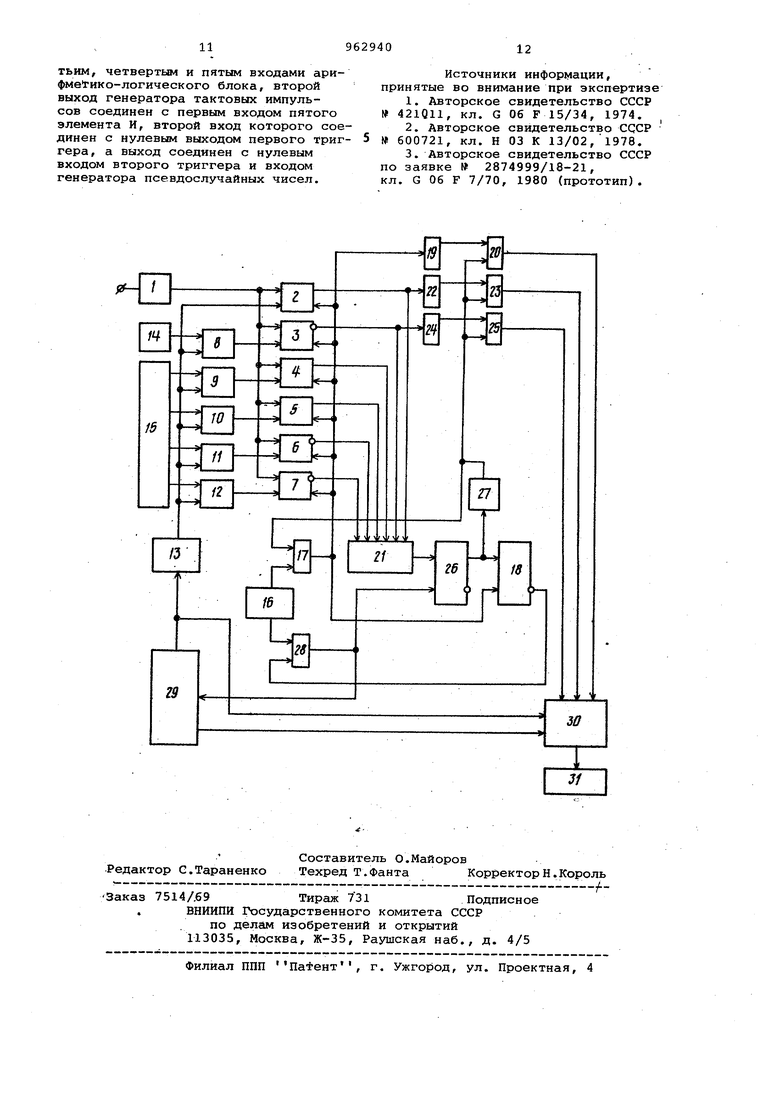

Минимальное время измерения действующего значения сигнала при помощи этого измерителя также ограничено временем установления цифро30аналогового преобразователя. Цель изобретения - повьошение быстродействия. Поставленная цель достигается те что в стохастическое устройство для определения действующего значения сигнала, содержащее входной усилитель, вход которого является входом {измерителя, первый и второй коммутаторы, первые входы которых соединены с выходом входного усилителя, первый аналоговый сумматор, выход которого соединен с вторым входом второго компаратора, источник постоянного напряжения, выход которого соединен с первым входом первого аналогового сумматора, цифро-аналоговый преобразователь, выход которого соединен с вторыми входами первого аналогового сумматора и первого компаратора, генератор псевдослучайных чисел, первый выход которого соединен с входом цифро-аналогового преобразователя, арифметико-логический блок, первый и второй входы кото рого соединены соответственно с первым и вторым выходами генератора псевдослучайных чисел, регистрирующий блок, вход которого соединен с выходом арифметико-логического блока, и генератор тактовых импульсов, дополнительно содержит блок источников постоянного напряжения, второй, третий, четвертый и пятый аналоговые сумматора, третий, четвертый, пятый и шестой компараторы, cS/ мматор по модулю два, однорибратор, первый и второй триггеры, первый, второй, тре тий, четвертыйи пятый элементы И, первый, второй и третий элементы задержки, причем первый, второй, третий и четвертый выходы блока источников постоянного напряжения соединены с первыми входами соответстве но второго, третьего, четвертого и пятого аналоговых сумматоров, вторые входы которых подключены к выходу цифро-аналогового преобразователя, выходы второго, третьего, четвертого и пятого аналоговых сумматоров соединены с первыми входами соответственно третьего, четвертого, пятого и шестого компараторов, вторые входы которых подключены к выходу входного усилителя, первый выход генератора тактовык импульсов соединен, с (первым входом первого элемента И, которого соединен с нулевым входом первого триггера, третьими входами первого, второго, третьего, четвертого, пятого и шестого компараторов и входом первого элемента задержки, входы ;второго; и третьего элементов задержки подкл1рчены к выходам соответственно первого и второго компараторов, а выходы первого, второго и третьего элементов задержки соединены с первыми входами соответственно второго, третьего и четвертого элементов И, выходы первого, второго, третьего, четвертого, пятого и шестого компараторов соединены с соответствующими входами сумматора по модулю два, выход которого соединен с единичным входом второго триггера, выход второго триггера соединен с единичным входом первого триггера и входом одновибратора, выход которого соединен со вторыми входами первого, второго, третьего и четвертого элемен- тов И, выходы второго, третьего и четвертого элементов И соединены соответственно с третьим, четвертым и пятым входами, арифметико-логического блока, второй выход генератора тактовых импульсов соединен с первым входом пятого элемента И, второй вход которого соединен с нулевым выходом первого триггера, а выход соединен с нулевым входом второго триггера и входом генератора псевдослучайных чисел. На чертеже представлена блок-схема устройства. Она содержит входной усилитель 1, первый 2, второй 3, третий 4, четвертый 5, пятый б и шестой 7 компараторы, первый 8, второй 9, тветий 10, четвертый И и пятый 12 аналоговые сумматоры, цифро-аналоговый преобразователь 13, источник 14 постоянного напряжения,блок 15 источников постоянного напряжения, генератор 16 тактовых импульсов, первый элемент И 17, первый триггер 18, первый элемент 19 задержки, второй элемент И 20, сумматор 21 по модулю два, второй элемент 22 задержки, третий элемент И 23, третий элемент 24 задержки, четвертый элемент И 25, второй триггер 26f одновибратор 27, пятый элемент И 28, генератор 29 псевдослучайных чисел, арифметикологический блок 30, регистрирующий блок 31, Арифметико-логический блок 30 состоит из двух накапливающих сумматоров, двух последовательных регистров сдвига, четырех элементов И,. двух элементов ИЛИ, трех реверсивных счетчиков,. суммирующего счетчика и решающего устройства, соединенных соответствующим образом для реализации алгоритма в соответствии с формулой (1). Выход входного усилителя 1 соединен с первыми входами первого 2, второго 3 компараторов и с . вторыми входами третьего 4, четвертого 5, пятого 6 и шестого 7 компараторов. Выход источника 14 постоянного напряжения соединен с первым входом первого аналогового сумматора 8. Первый,, второй, третий и четвертый выходы блока 15 источников постоянного напряжения соединены с первыми входами соответственно второ го 9, третьего 10, четвертого 11 и пятого 12 аналоговых сумматоров. Выход цифро-аналогового преобразователя 13 соединен с вторыми входами аналоговых сумматоров 8-12 и первого компаратора 2. Выходы первого 8, второго 9, третьего 10, четвертого 11 и пятого 12 аналоговых сумматоров соединены соответственно с вторым входом второго компаратора 3 и первыми входами третьего 4, четвертого 5, пятого б и шестого 7 компараторов Прямой выход первого компаратора 2 соединен с входом второго элемента 22 задержки и первым входом суммато ра 21 по модулю два. Инверсный выход второго компаратора 3 соединен с входом третьего элемента 24 задержки и вторым входом сумматора 21 по модулю два. Прямые выходы третьего 4 , четвертого 5 компараторов и инверсные выходы пятого 6 и шестого .7 .компараторов соединены соответственно с третьим, четвертым, пятым и шестым входами сумматора 21 по модулю два, выход которого соединен с единичным входом второго триггера 26. Выходы первого 19, второго 22 и третьего 24 элементов задержек coe динены с первыми входами соответственно второго 20, третьего 23 и четвертого 25 элементов И, выходы которых соединены соответственно с третьим, четвертым и пятым входами арифметико-логического блока 30. Первый вход блока 30 соединен с пер вым выходом генератора 29 псевдослучайных чисел и входом цифро-аналогового преобразователя 13, второй вход соединен с вторым выхЬдом генератора 29 псевдослучайных чисел, а выход - с входом регистрирующего блока 31. Первый выход генератор 16 тактовых импульсов соединен с первым входом первого элемента И, второй вход которого соединен с выходо одновибратора 27 и вторыми входами второго 20, третьего 23 и четвертого 25 элементов И, Выход первого эл .,„т 1я 1-7 -«„,,.-,. „ ™,„,т,г,,.,,, „мента И 17 соединен с третьими вход ми компараторов 2-7, входом первого элемента 19 задержки и нулевым входом первого триггера 18, единичный вход которого -соединен с единичным выходом второго триггера 26 и входо одновибратора 27. Второй выход гене тора 16 тактовых импульсов соединен с первым входом пятого элемента И 2 второй вход которого соединен с нулевым выходом первого триггера 18, выход - с нулевым входом второго триггера 26 и входом генератора 29 псевдослучайных чисел. Устройство работает следующим об разом. Оценка действующего значения к, змеряемого сигнала x{t) определятся в соответствии с формулой л /2 N п t nf 3 N J, де „ - k-я реализация-псевдослучайного числа на первом выходе генератора 29 псевдослучайных чисел еГо, , реализация псевдослучайного числа на втором выходе генератора 29 псевдослучайных чисел; -выходной сигнал первого компаратора 2. 1, если (b.-1); ,. 0,если x(t) (-1); -инверсия выходного сигнала второго компаратора 3; 1,если x(t),«q( -1) ; , . О, если x((J -1); q - предел измерения; N - количество тактов дискретизации за время из мерения. Сигнал x(t) приводится в область х (t),q во входном усилителе I и поступает на- первые входы компараторов 2 и 3 и вторые входы компараторов 4-7. На вторые входы компаратора 2 и аналоговых сумматоров 8-12 поступает аналоговый псевдослучайный опорный сигнал 0 qe{0,qj, образованный в цифро-аналоговом преобразователе 13 в соответствии с кодом чисел | , поступающих с первого выхода генератора 29 псевдослучайных чисел. На первый вход аналогового сумматора 8 поступает напряжение -q от источника 14 постоянного напряжения, и на выходе аналогового сумматора 8 образуется псевдослучайный аналоговый сигнал D 4fOJr который поступает в качестве опорного сигнала на второй вход компаратора 3.На первые входы аналоговых сумматоров 9-12 с первого,второго третьего и четвертого выходов блока 15 источников постоянного напряжения поступает напряжение соответственно Г й -Ч+дд и -q-aq. где uq а разрядность псевдослучайных чисел 5 1 ; пХ.(1-5) выбирается в зависимости от параметров примененного в предлагаемом устройстве цифро-аналогового преобразователя 13. На выходе аналоговых сумматоров 9-12 образуется псевдослучайный опорный сигнал для компараторов 4-7. Компараторы 2, 4 и 5 работают в области положительных значений сигнала x(t) и опорные сигналы вспомогательных компараторов 4 и 5 отличаются от опорного сигнала осно ного компаратора. 2 только на величину ±дд. Аналогично, компараторы 3, б и 7 работают в области отрицательных значений сигнала x(t), при этом опорные сигналы вспомогательных компараторов б и 7 отличаются от опорного сигнала основного компаратора 3 только на величину ±дд. Вспомогательные компараторы 4-7 работают аналогично основным компараторам 2 и 3 и имеют выходные сигналы соответственно ++ I 1, если K(t},.-7/q- +c ; к /О, если к{t) II, если x(t)/qJ к I О, если х( t)q-А-дд; 1, если х{1))+дд; 0,если x(t)7q(( -l)+дq; 1,если x(t);fq(()-uq; 0, если x{t)(-l)-дq. Тактовь.е импульсы с первого выхо да генератора 16 тактовых импульсов через элемент И 17 поступают на тре тьи входы компараторов 2-7, на нуле вой вход первого триггера 18 и через элемент 19 задержки на первый вход элемента И 20. Тактовые импульсы с второго выхода генератора 16 тактовых иьшульсов через эл мент И 28 поступают на нулевой вход второго триггера 26 и на вход генератора 29 псевдослучайных чисел. Выходные сигналы , п и nj ком раторов 2, 4 и 5 и инверсные выходные сигналы п, п компараторов 3, б и 7 возникают в момент поступления тактовых импульсов в результате сравнения значения сигнала x{t) со значениями соответствующих опорных сигналов и поступают на вхо ды сумматора 21 по модулю два. Сигналы и кроме того, поступают Соответственно через элементы 22 и 24 задержки на первые входы элементов И 23 и 25. На вторые входы элементов И 20, 23 и 25 в исходном состоянии с выхода одновибратора 27 поступает разрешающий сигнал. Таким образом, в исходном состоя нии с первого и второго выходов генератора 29 псевдослучайных чисел на первый и второй входы арифметико логического блока 30 соответственно поттупают сигналы и , а на третий, четвертый и пятый входы бло ка 30 с выходов элементов И 20, 23 и 25 поступают соответственно такто вые импульсы, сигналы и . При этом арифметико-логический блок 30 набирает отсчеты для оценки х действующего значения сигнала x(t) в соответствии с формулой(1). Выходной сигнал сумматора 21 по модулю два появляется только в случае, если , или или п п, т.е. если значение Х| измеряемого сигнала x(t) находится в пределах UOK K UOK АЧ . В этом случае .выходной сигнал сумматора 21 по модулю два перебрасывает триггер 26 и далее триггер 18 в состояния Ч и запускает одновибратор 27..При этом с нулевого выхода триггера 18 поступает запрет на элемент И 28, а с выхода одновибратора 27 - запрет на элементы И 17, 20, 25 и 25. Длительность временного интервала одновибратора 27 Q выбирается равной времени установления примененного в предлагаемом устройстве цифро-аналогового преобразователя, и на время tg поступление тактовых импульсов на третьи входы компараторов 2-7 и на вход генератора 29 дискретных псевдослучайных чисел прекргидается. Длительность задержки сигналов в элементах 22 и 24 задержки должна быть больше суммарной задегжки распространения сигнала в блоке 21, триггере 26, в одновибраторе 27. Длительность задержки тактовых импульсов в элементе 19 задержки должна быть ольше суммарной задержки распространения сигнала с третьих входов компараторов 2-7, сумматоре 21 по модулю два, в триггере 26 и в одновибраторе 27. Поэтому в случае срабатывания сумматора 21 по модулю два и триггеров 26 и 18 соответствующий тактовый импульс и соответствующие сигналы Н в арифметикологический блок 30 не попадают и им не учитываются. За время Tg выходной сигнал цифро-аналогового пр еобразователя 13 устанавливается с заданной предельной точностью. После истечения времени Т одновибратор 27 открывает элементы И 17, 20, 23 и. 25 и очередной тактовый импульс с первого выхода генератора 16 тактовых импульсов через элемент И 17 производит повторный опрос компараторов 2-7 и по нулевому входу возвращает в исходное состояние триггер 18, который посылает разрешающий сигнал на элемент И 28. Очередной тактовый импульс со второго выхода генератора 16 тактовых импульсов через элемент И 28 возвращает в исходное состояние триггер 26 и переключает в следующее состояние генератор 29 псевдослучайных чисел. .С целью исключения возможного повторного срабатывания триггера 26 задержка тактовых импульсов, поступающих со второго выхода генератора 16 тактовых импульсов , по отношению к тактовым импульсам, поступающим с первого выхода этого генератора, должна быть больше, чем суммарная задержка распространения сигнала по третьему входу компараторов 2-7 и сумматора 21 по .модулю два. Далее устройство работа ;аналогичным образом, арифметикологический блок 30 накапливает оцен ку 5k9 действующего значения сигнала x(t) и передает ее на регистрирующий блок 31. , В предлагаемом устройстве по сра нению с другими устройствами аналогичного назначения можно значитель но повысить частоту следования тактовых импульсов и тем самым сократить время измерения. В данном случае эт частота определяется в основном тол ко быстродействием примененных компараторов и элементов дискретной техники и. мало зависит от времени установления цифро-аналогового пре образователя. Коэффициент А повышения быстродействия предлагаемого устройства сравнению с прототипом можно оцени по следующей формуле: t-JCTUAn . время установления цифро-аналогового пр образователя, не; -время задержки распространения сигнала в компараторе со стробирующего входа, не; - среднее время задержки распространения сигнала выбранной серии логических интегральных схем, не; Например, если в устройстве выбраны цифро-аналоговый преобразователь (ЦДЛ) с временем установления Цстцдп 300-350 НС, компараторы типа 521СА4 или 597СА2, а все цифровые элементы - микросхемы серии 155, тогда предлагаемое устройство имеет не менее, чем в 5 раз большее быстродействие по сравнению с прототипом . Формула изобретения Стохастическое устройство для определения действующего значения сигнала, содержащее входной усили- тель, вход которого является входом измерителя, первый и второй компар торы, первые входы которых соедине с выходом входного усилителя, первы аналоговый сумматор, выход которог соединен с вторым входом второго компаратора, источник постоянного пряжения, выход которого соединен первым входом первого аналогового сумматора, цифро-аналоговый преобр зователь, выход которого соединен вторыми входами первого аналогового сумматора и первого компаратора, генератор псевдослучайных чисел, первый выход которого соединен с входом цифро-аналогового преобразователя, арифметико-логический блок, первый и второй входы которого соединены соответственно с первым и вторым выходами генератора псевдослучайных чисел, регистрирующий блок, вход которого соединен с выходом арифметико-логического блока, и генератор тактовых импульсов, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, он содержит блок источников постоянного напряжения, второй, третий, четвертый и пятый аналоговые сумматоры, третий, четвертый, пятый и шестой компараторы, -сумматор по модулю два, одновибратор, первый и второй триггеры, первый, второй, третий, четвертый и пятый элементы И, первый, второй, третий элементы задержки, причем первый, второй, третий и четвертый выходы блока источников постоянного напряжения соединены с первыми входами соответственно второго, третьего, четвертого и пятого аналоговых сумматоров, вторые входы которых подключены к выходу цифро-аналогового преобразовате- ля, выходы второго, третьего, четвертого и пятого аналоговых суммато,ров соединены с первыми входами соот-; ветственно третьего, четвертого, пятого и шестого компараторов, вторые входы которых подключены к выходу входного усилителя, первый выход генератора тактовых импульсов соединен с первым входом первого элемента И, выход которого соединен с нулевым входом первого триггера, третьими входами первого, второго, третьего, четвертого, пятого и шестого компараторов и входом первого элемента задержки, входы второго и третьего элементов задержки подключены к выходкам соответственно первого и второго компараторов, а выходы первого, второго и третьего элементов, задержки соединены с первыми входами соответственно второго, третьего и четвертого элементов И, выходы первого, второго, третьего, четвертого, пятого и шестого компараторов соединены с соответствующими входами сумматора по модулю два, выход которого соединен с единичным входом второго триггера, выход второго триггера соединен сг единичным входом первого триггера и входом одновибратора, выход которого соединен с вторыми входами первого, второго, третьего и четвертого элементов И, выходы второго, третьего и четвертого элементов И соединены соответственно с тре

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регистрации информации | 1985 |

|

SU1304170A1 |

| Коррелометр | 1980 |

|

SU940171A2 |

| ЧАСТОТОМЕР ДЛЯ ПРОМЫШЛЕННЫХ ЭЛЕКТРИЧЕСКИХ СЕТЕЙ | 2006 |

|

RU2326390C1 |

| Устройство для синхронизации шумоподобных сигналов | 1982 |

|

SU1022326A1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ ПРОФЕССИОНАЛЬНОЙ ПРИГОДНОСТИ ОПЕРАТОРОВ | 1991 |

|

RU2020598C1 |

| Вероятностный интегрирующий преобразователь аналог-код | 1987 |

|

SU1441476A1 |

| Стохастический измеритель действующего значения периодического сигнала | 1980 |

|

SU869019A1 |

| Устройство для измерения времени задержки отсчета аналого-цифровых преобразователей | 1985 |

|

SU1280697A1 |

| Синтезатор частот | 1982 |

|

SU1067603A1 |

| Устройство для синтеза речи | 1982 |

|

SU1095167A1 |

Авторы

Даты

1982-09-30—Публикация

1981-01-12—Подача