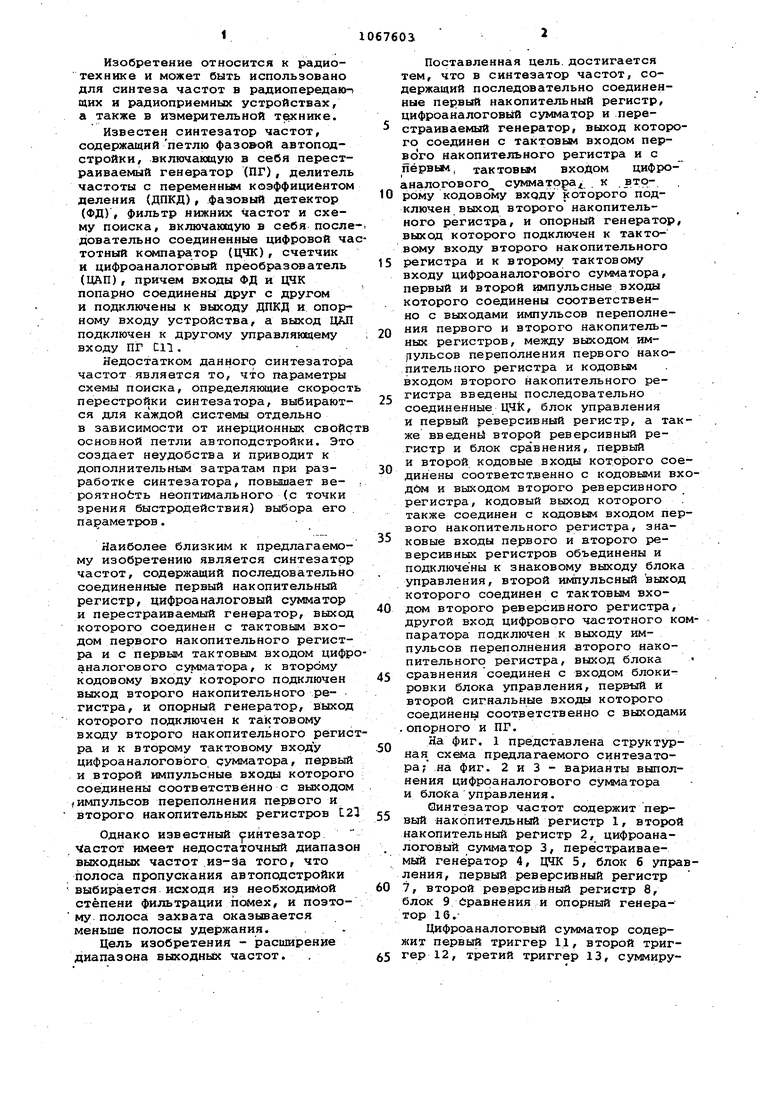

Изобретение относится к радиотехнике и может быть использовано для синтеза частот в радиопередаки щих и радиоприемных устройствах, а также в иэмерительной технике. Известен синтезатор частот, содержгицийпетлю фазовОй автоподстройки, включающую в себя перестраиваемый генератор (ПГ), делитель частоты с переменным коэффициентом деления (ДПКД), фазовый детектор (ФД), фильтр нижних частот и схему поиска, включающую в себя после довательно соединенные цифровой ча тотный компаратор (ЦЧК), счетчик и цифроаналоговый преобразователь (ЦАП), причем входы ФД и ЦЧК попарно соединены друг с другом и подключены к выходу ДПКД и опорному входу устройства, а выход ЦАП подключен к другому управляющему входу ПГ СИ.. Недостатком данного синтезатора частот является то, что параметры схемы поиска, определяквдие скорост перестройки синтезатора, выбираются для каждой системы отдельно в зависимости от инерционных свойс основной петли автоподстройки. Это создает неудобства и приводит к дополнительным затратам при разработке синтезатора, повышает вероятноЬть неоптимального (с точки зрения быстродействия) выбора его параметров. Наиболее близким к предлагаемому изобретению является синтезатор частот, содержащий последовательно соединенные первый накопительный регистр, цифроаналоговый cy ямaтop и перестраиваемый генератор, выход которого соединен с тактовым входом первого накопительного регистра и с первым тактовым входом цифр аналогового сумматора, к второму кодовому входу которого подключен выход второго накопительного регистра, и опорный генератор, выход которого подключен к тактовому входу второго накопительного регис ра и к второму тактовому входу цифроаналогового сумматора, первый и второй импульсные входам которого соединены соответственно с выходом (ИМПУЛЬСОВ переполнения первого и второго накопительных регистров L2 Однако известный ринтезатор Частот имеет недостаточный диапазо выходных частот иэ-За того, что полоса пропускания автоподстройки выбирается исходя из необходимой степени фильтрации помех, и поэто му полоса захвата оказывается меньше полосы удержания.. Цель изобретения - расширение диапазона выходньк частот. . Поставленная цель, достигается тем, что в синтезатор частот, содержащий последовательно соединенные первый накопительньЛ регистр, цифроаналоговьгй сумматор и перестраиваемый генератор, выход которого соединен с тактовым входом первого накопительного регистра и с пёрвьм, тактовБМ входом цифроаналогового сумматора , к JBTOрбму кодовому входу которого подключен выход второго накопительного регистра, и опорный генератор, выход которого подключен к тактовому входу второго накопительного регистра и к второму тактовому ВХОДУ цифроаналогового сумматора, первый и второй импульсные входы которого соединены соответственно с выходами импульсов переполнения первого и второго накопительных регистров, между выходом имрульсов переполнения первого накопительного регистра и кодовьфл входом второго накопительного регистра введены последовательно соединенные ЦЧК, блок управления и первый реверсивный регистр, а также введенй вторсэй реверсивный регистр и блок сравнения, первый и второй кодовые входы которого соединены соответственно с кодовыми входОм и выходом второго реверсивного регистра, кодовый выход которого также соединен с кодовым входом первого накопительного регистра, знаковые входы первого и второго реверсивных регистров объединены и подключены к знаковому выходу блока управления, второй ш шульсный ыход которого соединен с тактовым вхоROM второго реверсивного регистра, другой вход цифрового частотного компаратора подключен к выходу импульсов переполнения второго накопительного регистра, выход блока сравнения соединен с входом блокировки блока управления, первой и второй сигнальные входы которого соединены соответственно с выходами опорного и ПР. На фиг. 1 представлена структурная схема предлагаемого синтезатора; на фиг. 2 и 3 - варианты выполнения цифроаналогового cyNwaTopa и блока управления. Иинтезатор частот содержит первый накопительный регистр 1, второй накопительный регистр 2, цифроанаоговый сумматор 3, перестраиваеый генератор 4, ЦЧК 5, блок б управения, первый реверсивный регистр 7, второй рев.ерсивный регистр 8, лок 9 Сравнения и опорный генераор 10. Цифроаналоговый сумматор содерит первый триггер 11, второй тригер 12, третий триггер 13, суммируюций цифроаналоговый преобразователь 14 и фильтр 15 нижних частот.

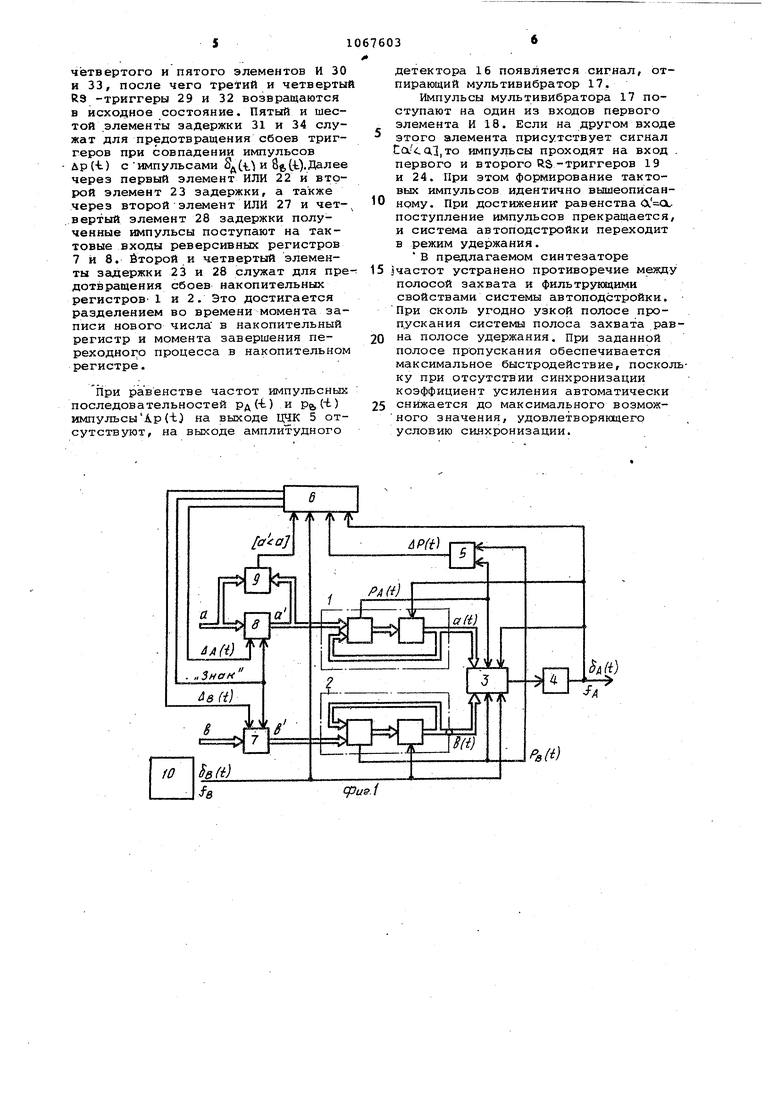

Блок управления включает в себя амплитудный детектор 16, мультивибратор 17, первый элемент И 18, Й8-триггер 19, второй элемент И- 20, первый элемент 21 задержки., первый элемент ИЛИ 22, второй элемент 23 задержки, второй RS-триггер 24, третий элемент И 25, третий элемент 26 задержки, второй элемент ИЛИ 27, четвертый элемент. 28 задержки, третий ЯЗ-триггер 29, четвер тый элемент И 30, пятый элемент 31 задержки, четвертый ЯЗ-триггер 32, пятый элемент И 33, и шестой элемент 34 задержки.

Синтезатор частот работает следующим образом.

Накопительные регистры 1 и 2 тактируются импульсами с выхода ПГ 4 и с выхода опорного генератора 10. Под действием тактовых импульсов Sft trt) с частотой Ед поступающих от перестраиваемого генератора 4, содержимое л (-t) накопительного регистра 1 возрастает с каждьм импульсом на величину Oi , задаваемую этим числом на кодовом входе накопитeль oгo регистра 1. Аналогичным образом действует накопительный регистр 2, формируя функцию Bbfc) возрастаюцую на величину 6; при поступлен ии на его тактовый вход импульсов опорной последовательности 2б (.t) с частотой в.. Изэа ограниченности емкости q, накопительных регисгров 1 и 2 огибающие процессов a(;fc) и 6{-t) представляют собой пилообразные функции, средняя частота каждой из которых соответственно равна ift-a/q, и iu-S/q, . В .цифроаналоговом сумматоре 3 функ:ция CV(t) суммируется с функцией 6(t) снимаемой с инверсных выходов накопительного регистра 2, результат суммирования преобразуется в анап логовую форму и поступает на управ.ление частотой ПГ 4.

Первый и второй реверсивные регистры 7 и 8 преобразуют числа о.. и i, поступающие на их входы, в соответствующие им числа 6 ft и Л 4- сх. Число Сх на выходе второго реверсивного регистра 8 сравнивается о исходным числом о. в блоке 9 сравнения, который выдает сигнал в блок 6 управления при услов.ии ..В бло 6 управления поступает также сигнал с выхода цифрового частотного компаратора 5, который в случае неравенства частот импульсов переполнения Рд (t) и. Pg, (t) при отсутствий синхро.низации вырабатывает импульсы xp{t) с разностной частотой. Блок 6 управления тактируется импульсами Зд (-t)

перестраиваемого генератора 4 и импульсами fi(i) опорного генератора 10 Если в синтезаторе нет синхронизма, выходные импульсы цифрового частотного компаратора 5 преобразуются блоком 6 управления в сигнал на знаковом выходе, переводящий первый и второй реверсивные регистры 7 и 8 в режим сдвига чисел 6 и о вправо. Под действием тактовых импульсов с первого и второго импульсных вькодов блока 6 управления числа б и сх уменьшаются, .крутизна характеристики фазового детектирования падает до тех прр, пока коэффициент усиления системы не входит в соответствие с инерционностью цифроаналогового сумматора 3, определяемой расположенным в нем фильтром нижних частот 15. Происходит синхронизация системы, импульсы на выходе цифрового частотного компаратора 5 исчезают, и блок 6 управления переводит первый и второй реверсивные регистры 7 и 8 в режим сдвига чисел

€ и О- влево. Сдвиг чисел влево происходит до выполнения условия a cv при котором сигнал принимает значение нуль, и поступление импульсов с первого и второго импульсных выходов блока 6 управления прекращается.

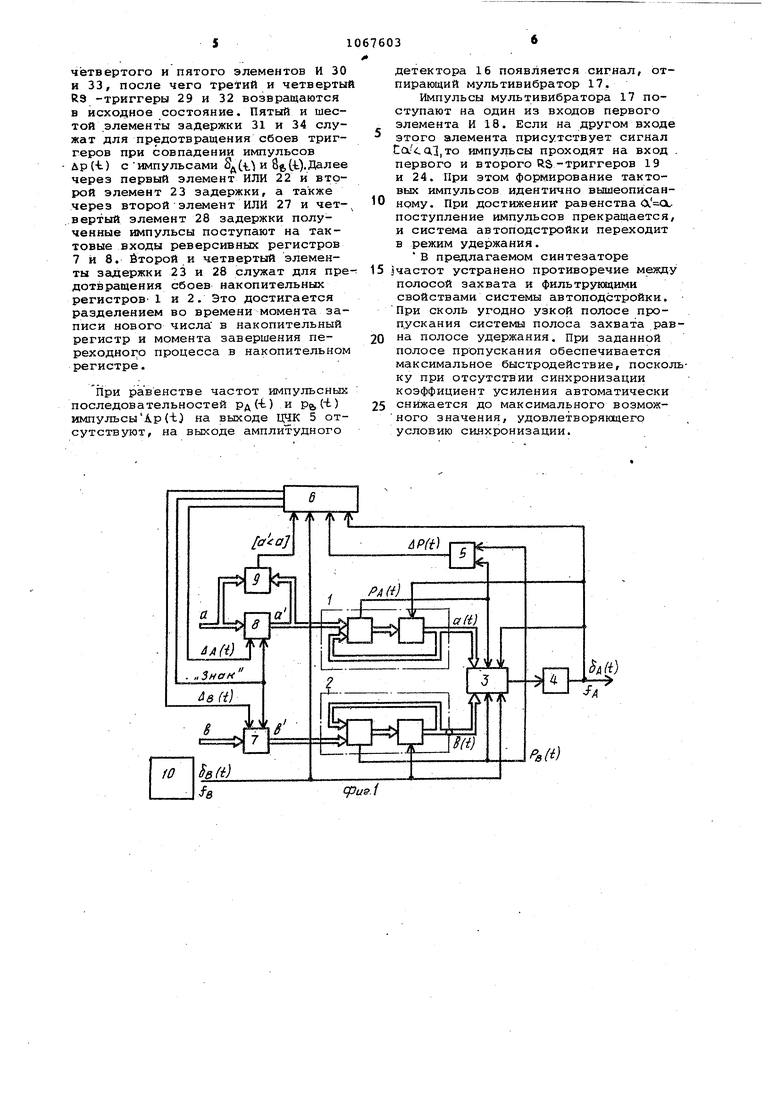

Один из вариантов выполнения .цифроаналогового сумматора (фиг.2) включает первый и второй триггеры 1 и 12, в которые записывают импульсы переполнения p(t) и P(t) с помощью соответствующих тактовых импульсов Оь и SB W,чем : Обеспечивается заддржка на один

такт переключений третьего тригге-. ра 13 относительно переполнения на-г копительных регистров 1 и 2. Кодовы .сигналы aCt). и 6 (-t) поступают-на Входы суммирующего цифроаналогового преобразователя 14, к входу старшего разряда которого подключен выход

третьего триггера 13.

1. . -..

На фиг. 3 показан пример выполнения блока управления.

При неравенстве частот импульсных последовательностей Рд(t) и pgH) на выходе цифрового част.отного компаратора 5 появляются импульсы A.p{-fc) с разностной частотой F-l(.f6), На выходе амплитудного детектора 16 появляетсяпри этом сигнал, устанавливающий первый и второй реверсивные регистры 7 и В в режим уменьшения чисел QL и б . Этот же сигнал запирает мультивибратор 17. Импульсы &p(i.) поступают также йа входы третьего и четвертого RS-триггеров 29 и 32.и переводят их в состояние, разрешающее прохождение импульсам д (t) и ) соответственно на вькоды

четвертого и пятого элементов И 30 и 33, после чего третий и четверты R3 -триггеры 29 и 32 возвращаются в исходное состояние. Пятый и шестой ,элементы задержки 31 и 34 служат для предотвращения сбоев триггеров при совпадении импульсов ДР (-t) с импульсами ,) и 8g,{t).Далее через первый элемент ИЛИ 22 и второй элемент 23 задержки, а также через второй элемент ИЛИ 27 и четвертый элемент 28 задержки полученные импульсы поступают на тактовые входы реверсивных регистров 7 и 8. ёторой и четвертый элементы задержки 23 и 28 служат для предотвращения сбоев накопительных регистров 1 и 2. Это достигается разделением во времени момента записи нового числа в накопительный регистр и момента завершения переходнозро процесса в накопительном регистре.

ПРИ равенстве частот импульсных последовательностей рд{-Ь) и РьН) импульсы 4p(t) на выходе ЦЧК 5 отсутствуют, на выходе амплитудного

детектора 16 появляется сигнал, отпирающий мультивибратор 17.

Импульсы мультивибратора 17 поступают на один из входов первого элемента И 18. Если на другом входе

этого элемента присутствует сигнал Сасо.1,то импульсы проходят на вход . первого и второго t S-триггеров 19 и 24. При этом формирование тактовых импульсов идентично вышеописанному. При достижении равенства поступление импульсов прекращается, и система автоподстройки переходит в режим удержания.

В предлагаемом синтезаторе

зчастот устранено противоречие между полосой захвата и фильтрукнцимн свойствами системы автоподстройки. При сколь угодно узкой полосе пропускания системы полоса захвата равна полосе удержания. При заданной полосе пропускания обеспечивается максимальное быстродействие, поскольку при отсутствии синхронизации коэффициент усиления автоматически

снижается до максимального возможного значения, удовлетворяющего условию синхронизации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1982 |

|

SU1117839A1 |

| Синтезатор частот | 1983 |

|

SU1202054A1 |

| Устройство стабилизации частоты управляемого напряжением генератора | 1987 |

|

SU1418897A1 |

| Делитель-синтезатор частот | 1982 |

|

SU1149395A1 |

| Синтезатор частот | 1983 |

|

SU1169165A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ПЛОТНОСТИ РАСПРЕДЕЛЕНИЯ ВЕРОЯТНОСТЕЙ СЛУЧАЙНОГО ПРОЦЕССА | 2000 |

|

RU2174706C1 |

| СИНТЕЗАТОР ЧАСТОТ | 1990 |

|

RU2030829C1 |

| Формирователь сигналов с заданным законом изменения фазы | 1986 |

|

SU1385239A1 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| Цифровой синтезатор частоты | 1986 |

|

SU1365345A1 |

СИНТЕЗАТОР ЧАСТОТ, содержащий последовательно соединенные первый накопительный регистр, цифроаналоговый сумматор и перестраиваемый генератор, выход которого соединен с тактовьам-входом первого накопительного регистра и с первым тактовым.входом цифроаналогового сумматора, к второму кодового входу которого подключен выход второго накопительного регистра, и опорный генератор, выход которого подключен к тактовому входу второго накопительного регистра и к второму .тактовому входу цифроаналогового сумматора, первый и второй импульсные входы которого соединены соответственно с выходом импульсов переполнения первого и второго накопительного регистров , отличающийся т.ем, что, с целью расширения диапазона выходных частот, между выходом э пульсов переполнения первого накопительного регистра и кодовым входом второго накопительного регистра введены последовательно соединенные цифровой частотный компаратор, блок управления и первый реверсивный регистр, а также введены второй реверсивный регистр и блок сравнения, первый и второй кодовые входы которого соединены соответственно с кодовыми входом и выходом второго реверсивного регистра, кодовый выход которого также соединен с кодовым, входом первого накопительс S ного регистра, знаковые входы первого и второго реверсивных регистров объединены и подключены к знаковому выходу блока управления, второй ш пульсный выход которого соединен с тактовым входом второго реверсивного регистра, другой вход цифрового частотного компаратора подключен к выходу импульсов переполнения второго накопительО ного регистра, выход блока сраво нения соединен с входом блокиров;КИ блока управления, первый и вто-4 рой сигнальные входы которого соо: единены соответственно с выходами опорного и перестраиваемого генео со раторов .

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Накладной висячий замок | 1922 |

|

SU331A1 |

| Патент США № 3913028, кл | |||

| Накладной висячий замок | 1922 |

|

SU331A1 |

Авторы

Даты

1984-01-15—Публикация

1982-05-27—Подача