Изобретение относится к контрольнo-измepитeл нoй технике и может быть использовано для контроля линейных интегральных схем.

Известно устройство для контроля . линейных интегральных схем, содержащее задатчик питания и компаратор.

Однако это устройство характе- ризуется низкой достоверностью контроля Обусловленной тем, что напряжение питания задаетсй дискретно, в статическом режиме, что не позволяет обнаруживать превышения тока потребления во всем диапазоне и контролировать непрерывность и отсутствие выбросов тока питания.

Наиболее близким к предлагаемому, является характериограф ПНХТ-2 содержащий синхронизатор, генератор линейно-нарастающего напряжения,, резистор и электроннолучевую трубКУ12 .

Недостатком этого устройства является низкая производительность, обусловленная необходимостью визуального контркэля характеристик и низкая достоверность, обусловленная т&л, что человек-оператор не обнаруживает

кратковременные относительно длитель- ности развертки выбросы на характеристиках , обусловленные нарушением

с непрерывности нарастания тока питания.

Цель изобретения - повыиение достоверности контроля и производительности устройства. .

Поставленная цель достигается

10 тем что в устройство ,для контроля интегральных схем, содержащее синхронизатор, соединенный первым выходом с входом генератора линейно-нарастающего напряжения, соединенного

tS выходом с первым выводом резистора, введены блок цифрового отсчета вре, мени, дифференцирующий блок, блок сравнения, пороговый блок, блок анализа, индикатор и KONMyTaTop, сое20диненный первым входом с вторым выходом синхронизатора, первым, вторым и третьим выходами - с соответствующими входами контролируетлой интегральной схекы, вторым входом 25с общей шиной устройства, третьим входом - с вторым выводом резистора и первым входсил дифференцирующего блока, соединенного вторым входом с первым выводом резистора, выходом

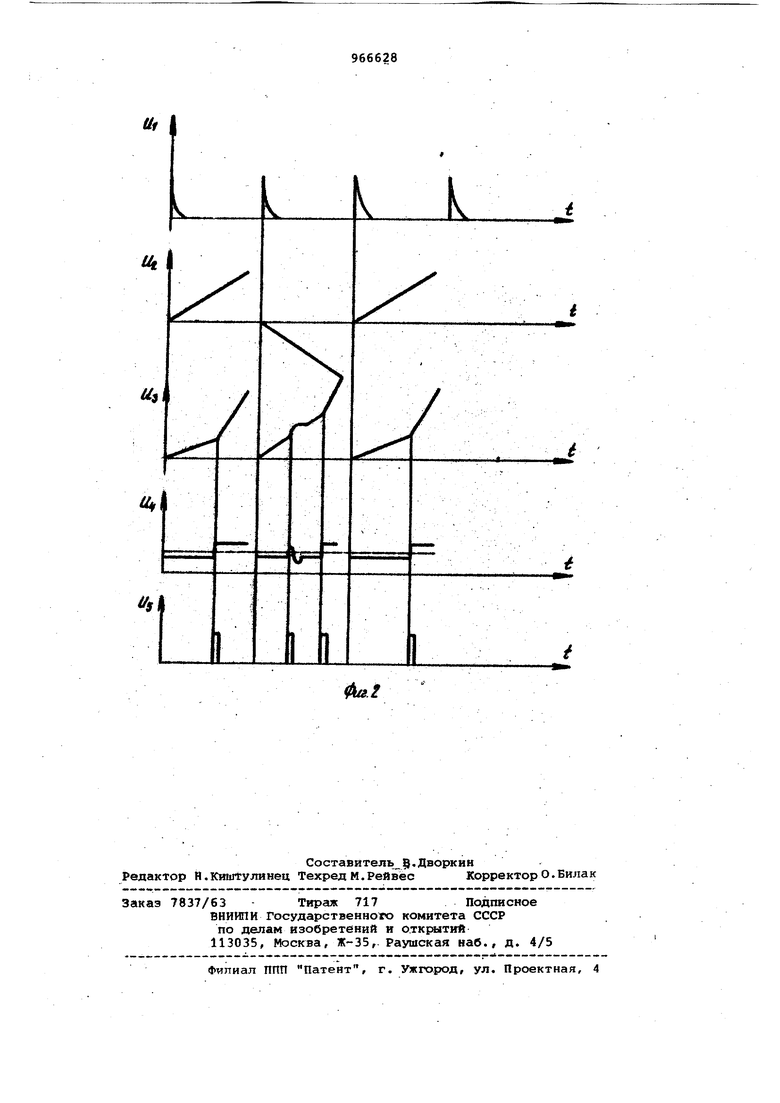

30 через пороговый блок - с первым вхОдОм блока сравнения и блока цифрового отсчета времени, второй вход к iToporo соединен с первым выходом синхронизатора/ выход - с вторым входом блока сравнения, соединенного, выходом через блок анализа с входом индикатора. На фиг. 1 приведена блок-схема устройства на фиг. 2 - временные диаграммы его работы. На фиг. 2 - приняты обозначенияf и. - напряжение на первом выходе синхронизатора; и - выходное напряжение генератора линейно нарастающего напряжеаия U-- входное напряжение дифференцирующего блока, и - выходное напряжение дифферен UHpsToajero блока; Ц - выходное напряжение порогового блока. Устройство содержит синхронизатор 1 генератор 2 линейно-нарастающего напряжения 2, коммутйтор 3, и дикатор 4/ резистор 5, дифференциру щий блок б, пороговый блок 7, блок цифрового отсчет а времени, блок 9 сравнения/ блок 10 анализа контролируемая интегральная схема 11 в со тав устройства не входит и показана для пояснения принципа действия устройства). Устройство работает следующим об разом. Синхронизатор 1 выдает с первого выхода запускающий ишульс на вход генератора; 2, а со второго вывода на вход коммутатора 3. Под действиеем управляющего импульса коммутатор устанавливается в положение, при котором общая шина устройства сое диняется с выводом Земля интег радьной схемы 11, а выход генератора 2 соединяется с выводом питания положительной полярности интегральной схемы 11. Синхронизатор 1 формирует эапускакяций импульс на генератор 2 с задержкой относительно импульса Hai коммутатор 3 после чего генератор 2 начинает вырабатывать линейно-нарас тающее положительное напряжение Uj, поступающее через резистор 5 и тйтор 3 на вывод питания положительной полярности интегральной схемы 1 (фиг. 2).. Одновременно с запусксм генератора 2, синхронизатор 1 запускает блок 8 цифрового отсчета времени, которыйотсчитывает в двоичном коде время нарастания напряжения питания на входе контролируемой интегральной схемы И до момента пробоя или нарушенкя непрерывности нарастания питания. В связи с тем, что напряжение питания возрастает по линейному закону, цифровой отсчет времени в блоке пропорционален текущему значению напряжения питания. Блок 6 дифференцирует,поступающее иа его вход линейно-возрастающее напряжение iJ-и на выходе вырабатывает постоянное напряжение и, поступающее на вход порогового блока 7. Крутизна нарастания напряжения U и порог срабатывания блока 7 подобр ны так, что при заданной крутизне нарастания и, пороговый блок 7 не срабатывает. При увеличении крутизны нарастания напряжения Uj , что происходит в момент начала пробоя по цепям питания, или наличии прерывности перегибов, скачков, выбросов тока Питания интегральной схемы 11, амплитуда выходного напряжения Ид блока 6 увеличивается и может превысить пороговое напряжение блока 7 Сфнг.2) При этом 7 формирует импульсости- , навливающий отсчет времени в блоке 8 и запускающий блок 9 сравнения. Код величины достигнутого напряжения питания поступает с блока 8 на вход блока 9 и сравнивается этим блоком с заданнымиуставками. Если .напряжение пробега меньше задан- нъго в блоке допустимого, тоблок 9 формирует на выходе сигнал Брак. Если напряжение пробоя больше допустимого, го блок 10 формирует на выходе сигнал Годен и одновременно выдает признак, характеризующий к какому поддиапазону годных значений напряжения питания относится данная интегральная схема. Результаты срабатывания блока 9 запоминаются в блоке 10 анализа послр чего синхронизатор 1 выдает второй управляющий импульс на коммутатор 3, который подключает резистор 5 к выводу напряжения питания отрицательной полярности интегральной схемы 11. Генератор 2 выдает линейно-нарастаяицее напряжение отрицательной полярности, которое поступает на вывод пига кия отрицательной полярности интегральной схемы 11. При этом устройство повторяет цикл контроля, описанный для напряжения питания положительной полярности. Блок 10 анализа сравнивает результаты контроля при напряжениях питания интегральной схемы 11 разной полярности, классифицирует качество схв№1 11 по наихудшему из двух полученных р(вЭультатов и выдает результат классификации на индикатор 4 для визуального контроля. Таким образом, введение блоков позволяет автоматизировать контроль допустимого напряжения питания, интегральных СХЙ4 11, а также обнаруживать кратковременные нарушения непреривности возрастании испытательного напряжения, что повьшает производительность устройства и досто верность результатов контроля. формула изобретения Устройство для контроля интегральных схем, содержащее синхронизатор, соединенный первым выходом с входом генератора линейно-нарастающего напряжения, соединённого выходом с первым выводом резистора о т л ич а ю щ е ее я тем, что, с целью повышения достоверности контроля и производительности устройства в него введены блок цифрового отсчета времени, дифференцирующий блок, блок сравнения, пороговый блок, блок анализа, индикатор и коммутатор, соединенный первым входсм с вторым выходом синхронизатора, первым, вторым и третьим выход; ами - с соответствующими вводами контролируемой интегр ьНОЙ схемы, вторым входом - с общей шиной устройства, третьим входом с вторым выводом резистора и первым входом дифференцирующего блока, соединенного вторым входом с первым выводом резистора, выходом через пороговый блок - с первым входом блока сравнения и блока цифрового отсчета времени, второй вход которого соединен с первым выходом синхронизатора, выход - с вторым входом блока сравнения, соединенного выходом через блок анализа с входом индикатора. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР И 325571, кл. G 01 R 31/28, 1972. 2.Характериограф ПНХТ-2. - В кн. Нерельман Б.Л., Сидоров В.Г. Методы испытаний и оборудование для контроля качества полупроводниковых приборов. М., Высшая школа, 19 79, с. 56 (прототип).

Ui

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ультразвукового контроля качества материалов | 1983 |

|

SU1133545A1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО КОНТРОЛЯ ГЕОМЕТРИЧЕСКИХ НЕРОВНОСТЕЙ КОЛЕСНЫХ ПАР ПОДВИЖНОГО СОСТАВА12 | 1973 |

|

SU384711A1 |

| Стабилизирующий источник двуполярного напряжения | 1989 |

|

SU1617426A1 |

| Имитатор пульсового сигнала | 1986 |

|

SU1360697A1 |

| Стабилизированный преобразователь постоянного напряжения с защитой | 1986 |

|

SU1317597A2 |

| Способ измерения сопротивления и устройство для его осуществления | 1990 |

|

SU1789940A1 |

| Устройство для решения краевых задач теории поля | 1985 |

|

SU1285495A1 |

| Устройство для контроля асинхронных электродвигателей | 1990 |

|

SU1742653A1 |

| Устройство для контроля пороговых уровней радиоэлектронных схем | 1981 |

|

SU1002991A1 |

| Способ регулирования скорости надвигания пилы при распиловке лесоматериалов и устройство для его осуществления | 1990 |

|

SU1831419A3 |

Авторы

Даты

1982-10-15—Публикация

1981-01-22—Подача