(5) УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ УПРУГОГО ГИСТЕРЕЗИСА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования упругого гистерезиса | 1986 |

|

SU1397946A1 |

| Устройство для моделирования упругого гистерезиса | 1989 |

|

SU1674178A2 |

| Устройство для моделирования упругой характеристики привода в виде петли гистерезиса | 1980 |

|

SU942061A1 |

| Устройство для моделирования сухого трения | 1983 |

|

SU1103251A1 |

| Устройство для моделирования конструкционного трения | 1979 |

|

SU860091A1 |

| Устройство для моделирования @ -фазного управляемого выпрямителя | 1980 |

|

SU959105A1 |

| Масштабный преобразователь напряжения и его варианты | 1980 |

|

SU922780A1 |

| Устройство для моделирования вентильных преобразователей | 1983 |

|

SU1137491A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU862238A1 |

| Генератор напряжения ступенчатой формы | 1983 |

|

SU1113814A2 |

1

Изобретение относится к аналогоВОЙ-. вычислительной технике и может быть применено при решении на аналоговых вычислительных машинах задач теории колебаний, динамики и прочности, конструкций.

Известно устройство для моделированяя упругого гистерезиса, содержащее два интегратора, блок нелинейности, блок вь/деления модуля, инвертор, блок умножения, ключ и блок фиксации нуля и сброса .

Недостатком устройства является наличие постоянной составляющей в выходном сигнале, что сказывается на точности моделирования.

Наиболее близким к предлагаемому изобретению является устройство для моделирования, содержащее первый и второй интеграторы, каждый из которых содержит операционные усилители, масштабные резисторы, ключи, конденсатор. Выход операционного

усилителя первого интегратора через блок задания нелинейности соединен со входом инвертора, выход которого подключен к первому входу блока выделения модуля второй вход которого связан с выходом блока нелинейности, а выход блока выделения модуля соединен с первым входом блока умножения, выход которого подключен к

,Q входу второго интегратора. Устройство содержит также блок фиксации нуля, вход которого соединен с входом первого интегратора, являющимся входЪм устройства, и с вторым входом блока

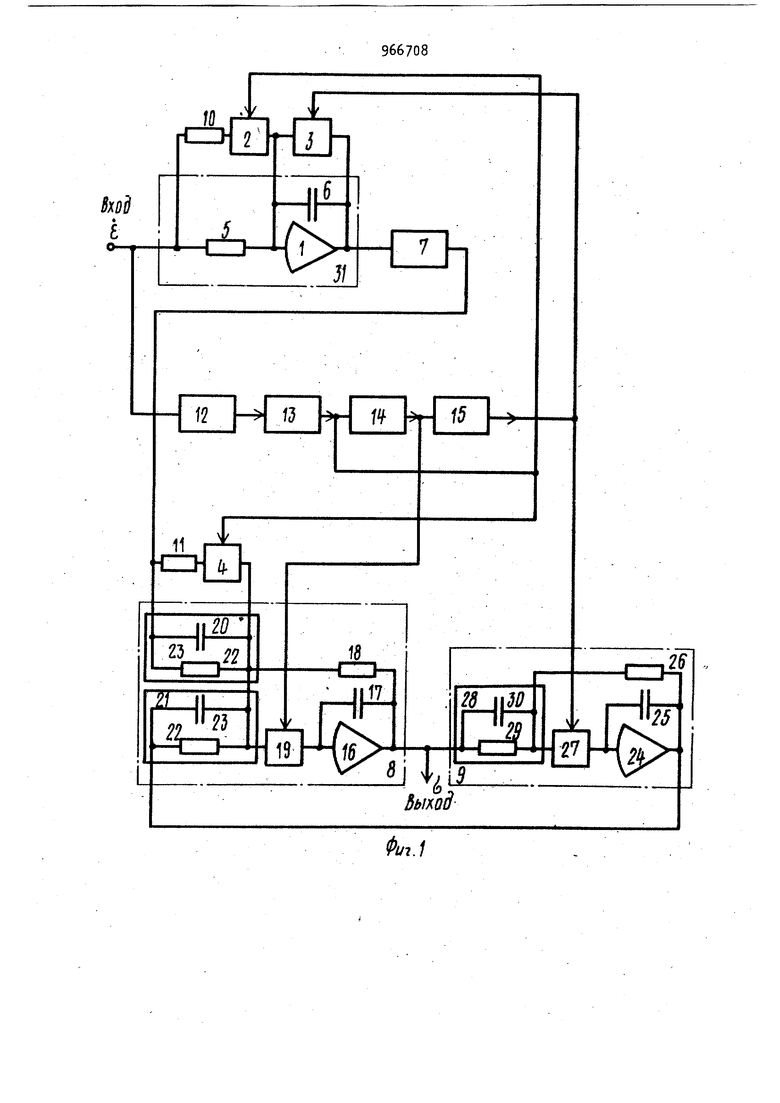

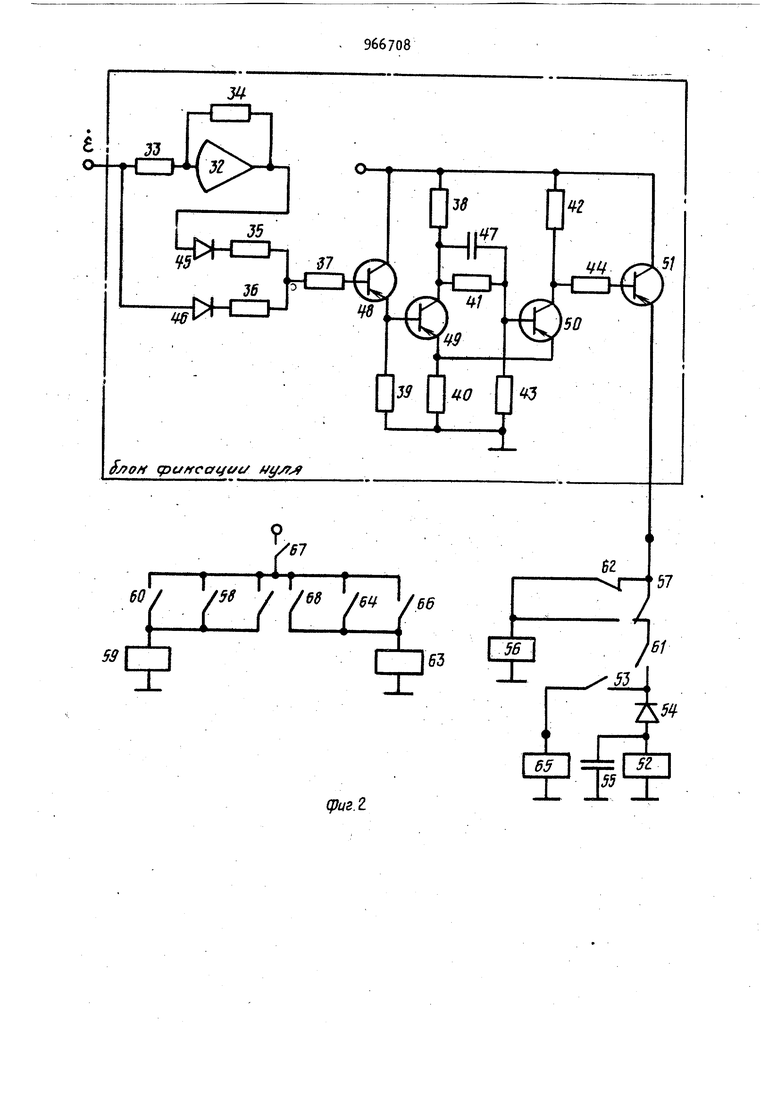

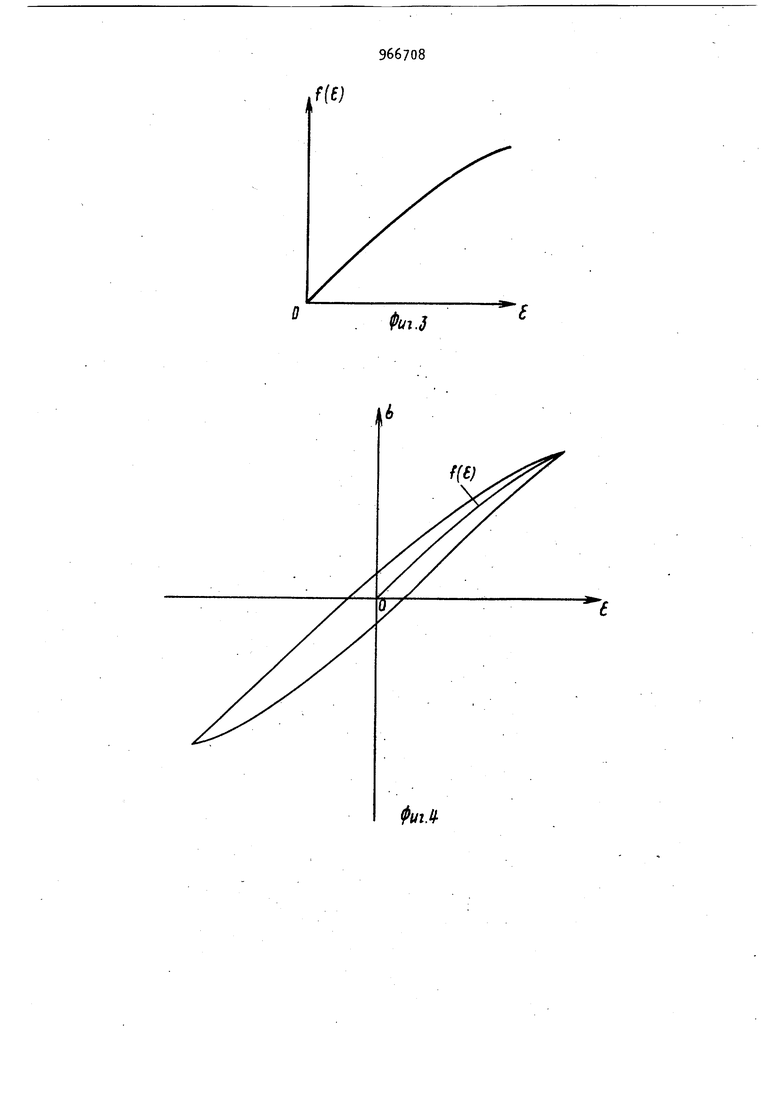

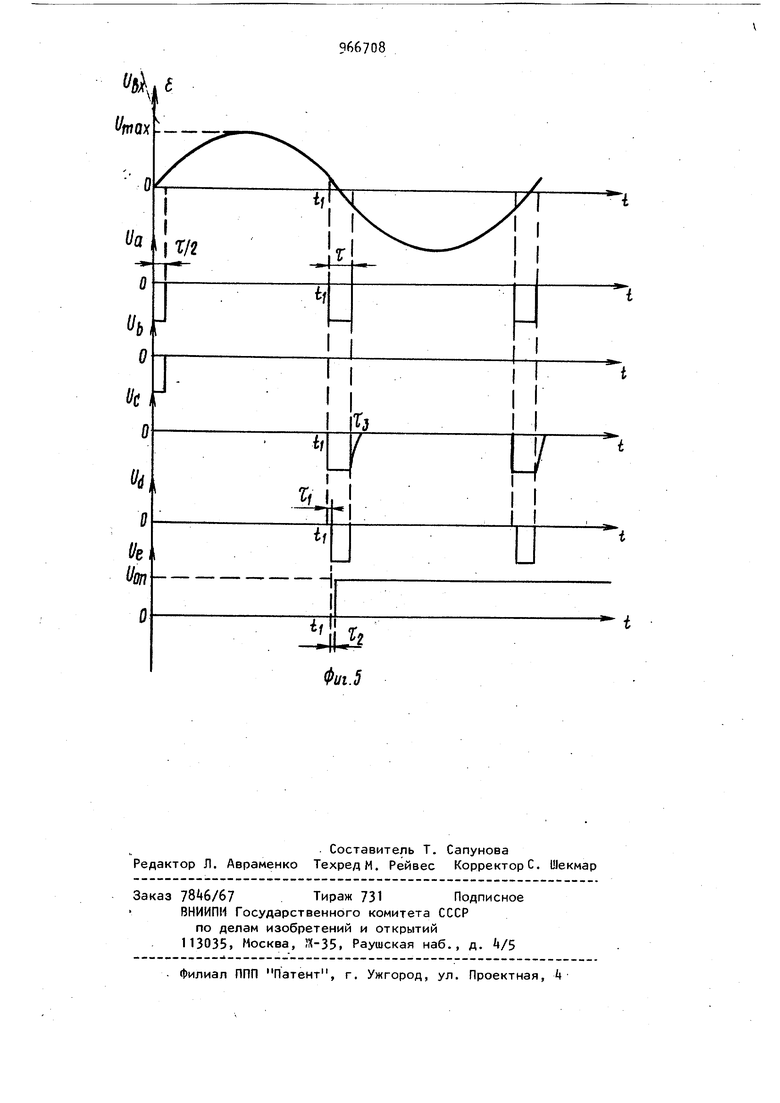

15 умножения, а выход - с входом управляемого источника напряжения и с управляющим входом ключа, информационные вход и выход .которого соответственно подключены к выводам конденсатора первого интегратора. Выход управляемого источника напряжения соединен с управляющими входами ключей во входных цепях интеграторов f .J. Наличие в этом устройстве блока выделения модуля и блока умножения, обладающих сравнительно низкой точностью, а также выходного интегратора, который интегрирует ошибку выполнения всех предыдущих операций, существенно снижает точность моделирования петли гистерезиса. Мель изобретения - повышение точности моделирования упругого гистерезиса. Поставленная цель достигается тем что в известное устройство для моделирования упругого гистерезиса, содержащее операционный усилитель, в цепь обратной связи которого включен параллельно соединенные интегрирующий конденсатор и ключ сброса, а в.о входной цепи - первый и второй масштабные резисторы, первые выводы кото рых объединень и являются входом уст ройства, первый ключ, информационный вход которого подключен к второму вы воду первого масштабного резистора, выход первого ключа и второй вывод второго масштабного резистора объеди нены и подключены к входу операционного усилителя, последовательно соединенные блок фиксации нуля и управляемый источник напряжения, выход которого подключен к управляющему входу первого ключа, вход блока фиксации нуля подключен к входу устройства, и блок нелинейности, вход которого подключен к выходу операционного усилителя i введены сумматор с запоминанием, выход которого является выходом устройства, последователь но соединенные цепь управления сумматором с запоминанием и элемент задержки, последовательно соединенные третий масштабный резистор и второй ключ, и аналоговый запоминающий блок выход блока нелинейности подключен к первому информационному входу сумматора с запоминанием и к второму выводу третьего масштабного резистора, выход второго ключа подключен к второму информационному входу сумматора с запоминанием, выход которого подключен к информационному входу аналогового запоминающего блока, выход которого подключён к третьему информационному входу сумматора с запоминанием, управляющие входы аналогового запоминающего блока и ключа сброс объединены и подключены к выходу эле мента задержки, управляющий вход вто рого ключа подключен к выходу управляемого источника напряжения, а управляющий вход сумматора с запоминанием . подключен к выходу цепи управления сумматором с запоминанием. Кроме того, сумматор с запоминанием содержит операционный усилитель, в цепь обратной связи которого включен интегрирующий конденсатор, масштабный резистор, ключ и два форсирующих зве.на, входы которых являются соответственно первьгм и третьим информационными входами сумматора с запоминанием, выходы форсирующих звеньев объединены, подключены к ин формационному входу ключа, к первому выводу масштабного резистора и являются вторым информационным входом сумматора с«запоминанием, управляющий вход ключа является управляющим входом сумматора с запоминанием, а выход ключа подключен к входу операционного усилителя, выход которого подключен к второму выводу масштабного резистора и является выходом сумматора с запоминанием. Цепь управления сумматором с запоминанием содержит последовательно соединенные реле и коммутирующий диод, анод которого через |3арядный конденсатор подключен к шине нулевого потенциала, а катод является входом-выходом цепи управления сумматором с запоминанием. На фиг, 1 представлена функциональная схема устройства для моделирования упругого гистерезиса; на фиг, 2 - принципиальная схема блока фиксации нуля, управляемого источника напряжения и конструкция цепи управления cj/мматором с запоминанием; на фиг, 3 - экспериментальная зависимость f(f); на фиг, - полученная петля гистерезиса; на фиг, 5 временная диаграмма работы цепей управления. Устройство моделирования упругого гистерезиса содержит операционный усилитель 1, ключи 2, 3 и i, масштабный резистор 5, интегрирующий конденсатор 6, блок 7 нелинейности, сумматор 8 с запоминанием, аналоговый запоминающий блок 9 масштабные резисторы 10 и Т1, блок 12 фиксации нуля,управляемый источник 13 напряжения, цепь 14 управления сумматором с запоминанием, элемент 15 задержки. Сумматор с запоминанием 8 содержит операционный усилитель 16, ин5тегрирующий конденсатор 17, масштаб ный резистор Ifi, ключ 19, два форси рующих звена 20 и 21, каждое из которых содержит параллельно включенные резистор 22 и конденсатор 23. Аналоговый запоминающий блок 9 содержит операционный усилитель 2k, интегрирующий конденсатор 25, масштабный резистор 26, ключ 27, форсирующее звено 28, состоящее из параллельно соединенных резистора 29 и конденсатора 30. Элементы 1,5 и 6 представляют со бой интегратор 31. Блок фиксации нуля 12 содержит операционный усилитель 32, резисторы ЗЗ-, диодьГ 45 и 46, конденсато 47 и транзисторы 48-51. Цепь управления сумматором с запоминанием 14 (на фиг.З обведена жи ной линией) содержит реле 52 с груп пой контактов 53, коммутирующий диод 54, зарядный конденсатор 55. На фиг. 3 обозначены реле 56 с группами контактов 57 и 58, реле 59 с группами контактов 60, 61 и б2,чре ле 63 с группой контактов 64, реле б5 с группой контактов 66, группа контактов реле Рр б7 и тумблер 68. На основании теории упругопластических деформаций и параллельно-последовательной динамической модели у ругого гистерезиса Ишлинского мате мати)ескую модель упругого-гистерез са при циклических деформациях можн представить в следующем виде (c(€) io ts-ti dt , t.7-ti где (t) напряжение в конструкции;t e(t) приращение деформаци конструкции; c(e) текущая жесткость конструкции. Приращение деформации определяетс следующим о разом: (К--ОЛй,...), где t| - момент времени, соответствующий 0. Первое дифференциальное уравнение описывает начальный участок петли гистерезиса при движении из точки покоя, а второе - восходящие и нисходящие ветви петель замкнутого тип 8 Проинтегрировав исходную систему уравнений, приведем ее к виду, удобному для моделирования .(.:.U(i) ,-to -b5ti -1о-ак)ь2(2е) где f(tj- экспериментальная функция (фиг.2); O(t.)- напряжение в конструкции, соответствующее моменту t , причем (У(to)0, так как движение начинается из точки покоя. Экспериментальная функция имеет f(e)--IcCx dy. Таким обоазом, на начальном участке петли гистерезиса значение напряжения в конструкции при любой величине деформации соответствует значению функции f(8 ) при этой деформации. Чтобы получить значение напряжения в конструкции G-i , соответствующее любой точке других участков петли при любой величине деформации 6 , необходимо сложить знамение функции f( 6) при этой деформации с величиной напряжения в конц,е предыдущего цикла деформации О (ty.), соответствующей моменту времени t , когда ё 0. Рассмотрим алгоритм работы устройства. Весь процесс моделирования петли гистерезиса разбивается на три основных этапа: моделирование начального участка петли; моделирование нисходящей ветви; моделирование восходящей ветви. Алгоритм получения выходного сигнала устройства 0(t) в любой момент времени на любом этапе моделирования (эеализуется путем суммирования конечного результата предыдущего этапа моделирования с текущим значением некоторой экспериментальной функции fX). Указанный алгоритм реализуется в предлагаемом устройстве следующим образом. Исходное состояние схемы устройства соответствует этапу моделирования начального участка петли. В исходном состоянии коэффициент передачи интегратора 31, образованного элементами 1, 5 и 6, и коэффициент передачи по первому входу сумматора с запоминанием 8 равны единице. Напряжение, соответствующее скорости деформёции g , поступает на вход опе.рационного усилителя 1 через масштаб ный резистор 5 и ё блок 12 фиксации нуля. При движении из точки покоя воспроизводится начальный участок петли гистерезиса, описываемый уравнением ()(t)f() . Напряжение, отражающее деформацию, с выхода интегратора 31 поступает на блок нелинейности 7, настроенный на воспроизведение функциональной зависимости fC). Сигнал с выхода блока 7 поступает на первый вход сумматора 8 с за поминанием. На третий вход сумматора 8 с запоминанием поступает напряжение с выхода блока 9. Но поскольку в начальный момент времени на выходе аналогового запоминающего блока 9 на пряжение равно нулю, то сумматор 8 с запоминанием работает как инвертор входного сигнала, и на его выходе напряжение пропорционально функции f(). Длительность этого этапа моделирования определяется промежутком времени от до , при котором g 0. Для перехода от моделирования начального участка петли к моделированию нисходящей ветви необходимо сохранить конечный результат последнего этапа. С этой целью в момент вр мени , когда 0, сумматор 8 с запоминанием с помощью своего ключа 19 переводится в режим запоминания. После этого осуществляется сброс интегратора 31I а аналоговый запоминающий блок 9 с помощью своего ключа 27 превращается в масштабирующее звено, инвертирующее напряжение, поступающее с выхода сумматора 8 с запоминанием. Затем производится переключение коэффицента передачи интегратора 31 и коэффициента передачи по первому входу сумматора. Они становятся, соответственно, равными 1/2 и 2. Эти новые значения коэффициентов передачи сохраняются неизмен ными в течение всех последующих эта пов моделирования. В момент времени t t по сигнал производится возврат схемы в рабочее состояние для моделирования нисхЬдящей ветви, описываемой уравнением ((t) G (t)+ 2f(ie)., Обратные переключения в схеме так же должны производиться в определенНОЙ последовательности. Сначала в исходное состояние возвращаются интегратор 31 и блок 9 на выходе которого теперь хранится конечный результат предыдущего этапа моделирования. После этого возможно возвращение в исходное состояние -.режим суммирования - сумматора с .запоминанием. Начинается этап моделирования нисходящей ветви до момента времени , при котором . При t t происходит переход от моделирования нисходящей ветви к моделированию восходящей ветви петли, который проводится в той же последовательности, что и переход от моделирования начального участка петли к моделированию нисходящей ветви. Заключительный этап - моделирование восходящей ветви - длится до момента времени t,, при котором снова 0. Рассмотрим состав и работу цепей управления. Схема управляемого источника напряжения выполнена на реле б5 и 5б, 59 и 63 (фиг.2). Одна группа контактов реле б5 используется в качестве ключа 3 в цепи обратной связи интегратора 31, а вторая - в качестве ключа 27 во входной цепи блока 9. Контакты реле 63 используются в качестве ключей 2 и k, соответственно, в цепях управления коэффициентом передачи интегратора 31 и коэффициентом передачи по первому входу сумматора 8 с запоминанием. Реле 5б и 59 являюtcя вспомогательными и служат для блокировки срабатывания основных и 63 в момент времени при 0. Введение цепи 1 управления сумматором с запоминанием вызвано необходимостью выработки специального.сигнала управления ключом сумматора, отличающегося длительностью и временным сдвигом от управляющих сигналов других ключей. Исходя из рассмотренного алгоритма моделирования петли упругого гистерезиса, можно следующим образом сформулировать задачу цепи k управления сумматором с запоминанием: обеспечить опережение срабатывания ключа 19 сумматора 8 с запоминанием, пе эеводящего его в режим запоминания, в первый момент перехода от одного этапа моделирования к другому, и запаздывание срабатывания этого ключа в конце перехода по сравнению с моментом срабатывания остальных ключей схемы. Блок 13 содержит реле 5б, 59 и 63 блок 15 - контакты 53 и реле б5. На диаграмме напряжений фиг. 5 вве дены следующие обозначения U-y- напряжение, пропорциональное скорости деформации ; 1 , U, с, d, е напряжение в точках а, принципиальной электрической схемы фиг.2. Схема цепей управления работает следующим образом. В исходном положении ключи 2, 3 и 27 разомкнуты, а ключи ,и 19 замкнуты. При подаче сигнала на вход блока 12 фиксации нуля при g 0 формируются импульсы отрицательной полярности. От первого же импульса, поступающего с выхода блока 12, сраб тывает реле 5б блока и своими контактами 57 самоблокируется. Одновременно эта же группа контактов разрывает цепь питания реле б5 и 52,.а другая контактная группа 58 реле 5б замыкает цепь 59 литания реле.Реле 59 срабатывает и своими контактами 60 jсамоблокируется.При этом группа его Контактов 61 замыкается и подготавливает цепь питания реле б5 и 52, а другая группа 62 размыкается и разры вает основную цепь питания реле 56. После окончания импульса с выхода блока 12, реле 5б обесточивается и его контактные группы возвращаются в исходное состояние. При появлении на выходе блока 12 следующего импульса в момент времени , происходит быстрый заряд конденсатора 55 цепи управления сумматором с запоминанием Н через малое внутреннее сопротивление коммутирующего диода 5 открытого для отрицательного управляющего импульса с выхода блока 12. Реле 52 срабатывает и включает цепь сброса интегратора 31 и блока 9- Через его контакты 53 замыкается цепь питания реле б5. Одновременно контакты реле 52 (-ключ 19) размыкаются, отключают вход операционного усилителя (ОУ ) 1б .сумматора с запоминанием от его вход ных цепей и переводят сумматор 8 с запоминанием в режим запоминания сигнала, который находился на выходе.ОУ. За счет времени переходного процесса замыкания контактов обеспечивается задержка переднего фронта импульса, который поступает на обмотку Питания реле б5 и, следовательно, задержка сброса ключа 3 и клю ча 27. Реле 65 срабатывает. Его контакты (ключ 3 замыкают цепь обратной связи интегратора31 и сбрасывают его в нулевое положение, а контакты (ключ 27 замыкаются и соединяют , вход ОУ 2 с его входной цепью, превращая блок 9 в масштабное звено. Одновременно через контакты 66 запитывается реле 63. Время переходного процесса замыкания контактов 66 дает некоторую 3af epwKy переднего фронта импульса, поступающего на обмотку питания реле 63. Реле 63 срабатывает и своими контактами самоблокирхуется. При этом его контакты (ключ 2) переключают коэффициент передачи интегратора 31, устанавливая его равным 1/2, а контакты ( ключ t) переключают коэффициент передачи по первому входу сумматора 8 с запоминанием, устанавливая его равным 2. После окончания управляющего импульса с выхода блока 12 обесточивается реле 65. При этом в исходное состояние возвращается интегратор 31 и блок 9- Конденсатор 55 начинает разряжаться через обмотку реле 53. Постоянная времени цепи разряда конденсатора С обеспечивает задержку заднего фронта имрульса, запитывающего реле 52. После окончания этого импульса реле 52 обесточивается и сумматор с запоминанием 8 возвращается в исходное состояние. Полный возврат цепей управления в исходное положение осуществляется при размыкании контактов б7 реле пуска, срабатывающего от кнопки Пуск АВМ. При нен.улевых начальных условиях по t, и(У блокировка цепей воспроизведения начального участка петли гистерезиса осуществляется с помощью тумблера 68, замыкают цепь питания реле 59 и 63 обеспечивая переключение коэффициента передачи интегратора 3.1 и коэффициента передачи по первому входу сумматора с запоминанием и подготовку цепи питания реле б5. Устройство позволяет моделировать динамику систем с упругим гис.терезисом при действии циклических деформаций различной амплитуды. При этом полученные петли гистерезиса всегда симметричны относительно начала координат (точки покоя). Система с упругим гистерезисом в общем случае должна исследоваться только при движении из состояния покоя ввиду неоднозначности зависимости напряжения в конструкции от деформации и скорости деформации. Однако схема устройства, в принципе, допускает установку любых начальных условий по этим параметрам, если известна вся история предыду;щих нагружений. Формула изобретения 1. Устройство для моделирования, упругого гистерезиса, содержащее опе рационный усилитель, в цепь обратной связи которого включены параллельно соединенные интегрирующий конденсатор и ключ сброса, а во входной цепи первый и второй масштабные резисторы первые выводы которых объединены и являются входом устройства, первый ключ, информационный вход которого подключен к второму выводу первого масштабного резистора, выход первого ключа и второй вывод второго масштаб ного резистора объединены и подключены к входу операционного усилителя последовательно соединенные блок фик сации нуля и управляемый источник напряжения, выход которого подключен к управляющему входу первого ключа, вход блока фиксации нуля подключен к входу устройства, и блок нелинейности , вход которого подключен к выходу операционного усилителя, отличающееся тем, что, с целью повышения точности моделирования, в него введены сумматор с запоминанием, выход которого является выходом устройства, последовательно соединенные цепь управления сумматором с запоминанием и элемент задержки, последовательно соединенные третий масштабный резистор и второй ключ, и аналоговый запоминающий блок выход блока нелинейности подключен к первому информационному входу суйматора с запоминанием и к второму выводу третьего масштабного резистора , выход второго ключа подключен к второму информационному входу сумматора с запоминанием, выход которого подключен к информационному входу аналогового запоминающего блока, выход которого подключен к третьему информационному входу сумматора с запоминанием, управляющие входы аналогового запоминающего блока и ключа сброса объединены и подключены к выходу элемента задержки, управляющий вход второго ключа подключен к выходу управляемого источника напряжения, а управляющий вход сумматора с запоминанием подключен к выходу цепи управления сумматором с запоминанием. 2.Устройство по п.1, отличающееся тем, что сумматор с запоминанием содержит операционный усилитель, в цепьобратной связи которого включен интегрирующий конденсатор, масштабный резистор, ключ и два форсирующих звена, входы которых соответственно являются первым и третьим информационными входами сумматора с запоминанием, выходы форсирующих звеньев объединены, подключены к информационному входу ключа, к первому выводу масштабного резистора и являются вторым информационным входом сумматора с запоминанием, управляющий вход ключа является управляющим входом сумматора с запоминанием, а выход ключа подключен к входу операционного усилителя, выход которого подключен к второму выводу масштабного резистора и является выходом сумматора с запоминанием. 3.Устройство по п.1, о т л и ч аю щ е е с я тем, что цепь управления сумматором с запоминанием содержит последовательно соединенные реле и коммутирующий диод, анод которого через зарядный конденсатор подключен к шине нулевого потенциала, а катод является входом-выходом цепи управления сумматором с запоминанием. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 398981, кл. G 06 G 7/68, 1972. 2.Авторское свидетельство СССР по заявке № 2800786/18-2, кл. Г, Об G , 1979 (прототип).

Авторы

Даты

1982-10-15—Публикация

1980-12-22—Подача