... .1 - . ,

Изобретение относится к вычислительной технике и может быть использовано при технической реализации устройств для контроля и. обработки цифровых данных.

Известно устройство для сравнения чисел, содержащее счетчик, дешифратор допусков, дешифратор анализа, триггеры допусков., Число-импульсный код записывается в счетчик, при этом срабатывают дешифраторы допусков, подключенные к выходам счетчика и триггеры допусков, входы которых подключены к выходам дешифратора, а выходы к входам дешифратора анализа, фор лируюшего результат сравнения (l.

Недостатком .устройства является невозможность оперативного изменения положения поля допуска на числовой оси и величины поля допуска.

Наиболее близким к предлагаемому является устройство для сравнения двоичных чисел с допусками, содержащее счетчик, блок сравнения, блок памяти, триггеры, элементы И. Блок памяти выдает на блок сравнения сначала код минимального допуска, который сравнивается с число-импульсным, кодом, записывающимся в регистр, njm равенстве формируется импульс на выходе блока сравнения и потенциал на выходе Равно, при этом блок памяти выдает на сравнение код максимального допуска. Если

10 второй импульс равенства не формируется, потенциал на выходе Равно остается, если второй импульс равенства формируется, потенциал с выхода Равно j снимается и формируется на выходе Больше,, что свидетельствует о том, что входной код превысил максимальный допуск 2.

Недостатком этого устройства является

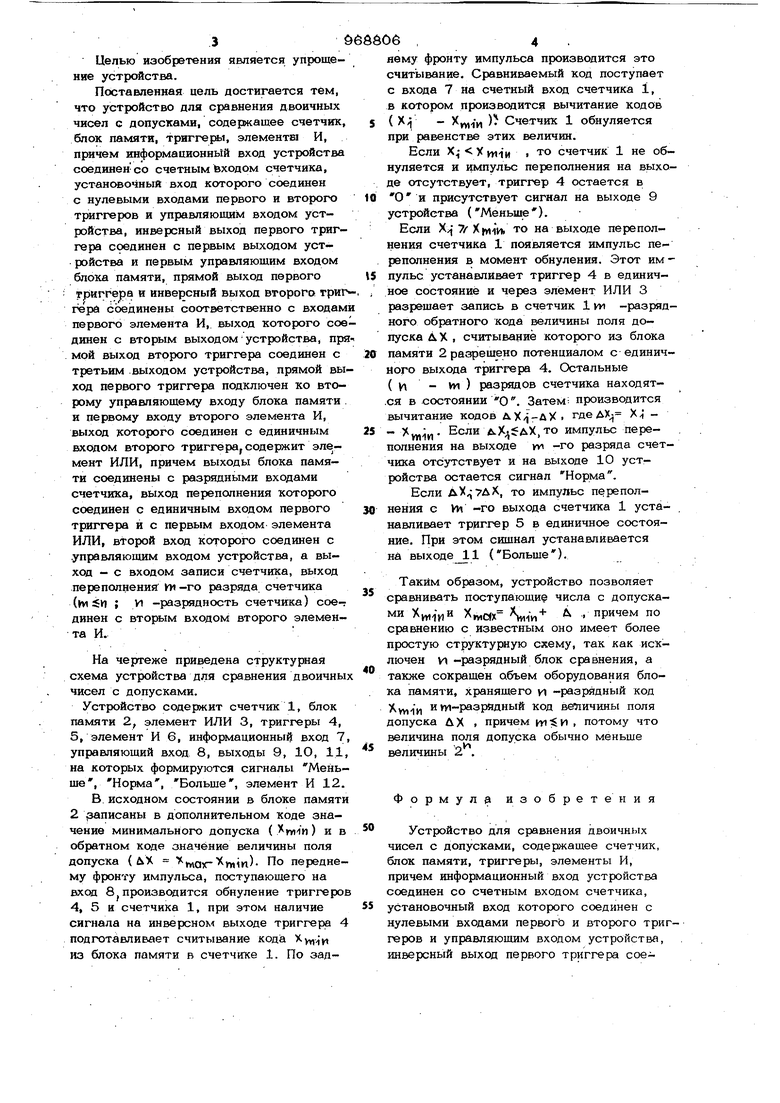

20 его сложность, так как оно содержит блок сравнения, а также в блоке памяти для хранения кодов допусков необходимо иметь два И -разрядных регистра./ Целью изобретения является упрощение устройства. Поставленная цель достигается тем, что устройство для сравнения двоичных чисел с допусками, содержащее счетчик, блок памяти, триггегы, элементы И, причем информационный вход устройства соединенсо счетным ьходом счетчика, установочный вход которого соединен с нулевыми входами первого и второго триггеров и управляющим входом устройства, инверсный выход первого триггера соединен с первым выходом устройства и первым управляющим входом блока памяти, прямой выход первого триггера и инверсный выход второго триг гера соединены соответственно с входам первого элемента И,, выход которого сое динен с вторым выходом устройства, пр . мой выход второго триггера соединен с третьим выходом устройства, прямой вы ход первого триггера подключен ко второму управляющему входу блока памяти и первому входу второго элемента И, выход которого соединен с единичным входом второго триггера, содержит элемент ИЛИ, причем выходы блока памяти соединены с разрядными входами счетчика, выход переполнения которого соединен с единичным входом первого триггера и с первым входом элемента ИЛИ, второй вход которого соединен с управляющим входом устройства, а выход - с входом записи счетчика, выход переполнения ки -го разряда счетчика (hi И ; VI -разрядность счетчика) сое-т динен с вторым входом второго элемента И. На чертеже приведена структурная схема устройства для сравнения двоичны чисел с допусками. Устройство содержит счетчик 1, блок памяти 2, элемент ИЛИ 3, триггеры 4, 5, элемент И 6, информационный вход 7 управляющий вход 8, выходы 9, 1О, 11, на которых формируются сигналы Меньще, Норма, Больще, элемент И 12. В исходном состоянии в блоке памяти 2 раписаны в дополнительном коде значение минимального допуска ( rwin) и в обратном коде значение величины поля допуска (ЛХ wax- nim)- По переднему фронту импульса, поступающего на вход 8Jпроизводится обнуление триггеров 4, 5 и счетчика 1, при этом наличие сигнала на инверсном выходе триггера 4 подготавливает считывание кода Хуу,{ из блока памяти в счетчике 1. По эаднему фронту импульса производится это счить1вание. Сравниваемый код поступает с входа 7 на счетный вход счетчика 1, в котором производится вычитание кодов ( X;j - , ) Счетчик 1 обнуляется при равенстве этих величин. Если Х X yniH , то счетчик 1 не обнуляется и импульс переполнения на выходе отсутствует, триггер 4 остается в О и присутствует сигнал на выходе 9 устройства (Меньше). Если / XfwiH, то на выходе переполнения счетчика 1 появляется импульс переполнения в момент обнуления. Этот им пульс устанавливает триггер 4 в единичное состояние и через элемент ИЛИ 3 разрещает запись в счетчик 1 уи -разрядного обратного кода величины поля допуска ЛХ , считывание которого из блока памяти 2 разрешено потенциалом с единичного выхода триггера 4. Остальные ( у - УИ ) разрядов счетчика находят.ся в состоянии О. Затем: производится вычитание кодов &X/j-uX. гдеАХ MiiH- Если , то импульс пере- . полнения на выходе w -го разряда счетчика отсутствует и на выходе 10 устройства остается сигнал Норма. Если , то импульс переполнения с УИ -го выхода счетчика 1 устанавливает триггер 5 в единичное состояние. При этом сшинал устанавливается на выходе 11 (Больще). Таким образом, устройство позволяет сравнивать поступающие числа с допусками ,y,и Х, и1и .причем по сравнению с известным оно имеет более простую структурную схему, так как исключен и -разрядный блок сравнения, а также сокращен объем оборудования блока памяти, хранящего ц -разрядный код Хум1И ит-разрядный код величины поля допуска ДХ , причем , потому что величина поля допуска обычно меньще величины 2 . Формула изобрете Устройство для сравнения двоичных чисел с допусками, содержащее счетчик, блок памяти, триггеры, элементы И, причем информационный вход устройства соединен со счетным входом счетчика, установочный вход которого соединен с нулевыми входами первогЬ и второго триггеров и управляющим входом устройства, инверсный выход первого триггера соедипен с первым выходом устройства и первым управляющим входом блока памяти, прямой выход первого триггера и инверсный выход второго триггера соединены соответственно с входами, перво.го элемента И, выход которого соединен с вторым выходом устройства, прямой выход второго триггера соединен с третьим выходом устройства, прямой выход первого триггера подключен к второму управляющему входу блока памяти и первому входу второго элемента И, выход которого соединен с единичным-входом второго триггер, от личаюшее с я тем, что, с целью упрощения устройства, оно содержит элемент ИЛИ, причем выходы блока памяти соединены с

разрядными входами счетчика, выход переполнения которого соединен с единичным входом первого триггера и с первым входом элемента ИЛИ, второй вход которого соединен с управляющим входом устройства, а выход - с входом записи счетчика, выход переполнения разряда счетчика (ур И ; «, -разрядность счетчика) соединен с BTOpfciM входом второго элемента И,

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 641446, кл. Q06F 7/О4, 1977,

2.Авторское сввдетельство СССР № 538358, кл, G06 F 7/О4, 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения чисел | 1980 |

|

SU955032A1 |

| Устройство для сравнения чисел с допусками | 1980 |

|

SU968805A1 |

| Устройство для сравнения чисел | 1979 |

|

SU809168A1 |

| Стохастическое вычислительное устройство | 1982 |

|

SU1062700A1 |

| Устройство для допускового контроля частоты | 1990 |

|

SU1781633A1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ НЕИСПРАВНОСТЕЙ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1992 |

|

RU2030784C1 |

| Устройство для сравнения двоичных чисел с допусками | 1978 |

|

SU744554A1 |

| Генератор последовательности импульсов | 1984 |

|

SU1309275A1 |

| Устройство для программного управления намоточным станком | 1987 |

|

SU1451648A1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ ОТКАЗОВ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1996 |

|

RU2099777C1 |

7

Авторы

Даты

1982-10-23—Публикация

1980-11-24—Подача