1

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при реализации техниче-. ских средств цифровых контрольно-измерительных комплексов и устройств автомати- 5 ческого управления.

Известно устройство для сравнения чисел, содержащее элементы И, ИЛИ, триггеры 1. Это устройство осуществляет сравнение поступающей последовательности чи- ю сел с допусками и формирует значение разности между ними.

К недостаткам устройства относятся его сложность и невозможность контроля входа-выхода контролируемого параметра в is поле допусков.

Наиболее близким техническим решением к предложенному является устройство для сравнения двоичных чисел с допусками, содержащее счетчик, триггеры, элементы И, 20 ИЛИ, НЕ, формирователь импульсов, схемы сравнения, блоки памяти. При этом информационный вход устройства соединен с информационным входом счетчика, выходы которого подключены к первой группе вхо- 25 ДОН первой схемы сравнения, вторая группа входов которой соединена с выходами первого блока памяти, первый выход первой схемы сравнения подключен к первому входу первого элемента И, выход которого 30

соединен со входом установки в единичное состояние первого триггера, прямой выход которого подключен к первому входу второго элемента Инк первому входу управления первого блока памяти. Инверсный выход первого триггера соединен со вторым входом управления первого блока памяти и с первым входом третьего элемента И и со вторым входом первого элемента И, вход управления устройства через элемент НЕ- со входом управления счетчика и через формирователь импульсов со входами установки в нулевое состояние счетчика и второго триггера, прямой выход которого подключен к первому входу четвертого элемента И. Инверсный выход второго триггера соединен со вторым входом второго элемента И, вторые входы второго, третьего и четвертого элементов И подключены ко входу управления устройства. Кроме того, это устройство содержит регистры и элементы неравнозначности .

Недостатком этого устройства являются его низкие функциональные возможности, так как устройство позволяет контролировать только возрастающие величины и не позволяет вести длительный контроль за случайно изменяющимся параметром, когда контролируемая величина многократно входит и выходит в зону допусков, что снижает эффективность и качество контроля.

Цель изобретения - раси1ирение функциональных возможностей путем контроля пронзвольно изменяющихся параметров.

Поставленная цель достигается, тем, что в устройстве второй выход первой схемы сравнения соединен с первым входом пятого элемента И, второй вход которого связан с первым входом первого элемента Р1ЛИ и с прямым выходом второго триггера, второй вход первого элемента ИЛИ, третий вход пятого элемента И, уиравляющийвход второго блока памяти подключены к прямому выходу первого триггера, выходы второго блока памяти соединены с ииформационными входами второй схемы сравнения, управляющий вход которой подключен к выходу пятого элемента И, выход второй схемы сравнения соединен с первым входом второго элемента ИЛИ, второй вход которого подключен к выходу формирователя импульсов, выход второго элемента ИЛИ- со входом установки в нулевое состояние первого триггера, выход первого элемента ИЛИ и первый выход первой схемы сравнения подключены ко входам шестого элемента И, выход которого соединен со счетным входом второго триггера.

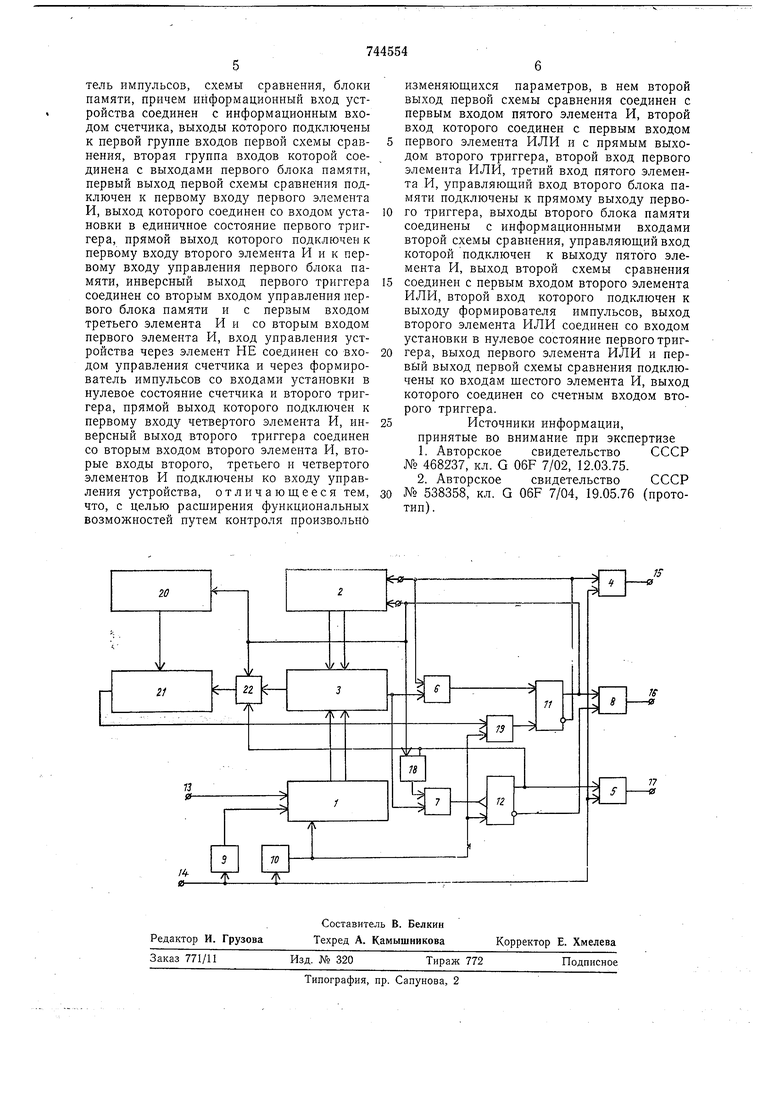

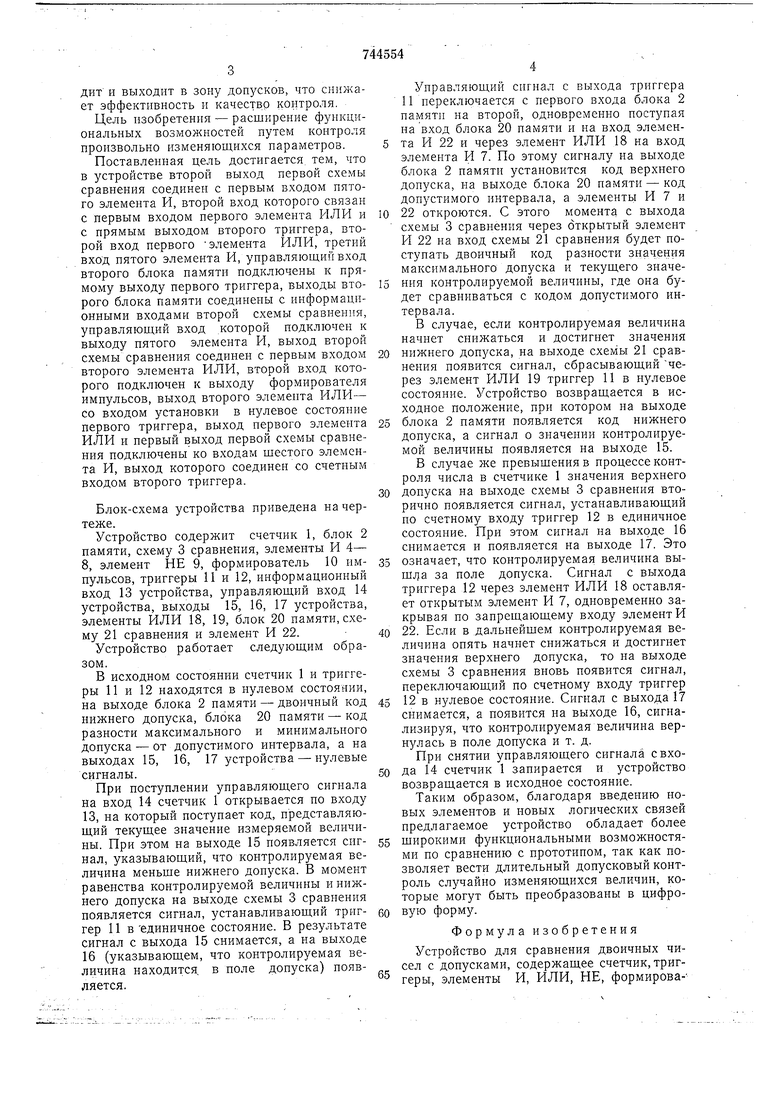

Блок-схема устройства приведена на чертеже.

Устройство содержит счетчик 1, блок 2 памяти, схему 3 сравнения, элементы И 4- 8, элемент НЕ 9, формирователь 10 имцульсов, триггеры И и 12, информационный вход 13 устройства, управляющнй вход 14 устройства, выходы 15, 16, 17 устройства, элементы ИЛИ 18, 19, блок 20 памятн, схему 21 сравнения и элемент И 22.

Устройство работает следующим образом.

В исходном состоянии счетчик 1 и триггеры И и 12 находятся в нулевом состоянии, на выходе блока 2 памяти - двоичный код нижнего допуска, блока 20 памяти - код разиости максимального и минимального допуска - от допустимого интервала, а на выходах 15, 16, 17 устройства - нулевые сигналы.

При поступлении управляющего сигиала на вход 14 счетчик 1 открывается по входу 13, на который поступает код, представляющий текущее значенне измеряемой величины. При этом на выходе 15 появляется сигнал, указывающий, что контролируемая величина меньще нижнего допуска. В момент равенства контролируемой величины и нижнего допуска на выходе схемы 3 сравнения появляется сигнал, устанавливающий триггер 11 в единичное состояние. В результате сигнал с выхода 15 снимается, а на выходе 16 (указывающем, что контролируемая величина находится, в ноле допуска) появляется.

Управляющий спгнал с выхода триггера 11 переключается с первого входа блока 2 памяти на второй, одновремеиио иоступая на вход блока 20 памяти и на вход элемен5 та И 22 и через элемент ИЛИ 18 на вход элемента И 7. По этому сигналу на выходе блока 2 памяти установится код верхнего допуска, на выходе блока 20 памяти - код допустимого интервала, а элементы И 7 и iO 22 откроются. С этого момента с выхода схемы 3 сравнения через открытый элемент И 22 на вход схемы 21 сравнения будет поступать двоичный код разности значения максимального допуска и текущего значе15 ння контролируемой величииы, где она будет сравниваться с кодом допустимого интервала.

В случае, если контролируемая величина начнет снижаться и достигнет значения 20 нижнего допуска, на выходе схемы 21 сравнения появится сигнал, сбрасывающий через элемент ИЛИ 19 триггер 11 в нулевое состояние. Устройство возвращается в исходное положение, при котором на выходе 5 блока 2 памяти появляется код нижнего допуска, а сигнал о значении коитролируемой величины появляется на выходе 15.

В случае же превышения в процессе контроля числа в счетчике 1 значения верхнего 0 допуска на выходе схемы 3 сравнения вторично появляется сигнал, устанавливающий по счетному входу триггер 12 в единичное состояние. При этом сигнал на выходе 16 снимается и появляется на выходе 17. Это 5 означает, что контролируемая величина выщла за поле допуска. Сигнал с выхода триггера 12 через элемент ИЛИ 18 оставляет открытым элемент И 7, одновременно закрывая по запрещающему входу элемент И 0 22. Если в дальнейшем контролируемая величина опять начнет снижаться и достигнет значения верхнего допуска, то на выходе схемы 3 сравнения вновь появится сигнал, переключающий по счетному входу триггер 5 12 в нулевое состояние. Сигнал с выхода 17 снимается, а появится на выходе 16, сигиализируя, что контролируемая величина вернз лась в поле допуска и т. д.

При снятии управляющего сигнала свхо0 да 14 счетчик 1 запирается и устройство возвращается в исходное состояние.

Таким образом, благодаря введению новых элементов и новых логических связей предлагаемое устройство обладает более 5 щирокими функциональными возможностями но сравнению с нрототииом, так как позволяет вести длительный допусковый контроль случайно изменяющихся величин, которые могут быть преобразованы в цифровую форму.

Формула изобретения

Устройство для сравнения двоичиых чисел с допусками, содержащее счетчик, триггеры, элементы И, ИЛИ, НЕ, формирователь импульсов, схемы сравнения, блоки памяти, причем информационный вход устройства соединен с информационным входом счетчика, выходы которого подключены к первой группе входов первой схемы сравнения, вторая группа входов которой соединена с выходами первого блока памяти, первый выход первой схемы сравнения подключен к первому входу первого элемента И, выход которого соединен со входом установки в единичное состояние первого триггера, прямой выход которого подключен к первому входу второго элемента И и к первому входу управления первого блока памяти, инверсный выход первого триггера соединен со вторым входом управления первого блока памяти и с первым входом третьего элемента И и со вторым входом первого элемента И, вход управления устройства через элемент НЕ соединен со входом управления счетчика и через формирователь импульсов со входами установки в нулевое состояние счетчика и второго триггера, прямой выход которого подключен к первому входу четвертого элемента И, инверсный выход второго триггера соединен со вторым входом второго элемента И, вторые входы второго, третьего и четвертого элементов И подключены ко входу управления устройства, отличающееся тем, что, с целью расширения функциональных возможностей путем контроля произвольно

изменяющихся параметров, в нем второй выход первой схемы сравнения соединен с первым входом пятого элемента И, второй вход которого соединен с первым входом первого элемента ИЛИ и с прямым выходом второго триггера, второй вход первого элемента ИЛИ, третий вход пятого элемента И, управляющий вход второго блока памяти подключены к прямому выходу первого триггера, выходы второго блока памяти соединены с информационными входами второй схемы сравнения, управляющий вход которой подключен к выходу пятого элемента И, выход второй схемы сравнения соединен с первым входом второго элемента ИЛИ, второй вход которого подключен к выходу формирователя импульсов, выход второго элемента ИЛИ соединен со входом установки в нулевое состояние первого триггера, выход первого элемента ИЛИ и первьтй выход первой схемы сравнения подключены ко входам щестого элемента И, выход которого соединен со счетным входом второго триггера.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 468237, кл. G 06F 7/02, 12.03.75.

2.Авторское свидетельство СССР № 538358, кл. G 06F 7/04, 19.05.76 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения чисел с допусками | 1979 |

|

SU769533A1 |

| Устройство для допускового контроля последовательностей импульсов | 1982 |

|

SU1084749A1 |

| Устройство для программного контроля | 1987 |

|

SU1464142A1 |

| Устройство для сравнения двоичных чисел с допусками | 1975 |

|

SU538358A1 |

| Устройство для регистрации команд в резервированной системе управления | 1989 |

|

SU1633284A1 |

| Устройство для контроля блоков памяти | 1980 |

|

SU894799A1 |

| Устройство для контроля параметров радиоэлектронных узлов | 1989 |

|

SU1615748A1 |

| Устройство для программного управления намоточным станком | 1987 |

|

SU1451648A1 |

| Устройство для допускового контроля временных команд | 1988 |

|

SU1566328A1 |

| Устройство для контроля логических блоков | 1984 |

|

SU1223234A1 |

Авторы

Даты

1980-06-30—Публикация

1978-02-22—Подача