Изобретение относится к импульсной технике, предназначено для вычислительных устройств и может быть исгюльзоЕиню в синхронизаторах, управляющих и вычислительных системах.

Цель изобретения - повышение 11адеж- ности и быстродействия.

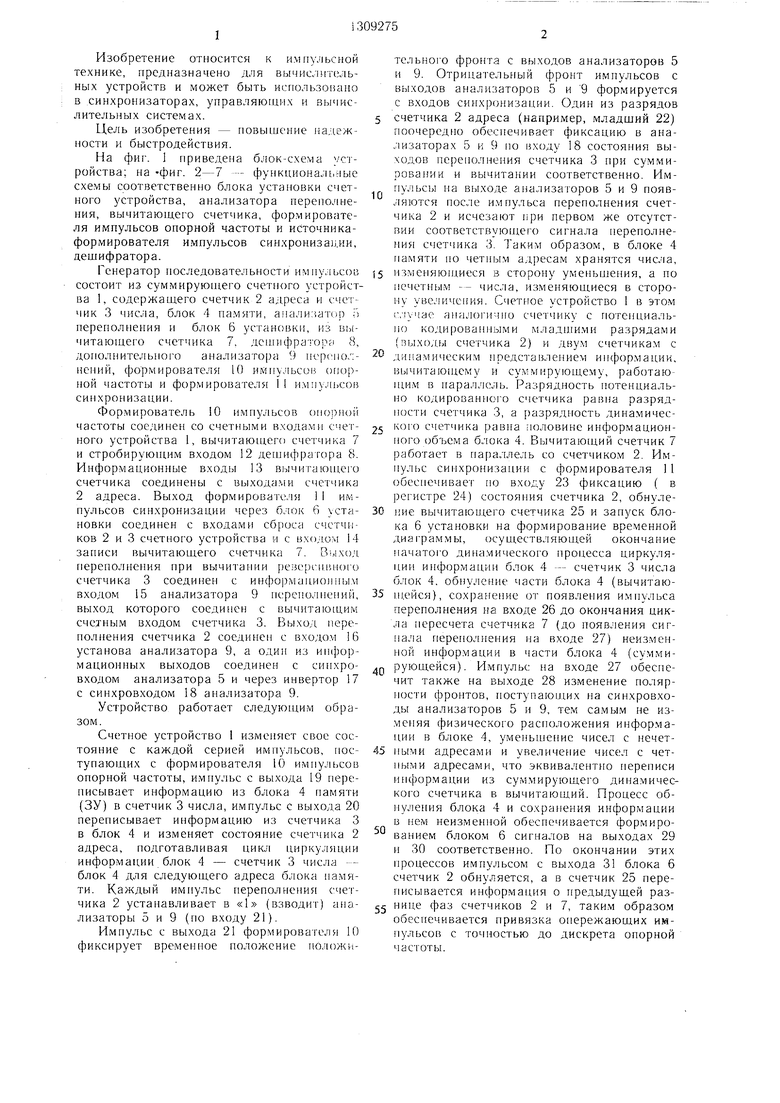

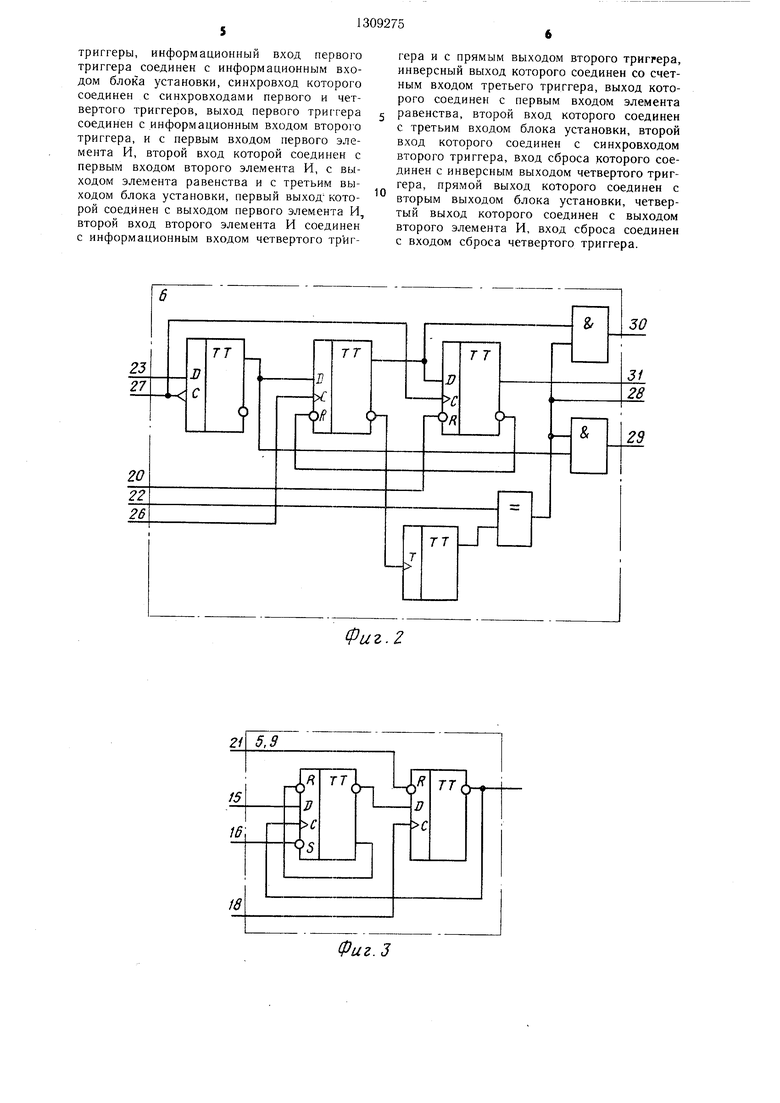

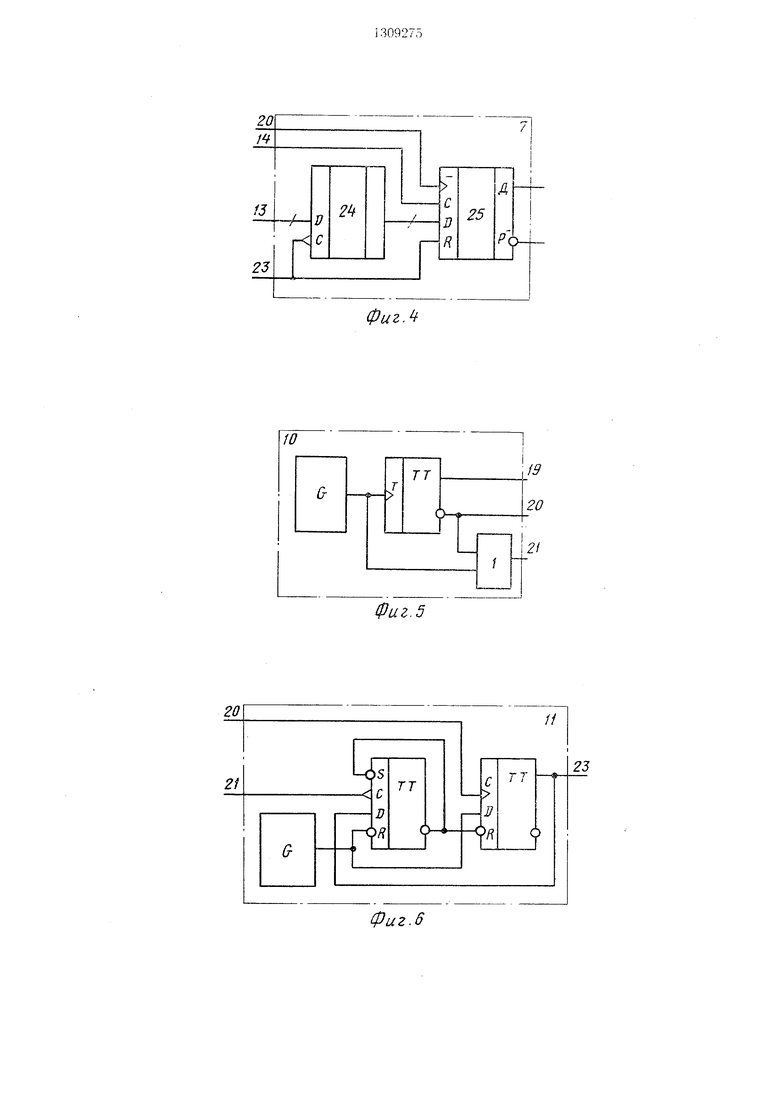

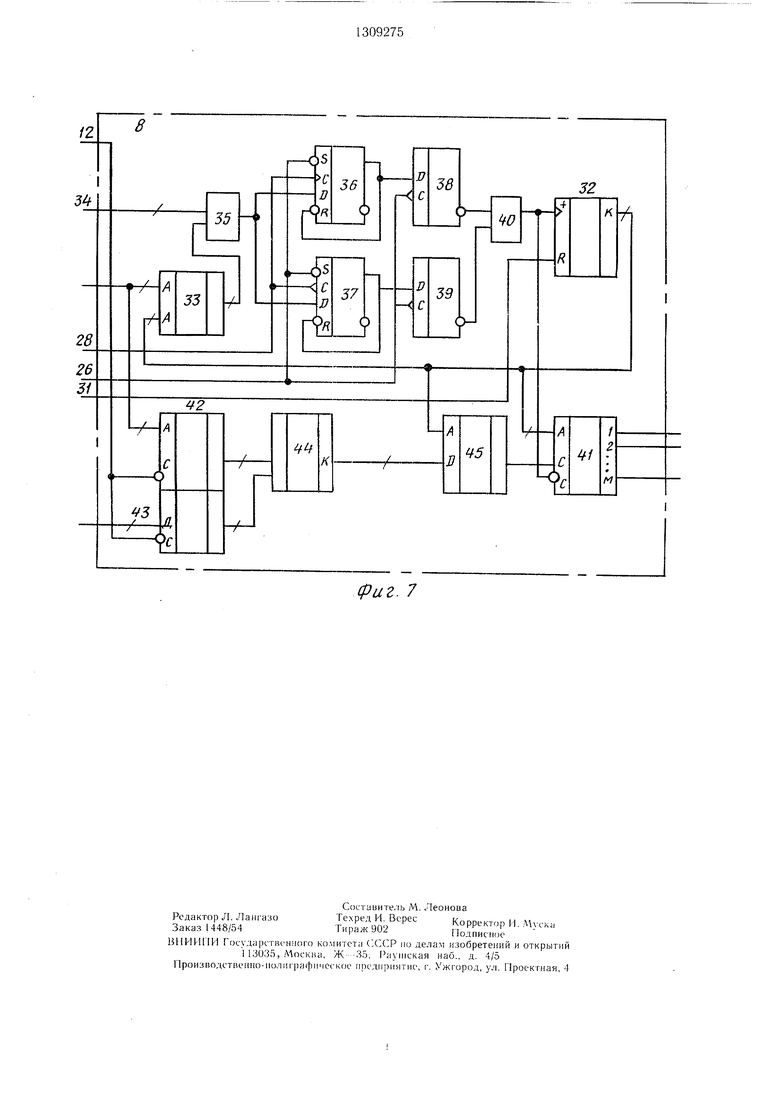

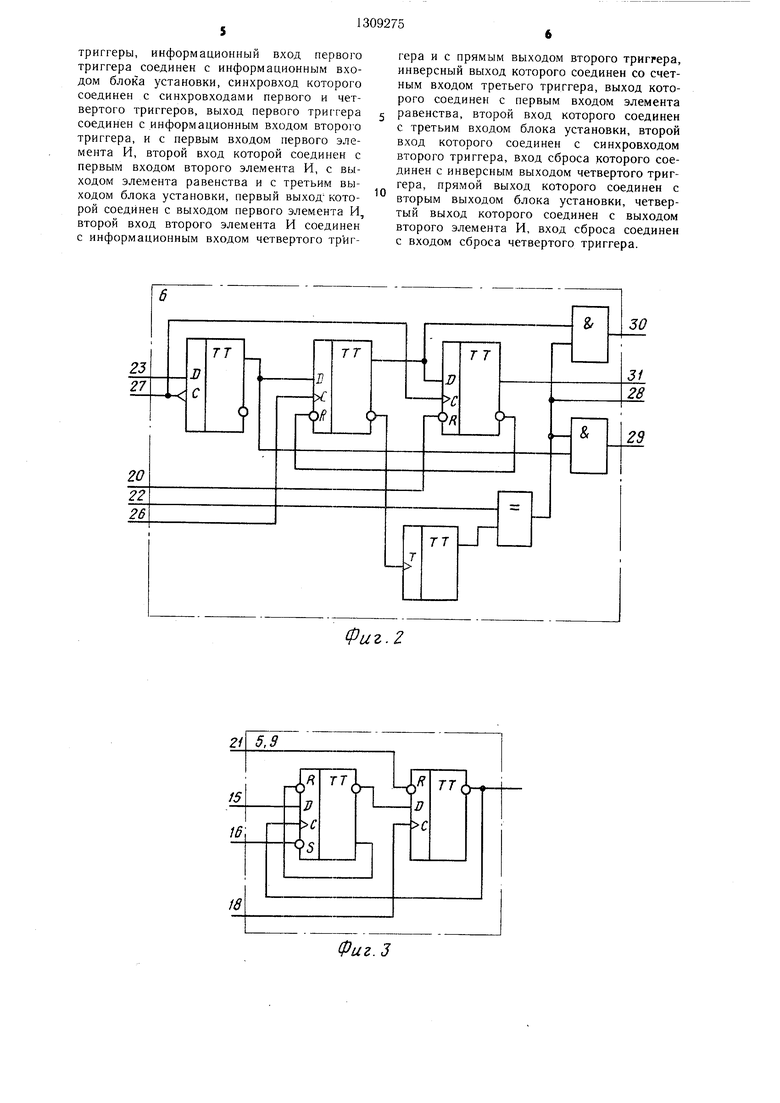

На фиг. 1 приведена блок-схема устройства; на -фиг. 2-7 -- функциональные схемы соответственно блока установки счетного устройства, анализатора переполнения, вычитающего счетчика, формирователя импульсов опорной частоты и источника- формирователя и.мпульсов синхрониза),ии, дешифратора.

Генератор последовательности импульсов состоит из суммирую дего счетного устройства 1, содержащего счетчик 2 ад,реса и счетчик 3 числа, блок 4 па.мяти, анализатор ;) переполнения и блок 6 установки, из кы- читающего счетчика 7, дсншфрато - 8, дополнительного анализатора 9 перспо, :- нений, формирователя К) HMiiyju-jCOB orjo)- ной частоты и формирователя 11 импул1 сов синхронизации.

Формирователь 10 импульсов oiioj iioi i частоты соединен со счетными входами счетного устройства 1, вычитающего счетчика 7 и стробирующим входом 12 ден:ифрагора 8. Информационные входы 13 вычнтаюндего счетчика соединены с выходами счетчика 2 адреса. Выход формирователи 1 1 импульсов синхронизации через блок 6 установки соединен с входами сброса счетчиков 2 и 3 счетного устройства и с входом 14 записи вычитающего счетчика 7. В глход переполнения при вычитаиии peBepriuiHoi o счетчика 3 соединен с информационным входом 15 анализатора 9 нсренолнений, выход которого соединен с вычитающим счетным входом счетчика 3. Выход переполнения счетчика 2 соединен с входом 16 установа анализатора 9, а один из ин(|юр- мационных выходов соединен с синхро- входом анализатора 5 и через инвертор 17 с синхровходом 18 анализатора 9.

Устройство работает следующим образом.

Счетное устройство 1 изменяет свое состояние с каждой серией импульсов, поступающих с формирователя 10 импульсов опорной частоты, импульс с выхода 19 переписывает информацию из блока 4 памяти (ЗУ) в счетчик 3 числа, импульс с выхода 20 переписывает информацию из счетчика 3 в блок 4 и изменяет состояние счетчика 2 адреса, подготавливая цикл циркуляции информации блок 4 - счетчик 3 числа -- блок 4 для следующего адреса блока памяти. Каждый имнульс перенолнения счетчика 2 устанавливает в «1 (взводит) анализаторы 5 и 9 (по входу 21).

Импульс с выхода 21 формирователя 10 фиксирует вре.менное положение пОложи

S

0

5

0

5

0

5

O

55

тельного фронта с выходов анализаторов 5 и 9. Отрицательный фронт импульсов с выходов анализаторов 5 и 9 формируется с входов синхронизации. Один из разрядов счетчика 2 адреса (например, младший 22) поочередно обеспечивает фиксацию в ана- ;1изаторах 5 и 9 по 1)ходу 18 состояпия выходов перенолнения счетчика 3 при суммировании и вычитании соответственно. Импульсы на выходе анализаторов 5 и 9 появляются после импульса переполнения счетчика 2 и исчезают при нерво.м же отсутствии соответствующего сигнала переполнения счетчика 3. Таким образом, в блоке 4 памяти но четным адресам хранятся числа, изменяюнлиеся в сторону уменьшегтя, а по нечетным -- числа, изменяющиеся в сторону увеличения. Счетное устройство 1 в этом с. анало1л-1чио счетчику с потенциально кодироваппыми младнш.ми разрядами (пыхол,ы счетчика 2) и двум счетчикам с динамическим представлением информации, вычитающему и суммирующему, работающим в нараллсль. Разрядность нотенциаль- но кодированного счетчика равна разрядности счетчика 3, а разрядггость динамичес- Koi o счетчика равна половине информационного объема блока 4. Вычитаю ций счетчик 7 работает в па)аллель со счетчиком 2. Импульс синхронизании с формирователя 11 обеснечивает iio входу 23 фиксацию ( в регистре 24) состояния счетчика 2, обнуление вычитающего счетчика 25 и зануск блока 6 установки на фор.мирование временной диаграммы, осуществляющей окончание начатого дина.мического процесса циркуляции информа и1и блок 4 -- счетчик 3 числа б.чок 4. обнуление части блока 4 (вычитающейся), сохранение от появления имнульса перенолнения на входе 26 до окончания цикла нересчета счетчика 7 (до появления сиг- ia/ia перенолнения на входе 27) неизменной информации в части блока 4 (суммирующейся). Имнульс на входе 27 обеспечит также на выходе 28 изменение ноляр- ности фронтов, поступающих на синхровхо- ды анализаторов 5 и 9, тем самым не из- .меняя физического расположения инфор.ма- ции в блоке 4, уменьшение чисел с нечетными адресами и увеличение чисел с четными адресами, что эквивалентно нерениси информации из суммирующего динамического счетчика в вычитающий. Процесс об- ||уле ия блока 4 и сохранения информации в нем неиз.менной обеспечивается формированием блоком 6 сигналов на выходах 29 и 30 соответственно. По окончании этих процессов импульсом с выхода 31 блока 6 счетчик 2 обнуляется, а в счетчик 25 переписывается информация о предыдущей разнице фаз счетчиков 2 и 7, таким образо.м обеспечивается привязка опережающих импульсов с точпостью до дискрета опорной частоты.

Формирование выходных запаздывающих и опережающих импульсов осуществляется динамическим дешифратором 8. По каждому импульсу синхронизации сформированный в блоке 6 установки на выходе 31 импульс переводит в исходное состояние счетчик 32 каналов (порядковых номеров выходов) дешифратора 8, инфор- мация о выходе которого адресует начальное (исходное) слово, выбираемое из памяти кодов (времени) каналов блока 33. В каждом из циклов пересчета счетчик 2 адреса динамически, например потетрадно, выбирает из блока 33 код времени канала, который сравнивается с кодом времени, поступающим со счетчика 3 числа по входу 34, на элементе 36 сравнения и на триггерах- защелках 36 и 37, затем фиксируется на триггерах 38 и 39. Полярность фронтов синхронизации триггеров 36 и 37 выбрана такой, что в триггерах 36 и 38 формируется результат сравнения с суммирующимся кодом в блоке 4, а в триггерах 37 и 39 - с вычитающимся. Элементы 32, 33, 35-41 дешифратора 8 узла образуют канал грубого отсчета, отсчета времени с точностью до периода переполнения счетчика 2. Канал точного отсчета (с точностью до периода импульсов опорной частоты) содержит дешифраторы 42 и 43 счетчиков 2 и 7, коммутатор 44 и мультиплексор 45. На коммутаторе 44, например, путем соединения соответствующего выхода дешифратора с входом .мультиплексора 45, соответствующим определенному номеру канала, фиксируется положение выходного импуль са внутри периода переполнения счетчика адреса в каждом из выходных каналов и передается с выхода мультиплексора 45 на стробирую- щий вход выходного дешифратора 41.

Таким образом на выходах 41 будут сформированы импульсы, имеющие временное положение относительно импульса синхронизации, старшие разряды кода которого определены в блоке 33, а младшие - в соединениях коммутатора 44. В предлагаемом варианте построения устройства коды опережающих и запаздывающих импульсов не должны пересекаться, поскольку для их хранения использован общий блок 33.

Формула изобретения

1. Генератор последовательности импульсов, содержащий выходной дешифратор, суммирующее счетное устройство и вычитающий счетчик, в котором счетные входы счетного устройства и вычитающего счетчика соединены со стробирующим входом дешифратора и с первым выходом формирователя импульсов опорной частоты, информационные входы вычитаюшего счетчика соединены с адресными входами выходного дешифратора и выходами счетного

0

устройства, информационные выходы вычитающего счетчика соединены с информационными входами выходного дешифратора, фор.мирователь импульсов синхронизации, отличающийся тем, что, с целью повышения надежности и быстродействия, в него введены первый анализатор переполнения, а счетное устройство содерж1гг блок установки, блок памяти, счетчик числа, анализатор переполнения и счетчик адреса, информационные выходы которого соединены с адресными выходами счетного устройства и адресными входами блока памяти, информационные входы которого соединены с инфор.мационными выходами счетного

5 устройства и счетчика числа, а выходы соединены с информационными входами счетчика числа, выходы переполнения при суммировании и при вычитании соединены с первыми входами анализаторов переполнения при суммировании и при вычитании соответственно, выходы которых соединены со счетны.ми входами счетчика числа, вход сброса которого соединен с первым выходом блока установки, второй выход которого соединен с входом сброса счетчи5 ка адреса и с выходом сброса счетного устройства, третий выход блока установки соединен с входами синхронизации анализаторов переполнения и с выходо.м синхронизации счетного устройства, четвертый выход блока установки соединен с входом разре0 шения записи блока памяти, вход записи которого соединен со счетным входом счетчика адреса, с первым входом блока установки и со счетным входом счетного устройства, выход переполнения счетчика адреса соединен с входами установки анализаторов переполнения, с вторым входом узла установки и с выходом переполнения счетного устройства, третий вход узла установки соединен с информационным выходом счетчика адреса, четвертый и пятый

0 входы узла установки соединены с входами синхронизации и информационным счетного устройства соответственно, выход сброса счетного устройства соединен с входом сброса выходного дешифратора и с входом записи вычитающего счетчика, выходы син5 хронизации и переполнения счетного устройства соединены с входами синхронизации и установа выходного дешифратора соответственно, входы данных которого соединены с информационными выходами счет- .. ного устройства, выход переполнения вычитаюшего счетчика соединен с входом синхронизации счетного устройства, информационный вход которого соединен с выходом формирователя синхронизирующих импульсов и с входом сброса вычитающего счет5 чика.

2. Генератор по п. I, отличающийся тем, что блок установки счетного устройства содержит первый, второй, третий и четвертый

триггеры, информационный вход первого триггера соединен с информационным входом блока установки, синхровход которого соединен с синхровходами первого и четвертого триггеров, выход первого триггера соединен с информационным входом второго триггера, и с первым входом первого элемента И, второй вход которой соединен с первым входом второго элемента И, с выходом элемента равенства и с третьим выходом блока установки, первый выход которой соединен с выходом первого элемента И, второй вход второго элемента И соединен с информационным входом четвертого тригФиг.З

гера и с прямым выходом второго триггера, инверсный выход которого соединен со счетным входом третьего триггера, выход которого соединен с первым входом элемента равенства, второй вход которого соединен с третьим входом блока установки, второй вход которого соединен с синхровходом второго триггера, вход сброса которого соединен с инверсным выходом четвертого триггера, прямой выход которого соединен с вторым выходом блока установки, четвертый выход которого соединен с выходом второго элемента И, вход сброса соединен с входом сброса четвертого триггера.

Фиг. 2

13

2ii

r

25

:гФиг Л

фиг. 5

Фиг. 6

сриг. 7

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь сетки частот | 1985 |

|

SU1287257A1 |

| Интегрирующий частотомер | 1985 |

|

SU1308921A1 |

| Частотомер-периодомер | 1985 |

|

SU1337800A1 |

| Логический анализатор | 1984 |

|

SU1259267A1 |

| Формирователь сетки частот | 1988 |

|

SU1656674A1 |

| Генератор серии задержанных импульсов | 1985 |

|

SU1372598A1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ НЕИСПРАВНОСТЕЙ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1992 |

|

RU2030784C1 |

| Счетное устройство | 1979 |

|

SU856011A1 |

| Преобразователь двоичного кода в код с произвольным весом младшего разряда | 1985 |

|

SU1325708A1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ ОТКАЗОВ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1996 |

|

RU2099777C1 |

Изобретение предназначено для вычислительных устройств и может быть использовано в синхронизаторах, управляющих и вычислительных снстемах. Цель изобретения - 1ювын1ение надежности устройства и его быстродействия. Устройство содержит суммирующее счетное устройство I, вычитаюн1ий счетчик 7, дешифратор 8, формирователь 10 имиульсоЕ онорной частоты и формирователь II импульсов синхрони- зании. Введение анализатора 9 неренолпе- ний, вьпюлпение суммируюн1его счетного устройства 1 в виде счетчиков 2 и 3 адреса и числа, блока 4 памяти, анализатора 5 переполнений и б,1ока 6 установки и образование новых функниональных связей позволяет достичь ноставленную цель. I з.п.ф-лы, 7 и. 1. сл со о со го СП

| Формирователь импульсных последовательностей | 1978 |

|

SU790197A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| Генератор запаздывающих и опережающих импульсов | 1981 |

|

SU961119A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-05-07—Публикация

1984-12-06—Подача