( ЦИФРОВОЙ РЕГИСТРАТОР ФОР№1 ПЕРИОДИЧЕСКИХ СИГНАЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой регистратор формы однократных и редкоповторяющихся сигналов | 1981 |

|

SU970266A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1982 |

|

SU1043677A1 |

| Устройство для измерения времени установления выходного сигнала цифроаналогового преобразователя | 1990 |

|

SU1716601A2 |

| Устройство для вычисления показателя экспоненциальной функции | 1986 |

|

SU1335990A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1983 |

|

SU1129611A1 |

| Устройство для преобразования контролируемых параметров | 1986 |

|

SU1320816A1 |

| Устройство для измерения времени установления цифроаналогового преобразователя | 1986 |

|

SU1432776A1 |

| Многоканальный преобразователь напряжения в код | 1977 |

|

SU658586A1 |

| Ультразвуковой дефектоскоп | 1988 |

|

SU1663534A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

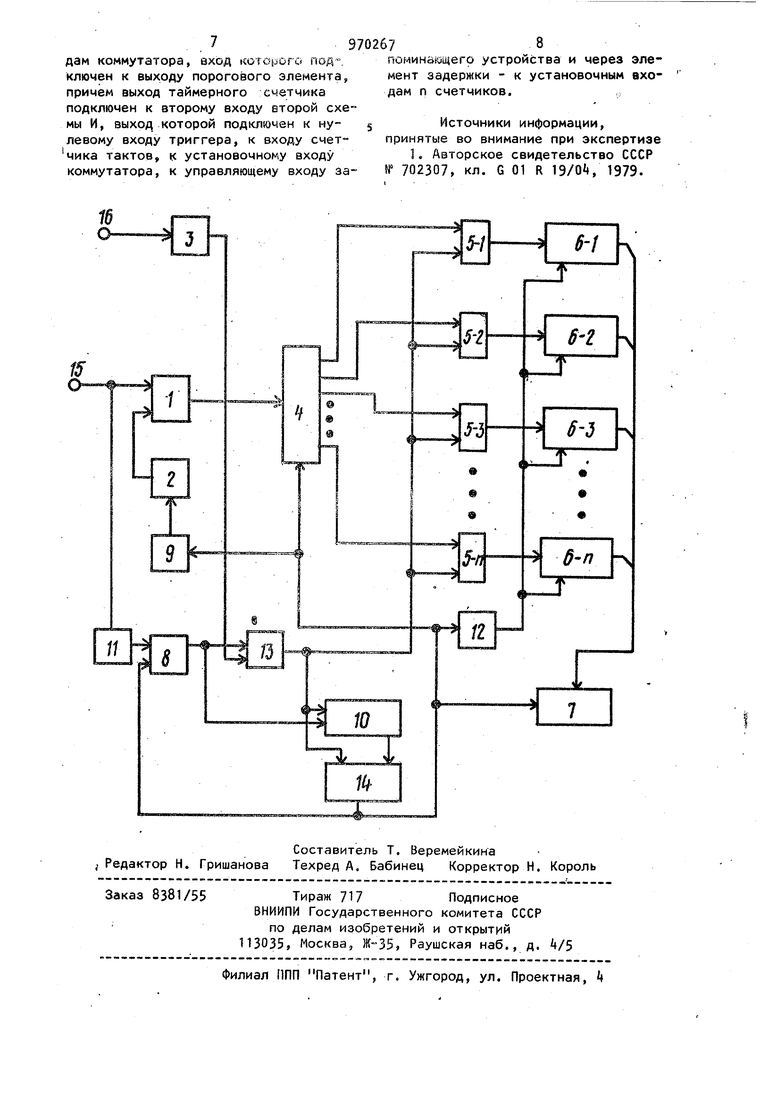

Изобретение относится к контрольно-измерительной технике и может быт использовано при анализе формы перио дических сигналов. Известно устройство для регистрации формы повторяющихся сигналов наносекундной длительности, содержащее блок синхронизации, линию задержки, блок управления, последовательно соединенные запоминающее устройство и устройство вывода результатов.измере ния , пороговый элемент, последовател но Соединенные счетчик тактов и цифроаналоговый преобразователь, двухвх довой элемент И-НЕ, Два преобразователя длительности в число импульсов, два коммутатора на п выходов и две группы счетчиков по п счетчиков в каждой, причем первый вход порогового элемента через линию задержки соединен с входом блока синхронизации и подключен к входу устройства, выход порогового элемента соединен с входом первого преобразователя длите ности в число импульсов и первым входом элемента И-НЕ, выход которого подключен к входу второго преобразователя длительности в число импульсов, выходы преобразователей длительности в число импульсов подключены к входам соответствующих коммутаторов, выходы которых подключены к входам соответствующей группы счетчиков, выход блока синхронизации подключен к второму входу элемента И-НЕ, входу блока управления и через счетчик тактов и цифроаналоговый преобразователь к второму входу порогового элемента, выходы блока управления подключень к управляющим входам блока синхронизации, запоминающего устройства, устройства вывода информации и к установочным входам счетчиков и преобразователей длительности в число импульсов ГО Недостатком этого устройства является невысокая точность регистрации сигналов сложной формы, обусловленная тем, что определение временных параметров сигнала осуществляется путем измерения интервалов времени межДУ двумя соседними пересечениями уровня опорного напряжения регистрируемым сигналом. Очевидно, что в таком устройстве сигналЫвСЛожной формы с длительностями интервалов пересечения уровня опорного напряжения менее величины кванта преобразования At вообще не зарегистрируется. Кроме того, это устройство не позволяет регистрировать сигналы с высокой точностью в широком диапазоне временных интервалов, та1 как регистрация сигнала происходит после пропускания его через линию задержки. Цель изобретения - повышение точност.и регистрации сигналов сложной формы и расширение временного диапазо на регистрируемых сигналов. Поставленная цель достигается тем что в цифровой регистратор формы периодических сигналов, содержащий последовательно соединенные счетчик так тов и цифроаналоговый преобразователь выход которого подключен к первому входу порогового элемента, коммутатор на п выходов, п счетчиков, выходы которых подключены к запоминающему устроиству, введены эталонный генератор п электронных ключей, формирователь, триггер, таймерный счетчик, элемент задержки, две схемы И, управляющий вход, подключенный к входу эталонного генератора, причем вход устройства подключен к второму входу порогового элемента и через формирователь к единичному входу триггера, выход которого подключен к установочному входу таймерного счетчика и к первому входу первой схемы И, второй вход которой подключен к выходу эталонного генератора, а выход подключен к первому входу второй схемы И, к счетному входу таймерного счетчика и к первым входам п электронных ключей, выходы которых соответственно подклю14ены к входам п счетчиков, а вто15ые входы п электронных ключей подключены соответственно к п выходам коммутатора, вход которого подключен к выходу порогового элемента, причем выход таймерного счетчика подключен к второму входу второй схемы И, выход которой подключен к нулевому входу триггера, к входу счетчика тактов, к установоч ному входу коммутатора, к управляюще му входу запоминающего устройства и через элемент задержки - к установочным входам п счетчиков. На чертеже представлена функциональная схема предлагаемого устройства. Устройство содержит пороговый элемент 1, цифроаналоговый преобразователь 2,- эталонный генератор 3, коммутатор k на К1 выходов, и последовательно включенных электронных ключей -,,,., 5-п и счетчиков 6-1,..,6-п, запоминающее устррйство 7 триггер 8, счетчик 9 тактов, таймерный счетчик 10, формирователь 11, элемент 12 задержки и схемы И 13 и 1, входы 15 и 16 устройства. Цепи начальной установки на чертеже не показаны. Устройство работает следующим образом. В исходном состоянии коммутатор 4, триггер 8, счетчики 6-1 ,.. ,.,6-п, таймерный счетчик 10 находятся в нулевом состоянии, в счетчике Э тактов записан код, равный единице, Код, со- . держащийся в счетчике 9 тактов, преобразуется цифроаналоговым преобразо- вателем 2 в соответствующий номеру такта измерения уровень опорного напряжения, который поступает на первый (опорный) вход порогового элемента 1. Таким образом, в исходном состоянии на опорном входе порогового элемента 1 присутствует уровень напряжения, соответствующий первому такту измерения. Исследуемый повторяющийся сигнал, подаваемый на вход 15 устройства, поступает одновременно на второй вход порогового элемента 1 и вход формирователя 11. При пересечении регистрируемым сигналом уровня опорного напряжения порогового элемента на его выходе формируются сигналы, которые проходят на вход коммутатора и послб довательно появляются на его , втором и т. д. выходах. Эти сигналы поступают на первые входы соответствующих электронных ключей ,...,5-п, разрешая прохождение через них импульсов эталонного генератора, на вход счетчиков 6-1,..., 6-п, и являются началом интервалов времени, определяющих временное положение сигнала на уровне опорного напряжения. Число выходов п коммутатора t, а следовательно, и число электронных ключей и счетчиков определяется степенью сложности регистрируемых сигна лов. Исследуемый сигнал через.формирователь 11 подается на единичный вход триггера 8 и перебрасывает его в состояние логической единицы. Сигнал с выхода триггера 8 поступает на первы вход схемы И 13 и снимает сигнал сброса с установочного входа таймерного счетчика 10. При этом выходные импульсы эталонного генератора 3 через схему И 13 проходят на счетный вход таймерного счетчика 10 и через электронные ключи 5-1,...,5-п - на входы счетчиков 6-1,..,6-п. Момент окончания процесса измерения в каждом такте определяется таймерным счетчиком 10. Он формирует интервал времени при подсчете опреде ленного числа импульсов эталонного i генератора 3. Число разрядов таймериого счетчи ка 10 выбирается из учета того, чтоб формируемый интервал времени превыша длительность исследуемого сигнала. При заполнении таймерного счетчика 10 с его выхода на первый вход схемы И 1 подается сигнал логической единицы, по которому на выходе схемы И 14 синхронно с импульсами эталонного генератора, поступающими на ее второй вход формируется сигнал конца измерения. Этот сигнал поступает на установочный вход коммутатора k, устанавливая его в исходное состояние. При этом прекращается сче импульсов в счетчиках 6-1,,..,6-п, в которых окажуются записанными коды определяющие временное положение точек пересечения регистрируемым си|- налом уровня опорного напряжения относительно единого сигнала конца измерения, синхронизированного импульсами эталонного генератора. Сигнал конца измерения поступает также на вход счетчика 9 тактов, на нулевой вход триггера 8, на управляющий вход запоминающего устройства 7 и через элемент 12 задержки - на установочные входы счетчиков 6-1,..., 6-п. При подаче сигнала конца измерения на нулевой вход триггера 8 он устанавливается в исходное состояние, закрывает по первому входу схему И 13 и устанавливает в нулевое состояние таймерный счетчик 10. Сигнал конца измерения, подаваемый ,на вход счетчика 9 тактов, увеличивает его состояние на единицу. 8 результате на опорном входе порогового элемента 1 появляется уровень опорного напряжения, соответствующий следующе- ; му такту измерения. Сигнал конца измерения, подаваемый на управляющий вход -запоминающего устройства 7, считывает информацию со счетчиков 6-1,... 6-п в запоминающее устройство, и, пройдя через элемент задержки 12, обнуляет счетчики. Регистратор готов к следующему такту измерения. Расширение временного диапазона регистрируемых сигналов .в данном устройстве обеспечивается путем изменения частоты эталонного генератора 3, для чего на управляющий вход генератора подается сигнал с входа 16 устройства. Формула, изобретения Цифровой регистратор формы периодических сигналов, содержащий последовательно соединенные счетчик тактов «и цифроаналоговый преобразователь, выход которого подключен к первому входу порогового элемента, коммутатор на п выходов, а также п счетчиков, выходы которых подключены к запоминающему устройству, отличающийся тем, что, с целью повышеч ния точности регистрации сигналов сложной формы и расширения временного диапазона регистрируемых сигналов, он дополнительно содержит эталонный генератор, п электронных ключей, формирователь, триггер, таймерный счетчик, элемент задержки, две схемы И, управляющий вход, подключенный к вхоч ду эталонного генератора, причем вход устройства подключен ко второму входу порогового элемента и через формирователь - к единичному входу триггера, выход которого подключен к установочному входу таймерного счетчика и к первому входу первой схемы И, второй вход которой подключен к выходу эталонного генератора, а выход подключен к первому входу второй схемы И, к счетному входу таймерного счетчика и к первым входам п электрон ных ключей, выходы которых соответст- зенно подключены к входам п счетчиков, а BTopbie входы п электронных ключей подключены соответственно к п выхо79702678

дам коммутатора, вход Korosjoro под-. поминающего устройства и через элеключен к выходу порогового элемента, причем выход таймерного счетчика подключен к второму входу еторой схемы И, выход которой подключен к ну- g Источники информации, левому входу триггера, к входу счет- принятые во внимание при экспертизе чика тактов, к установочному входу коммутатора, к управляющему входу замент задержки - к установочным аходам п счетчиков.

Авторы

Даты

1982-10-30—Публикация

1981-04-03—Подача