первого коммутатора, первые входы элементов И группы соединены с выходами ключей первой группы, первые входы которых подключены к П1ине логической единицы, а вторые входы - к тине логического нуля, вторые входы элементов И группы являются информационными входами устройства, выходы второго счетчика соединены с другими входами второго коммутатора, выходы которого являются адресными выходами устройства, первый и второй входы переключателя соединены соответственно с тиной логической единицы и с шиной логического нуля и являются управляющими входами устройства, управляющим выходом которого является выход первого элемента задержки.

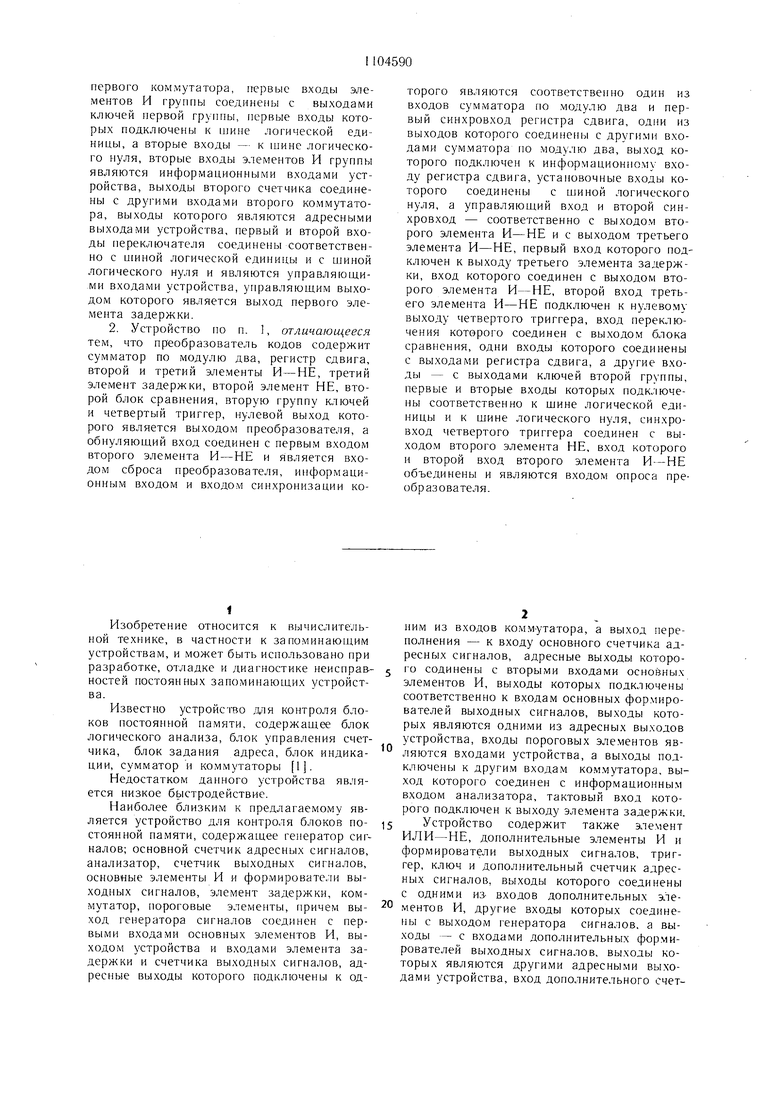

2. Устройство по п. 1, отличающееся тем, что преобразователь кодов содержит сумматор по модулю два, регистр сдвига, второй и третий элементы И-НЕ, третий элемент задержки, второй элемент НЕ, второй блок сравнения, вторую группу ключей и четвертый триггер, нулевой выход которого является выходом преобразователя, а обнуляющий вход соединен с первым входом второго элемента И - НЕ и является входом сброса преобразователя, информационным входом и входом синхронизации которого являются соответственно один из входов сумматора по модулю два и первый синхровход регистра сдвига, одни из выходов которого соединены с другими входами сумматора по модулю два, выход которого подключен к информационному входу регистра сдвига, установочные входы которого соединены с шиной логического нуля, а управляющий вход и второй синхровход - соответственно с выходом второго элемента И-НЕ и с выходом третьего элемента И-НЕ, первый вход которого подключен к выходу третьего элемента задержки, вход которого соединен с выходом второго элемента И-НЕ, второй вход третьего элемента И-НЕ подключен к нулевому выходу четвертого триггера, вход переключения которого соединен с выходом блока сравнения, одни входы которого соединены с выходами регистра сдвига, а другие входы - с выходами ключей второй группы, первые и вторые входы которых подключены соответственно к шине логической единицы и к щине логического нуля, синхровход четвертого триггера соединен с выходом второго элемента НЕ, вход которого и второй вход второго элемента И-НЕ объединены и являются входом опроса преобразователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Устройство для регистрации цифровой информации | 1986 |

|

SU1386915A2 |

| Устройство для контроля монтажа | 1985 |

|

SU1352505A1 |

| Устройство для задания тестов | 1982 |

|

SU1096612A2 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

| Коррелометр | 1980 |

|

SU1062717A1 |

| Устройство для задания тестов | 1983 |

|

SU1168951A1 |

| Устройство для испытаний датчиков давления | 1983 |

|

SU1129624A1 |

| Адаптивный коммутатор телеизмерительной системы | 1990 |

|

SU1785020A1 |

| Устройство для передачи информации | 1989 |

|

SU1700571A1 |

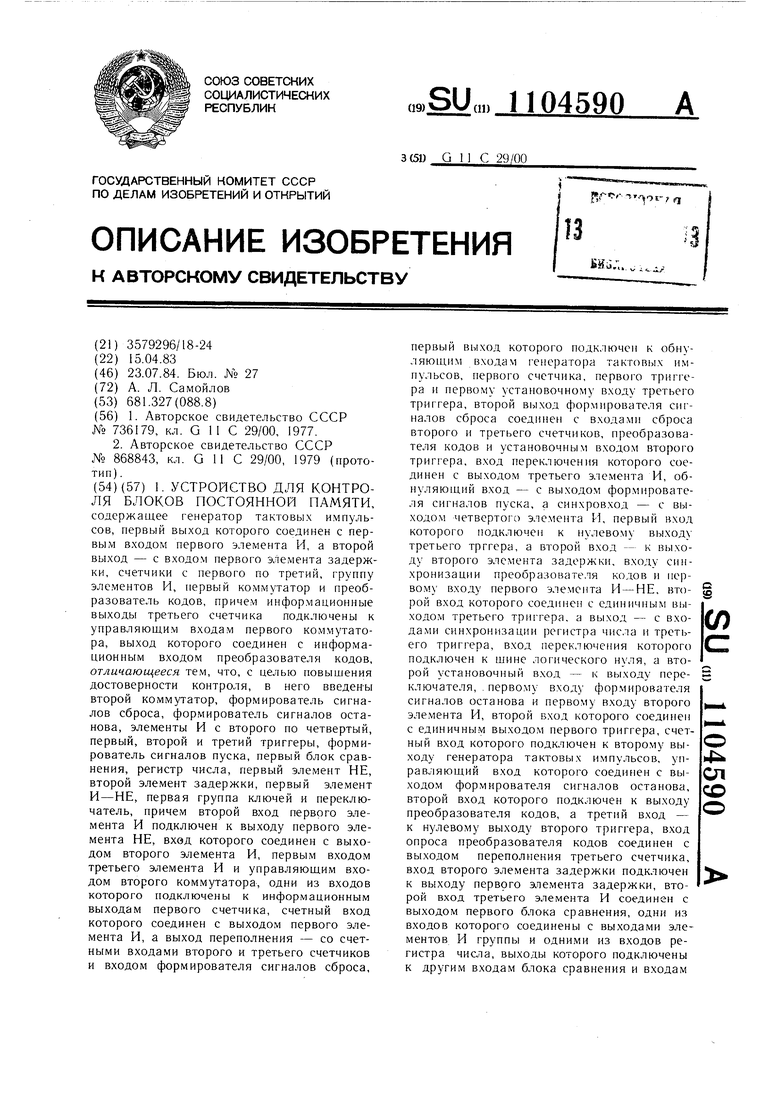

1. УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ ПОСТОЯННОЙ ПАМЯТИ, содержащее генератор тактовы.х импульсов, первый выход которого соединен с первым входом первого элемента И, а второй выход - с входом первого элемента задержки, счетчики с первого по третий, группу элементов И, первый коммутатор и преобразователь кодов, причем информационные выходы третьего счетчика подключены к управляющим входам первого коммутатора, выход которого соединен с информационным входом преобразователя кодов, отличающееся тем, что, с целью повышения достоверности контроля, в него введены второй коммутатор, формирователь сигналов сброса, фор.мирователь сигналов останова, элементы И с второго по четвертый, первый, второй и третий триггеры, формирователь сигналов пуска, первый блок сравнения, регистр числа, первый элемент НЕ, второй элемент задержки, первый элемент И-НЕ, первая группа ключей и переключатель, причем второй вход первого элемента И подключен к выходу первого элемента НЕ, вход которого соединен с выходом второго элемента И, первым входом третьего элемента И и управляющим входом второго коммутатора, одни из входов которого подключены к информационным выходам первого счетчика, счетный вход которого соединен с выходом первого элемента И, а выход переполнения - со счетными входами второго и третьего счетчиков и входом формирователя сигналов сброса. первый выход которого подключен к обнуляющим входам генератора тактовых импульсов, первого счетчика, первого триггера и первому установочному входу третьего триггера, второй выход формирователя сигналов сброса соединен с входами сброса второго и третьего счетчиков, преобразователя кодов и установочным входом второго триггера, вход переключения которого соединен с выходом третьего элемента И, обнуляющий вход - с выходом формирователя сигналов пуска, а синхровход - с выходом четвертого элемента И, первый вход которого подключен к нулевому выходу третьего трггера, а второй вход - к выходу второго элемента задержки, входу синхронизации преобразователя кодов и перi вому входу первого элемента и - НЕ. второй вход которого соединен с единичным вы(Л ходом третьего триггера, а выход - с входами синхронизации регистра числа и третьего триггера, вход переключения которого подключен к щине логического нуля, а второй установочный вход - к выходу переключателя, - первому входу формирователя сигналов останова и первому входу второго элемента и, второй вход которого соединен с единичным выходом первого триггера, счетный вход которого подключен к второму вы4 СП ходу генератора тактовых импульсов, управляющий вход которого соединен с выходом формирователя сигналов останова, СО второй вход которого подключен к выходу преобразователя кодов, а третий вход - к нулевому выходу второго триггера, вход опроса преобразователя кодов соединен с выходом переполнения третьего счетчика, вход второго элемента задержки подключен к выходу первого апемента задержки, второй вход третьего элемента И соединен с выходом первого б.яока сравнения, одни из входов которого соединены с выходами элементов и группы и одними из входов регистра чиста, выходы которого подключены к другим входам блока сравнения и входам

f

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть использовано при разработке, 01ладке и диагностике неисправностей постоянных запоминающих устройства.

Известно устройство дан контроля блоков постоянной памяти, содержащее блок логического анализа, блок управления счетчика, блок задания адреса, блок индикации, сумматор и коммутаторы 1.

Недостатком данного устройства является низкое бЬ1стродействие.

Наиболее близким к предлагаемому является устройство для контроля блоков постоянной памяти, содержащее генератор сигналов; основной счетчик адресных сигналов, анализатор, счетчик выходных сигналов, основные элементы И и формирователи выходных сигналов, элемент задержки, коммутатор, пороговые элементы, причем выход генератора сигналов соединен с первыми входами основных элементов И, выходом устройства и входами элемента задержки и счетчика выходных сигналов, адресные выходы которого подключены к одним из входов комм-утатора, а выход переполнения - к входу основного счетчика адресных сигналов, адресные выходы которого содинены с вторыми входами основных элементов И, выходы которых подключены соответственно к входам основных формирователей выходных сигналов, выходы которых являются одними из адресных выходов устройства, входы пороговых элементов являются входами устройства, а выходы подключены к другим входам ко.м.мутатора, выход которого соединен с информационным входом анализатора, тактовый вход которого подключен к выходу элемента задержки.

Устройство содержит также элемент ИЛИ-НЕ, дополнительные элементы И и формирователи выходных сигналов, триггер, ключ и дополнительный счетчик адресных сигналов, выходы которого соединены с одними из. входов дополнительных элементов И, другие входы которых соединены с выходом генератора сигналов, а выходы - с входами дополнительных формирователей выходных сигналов, выходы которых являются другими адресными выходами устройства, вход дополнительного счетчика адресных сигналов подключен к инверсному выходу триггера, установочный вход которого подключен к выходу переполнения основного счетчика адресных сигналов, вход сброса триггера содинен с входом сброса анализатора и с одним из выводов ключа, другой вывод которого соединен с шиной нулевого потенциала, прямой выход триггера и выход переполнения дополнительного счетчика адресных сигналов соединены с входами элемента ИЛИ-НЕ, выход которого соединен с управляющим входом генератора сигналов 2.

Недостатком известного устройства является низкая достоверность контроля вследствие того, что при контроле блока постоянной памяти проверяется информация поочередно во всех разрядах каждого адреса и, следовательно, период смены адреса в К раз (где К - число разрядов ПЗУ) больше периода обращения к ПЗУ, а также вследствие отсутствия контроля взаимного влияния информации, записанной в различных микросхемах и контроля индивидуально каждого разряда ПЗУ.

Цель изобретения - повышение достоверности контроля блоков постоянной памяти.

Поставленная цель достигается тем, что в устройство для контроля блоков постоянной памяти, содержащее генератор тактовых импульсов, первый выход которого соединен с первым входом первого элемента И, а второй выход - с входом первого элемента задержки, счетчики с первого по третий, группу элементов И, первыйкоммутатор и преобразователь кодов, причем информационные выходы третьего счетчика подключены к управляющим входам первого коммутатора, выход которого содинен с информационным входом преобразователя кодов, введены второй коммутатор, формирователь сигналов сброса, формирователь сигналов останова, элементы И с второго по четвертый, первый, второй и третий триггеры, формирователь сигналов пуска, первый блок сравнения, регистр числа, первый элемент НЕ, второй элемент задержки, первый элемент И-НЕ, первая группа ключей и переключатель, причем второй вход первого элемента И подключен к выходу первого элемента НЕ, вход которого соединен с выходом второго элемента И, первым входом третьего элемента И и управляющим входом второго коммутатора, одни из входов которого подключены к информационным выходам первого счетчика, счетный вход которого соединен с выходом первого элемента И, а выход переполнения - со счетными входами второго и третьего счетчиков и входом формирователя сигналов сброса, первый выход которого подключен к обнуляющим входам генератора тактовых импульсов, первого счетчика, iiepBoio триггера и первому установочному входу третье|-о триггера, второй выход формирователя сигналов сброса соединен с входами сброса второго и третьего счетчиков, преобразователя кодов и установочным входом второго триггера, вход переключения которого соединен с выходом третьего элемента И, обнуляющий вход - с выходом формирователя сигналов пуска, а синхровход - с выходом четвертого элемента И, первый вход которого подключен к нулевому выходу третьего триггера, а второй вход - к выходу второго элемента задержки, входу синхронизации преобразователя кодов и первому входу первого элемента И-НЕ, второй вход которого соединен с единичным выходом третьего триггера, а выход - с входами синхронизации регистра числа и третьего триггера, вход переключения которого подключен к шине логического нуля, а второй установочный вход - к выходу переключателя, первому входу формирователя сигналов останова и первому входу второго элемента И, второй вход которого соединен с единичным выходом первого триггера, счетный вход которого подключен к второму выходу генератора тактовых импульсов, управляющий вход которого соединен с выходом формирователя сигналов останова, второй вход которого подключен к выходу преобразователя кодов, а третий вход - к нулевому выходу второго триггера, вход опроса преобразователя кодов соединен с выходом переполнения третьего счетчика, вход второго элемента задержки подключен к выходу первого элемента задержки, второй вход третьего элемента И соединен с выходом первого блока сравнения, одни из входов которого соединены с выходами элементов И группы и одними из входов регистра числа, выходы которого подключены к другим входам блока сравнения и входам первого коммутатора, первые входы мементов И группы соединены с выходами ключей первой группы, первые входы которых подключены к щине логической единицы, а вторые входы - к щине логического нуля, вторые входы элементов И группы являются информационными входами устройства, выходы второго счетчика соединены с другими входами второго коммутатора, выходы которого являются адресными выходами устройства, первый и второй входы переключателя соединены соответственно с щиной логической единицы и с щиной логического нуля и являются управляющими входами устройства, управляющим выходом которого является выход первого элемента задержки.

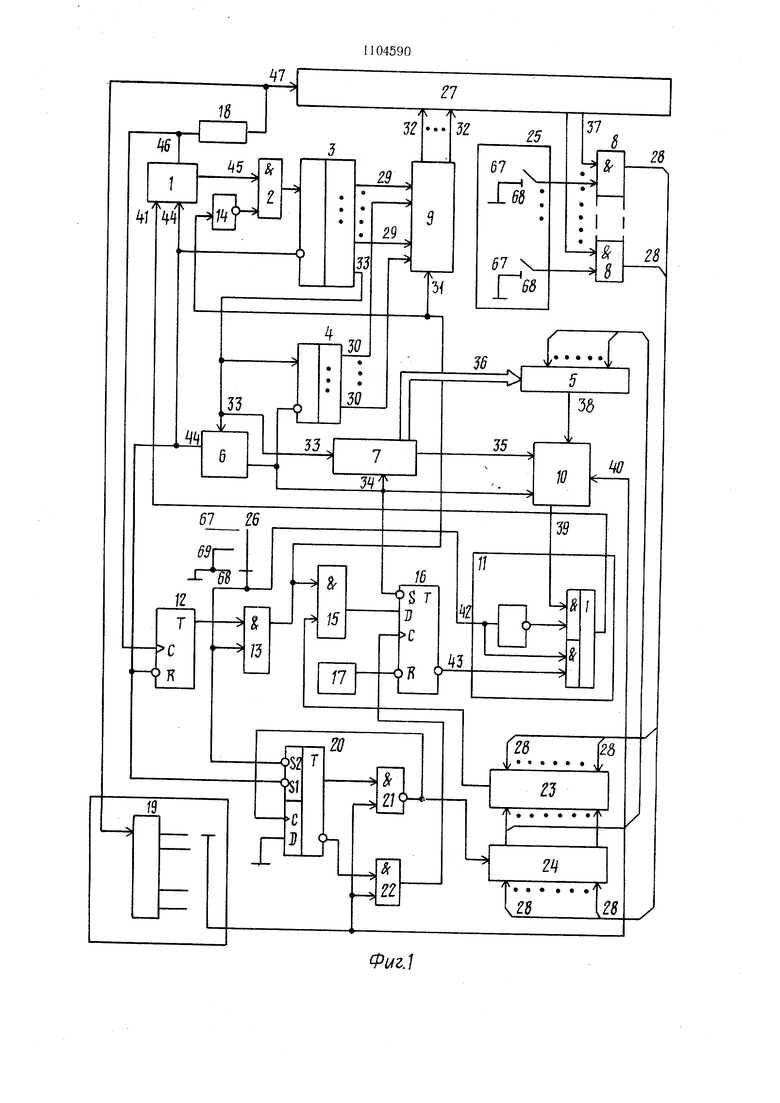

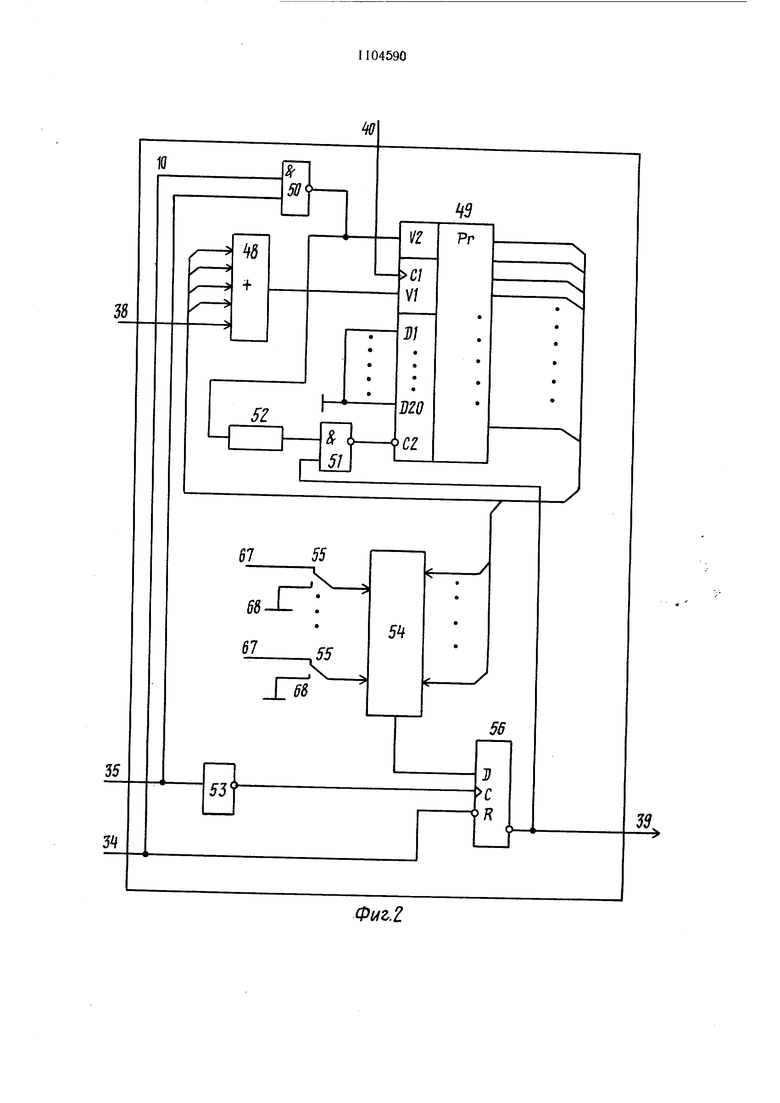

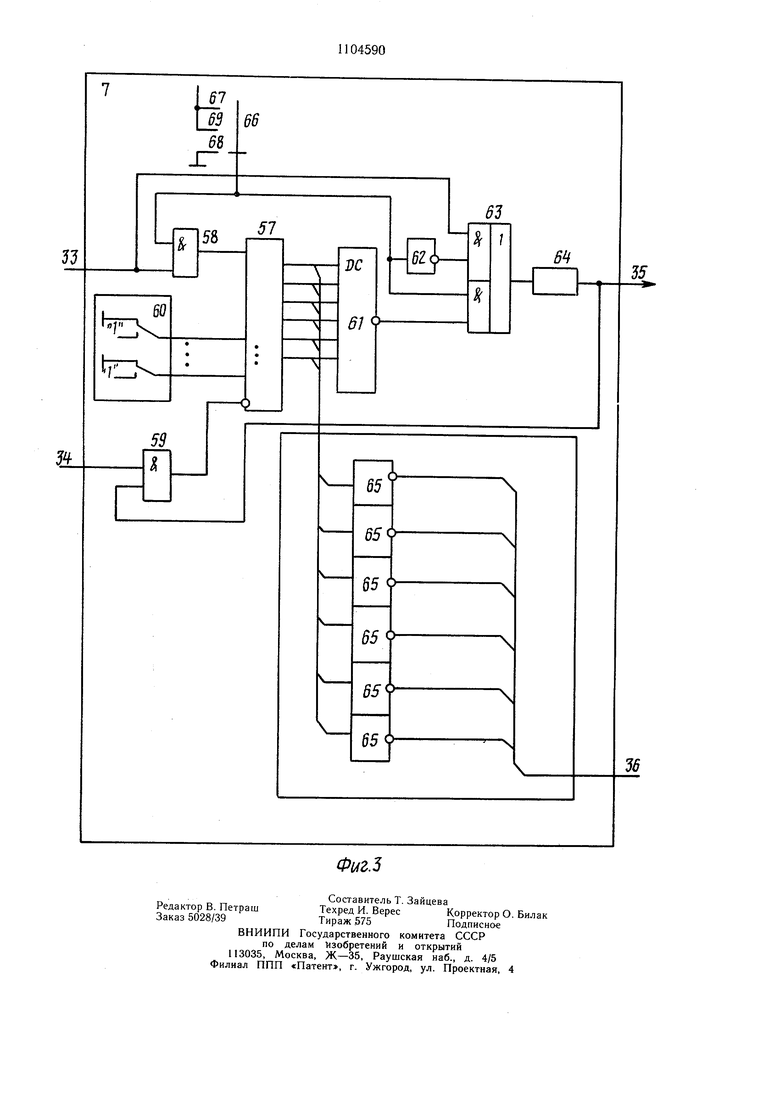

Преобразователь кодов содержит сумматор по модулю два, регистр сдвига, второй и третий элементы И-НЕ, третий элемент задержки, второй элемент НЕ, второй блок сравнения, вторую группу ктючей и четвертый триггер, нулевой выход которого является выходом преобразователя, у обнуляющий вход соединен с первым входом второго элемента И-НЕ и является входом сброса преобразователя, информационным входом и входом синхронизации которого являются соответственно оди1; из входов сумматора по модулю два и первый синхровход регистра сдвига, одни из выходов которого соединены с другими входами сумматора но модулю два, выход которого подключен к информационному входу регистра сдвига, установочные входы которого соединены с шиной логического нуля, а управляющий вход и второй синхровход- соответственно с выходом второго элемента И-НЕ и с выходом третьего элемента И-НЕ, первый вход которого подключен к выходу третьего элемента задержки, вход которого соединен с выходом второго э.темента И-НЕ, второй вход третьего элемента И-НЕ подключен к нулегюму выходу четвертого триггера, вход переключения которогр соединен с выходом блока сравнения, одни входы которого соединены с выходами регистра сдвига, а другие входы с выходами ключей второй группы, первые и вторые входы которых подключены соответственно к шине логической единицы и к шине логического нуля, синхровход четвертого триггера соединен с выходом второго элемента НЕ, вход которого и второй вход второго элемента И-НЕ объединены и являются входом опроса преобразователя. На фиг. 1 приведена функциональная схема предлагаемого устройства; на фиг. 2 схема преобразователя кодов; на фиг. 3 - схема третьего счетчика. Устройство для контроля блоков постоянной памяти содержит (фиг. ) генератор 1 тактовых импульсов, первый эле.мент И 2, первый 3 и второй 4 счетчики, первый коммутатор 5, формирователь 6 сигналов сброса, третий счетчик 7, группу элементов И 8, второй коммутатор 9, преобразователь 10 кодов, формирователь И сигналов останова, первый триггер 2, второй элемент И 13, первый элемент НЕ 14, третий элемент И 15, второй триггер 16, формирователь 17 сигналов пуска, первый элемент 18 задержки, второй элемент 19 задержки с подвижным контактом, третий триггер 20, первый элемент И-НЕ 21, четвертый элемент И 22, первый блок 23 сравнения, регистр 24 чисел, первую группу ключей 25 и переключатель 26. На фиг. 1 показан контролируемый блок 27 постоянной памяти и обозначены выходы 28 элементав И 8 группы, информационные выходы 29 счетчика 3, выходы 30 счет0чика 4. у1 |1авл);н;|11ий вход 31 коммутатора 0,адресн;;1с вы.(),аы 32 устройства, выход 33 мере11олнепмя счетчика 3, выход 3-1 форми1К)вателя (, выход 35 Г срегк)лнения и выходы 36 счетчики 7, информаи. входы 37 уст|), входы 38, выход 39 и ci-n- хровход 40 преобразователя 10, выход 41 и входы 42 и 43 формирователя 11, обкуляюн1,ий вход 44 и выходы 45 и 46 генератора 1,управляюптий выход 47 устройства. Преобразователь 10 .кодов содержит (фи1. 2) сумматор 48 но модулю два, регистр 49 сдвига, второй.50 и третий 51 элементы И-НЕ, третий эле.мент 52 задержки, второй элемент НЕ 53, второй блок 54 сравнения, вторую i pynny ключей 55 и четвертый тригге) 56. Огетчик 7 содержит (фиг. 3) счетчик 57. циклов, эле.менты И 58 .ч 59, 1-руппу мючей 60, дешифратор 61, элемент НЕ 62, элемент 2 Н-ИЛИ 63, элемент 64 задержки, Ipyniiy эле.меитов НЕ 65 и нереключатель 66 режимов, механически связанный с переключате.аем 26 (фиг. I) и перек.чючаклцийся синхронно с ни.м. На фиг. --3 обозначены шина 67 логической единицы и шина 68 логического нуля, соответствующие положения.м «Эталонный контроль, «Разрядный контроль переключателей 26 и 66, а также обозначено положение 69 «Сигнатурный контроль переключателей 26 и 66. Устройство работает следующим образом. Исходное состояние устройства определяется положением переключателей в генераторе 1, ключей 25, переключателей 26 (фиг. 1 ) 60 и 66 (фиг. 3), ключей 55 (фиг. 2), которые устанавливаются вручную оператором. Переключатели в генераторе 1 определяют период обрац.1.ения к проверяе.мому блоку 27. С помощью переключателей 26 и 66 выбирается режим работы устройства (эталонный, сигнатурный). Ключи 25 отключают любой из разрядов контролируемого блока 27. С помощью к„тючей 60 устанавливается разрядность ком.мутатора 5 в соответствии с разрядностью проверяемого блока 27. С помонаью ключей 55 устанавливается ожидаемый результирующий код (сигнатура). Эле.менто.м 19 задержки устанавливается предполагаемое значение времени выборки чисел из контролируе.мого блока 27. Устройство работает в трех режи.мах: режим еигнатурного анализа любого разряда или всех разрядов проверяемого блока памяти и режим эталонного контроля. Режим сигнатурного анализа одного любого разряда заключается в проверке содержимого любого выбранного оператором разряда блока 27. Для этого оператор устанавливает на ключах 60 код номера проверяемого разряда, переключатели 26 (фиг. 1) и 66 (фиг. 3) в положение 68.

При этом поступает разреинающий (нулевой) curiia.i с выхода переключателя 26 на вход элемента И 13, на второй установочный вход трип-ера 20 и; на вход 42 формирователя 11. В сметчике 7 (фиг. 3) с выхода переключателя 66 запрещающий сигнал поступает на первый вход э.чемента И 58. на вход элемента НЕ 62 и на третий вход элемента 2И-ИЛИ 63. 1рн это.м фор.мирователь 11 будет пропускать резу.гьтат анализа с выхода 39 на выход 41 генератора 1. При нажатии оператором кнопки «Сброс (не показано) на выходах 44 и 34 формирователя 6 появляется сигнал сброса отрицательной полярности, которы.ц поступает в генератор 1 и устанавливает его в начальное состояние. Одновременно происходит обнуление счетчиков 3 и 4, ввод начального кода в счетчике 7, обнуление регистра 49 и сброс триггера 56 в преобразователе 10.

С выхода эле.мента И 3 нулевой потенциал направляется на вход 3 ко.чмутатора 9 и разрешает прохождение через него кода адреса с выходов 29 счетчика 3. Кро.ме того, сигнал с выхода элемента И 13 ироходит через элемент НЕ 14 и pa3peHjaeT прохождение тактовых импульеов с выхода 45 генератора 1 на счетный вход счетчика 3. При этом на единичном выходе триггера 20 будет единичный потенциал, разре иающий прохождение импульсов с выхода элемента 19 задержки через элемент И-НЕ 21 на синхровход регистра 24.

При отпускании кнопки «СБРОС сигнал обнуления и начальной установки на выходах 34 и 44 исчезнет. При этом генератор 1 начинает вырабатывать тактовые импульсы. Первый тактовый импульс появляется на выходе 46 и через апемент 18 задержки поступает в виде импульса обращения на выход 47 устройства и на вход элемента 19 задержки. Одновременно с импульсом обращения на выходы 32 поступает через коммутатор 9 код нулевого адреса со счетчика 3 (при появлении первого импульса обращения на выходе 45 тактового импульса не будет, поэтому в первом такте счетчик 3 остается в нулевом состоянии). По первому импульсу обращения и нулевому коду адреса из блока 27 считывается двоичное слово, которое проходит через разрешенные эле.менты И 8 и поступает на входы регистра 24. Импульс обращения задерживается элементом 19 задержки на время выборки, затем через a eмeнт И-НЕ 21 направляется на синхровход регистра 24 и записывает в него код слова, поступивший на входы 28. С выходов регистра 24 слово направляется на коммутатор 5.

В соответствии с кодом, поступившим с БЫХОДО& счетчика 7 на входы 36 коммутатора 5, через него проходит сигнал только

выбранного разряда считанного с.юва па вход 38 преобразователя 10. ijie (1ио этого разря.а,а с приходом IiiiixiJOiiMny.ibca на 40 записывается в регистр 49. Затем на выходе 45 появляется п.мпульс, который переключает счетчик 3 в состояние, соответствующее коду первого адреха. код проходит через коммутато 9 isa Bijixoды 32 устройства.

Одповременпо с выхода 47 поступает ИМПУЛЬС обращения на вход блока 27 памяти. При этом из блока 27 считывается второе слово, записанное по первому адресу, которое анало1Ч чно первому, записывается в регистр 24 числа и поступает в

коммутатор 5, где код выбранного разряда второго слова проходит на выход коммутатора 5, записывается в регистр 49 последователы ым кодом.

Аналогично считывается инфор.мация всех остальных слов при последовательной

0 выборке адресов от младшего к последнему старшему. При этом все коды выбранного контролируемого разряда слова блока 27 памяти последовательным кодом записываются в преобразователе 10. С оконча5 нием перебора всех адресов импульс переполнения счетчика 3 поступает на вход 33 формирователя 6 и счетчика 7, проходит через счетчик 7 на вход 35 для опроса результата сравнения в преобразователе 10.

0 В случае равенства считанной информации и ожидаемого кода, установленного на ключах 55, на выходе 39 появляется сигнал равенства единичной полярности, в результате формирователь 11 разрешает генератору 1 продолжить работу в следующем

5 цикле. Далее процесс контроля повторяется. В случае неравенства на выходе 39 преобразователя 10 появляется запрещающий нулевой сигнал, который запрещает дальнейшую работу генератора 1.

д Для работы в режиме сигнатурного анализа всех разрядов проверяемого блока памяти переключатели 26 (фиг. 1) и 66 (фиг. 3) устанавливают в положение 69. Оператор устанавливает ключами 60 код, соответствующий номеру К последнего проверяемого

5 разряда блока 27.

После нажатия кнопки «СБРОС происходит начальная установка аналогично описанному выше. После этого начинается

Q последовательная выборка информации из проверяемого блока 27. Информация последнего К-го разряда, номер которого установлен в счетчике 7, проходит через коммутатор 5 и последоватьным кодом записывается в регистр 49 (фиг. 3). После окон5 чания перебора всех состояний счетчиком 3 заканчивается запись всех считанных символов последнего разряда блока 27 памяти в регистр 49. Импульс переполнения с выхода счетчика 3 поступает на входы 33 формирователя 6 и счетчика 7, в результате на вход 44 генератора 1 поступает импульс копца цикла. Одновременно импульс переполнения поступает на вход 33 счетчика 7 и нереключает его в очередное состояние. Двоичный код с выходов счетчика соответствует номеру нредноследнего (К-1)-го разряда проверяемого блока 27 памяти. После этого генератор 1 начинает формировать импульсы обра1це1П1я и тактовые импу.льсы переключения счетчика 3. Далее начинается новый цикл выборки слов из блока 27, при этом через коммутатор 5 в преобразователь 10 проходит информация (К-1)-го разряда, считанная из блока 27. Аналогично в третьем цикле контроля в регистр 49 записывается информация (К-2)-го разряда из блока 27 памяти. После К циклов контроля заканчивается запись информации всех К разрядов проверяемого блока 27 в регистр 49 нреобразователя 10. На всех входах дешифратора 61 (фиг. 3) будут единичные потенциалы, которые обусловят на его выходе нулевой потенциал, поступающий на выход 35 и на элемент И 59, с выхода которого отрицательный ситнал запишет в счетчик 57 начальный код номера К-го разряда, которЬш набран на ключах 60. Одновременно импульс конца проверки поступает на вход преобразователя 10 и )иксирует на триггере 56 (фиг. 2) результат сравнения считанной (в регистре 49) сигнатуры всех разрядов проверяемого блока 27 с ожидаемым кодом, набранным на 55. В случае равенства процесс ключах проверки повторяется, в случае неравенства происходит останов. Режим эталонного контроля. Положительный результат контроля в рассмотренных выше режимах проверки свидетельствует о правильности записанной в блоке 27 памяти информации и устойчивости ее считывания при последовательном переборе адресов. Эта проверка не дает достоверного ответа о надежности блока, так как в реальной эксплуатации возможен случайный порядок выборки адресов. При этом возможно Неустойчивое считывание слов отдельных адресов после выборки других адресов. В предлагаемом устройстве эта проверка осуществляется в режиме эталонного контроля, в котором осуществляется проверка устойчивости считывания информации из блока 27 памяти при всех сочетаниях адресных нереходов. При этом за эталон принимается число, записанное в регистр 24 в перво.м такте каждого цикла Этот режим реализуется при установке переключателя 26 в положение 67. При этом запрещается прохождение сигналов останова с входа 39 и разрешается прохождение сигнала с выхода 43 триггера 16 на вход 41 генератора 1. Кроме того, с выхода переключателя 26 единичный потенциал подается на вход триггера 20, разрешая ему работать в режи.ме переключения, а также на вход элемента И 13, разрешая прохождение через него сигналов переключения с выхода триггера 12. Перед началом работы происходит начальная установка нажатием кнопки «СБРОС. Пуск устройства осуществляется при нажатии кнонки «ПУСК в формирователе 17, который устанавливает триггер 16 в нулевое положение и снимает запрет с генератора 1. При этом генератор 1 формирует на выходе 46 первый тактовый импульс, который поступает на синхровход триггера 12 и переключает его в единичное состояние. При этом на выходе элемента И 13 появляется единичный потенциал, который поступает на вход элемента И 2, вход 31 коммутататора 9 и переключает его в положение, пропускающее код адреса с выходов счетчика 4 на выходы 32 устройства, По нервому импульсу обращения из блока 27 считывается информация, записанная в нулевом адресе, аналогично описанному выше и записывается в регистр 24 сигналом с выхода элемента 19 задержки. Далее слова в регистр 24 записываться не будет до окончания перебора всех значений счетчика 3. Затем генератор 1 фор.мирует второй тактовый импульс, который переключает триггер 12 в нулевое положение, в результате коммутатор 9 переключается на трансляцию кода адреса с выходов 29 счетчика 3. Одновременно разрешается прохождение второго тактового импульса с выхода 45 на вход счетчика 3 при переключении его в состояние «1. Двоич чиото с кодом 00...01 (первый адрес) поступает через коммутатор 9 на выходы 32, и по импульсу обращения из блока 27 памяти считывается слово, которое поступает на входы регистра 24 и блока 23 сравнения, на выходе которого будет единичный сигнал неравенства, так как сравниваются слова, считанные по нулевому и первому адресам, Но сигнал неравенства не проходит через элементы И 15, так как он закрыт нулевым потенциалом с выхода элемента И 13. Второй тактовый импульс проходит через элемент 19 задержки на счетный вход триггера 16 и записывает в него «О, что соответствует имитированному положительному результату сравнения. С выхода триг gpa 16 единичный потенциал проходит на вход 41 генератора 1, не запрещая его работу. Таким образом, второй такт работы проходит без сравнения информации в блоке 23 (холостой такт) и нужен лишь для смены числа в блоке 27.

В третьем такте коммутатор 9 переключается для пропуска нулевого кода адреса с выходов 30 счетчика 4. По импульсу обращения из блока 27 считывается информация нулевого адреса, которая поступает на входы блока 23, на другие входы которого поступает слово с выходов регистра 24. Если слово считано правильно, то на выходе блока 23 будет нулевой сигнал равенства, который проходит на вход триггера 16. Затем результат сравнения записывается в триггер 16, с выхода которого единичный потенциал разрешает прод олжить работу генератора 1. Если же выборка слова нулевого адреса после выборки слова первого адреса произошла неустойчиво, то в блоке 23 зафиксируется неравнозначность. Сигнал неравенства запретит дальнейшую работу генератора 1. В этом случае следует изменить величину времени выборки в злементе 19 задержки и повторить пуск. Если

в этом случае останова нет, то это CESHдетельствует о неустойчивости (по времени) выборки слов из блока 27. В случае равенства устройство переходит к четвертому такту, в котором проверяется устойчивость вывода информации нулевого адреса после выборки информации второго адреса.

Таким образом, адреса из блока памяти 27 выбираются в первом цикле контроля в порядке, приведенном в таблице.

После окончания перебора всех значений счетчиком 3 импульс переполнения перек пючает счетчик 4 в состояние первого адреса, затем процесс контроля повторяется. Аналогично осуществляется проверка устойчивости выборки чисел из блока памяти для второго, третьего и т. д. адресов до самого старшего.

Технико-экономическое преимущество предлагаемого устройства заютючается в более высокой достоверности контроля блоков постоянной памяти по сравнению с прототипом.

Фиг.г

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля постоянных блоков памяти | 1978 |

|

SU736179A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля блоков постоянной памяти | 1980 |

|

SU868843A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-07-23—Публикация

1983-04-15—Подача