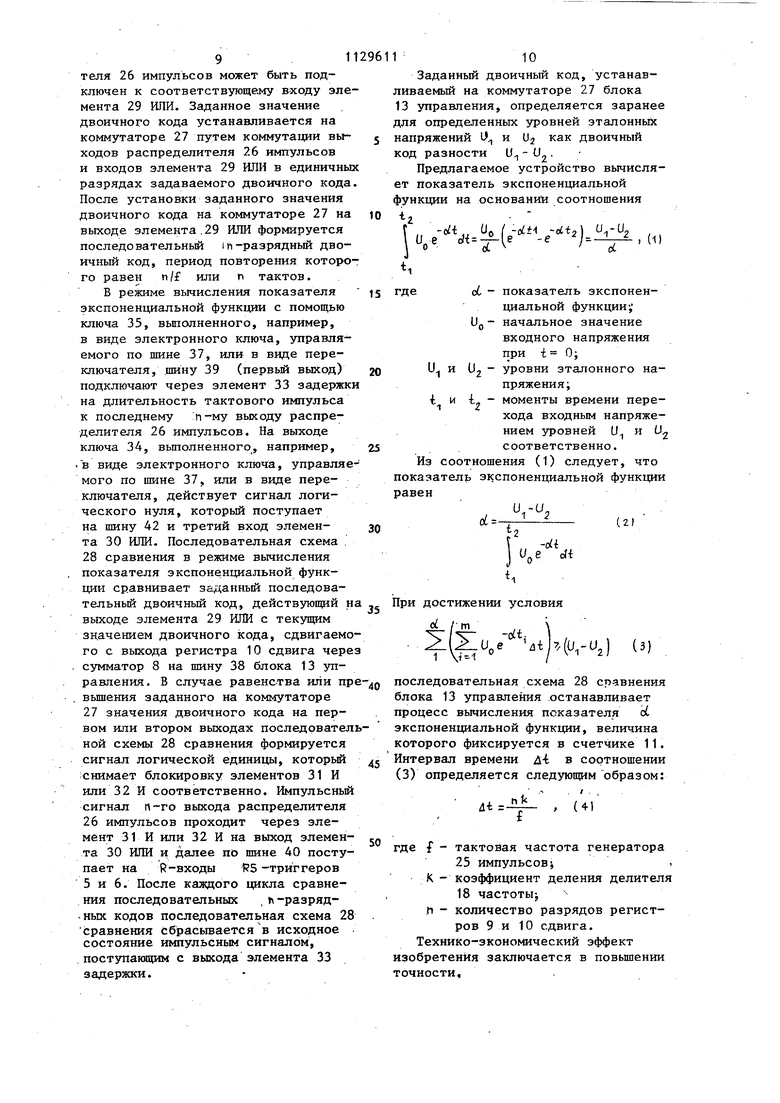

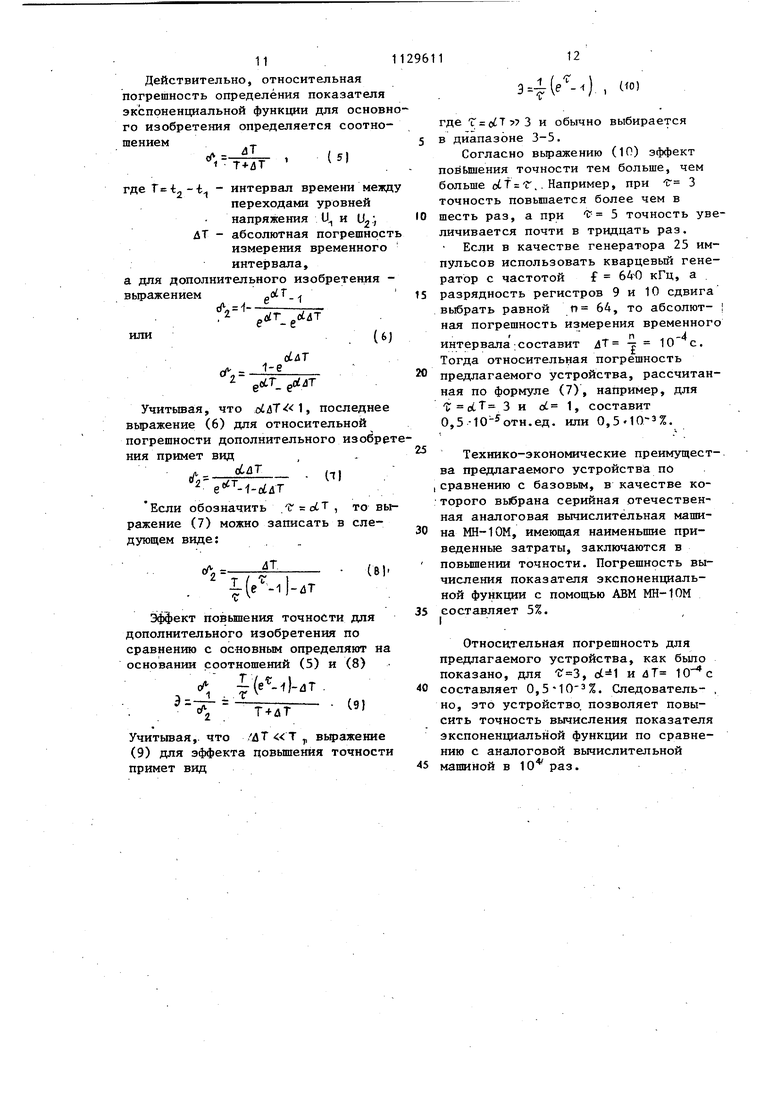

. Изобретение относится к вычислительной технике и может быть исполь зовано в различных областях техники и промьшшенности при исследовании процессов различной физической природы, которые описываются экспоненциальной функцией. По основному авт.св. № 1043677 известно устройство, содержащее первый и второй пороговые элементы, первьй RS-триггер, пpичe f первые входы первого и второго пороговых элементов соединены с информационным входом устройства, второй вход первого порогового элемента соединен с входом первого эталонного напряжения устройства, вход второго эталонного напряжения которого соединен с вторым входом второго порогового элемента,первый и второй генераторы одиночных импульсов, второй RS-триггер, три элемента И, счетчик, блок индикации, два сумматора, два регистра сдвига и блок управления, содержащий генератор импульсов, распределитель импульсов, элемент задержки. два ключа, коммутатор, два элемента ИЛИ, последовательную схему сравнения и два элемента И, выход генератора импульсов соединен с входом распределителя импульсов, выходы с первого по п-й которого, где п -, разрядное гь регистров сдви га, соединены с информационными вх дами коммутатора,управляющий вход которого соединен с входом кода ос нова блока, выходы коммутатора через первый элемент ИЛИ соединены с nepBbttd информационным входом после довательной схемы сравнения, вход сброса и тактовый вход которой сое динены соответственно с выходом эл мента задержки и выходом генератор импульсов, п-й выход распределите ля импульсов соединен с первыми вх дами первого и второго элементов И вторые входы которых соединены с выходами соответственно равенства превьшения эталонного кода последовательной схемы сравнения, выход первого и второго элементов И соеди нены с первым и вторьм входами втор го элемента ИЛИ, третий вход котор го соединен с выходом первого ключ информационный вход которого соеди нен с выходом генератора импульсов п-й выход распределителя импульсов через элемент задержки соединен с 112 информационным входом второго ключа, управляющие входы ключей соединены с входом задания режима блока управления, причем выход второго ключа блока управления соединен с тактовыми входами первого и второго генераторов одиночных импульсов, входы запуска которых соединены с выходами соответственно первого и второго пороговых элементов, выходы генераторов одиночных импульсов соединены с 5-входами соответствующих Р5-триггеров, R-входы которых соединены с выходом второго элемента ИЛИ блока управления, выход первого разряда распределителя импульсов которого соединен с первыми входами первого и второго элементов И, вторые входы которых соединены соответственно с инверсным и прямым выходами второго R5-триггера, инверсный и прямой выходы первого RS-триггера соединены соответственно с управляющими входами регистров сдвига и третьим входом первого элемента И, выход которого, соединен с первым входом первого сумматора, выход которого соединен с информационным входом первого регистра сдвига и первым входом третьего элемента И, второй вход и выход которого соединены соответственно с прямым выходом второго R5 -триггера и первым входом второго сумматора, выход которого соединен с информационным входом второго регистра сдвига и вторым информационным входом последовательной схемы сравнения блока управления, вьасоды первого ключа и генератора импульсов которого соединены соответственно с установочным входом счетчика и входами синхронизации первого и второго регистров сдвига, выходы и установочные входы которых соединены соответственно с вторыми входами соответствующих сумматоров и входом логического нуля устройства, выход второго элемента И соединен со счетным входом счетчика, выход которого соединен с входом блока .индикации 1 3. Недостатком этого устройства является ограниченная точность вычисления показателя экспоненциальной функции. Цель изобретения - повышение точности. Указанная цель достигается тем, что в устройство для вычисления по3казателя экспоненциальной функции дополнительно введены преобразователь аналог - длительность импульса, делитель частоты, элемент ИЛИ, четвертый элемент И и элемент задержки, причем информационный вход устройства соединен с информационным входом преобразователя аналог длительность импульса, выход которого подключен к четвертому входупервого элемента И, прямой выход первого R5 -триггера соединен через элемент задержки с входом четвертого элемента И, выхо которого подключен к информационно входу делителя частоты, вькод кото рого соединен с первым входом элемента ИЛИ, выход которого подключе к входу запуска преобразователя аналог - длительность импульса,инверсный выход второго RS -триггер соединен с вторьм входом четвертог элемента И, третий вход которого подключен к выходу второго ключа блока управления, установочный вхо делителя частоты соединен с выходом первого ключа блока управления выход первого генератора одиночных импульсов подключен к второму вход элемента ИЛИ. На фиг.1 изображена структурная схема предлагаемого устройства; на фиг.2 - структурная схема блока управления. Устройство (фиг.1) содержит пер вый и второй пороговые элементы 1 и 2, первый и второй генераторы 3 и 4 одиночньпс-импульсов, первый и второй R5-триггеры 5 и 6, первьй и второй сумматоры 7 и 8, перв и второй регистры 9 и 10 сдвига, счетчик 11, блок 12 индикации, блок 13 управления, первый,второй третий элементы 14, 15 и 16 И, пре образователь 17 аналог - длительность импульса, делитель 18 частот элемент 19 ИЛИ, четвертый элемент 20 И, элемент 21 задержки, ин формационный вход 22 устройства, входы 23 и 24 первого и второго эт лонного напряжения устройства соот ветственно. Блок 13 управления (фиг.2) содержит генератор 25 импульсов, рас пределитель 26 импульс:ов, коммутатор 27, по.следовательную схему 28 сравнения, элементы 29 и 30 ИЛИ, элементы 31 и 32 И, элемент 33 14. задержки, первый и второй ключи 34 и 35, вход 36 кода останова блока, вход 37 задания режима блока управления, информационный вход 38 блока управления,первую, вторую, третью, четвертую и пятую выходные шины 39, 40, 41, 42 и 43 соответственно. Устройство работаетследующим образом. В исходном состоянии на первом выходе блока 13 управления сигналы отсутствуют, а на втором и четвертом выходах вьтрабатьгоаются сигналы, которые устанавливают RS -триггеры 5 и 6, счетчик 11 и делитель 18 частоты в нулевое состояние. Единичный сигнал инверсного выхода .fes-триггера 5 поступает на вход управления регистров 9 и 10 сдвига и обеспечивает установку их в нулевое состояние, так как их установочные входы подключены к шине логического нуля устройства. В режиме вычисления показателя экспоненциальной функции шины 23 и 24 эталонных напряжений подключают к источникам эталонных напряжений, задаюш 1х два уровня эталонного напряжения U и Uj , а на информационный вход 22 устройства подается аналоговый сигнал, изменянщийся по экспоненциальному закону (ie, где Ug- начальное значение входного напряжения;; оС - показатель экспоненциальной функции t - время. В исходном состоянии на выходах пороговых элементов 1 и 2 действуют сигналы логического нуля. Как только входное напряжение, действующее на информационной шине 22, достигает первого уровня эталонного напряжения и,срабатывает пороговый элемент 1, на выходе которого формируется сигнал логической единицы. Выходной сигнал порогового элемента 1 запускает генератор 3 одиночных импульсов, на тактовый вход которого с первого выхода блока 13 управления поступает последовательность импульсов. Выходной импульс генератора 3 одиночных импульсов устанавливает RS-триггер 5 в единичное состояние и через элемент 19 ИЛИ запускает преобразователь 17 аналог - длительность импульса. На прямом выходе Rfe-триггера 5 формируется сигнал логической единицы.

снимающий блокировку элементов 14 И и 20 И, Последовательность импульсо формируемая блоком 13 управления на его третьем выходе, поступает через элемент 14 И на первый вход сумматора 7, так как на выходе преоразователя 17 аналог - длительность импульса формируется импульс, длительность которого пропорцио 5альна аналоговому Сигналу, действующему на информационном входе 22 устройства.

На первый вход сумматора 7 поступает количество импульсов третьего выхода блока 13 управления, пропорциональное длительности выходного и fflyльca преобразователя 17 аналог - длительность импульса. Сумматор 7 за время п тактов, где h- количество разрядов регист ра 9 сдвига, по каждому импульсу на его первом входе, увеличивает на единицу младшего разряда двоичный код, сдвигаемый под действием синхронизирующих импульсо в пятого выхода .блока 13 управления с выхода регистра 9 сдвига. Последовательный двоичный код с выхода сумматора 7 за время п тактов записывается в регистр 9 сдвига под действием синкронизрфующих импульсов пятого выхода блока 13 управления, В результате к моменту окончания действия импульса на выходе преобразователя 17 аналог - длительность импульса в регистре 9 сдвига формируется П-разрядный двоичный код, значение которого пропорционально текущему значению напряжения,, дей, ствующему на информационном входе 22 устройства.

Сигнал логической единицы прямого выхода PS-триггера 5 через элемент 21 задержки на длительность тактового импульса.снимает блокировку элемента 20. И, через который на информационньй вход делителя 18 частоты поступает последовательность импульсов первого выхода блока 13 управления. Коэффициент деления делителя 18 частоты выбирается таким образом, чтобы период следования выходных импульсов делителя 18 частоты бьш больше длительности выходного импульса преобразователя 17 аналог - длительность импульса для максимального уровня напряжения на информационном входе 22 устройства. Поэтому импульс на вькоде делителя 18 частоты сформируетсяпосл окончания действия импульса на выходе преобразователя 17 аналог длительность импульса. Выходной импульс делителя 18 частоты через элемент 19 ИЛИ вновь запускает преобразователь 17 аналог - длительность импульса, который вновь формирует импульсный сигнал, длительност которого пропорциональна текущему значению напряжения на информационном входе 22 устройства. На первьш вход сум чатора 7 через элемент 14 И вновь поступает серия импульсов третьего выхода блока13 управления, количество импульсов в которой пропорционально длительности выходного импульса преобразователя 17 аналог - длительность импульса. Сумматор 7 к двоичному коду предыдущего значения экспоненциальной функции, сдвигаемому с выхода регистра 9 сдвига под действием синхронизирующих импульсов пятого выхода блока 13 управления, прибавляет количество импульсов. пропорциональное текущему значению экспоненциальной функции а результат суммирования в виде п-разрядног ДВОИЧНОГО кода записывается, начиная с младшего разряда, в регистр 9 сдвига под действием синхронизирующих импульсов пятого выхода блока 13 управления.

В дальнейшем устройство работает аналогичным образом, а в регистре 9 сдвига накапливается двоичный код, значение которого пропорционально интегралу от аналогового сигнала экспоненциальной функции, действующей на информационном входе 22 устройства. Так продолжается до тех пор, пока не сработает пороговый элемент 2. Последний срабатывает при достижении входного напряжения, на шине ,22 второго уровня эталонного напряжения U. В этом случае из выходе порогового элемента 2 формируется сигнал логической единицы, который запускает генератор 4 одиночных импульсов, на тактовом входе которого действует последовательность импульсов первого выхода блока 13 управления. Выходной сигнал генератора 4 .одиночных импульсов устанавливает R5-триггер 6 в единичное состояние, при Котором сиг11нал инверсного выхода Я -триггера 6 блокирует элементы 14 И и 20 И, а сигнал его прямого выхода снимает блокировку элементов 15 и 16 И. К моменту установки RS -тригге ра 6 в единичное состояние в регист ре 9 сдвига накапливается двоичньй код, значение которого пропорционал но интегралу от аналогового сигнала экспоненциальной функции за интерва времени между событиями перехода входного аналогового сигнала экспоненциальной функции через первьй и второй уровни эталонного напряжения Так как элемент 14 И блокируется Я5-триггером 6 после установки его единичное состояние, то двоичньй код регистра 9 сдвига циркулирует без изменения с выхода на его информационньй вход через сумматор 7, а также поступает через элемент 15 последовательно во времени, начиная с младшего разряда, на первьй .вход сумматора ,8, на второй вход которог под действием синхронизирующих импульсов пятого выхода блока 13- управления сдвигается начальньй нулевой двоичный код регистра 10 сдвига За каждые и тактов работы устройст на, где п-количество разрядов регистра 10 сдвига, выполняется один цикл суммирования двоичных кодов регистра 9 и 10 сдвига. Поскольку выход сумматора 8 соединен с информ ционным входом регистра 10 сдвига, то в регистре 10 сдвига накапливается двоичньй код, равньй произведе нию количества циклов суммирования на величину двоичного кода регистре 9 сдвига. В это время десятичньй счетчик 11 вьшолняет подсчет количества циклов суммирования сумматором 8, так как через каждые г тактов на его информационном входе действует импульс третьего выхода блока 13 управления, поступающий через элемент 16 И. Так продолжается до тех пор, пока двоичньй код регистра 10 сдвига не достигнет заданного блоком 13 управления двоичного кода. Двоичньй код регистра 10 сдвигается под действием синхронизирующих импульсов пятого выхода блока 13 управления через сумматор 8 на вход блока 13 управления, где сравнивается с заданным значе1шем. 1 :8 Если двоичньй код в регистре 10 сдвига достиг или превысил заданное значение, то блок 13 управления вырабатьшает на втором выходе сигнал, которьй сбрасывает RS -триггеры 5 и 6 в нулевое состояние, при котором элементы 14, 15, 16 и 20 И блокируются и вычисление показателя экспоненциальной функции заканчивается . В счетчике 11 фиксируется значение показателя экспоненциальной функции, которое индицируется блоком 12 индикации. Блок 13 управления (фиг.2) работает следующим образом. В исходном режиме с помощью ключа 35 шину 39 (первьй выход) подключают к шине логического нуля, а ключом 34 подключают выход генератора 25 импульсов к шине 42 (четвертый выход) и к третьему входу элементов 30 ИЛИ, через которьй выходные сигналы генератора 25 импульсов поступают на шину 40 (второй выход). Генератор 25 импульсов формирует последовательность тактовых сигналов частоты f, которая поступает на шину 43 (пятьй выход) и на вход i-канального распределителя 26 импульсов. На h выходах распределителя 26 импульсов формируются п последова тельностейсигналов частоты /п,, сдвинутых друг относительно друга на время 1/. Каждьй вькодной сигнал распределителя 26 импульсов совпадает с моментом считывания соответствующего разряда двоичного кода с выходов регистров 9 и 10 сдвига. Последовательность импульсов первого выхода распределителя 26 импульсов, поступающая на шину 41 (третий выход) совпадает по , времени со сдвигом первого (младшего) разряда двоичных кодов в регистрах 9 и 10 сдвига. Последовательность импульсов последнего п-го выхода распределителя 26 импульсов, поступающая на первые входы элементов 31 и 32 И, совпадает по времени со сдвигом последнего . п то разряда двоичных кодов в регистрах 9 и 10 сдвига. С помощью коммутатора 27, выполненного, например, в виде электронного коммутатора, управляемого по шине 36, или в виде клавишного переключателя, каждый выход распредели91теля 26 импульсов может быть подключен к соответствующему входу эле мента 29 ИЛИ, Заданное значение двоичного кода устанавливается на коммутаторе 27 путем коммутации выходов распределителя 26 импульсов и входов элемента 29 ИЛИ в единичны разрядах задаваемого двоичного кода После установки заданного значения двоичного кода на коммутаторе 27 на выходе элемента,29 ИЛИ формируется последовательньй ih-разрядный двоичный код, период повторения которо го равен п/ или п тактов. В режиме вычисления показателя экспоненциальной функции с помощью ключа 35, выполненного, например, в виде электронного ключа, управляемого по шине 37, или в виде переключателя, .шину 39 (первьй выход) подключают через элемент 33 задержк на длительность тактового импульса к последнему п-му выходу распределителя 26 импульсов. На выходе ключа 34, выполненного, например, «в виде электронного ключа, управляе мого по шине 37, или в виде переключателя, действует сигнал логического нуля, который поступает на шину 42 и третий вход элемента 30 ИЛИ. Последовательная схема . 28 сравнения в режиме вычисления показателя экспоненциальной функции сравнивает заданный последовательньй двоичный код, действующий н выходе элемента 29 ИЛИ с текущим значением двоичного кода, сдвигаемо го с выхода регистра 10 сдвига чере сумматор 8 на шину 38 блока 13 управления, В случае равенства или up вьш1ения заданного на коммутаторе 27 значения двоичного кода на первом или втором выходах последовател ной схемы 28 сравнения формируется сигнал логической единицы, которьй снимает блокировку элементов 31 И или 32 И соответственно. Импульсньй сигнал п-го выхода распределителя 26 импульсов проходит через элемент 31 И или 32 И на выход элемента 30 ИЛИ и далее по шине 40 поступает на R-входы R5 -триггеров 5 и 6. После каждого цикла сравнения яоследовательных , л-разрядных кодов последовательная схема 28 сравнения сбрасывается в исходное состояние импульсным сигналом, поступаняцим с выхода элемента 33 задержки. 1 10 Заданный двоичный код, устанавливаемый на коммутаторе 27 блока 13 управления, определяется заранее для определенных уровней эталонных напряжений L и (Jj как двоичный код разности U-. Предлагаемое устройство вычисляет показатель экспоненциальной функции на оснований соотношения () где ct - показатель экспоненциальной функции-; UQ- начальное значение входного напряжения при 0; и и (2 уровни эталонного напряжения;t и t - моменты времени перехода входным напряжением уровней и и и соответственно. Из соотношения (1) следует, что показатель экспоненциальной функции равен . v ,„ 1 При достижении условия , (3) последовательная схема 28 сравнения блока 13 управления .останавливает процесс вычисления показателя об экспоненциальной функции, величина которого фиксируется в счетчике 11. Интервал времени A-t в соотношении (3) определяется следующим образом: где f - тактовая частота генератора 25 импульсовJ К - коэффициент деления делителя 18 частоты П - количество разрядов регистров 9 и 10 сдвига. Технико-экономический эффект изобретения заключается в повьш1ении точности. 11 Действительно, относительная погрешность определения показател экспоненциальной функции для осно го изобретения определяется соотн шением - интервал времени ме переходами уровней напряжения U и Uj. ДТ - абсолютная погрешно измерения временног интервала, а для дополнительного изобретения выражением „oLT Н - ,dr 4Т (f 2 g06r Учитьшая, что , последн выражение (6) для относительной погрешности дополнительного изобр ния примет вид ,Г e -1-d&T ЕСЛИ обозначить /f о6Т , то ражение (7) можно записать в сле дующем виде: е -1J-4T повьшения точности для дополнительного изобретения по сравнению с основным определяют н основании соотношений (5) и (8) ;.(л.)-.г, д-- -. . (gj Учитьгоая,. что /йТ«Т выражени (9) для эффекта цовьшгения точнос примет вид 1 Э4(е-) , Ио) где Т и обычно выбирается в диапазоне 3-5. Согласно выражению (10) эффект повышения точности тем больше, чем больше otТ г.. Например, при 3 точность повышается более чем в шесть раз, а при f 5 точность увеличивается почти в тридцать раз. Если в качестве генератора 25 импульсов использовать кварцевый генератор с частотой f 64Ю кГц, а . разрядность регистров 9 и 10 сдвига выбрать равной п 64, то абсолютная погрешность измерения временного 4Т . интервала;составит Тогда относительная погрешность предлагаемого устройства, рассчитанная по формуле (7), например, для 3 и 0 1, составит 0,5-10- отн.ед. или 0,, Технико-экономические преимущест-. ва предлагаемого устройства по сравнению с базовым, в качестве которого выбрана серийная отечественная аналоговая вычислительная машина МН-10М, имеющая наименьшие приведенные затраты, заключаются в повьш1ении точности. Погрешность вычисления показателя экспоненциальной функции с помощью АВМ МН-10М составляет 5%. I Относительная погрешность для предлагаемого устройства, как было показано, для , d- и dT 10 с составляет 0,. Следователь- , но, это устройство, позволяет повысить точность вычисления показателя экспоненциальной функции по сравнению с аналоговой вычислительной машиной в 10 раз.

hi.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1982 |

|

SU1043677A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1986 |

|

SU1335990A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1984 |

|

SU1272342A1 |

| Устройство для вычисления элементарных функций | 1984 |

|

SU1168930A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1335989A1 |

| Устройство для контроля экспоненциальных процессов | 1984 |

|

SU1282087A1 |

| Устройство для контроля экспоненциальных процессов | 1990 |

|

SU1732331A1 |

| Устройство для контроля экспоненциальных процессов | 1987 |

|

SU1500997A1 |

| Устройство для вычисления экспоненциальной функции | 1982 |

|

SU1057944A2 |

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНА ПОКАЗАТЕЛЯ ЭКСПОНЕНЦИАЛЬНОЙ ФУНКЦИИ по авт.св. № 1043677, отличающееся тем, что, с целью повышения точности, в него введены преобразователь аналог - длительность импульса, делитель частоты, элемент ИЛИ, четвертый элемент И и элемент задержки, причем информационньш вход устройства соединен с информационным входом преобразователя аналог - длительность импульса, выход которого подключен к четвертому входу первого элемента И, прямой выход первого RS-триггера соединен через элемент задержки с первым входом четвертого элемента И, выход которого подключен к информационному входу делителя частоты, выход которого соединен с первым входом элемента ИЛИ, вькод которого подключен к входу запуска преобразователя аналог - длительност импульса, инверсный выход второго RS-триггера соединен с вторым входом четвертого элемента И, третий вход которого подключен к выходу второго ключа блока управления, установочный вход делителя частоты соединен с выходом первого ключа блока управления,выход первого генератора одиночных импульсов подключен к второму входу элемента ИЛИ.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1982 |

|

SU1043677A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-12-15—Публикация

1983-02-02—Подача