Изобретение относится к автоматике и вычислительной технике и может быть использовано при исследовании процессов различной физической при- , которые описываются экспоненциальной функцией.

Цель изобретения - расширение области применения за счет обеспечения вычисления показателя для убывающей или возрастающей экспоненциальной функции с произвольным установившимся значением.

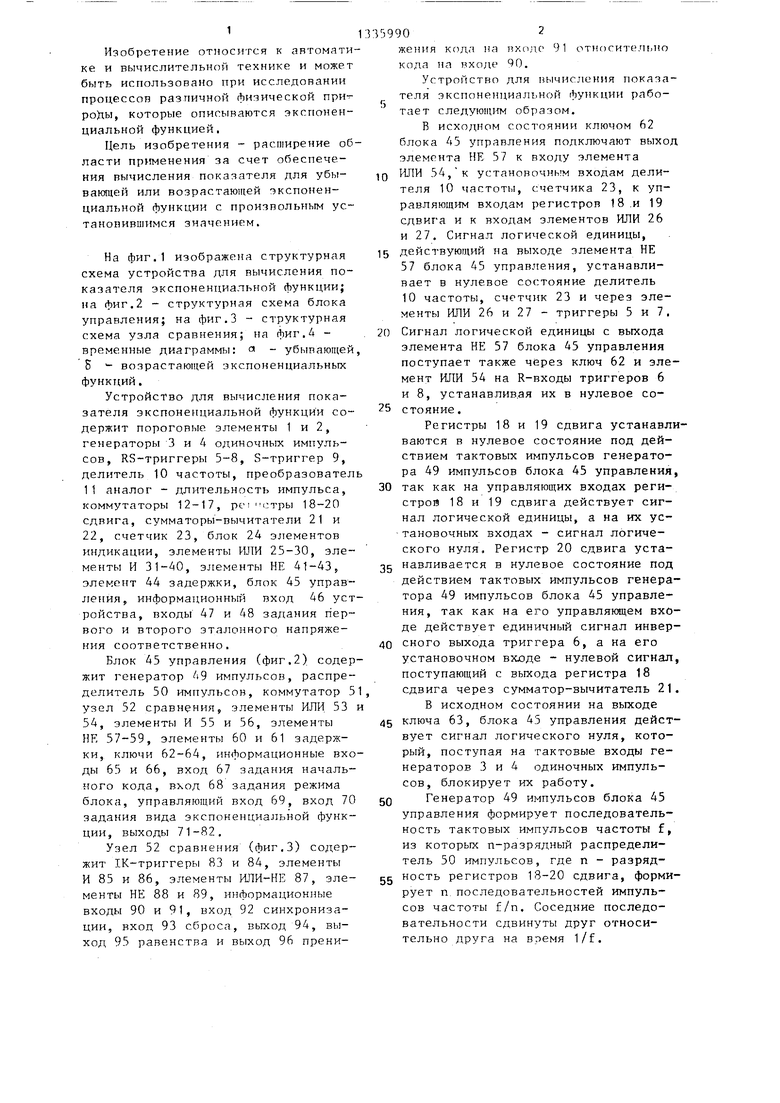

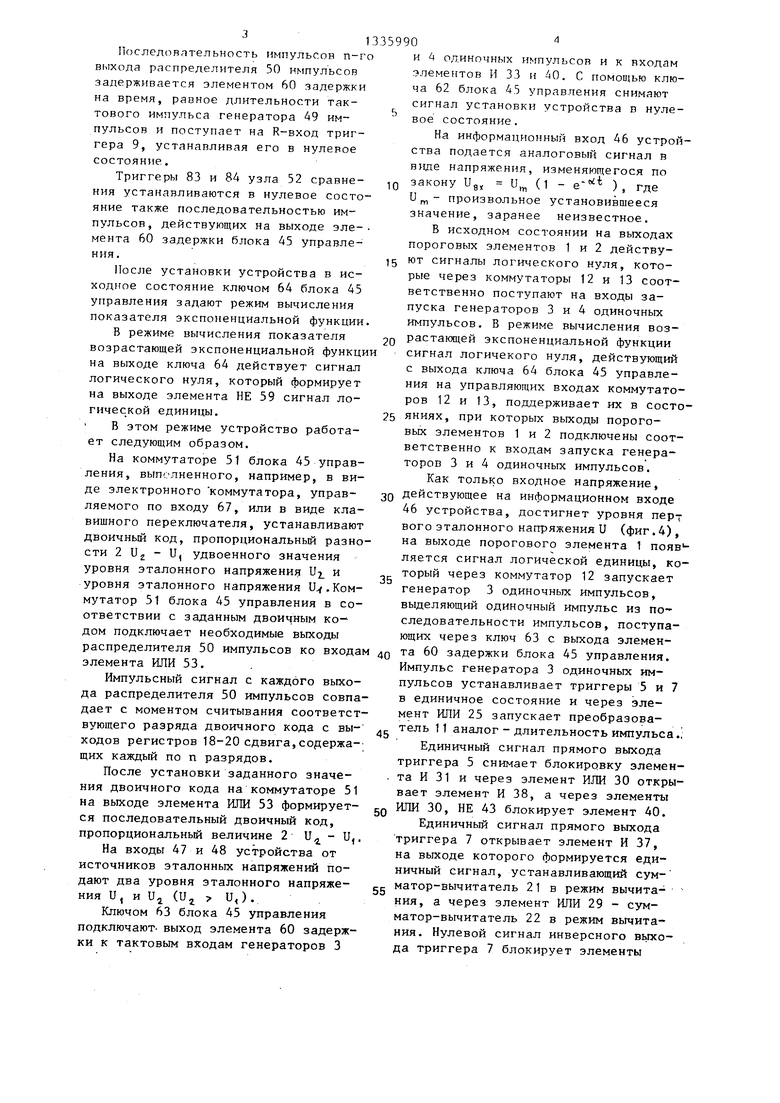

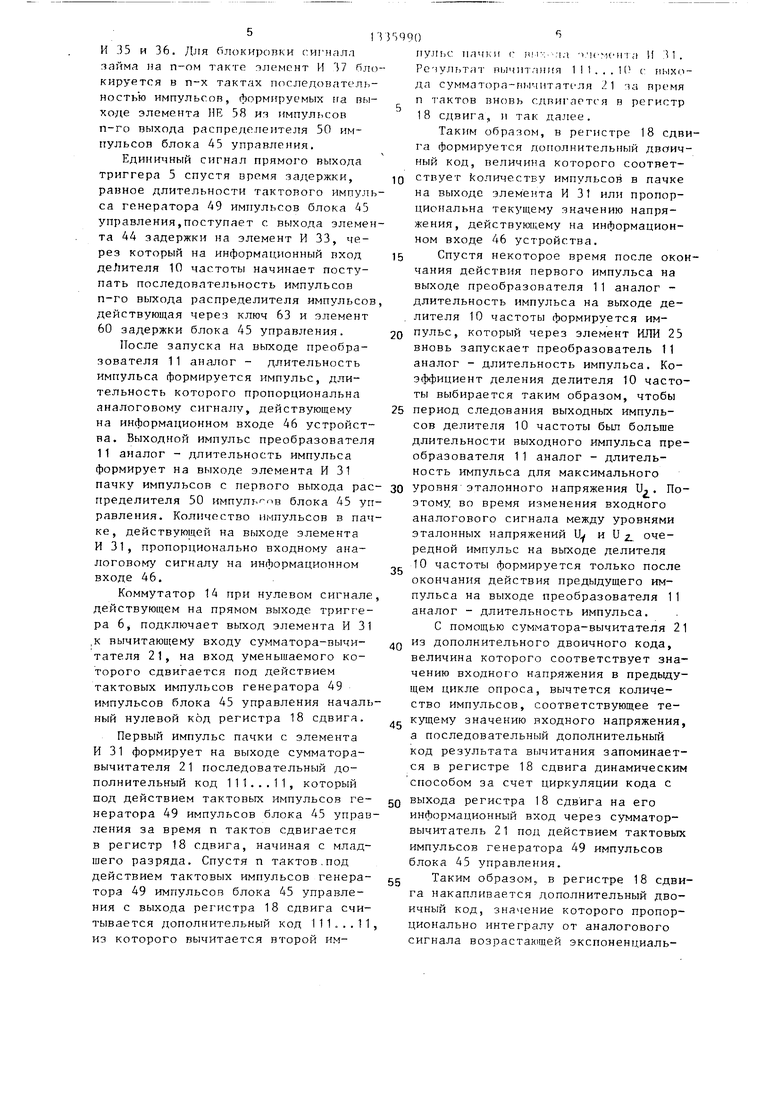

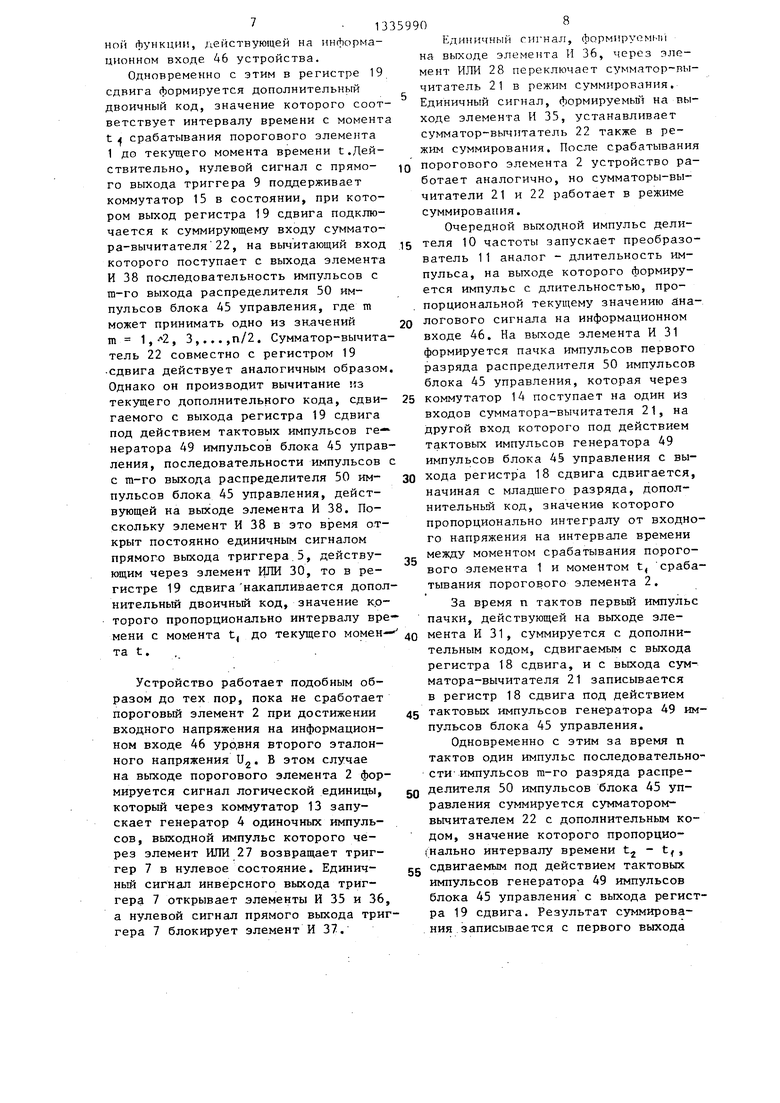

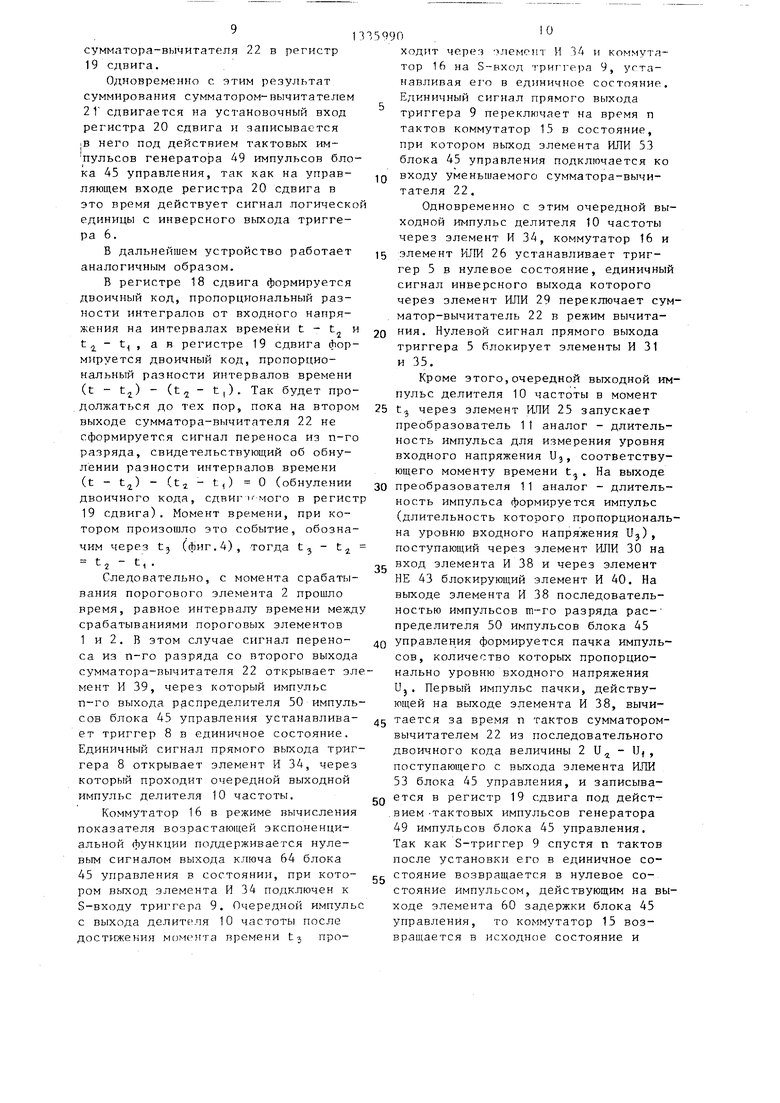

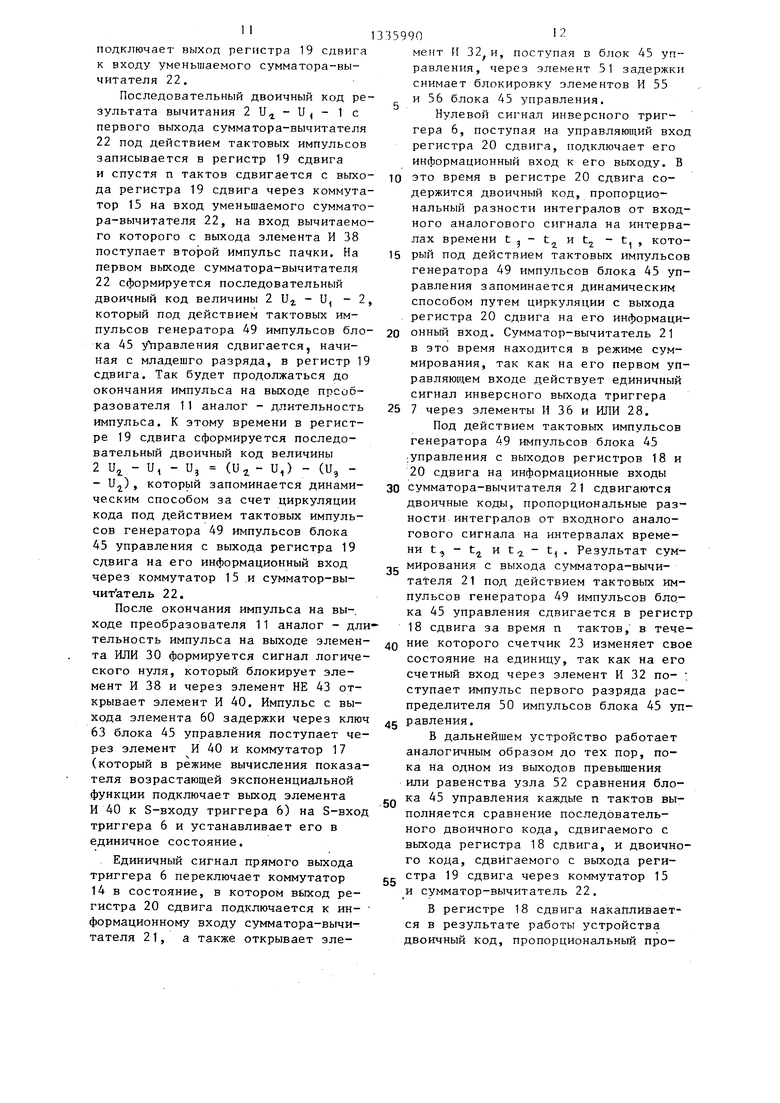

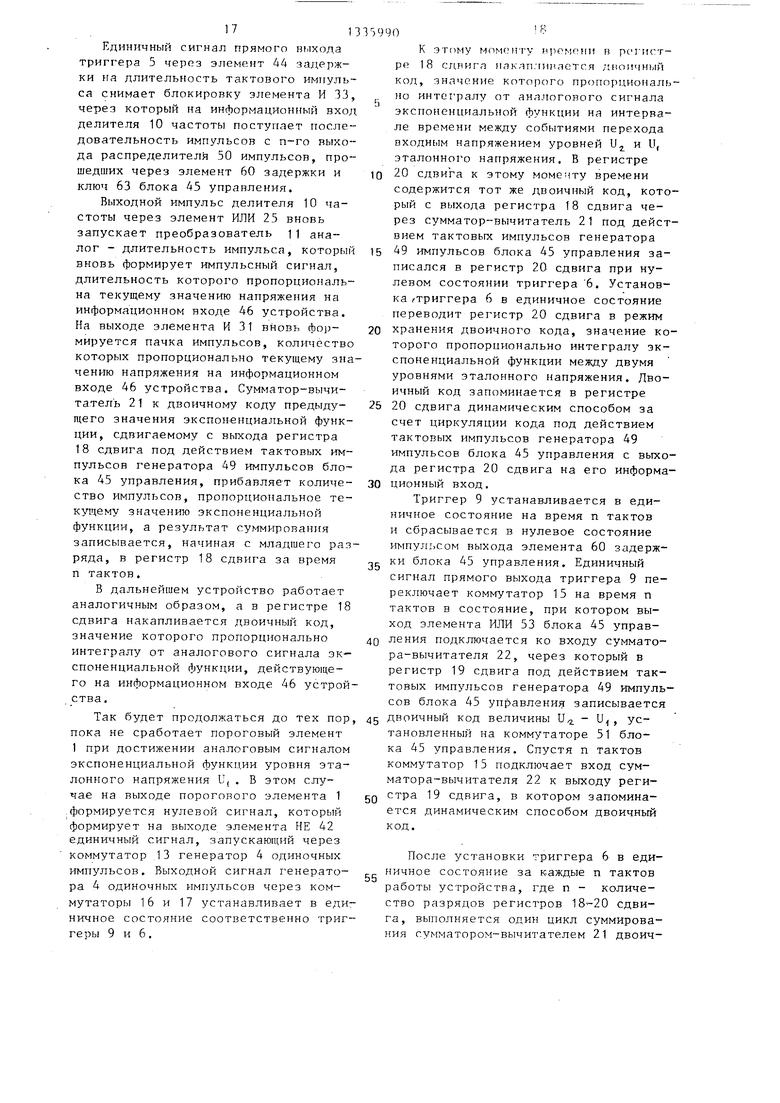

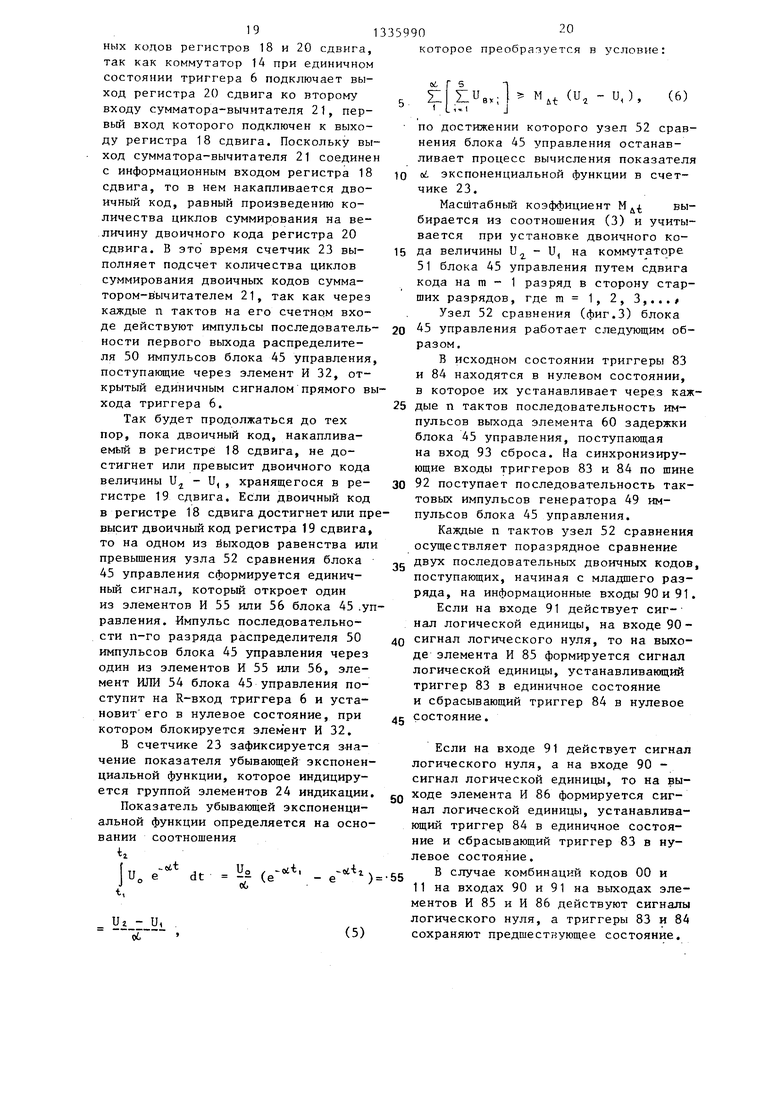

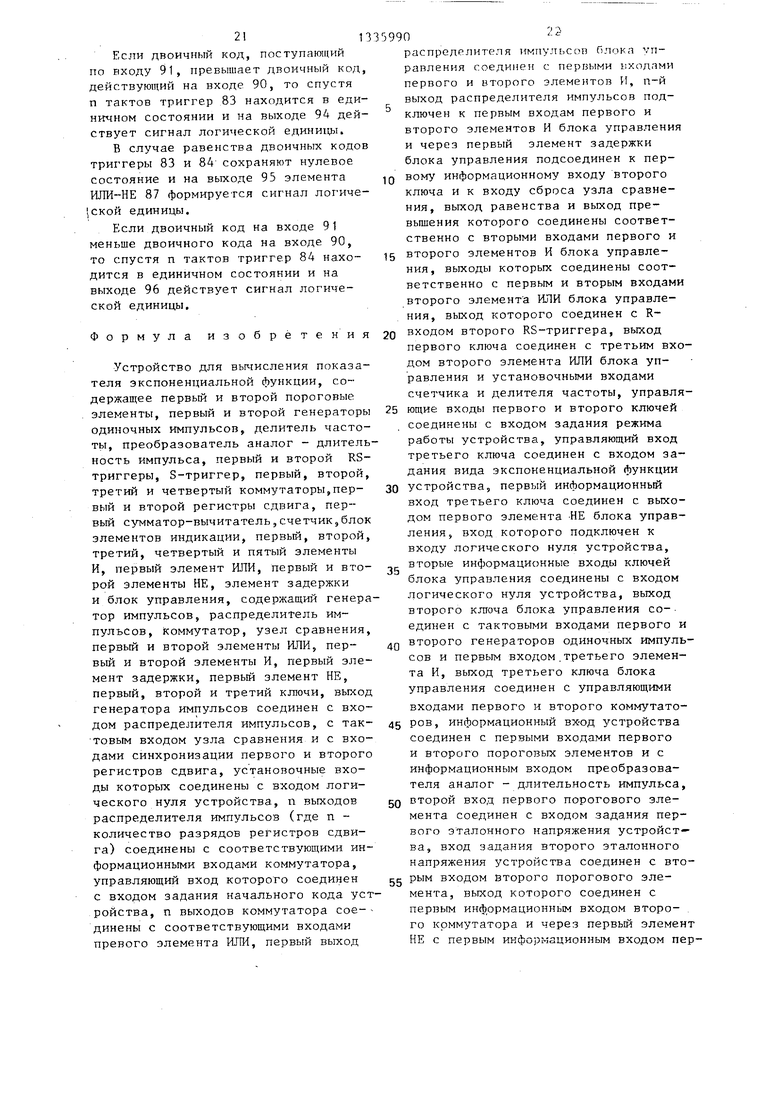

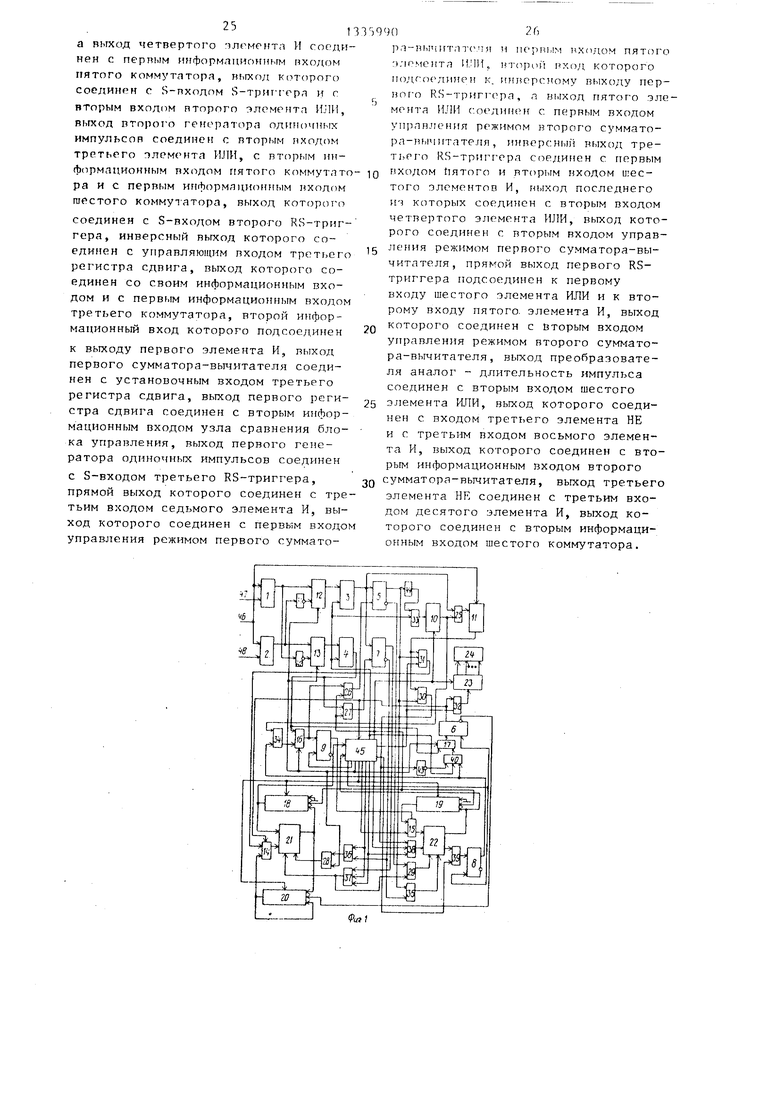

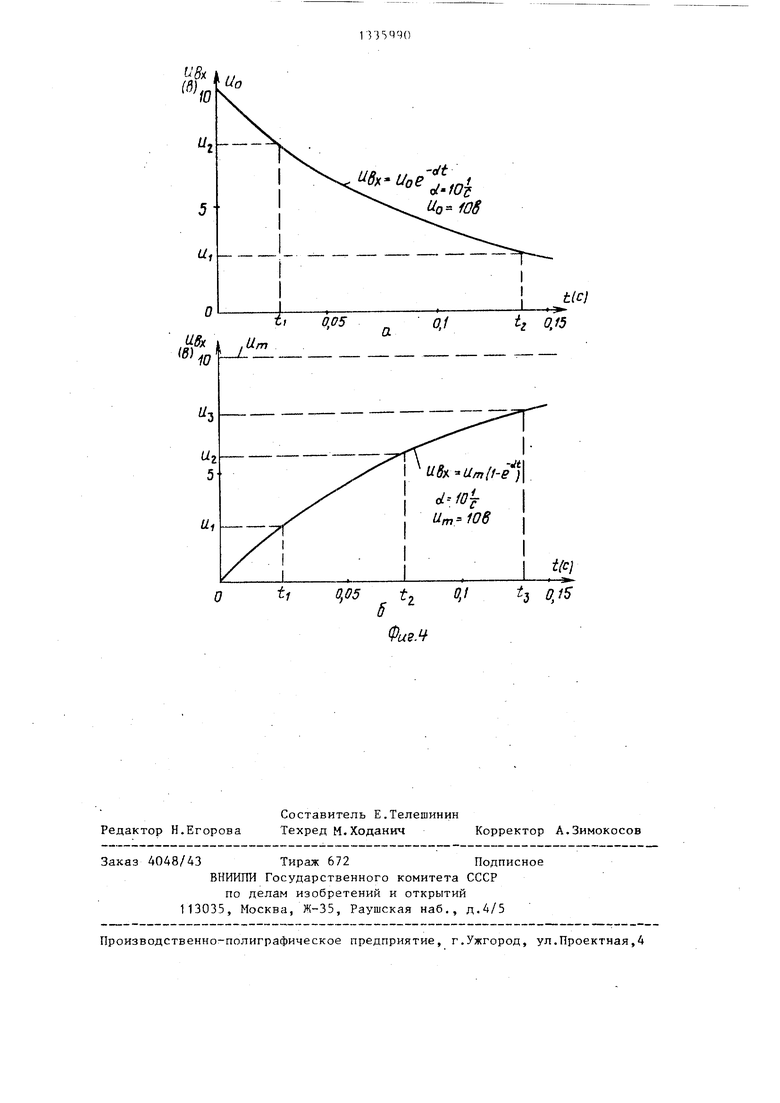

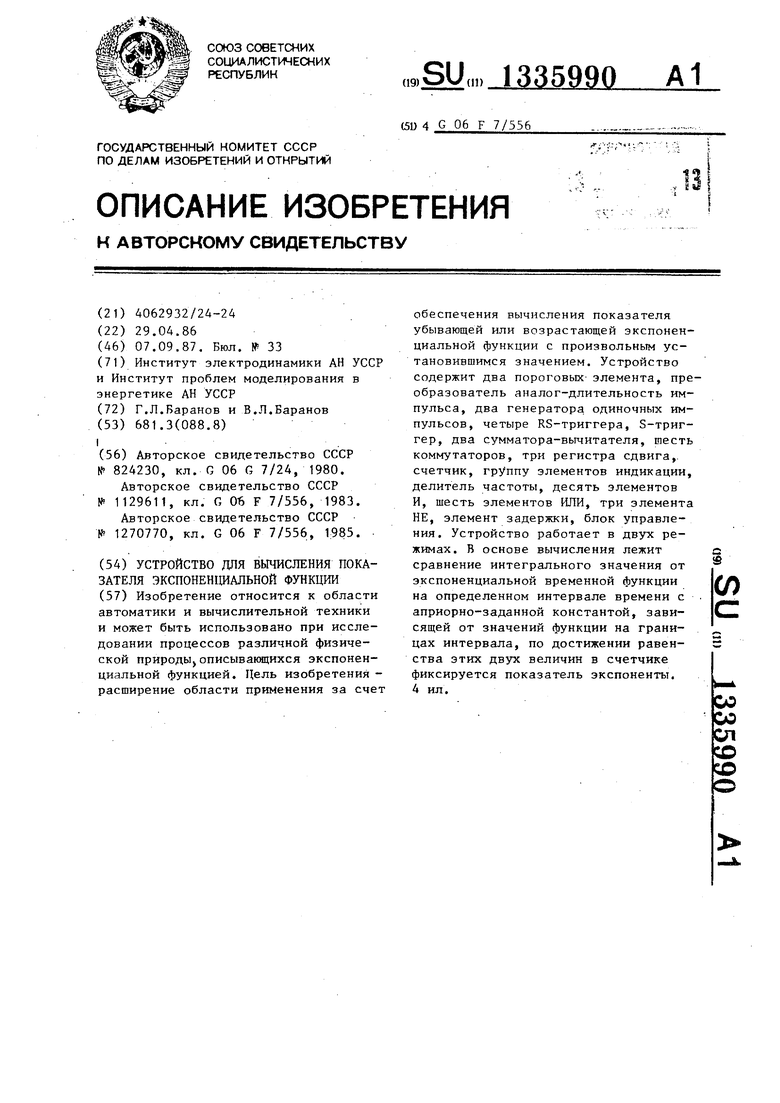

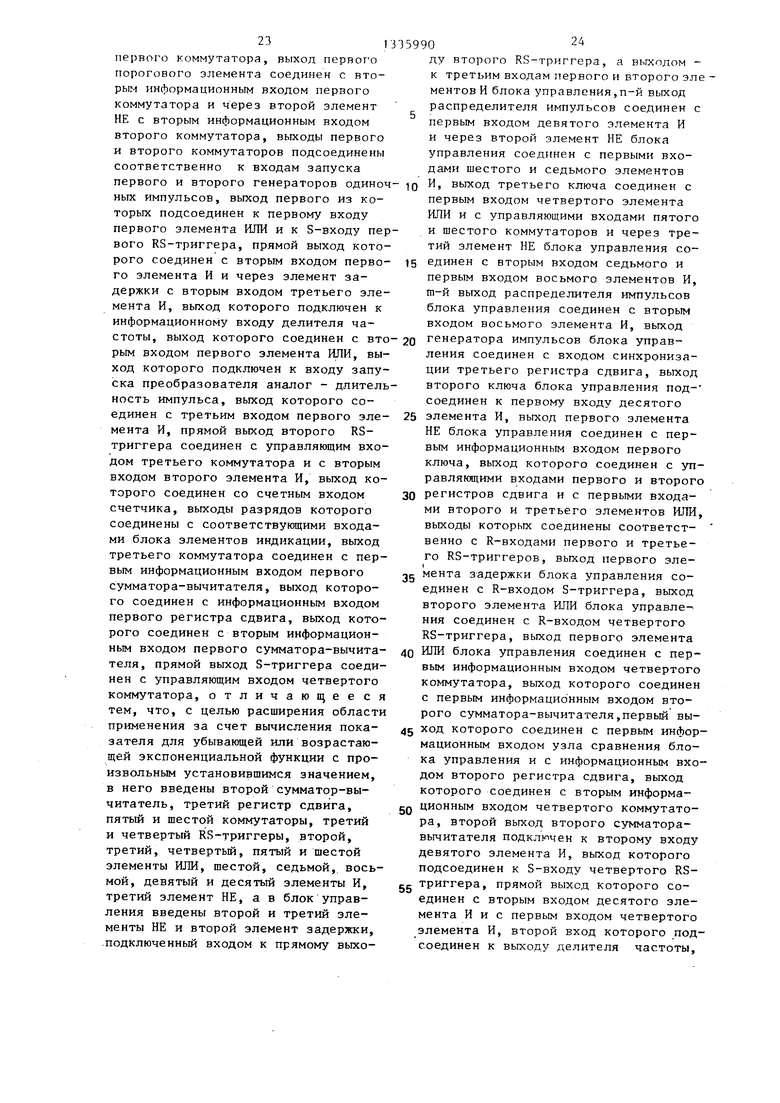

На фиг.1 изображена структурная схема устройства для вычисления показателя экспоненциальной функции; на фиг.2 - структурная схема блока управления; на фиг.3 - структурная схема узла сравнения; на фиг.А - временные диаграммы: а - убывающей 5 - возрастающей экспоненциальных функций.

Устройство для вычисления показателя экcпoнefIциaльнoй функци и содержит пороговые элементы 1 и 2, генераторы 3 и А одиночных импульсов, RS-триггеры 5-8, S-триггер 9, делитель 10 частоты, преобразовател 11 аналог - длительность импульса, коммутаторы 12-17, рс i стры 18-20 сдвига, сумматоры-вычитатели 21 и 22, счетчик 23, блок 2А элементов индикации, элементы ИЛИ 25-30, элементы И 31-40, элементы НЕ 41-43, элемент 44 задержки, блок 45 управления, информационный вход 46 устройства, входы 47 и 48 задания первого и второго эталонного напряжения соответственно.

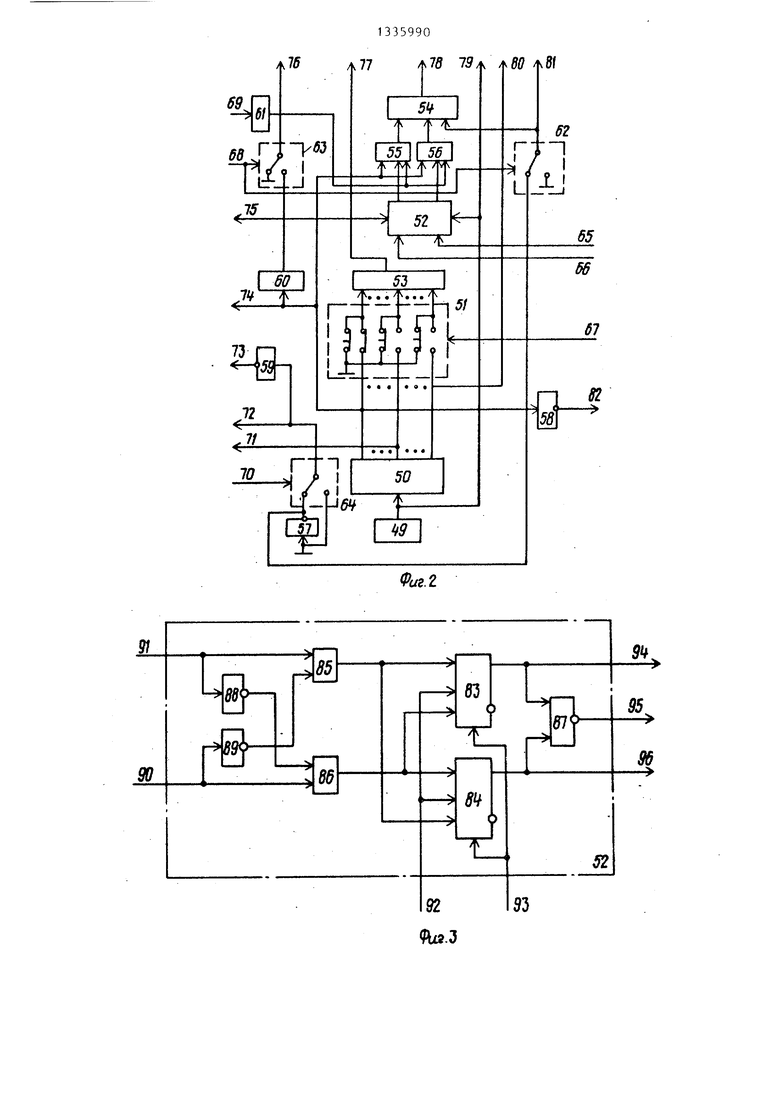

Блок 45 управления (фиг.2) содержит генератор 19 импульсов, распределитель 50 импульсов, коммутатор 5 узел 52 сравнения, элементы ИЛИ 53 54, элементы И 55 и 56, элементы НЕ 57-59, элементы 60 и 61 задержки, ключи 62-64, информационные входы 65 и 66, вход 67 задания начального кода, вход 68 задания режима блока, управляющий вход 69, вход 70 задания вида экcпoнeнциaJ:ьнoй функции, выходы 71-82.

Узел 52 сравнения (фиг.З) содержит 1К-триггеры 83 и 84, элементы И 85 и 86, элементы ИЛИ-НЕ 87, элементы НЕ 88 и 89, информационные входы 90 и 91, вход 92 синхронизации, вход 93 сброса, выход 94, выход 95 равенства и выход 96 прени

, 359902

женин кода на пходо 91 относите.П,но кода на входе 90.

Устройство для вычисления показателя экспоненциальной функции работает следуюпиад образом.

В исходном состоянии ключом 62 блока 45 управления подключают выход элемента НЕ 57 к входу элемента

1Q ИЛИ 54, к установочнь м входам делителя 10 частоты, счетчика 23, к управляющим входам регистров 18 .и 19 сдвига и к входам элементов ИЛИ 26 и 27. Сигнал логической единицы,

15 действующий на выходе элемента НЕ 57 блока 45 управления, устанавливает в нулевое состояние делитель 10 частоты, счетчик 23 и через элементы ИЛИ 26 и 27 - триггеры 5 и 7,

20 Сигнал логической единицы с выхода элемента НЕ 57 блока 45 управления поступает также через ключ 62 и элемент ИЛИ 54 на R-входы триггеров 6 и 8, устанавливая их в нулевое со25 стояние.

Регистры 18 и 19 сдвига устанавливаются в нулевое состояние под действием тактовых импульсов генератора 49 импульсов блока 45 управления,

30 так как на управляющих входах реги- строй 18 и 19 сдвига действует сигнал логической единицы, а на их ус- тановочных входах - сигнал логического нуля. Регистр 20 сдвига уста35 навливается в нулевое состояние под действием тактовых импульсов генератора 49 импульсов блока 45 управления, так как на его управляющем входе действует единичный сигнал инвер40 сного выхода триггера 6, а на его установочном вхлде - нулевой сигнал, поступающий с выхода регистра 18 сдвига через сумматор-вычитатель 21. В исходном состоянии на выходе

45 ключа 63, блока 45 управления действует сигнал логического нуля, который, поступая на тактовые входы генераторов 3 и 4 одиночных импульсов, блокирует их работу.

50 Генератор 49 импульсов блока 45 управления формирует последовательность тактовых импульсов частоты f, из которых п-разрядный распределитель 50 Импульсов, где п - разряд55 ность регистров 18-20 сдвига, формирует п.последовательностей импульсов частоты f/n. Соседние последовательности сдвинуты друг относительно друга на время 1/f.

Последовательность импульсов п-го выхода распределителя 50 импульсов задерживается элементом 60 задержки на время, длительности тактового импульса генератора 49 импульсов и поступает на R-вход триггера 9, устанавливая его в нулврое состояние.

Триггеры 83 и 84 узла 52 сравнения устанавливаются в нулевое состояние также последовательностью импульсов, действующих на выходе эле-, мента 60 задержки блока 45 управления.

После установки устройства в исходное состояние ключам 64 блока 45 управления задают режим вычисления показателя экспоненциальной функции.

В режиме вычисления показателя возрастающей экспоненциальной функци на выходе ключа 64 действует сигнал логического нуля, который формирует на выходе элемента НЕ 59 сигнал логической единицы.

В этом режиме устройство работает следующим образом.

На коммутаторе 51 блока 45 управления, выполненного, например, в виде электронного коммутатора, управляемого по входу 67, или в виде клавишного переключателя, устанавливают двоичньш код, пропорциональный разности 2

г и. удвоенного значения

Как только входное напряжение, 20 действующее на информационном входе 46 устройства, достигнет уровня пер7 вого эталонного напряжения U (фиг.4), на выходе порогового элемента 1 ляется сигнал логической единицы, который через коммутатор 12 запускает генератор 3 одиночных импульсов,

выделяющий одиночный импульс из ПО

следовательности импульсов, поступающих через ключ 63 с выхода элемен35

уровня эталонного напряжения U2. и уровня эталонного напряжения 1).Коммутатор 51 блока 45 управления в соответствии с заданным двоичным ко- дом подключает необходимые выходы распределителя 50 импульсов ко входам 40 задержки блока 45 управления, элемента ИЛИ 53. .Импульс генератора 3 одиночных имИмпульсный сигнал с каждого выхо- пульсов устанавливает триггеры 5 и 7

в единичное состояние и через элемент ИЛИ 25 запускает преобразова- тель 11 аналог - длительность импульса.

Единичный сигнал прямого выхода триггера 5 снимает блокировку элеменкаждого выхода распределителя 50 импульсов совпадает с моментом считывания соответствующего разряда двоичного кода с вы- ходов регистров 18-20 сдвига,содержа-; щих каждый по п разрядов.

После установки заданного значения двоичного кода на коммутаторе 51 на выходе элемента ИЛИ 53 формируется последовательный двоичный код.

50

та И 31 и через элемент ИЛИ 30 открывает элемент И 38, а через элементы ИЛИ 30, НЕ 43 блокирует элемент 40. Единичный сигнал прямого выхода триггера 7 открывает элемент И 37, на вькоде которого формируется единичный сигнал, устанавливающий сум- матор-вычитатель 21 в режим вычитания, а через элемент ИЛИ 29 - сум- матор-вычитатель 22 в режим вычитания. Нулевой сигнал инверсного вьпсо- да триггера 7 блокирует элементы

пропорциональный величине 2

На входы 47 и 48 устройства от источников эталонных напряжений подают два уровня эталонного напряжения и, и Uj (Uj и,).

Ключом 63 блока 45 управления подключают, выход элемента 60 задержки к тактовым входам генераторов 3

0

5

и 4 одиночных импульсов и к входам элементов И 33 и 40. С помощью ключа 62 блока 45 управления снимают сигнал установки устройства в нулевое состояние.

На информационный вход 46 устройства подается аналоговый сигнал в виде напряжения, изменяющегося по закону Ug, и (1 - ), где произвольное установившееся значение, заранее неизвестное.

В исходном состоянии на выходах пороговых элементов 1 и 2 действуют сигналы логического нуля, которые через коммутаторы 12 и 13 соответственно поступают на входы запуска генераторов 3 и 4 одиночных импульсов. В режиме вычисления возрастающей экспоненциальной функции сигнал логичекого нуля, действующий с выхода ключа 64 блока 45 управления на управляющих входах коммутаторов 12 и 13, поддерживает их в состояниях, при которых выходы пороговых элементов 1 и 2 подключены соответственно к входам запуска генераторов 3 и 4 одиночных импульсов.

Как только входное напряжение, 0 действующее на информационном входе 46 устройства, достигнет уровня пер7 вого эталонного напряжения U (фиг.4), на выходе порогового элемента 1 ляется сигнал логической единицы, который через коммутатор 12 запускает генератор 3 одиночных импульсов,

выделяющий одиночный импульс из ПО

следовательности импульсов, поступающих через ключ 63 с выхода элемен0

5

5

0 задержки блока 45 управления, Импульс генератора 3 одиночных им50

55

та И 31 и через элемент ИЛИ 30 открывает элемент И 38, а через элементы ИЛИ 30, НЕ 43 блокирует элемент 40. Единичный сигнал прямого выхода триггера 7 открывает элемент И 37, на вькоде которого формируется единичный сигнал, устанавливающий сум- матор-вычитатель 21 в режим вычитания, а через элемент ИЛИ 29 - сум- матор-вычитатель 22 в режим вычитания. Нулевой сигнал инверсного вьпсо- да триггера 7 блокирует элементы

5, -,

И 35 и 36. Для блокировки (:иг}|алл займа на п-ом такте элемент И S7 блс)- кируется в п-х тактах последовательностью импульсов, формируемых на выходе элемента НЕ 58 иr импульсов п-го тзыхода распределеителя 50 импульсов блока 45 управления.

Единичный сигнал прямого выхода триггера 5 спустя время задержки, равное длительности тактового импульса генератора 49 импульсов блока 45 управления,поступает с выхода элемента 44 задержки на элемент И 33, через который на информационный вход де/тителя 10 частоты начинает поступать последовательность импульсов п-го выхода распределителя импульсов действующая через ключ 63 и элемент 60 задержки блока 45 управления.

После запуска на выходе преобразователя 11 аналог - длительность импульса формируется импульс, длительность которого пропорциональна аналоговому сигналу, действующему на информационном входе 46 устройства. Выходной импульс преобразователя 11 аналог - длительность импульса формирует на выходе элемента И 31 пачку импульсов с первого выхода распределителя 50 импуль пв блока 45 управления. Количество импульсов в пачке, действующей на выходе элемента И 31, пропорционально входному аналоговому сигналу на информационном входе 46.

Коммутатор 14 при нулевом сигнале, действующем на прямом выходе тригг е- ра 6, подключает выход элемента И 31 ,к вычитающему входу сумматора-вычи- тателя 21, на вход уменьшаемого которого сдвигается под действием тактовых импульсов генератора 49 импульсов блока 45 управления начальный нулевой код регистра 18 сдвига.

Первый импульс пачки с элемента И 31 формирует на выходе сумматора- вычитателя 21 последовательный дополнительный код 1 1 1... 11 , который под действием тактовых импульсов генератора 49 импульсов блока 45 управления за время п тактов сдвигается в регистр 18 сдвига, начиная с младшего разряда. Спустя п тактов,под действием тактовых импульсов генератора 49 импульсов блока 45 управления с выхода регистра 18 сдвига считывается дополнительный код 111... 11 из которого вычитается второй им990

пульс плчки с , 1см(мгг а И . Ре 1у.г1ьтят лычитания 1 И ... 10 с пыхо- да сумматора-нычитателя 21 за время п тактов вновь сдвигается в регистр 18 сдвига, п так далее.

Таким образом, в регистре 18 сдвига формируется дополнительный двоичный код, величит а которого соответ1Q ствует koличecтвy импульсов в пачке на выходе элемента И 31 или пропорциональна текущему значению напряжения, действующему на информационном входе 46 устройства.

15 Спустя некоторое время после окончания действия первого импульса на выходе преобразователя 11 аналог - длительность импульса на выходе делителя 10 частоты формируется им0 пульс, который через элемент ИЛИ 25 вновь запускает преобразователь 11 аналог - длительность импульса. Коэффициент деления делителя 10 частоты выбирается таким образам, чтобы

25 период следования выходных импульсов делителя 10 частоты был больше длительности выходного импульса преобразователя 11 аналог - длительность импульса для максимального

30 уровня эталонного напряжения U, . Поэтому во время изменения входного аналогового сигнала между уровнями эталонных напряжений Uy и U 2 очередной импульс на выходе делителя 10 частоты формируется только после окончания действия предыдущего импульса на выходе преобразователя 11 аналог - длительность импульса.

С помощью сумматора-вычитателя 21

Q из дополнительного двоичного кода, величина которого соответствует значению входного напряжения в предыдущем цикле опроса, вычтется количество импульсов, соответствующее те.(- кущему значению входного напряжения, а последовательный дополнительный код результата вычитания запоминается в регистре 18 сдвига динамическим способом за счет циркуляции кода с

5Q выхода регистра 18 сдвига на его информационный вход через сумматор- вычитатель 21 под действием тактовых импульсов генератора 49 импульсов блока 45 управления.

gg Таким образом., в регистре 18 сдвига накапливается дополнительный двоичный код, значение которого пропорционально интегралу от аналогового сигнала возрастакидей экспоненциаль35

Hoii функции, действующей на информационном входе 46 устройства.

Одновременно с этим в регистре 19 сдвига формируется дополнительньгй двоичный код, значение которого соответствует интервалу времени с момента t срабатывания порогового элеме} та 1 до текущего момента времени t.Действительно, нулевой сигнал с прямого выхода триггера 9 поддерживает коммутатор 15 в состоянии, при котором выход регистра 19 сдвига подключается к суммирующему входу суммато- ра-вычитателя 22, на вычитающий вход которого поступает с выхода элемента И 38 по-следовательность импульсов с та-го выхода распределителя 50 импульсов блока 45 управления, где m может принимать одно из значений m 1,2, 3,.,.,п/2. Сумматор-вычита- тель 22 совместно с регистром 19 сдвига действует аналогичным образом. Однако он производит вычитание из текущего дополнительного кода, сдвигаемого с выхода регистра 19 сдвига под действием тактовых импульсов генератора 49 импульсов блока 45 управления, последовательности импульсов с с га-го выхода распределителя 50 импульсов блока 45 управления, действующей на выходе элемента И 38. Поскольку элемент И 38 в это время открыт постоянно единичным сигналом прямого выхода триггера.5, действующим через элемент ИЛИ 30, то в регистре 19 сдвига накапливается дополнительный двоичный код, значение к.о- торого пропорционально интервалу вре-

мени с

та t.

момента t, до текущего момеи- о

Устройство работает подобным образом до тех пор, пока не сработает пороговый элемент 2 при достижении входного напряжения на информационном входе 46 ур6,вня второго эталонного напряжения U. В этом случае на выходе порогового элемента 2 формируется сигнал логической единицы, который через коммутатор 13 запускает генератор 4 одиночных импульсов, выходной импульс которого через элемент ИЛИ 27 возвращает триггер 7 в нулевое состояние. Единичный сигнал инверсного выхода триггера 7 открывает элементы И 35 и 36, а нулевой сигнал прямого выхода триггера 7 блокирует элемент И 37.

5

5

0

о

Единичный сигнал, формируемми на выходе элемента И 36, через элемент ИЛИ 28 переключает сумматор-вы- читатель 21 в режим суммирования. Единичный сигнал, формируемьп на выходе элемента И 35, устанавливает сумматор-вычитатель 22 также в режим суммирования. После срабатывания порогового элемента 2 устройство работает аналогично, но сумматоры-вы- читатели 21 и 22 работает в режиме суммирования.

Очередной выходной импульс делителя 10 частоты запускает преобразователь 11 аналог - длительность импульса, на выходе которого формируется импульс с длительностью, пропорциональной текущему значению аналогового сигнала на информационном входе 46. На выходе элемента И 31 формируется пачка импульсов первого разряда распределителя 50 импульсов блока 45 управления, которая через коммутатор 14 поступает на один Из входов сумматора-вычитателя 21, на другой вход которого под действием тактовых импульсов генератора 49 импульсов блока 4§ управления с выхода регистра 18 сдвига сдвигается, начиная с младшего разряда, допол- нительньй код, значение которого пропорционально интегралу от входного напряжения на интервале времени между моментом срабатывания порогового элемента 1 и моментом t срабатывания порогового элемента 2.

За время п тактов первый импульс пачки, действующей на выходе элемента И 31, суммируется с дополнительным кодом, сдвигаемым с выхода регистра 18 сдвига, и с выхода сумматора-вычитателя 21 записывается в регистр 18 сдвига под действием тактовых импульсов генератора 49 импульсов блока 45 управления.

Одновременно с этим за время п тактов один импульс последовательности- импульсов т-го разряда распределителя 50 импульсов блока 45 управления суммируется сумматором- вычитателем 22 с дополнительным кодом, значение которого пропорцио- (нально интервалу времени t - t|, g сдвигаемым под действием тактовых импульсов генератора 49 импульсов блока 45 управления с выхода регистра 19 сдвига. Результат суммирования записывается с первого выхода

5

5

0

m

сумматора-вычитателя 22 в регистр 19 сдвига,

Одновременно с этим результат суммирования сумматором-нычитателем 21 сдвигается на установочный вход регистра 20 сдвига и записывается |В него под действием тактовых им- пульсов генератора 49 импульсов блока 45 управления, так как на управляющем входе регистра 20 сдвига в это время действует сигнал логическо единицы с инверсного выхода триггера 6.

В дальнейшем устройство работает аналогичным образом.

В регистре 18 сдвига формируется двоичный код, пропорциональный разности интегралов от входного напряжения на интерналах времени t - t, и

Ч t , а в регистре 19 сдвига формируется двоичный код, пропорциональный разности Интервалов времени (с - t,.,) - (t - t|). Так будет продолжаться до тех пор, пока на втором выходе сумматора-вычитателя 22 не сформируется сигнал переноса из п-го разряда, свидетельствующий об обнулении разности интерналов времени (t - t) - (t-i - t,) 0 (обнулении двоичного кода, сдвиг кмого в регистр 19 сдвига). Момент времени, при котором произошло это событие, обозначим через t (фиг.4), тогда t - t 12 t, .

Следовательно, с момента срабат)- вания порогового элемента 2 прошло время, равное интерналу времени между срабатываниями пороговых элементов 1 и 2. В этом случае сигнал переноса из п-го разряда со второго выхода сумматора-вычитателя 22 открывает элемент И 39, через который импульс п-го выхода распределителя 50 импульсов блока 45 управления устанавливает триггер 8 в единичное состояние. Единичный сигнал прямого выхода триггера 8 открывает элемент И 34, через который проходит очередной выходной импульс делителя 10 частоты.

Коммутатор 16 в режиме вычисления показателя возрастающей экспоненциальной функции поддерживается нулевым сигналом выхода ключа 64 блока 45 управления в состоянии, при котором выход элемента И 34 подключен к S-входу триггера 9. Очередной импульс с выхода делителя 10 частоты после достижения момента времени tj про990

ходит через -мтемот И 34 и коммутатор 16 на S-вход триггера 9, устанавливая его в единичное состояние, Е/тиничный сигнал прямого выхода триггера 9 переключает на время л тактов коммутатор 15 в состояние, при котором выход элемента ИЛИ 53 блока 45 управления подключается ко

Q входу уменьшаемого сумматора-вычитателя 22.

Одновременно с этим очередной выходной импульс делителя 10 частоты через элемент И 34, коммутатор 16 и

5 элемент ИЛИ 26 устанавливает триггер 5 в нулевое состояние, единичный сигнал инверсного выхода которого через элемент ИЛИ 29 переключает сум- матор-вычитатель 22 в режим вычита0 ния. Нулевой сигнал прямого выхода триггера 5 блокирует элементы И 31 и 35.

Кроме этого,очередной выходной импульс делителя 10 частоты в момент

5 tj через элемент И.Т1И 25 запускает преобразователь 11 аналог - длительность импульса для измерения уровня входного напряжения Uj, соответствующего моменту времени t. На выходе

0 преобразователя 11 аналог - длительность импульса формируется импульс (длительность которого пропорциональна уровню входного напряжения Uj), поступающий через элемент ИЛИ 30 на

g вход элемента И 38 и через элемент НЕ 43 блокирующий элемент И 40. На выходе элемента И 38 последовательностью импульсов т-го разряда рас- пределителя 50 импульсов блока 45

0 управления формируется пачка импульсов, количество которых пропорционально уровню входного напряжения Uj. Первый импульс пачки, действующей на выходе элемента И 38, вычи5 тается за время п тактов сумматором- вычитателем 22 из последовательного двоичного кода величины 2 U - U), поступающего с выхода элемента ИЛИ 53 блока 45 управления, и записывается в регистр 19 сдвига под действием -тактовых импульсов генератора 49 импульсов блока 45 управления. Так как З-триггер 9 спустя п тактов после установки его в единичное состояние возвращается в нулевое состояние импульсом, действующим на выходе элемента 60 задержки блока 45 управления, то коммутатор 15 возвращается в исходное состояние и

0

5

подключает выход регистра 19 сдвига к входу уменьшаемого сумматора-вы- читателя 22.

Последовательный двоичный код результата вычитания 2 и - и , - 1 с первого выхода сумматора-вычитателя 22 под действием тактовых импульсов записывается в регистр 19 сдвига и спустя п тактов сдвигается с выхода регистра 19 сдвига через коммутатор 15 на вход уменьшаемого сумматора-вычитателя 22, на вход вычитаемого которого с выхода элемента И 38 поступает второй импульс пачки. На первом выходе сумматора-вычитателя 22 сформируется последовательный двоичный код величины 2 U - U, 2 который под действием тактовых импульсов генератора 49 импульсов блока А5 уУ1равления сдвигается, начиная с младешго разряда, в регистр 19 сдвига. Так будет продолжаться до окончания импульса на выходе преобразователя 11 аналог - длительность импульса. К этому времени в регистре 19 сдвига сформируется последовательный двоичный код величины 2 и,, - и, - и, (и J - и,) - (и, - - Uj), который запоминается динамическим способом за счет циркуляции кода под действием тактовых импульсов генератора 49 импульсов блока 45 управления с выхода регистра 19 сдвига на его информационный вход через коммутатор 15 и сумматор-вы- чит атель 22.

После окончания импульса на вы-, ходе преобразователя 11 аналог - дли тельность импульса на выходе элемента ИЛИ 30 формируется сигнал логического нуля, который блокирует элемент И 38 и через элемент НЕ 43 открывает элемент И 40. Импульс с выхода элемента 60 задержки через ключ 63 блока 45 управления поступает через элемент И 40 и коммутатор 17 (который в режиме вычисления показателя возрастающей экспоненциальной функции подключает выход элемента И 40 к S-входу триггера 6) на S-вход триггера 6 и устанавливает его в единичное состояние.

Единичный сигнал прямого выхода триггера 6 переключает коммутатор 14 в состояние, в котором выход регистра 20 сдвига подключается к ин- формационному входу сумматора-вычитателя 21, а также открывает зле335990 мент И 32 и, поступая в блок 45 управления, через элемент 51 задержки снимает блокировку элементов И 55 и 56 блока 45 управления.

Нулевой сигнал инверсного триггера 6, поступая на управляющий вход регистра 20 сдвига, подключает его информационный вход к его выходу. В

10 это время в регистре 20 сдвига содержится двоичный код, пропорциональный разности интегралов от входного аналогового сигнала на интервалах времени t - t и t - t , кото15 рый под действием тактовых импульсов генератора 49 импульсов блока 45 управления запоминается динамическим способом путем циркуляции с выхода регистра 20 сдвига на его информаци20 онный вход. Сумматор-вычитатель 21 в это время находится в режиме суммирования, так как на его первом управляющем входе действует единичный сигнал инверсного выхода триггера

25 7 через элементы И 36 и ИЛИ 28.

Под действием тактовых импульсов генератора 49 импульсов блока 45 .управления с выходов регистров 18 и 20 сдвига на информационные входы

30 сумматора-вычитателя 21 сдвигаются двоичные коды, пропорциональные разности интегралов от входного аналогового сигнала на интервалах време- ни t, - t и t - t, . Результат сум

мирования с выхода сумматора-вычитателя 21 под действием тактовых импульсов генератора 49 импульсов блока 45 управления сдвигается в регистр 18 сдвига за время п тактов, в течение которого счетчик 23 изменяет свое состояние на единицу, так как на его счетный вход через элемент И 32 по- ; ступает импульс первого разряда распределителя 50 импульсов блока 45 управления.

В дальнейшем устройство работает аналогичным образом до тех пор, пока на одном из выходов превышения или равенства узла 52 сравнения блока 45 управления каждые п тактов вы

полняется сравнение последовательного двоичного кода, сдвигаемого с выхода регистра 18 сдвига, и двоичного кода, сдвигаемого с выхода регистра 19 сдвига через коммутатор 15 и сумматор-вычитатель 22.

В регистре 18 сдвига накапливается в результате работы устройства двоичный код, пропорциональный про

131

изведению количества циклов сумми.рования в сумматоре-вычитателе 21 на двоичный код разности интегралов от входного аналогового сигнала на ин тервалах времени t,, В регистре 19 сдвига хранится динамическим способом двоичный код величины (Uj - и,) - (и - и). В случае равенства или превышения двоичного кода регистра 18 сдвига по отношению к двоичному коду регистра 19 сдвига на одном из выходов узла 52 сравнени сформируется сигнал логической единицы, который откроет элемент И 55 или И 56 блока 45 управления. Импуль п-го выхода распределителя 50 импульсов блока 45 управления проходит через один из элементов И 55 или 56, затем через элемент ИЛИ 54 поступает на R-входы триггеров 6 и 8, .устанавливая их в нулевые состояния. Нулевой сигнал прямого выхода триггера 6 блокирует элемент И 32 и счет в счетчике 23 количества циклов суммирования сумматором-вычитателем 21 завершится. В счетчике 23 запоминается значение показателя возрастающей экспоненциальной функции, которое индицируется группой элементов 24 индикации.

В том, что в счетчике 23 устанавливается численное значение показателя oi возрастающей экспоненциальной функции Ug и„(1 - е ), мож:Но убедиться из рассмотрения следу ющего соотношения:

t,t,

8. dt - f и

i,

7

«.Ju

8

dt

1

(и, - и,) - (и, - UJ

Если разби гь интервалгз времени

Ч Ч t на равные промежутки времени ut и заменить интеграл его приближенным значением по формуле прямоугольников, то выражение (1) примет следующий виц:

5

Ци

ах.

5

Ни

41

SXj

М, (2 и - и, ) - М, .и, , (2) 55

где М

- масштабный коэффи- цие н т;

количестно интервалов д t.

Масштаб}1ый ко:)ффицнент удобно выбрать так, чтобы

f n-k

- )

№-

(3)

10 где

15

m

. я с

П

1,2,3,...,п/2 20

25

30

тактовая частота генератора 49 импульсов; коэффициент деления делителя 10 частоты; количество разрядов регистров 18-20 сдвига; номер разряда распределителя 50 импульсов блока 45 управления, который соединен с одним из входов элемента И 38.

При выборе масштабного коэффициента Мд в соответствии с выражением (3) двоичный код величины 2 Uj, - - и, устанавливается на коммутаторе 51 блока 45 управления со сдвигом на m - 1 разряд в сторону старших разрядов, что равносильно умножению величины

(2 и - и,) на К

&t

Умножение

величины М на Ug обеспечивается 35 путем формирования на выходе элемента И 38 пачки импульсов, соответствующей величине Uj, из последовательности импульсов т-го выхода-распределителя 50 импульсов блока 45 управ- 40 ления.

В процессе работы устройства при достижении условия

Ы. Г S

г ни

( I

БЧ ,

5

Ьи г-9Х

.м,(и,-и,)-(из-и,)

(4)

0

5

узел 52 сравнения блока 45 управления останавливает процесс вычисления показателя возрастающей экспоненциальной функции, а величина показателя фиксируется в десятичном (или двоичном) счетчике 23 в десятичном (или двоичном) виде,

В режиме вычисления показателя убывающей экспоненциальной функции

- oitвида Ug, Ug е

где

Uo на15

чальное значение входного напряжения, устройство работает следующим образом.

Ключ 64 блока 45 управления подключает вход элемента НЕ 59 к выходу элемента НЕ 57. Сигнал логической единицы выхода элемента НЕ 57 поступает через ключ 64 блока 45 управления и через элемент ИЛИ 28 на первый управляющий вход сумматора-вычитателя 21, устанавливая его в режим суммирования, а также, воздействуя на управляющие входы коммутаторов 16 и 17, переключает их состояния, при которых выход генератора 4 одиночных импульсов подключается через коммутатор 16 к S-входу триггера 9 и через коммутатор 17 - к S-входу триггера 6.

Сигнал логического нуля, действующий на выходе элемента НЕ 59 блока 45 управления, блокирует элементы И 37 и 38, Сигнал логической единицы с выхода элемента НЕ 57 поступает через ключ 64 блока 45 управления на управляющие входы коймутаторов 12 и 13, переключая их в состояния,при которых коммутатор 12 подключает выход элемента НЕ 41 к входу запуска генератора 3 одиночньгх импульсов, а коммутатор 13 подключает выход элемента НЕ 42 к входу запуска генератора 4 одиночных импульсов.

Установка устройства в исходное состояние выполняется таким же образом, как и в режиме вычисления показателя возрастающей экспоненциальной функции.

На коммутаторе 51 блока 45 управления устанавливается двоичный код разности Иу - и, уровней эталонных напряжений U и U,, действующих соответственно на входах 47 и 48 устройства. На информационный вход 46 устройства подается аналоговый сигнал, изменяющийся по экспоненциаль %ному закону Ug е. ,

В исходном состоянии на выходах пороговых элементов 1 и 2 действуют сигналы логической единицы, так как начальное значение входного напряжения Up превышает эталонные уровни и, и и.

. На выходах элементов НЕ 41 и НЕ 42 в это время действуют сигналы логического нуля. В режиме вычисления показателя экспоненциальной функции ключом 63 блока 45 управления подключают выход элемента 60 за1

10

15

20

25

35990

держки к тактовым входам генераторов 3 и 4 одиночных импульсов и ко входу элемента И 33,

Как только входное напряжение, действующее на информационном входе 46 устройства, достигнет уровня эталонного напряжения U, срабатывает пороговый элемент 2, на выходе которого устаналвивается нулевой сигнал, формирующий единичный сигнал на выходе элемента НЕ 41, который через коммутатор 12 запускает генератор 3 одиночных импульсов. Выходной импульс генератора 3 одиночных импульсов устанавливает триггеры 5 и 7 в единичные состояния и через элемент ИЛИ 25 запускает преобразователь 11 аналог - длительность импульса, на выходе которого формируется импульс, длительность которого пропорциональна аналоговому сигналу, действующему на информационном входе 46 устройства. Из последовательности импульсов с первого выхода распределителя 50 импульсов блока 45 управления элемент И 31, открытый единичным сигналом триггера 5 и управляемый выходным импульсом преобразователя 11 аналог - длительность импульса, формирует пачку импульсов, количество которых пропорционально аналоговому сигналу, действующему на информационном входе 46 устройства.

Пачка импульсов с выхода элемента И 31 через коммутатор 14 поступает на на один из входов сумматора-вычитате- ля 21, который за время п тактов по каждому импульсу пачки увеличивает на единицу младшего разряда двоичный код, сдвигаемьш под действием такто- вых импульсов генератора 49 импульсов блока 45 управления с выхода ре- |гистра 18 сдвига. Последовательный 45 двоичный код с выхода сумматора-вы- читателя 21, функционирующего в режиме суммирования, за время п тактов записывается в регистр 18 сдвига под действием тактовых импульсов

5Q Генератора 49 импульсов блока 45 управления, В результате к моменту окончания действия импульса на выходе преобразователя 11 аналог - длительность импульса в регистре 18

gg сдвига формируется двоичный код,значение которого пропорционально текущему значению напряжения, действующего на информационном входе 46 устройства.

30

35

40

1713

Единичный сигнал прямого н.1хода триггера 5 чероз элемент 44 задержки на длительность тактового импульса снимает блокировку элемента И 33, через который на информационный вход делителя 10 частоты поступает последовательность импульсов с п-го выхода распределители 50 импульсов, прошедших через элемент 60 задержки и ключ 63 блока 45 управления.

Выходной импульс делителя 10 частоты через элемент ИЛИ 25 вновь запускает преобразователь 11 аналог - длительность импульса, котор.1й вновь формирует импульсный сигнал, длительность которого пропорциональна текущему значению напряжения на информационном входе 46 устройства. На выходе элемента И 31 вновь фо)- мируется пачка импульсов, количество которых пропорционально текущему значению напряжения на информационном входе 46 устройства. Сумматор-вычи- татель 21 к двоичному коду предыдущего значения экспон-енциальной функции, сдвигаемому с выхода регистра 18 сдвига под действием тактовых импульсов генератора 49 импульсов блока 45 управления, прибавляет количество импульсов, пропорциональное те- кут.чему значению экспоненциальной функции, а результат суммирования записывается, начиная с младшего разряда, в регистр 18 сдвига за время п тактов.

В дальнейшем устройство работает аналогичным образом, а в регистре 18 сдвига накапливается двоичный код, значение которого пропорционально интегралу от аналогового сигнала экспоненциальной функции, действующего на информационном входе 46 устройства.

Так будет продолжаться до тех пор пока не сработает пороговый элемент 1 при достижении аналоговым сигналом экспоненциальной функции уровня эталонного напряжения U,. В этом случае на выходе порогового элемента 1 .формируется нулевой сигнал, который формирует на выходе элемента НЕ 42 единичный сигнал, запускающий через коммутатор 13 генератор 4 одиночных импульсов. Выходной сигнал генератора 4 одиночных импульсов через коммутаторы 16 и 17 устанавливает в единичное состояние соответственно триггеры 9 и 6.

0 К этому мом(Н-1 у HjJOMOHn п регистре 18 сднига накяплиилстся двоичный код, значение которого пропорционально интегралу от аналогового сигнала

экспоненциальной функции на интервале времени между событиями перехода входн)1м напряжением уровней U и U, эталонного напряжения, В регистре

20 сдвига к этому моменту времени

содержится тот же двоичный код, который с выхода регистра 18 сдвига через сумматор-вычитатель 21 под действием тактовых импульсов генератора

импульсов блока 45 управления записался в регистр 20 сдвига при нулевом состоянии триггера 6, Установка /триггера 6 в единичное состояние переводит регистр 20 сдвига в режим

хранения двоичного кода, значение которого пропорционально интегралу экспоненциальной функции между двумя уровнями эталонного напряжения. Двоичный код запоминается в регистре

20 сдвига динамическим способом за счет циркуляции кода под действием тактовых импульсов генератора 49 импульсов блока 45 управления с выхода регистра 20 сдвига на его информационный вход.

Триггер 9 устанавливается в единичное состояние на время п тактов и сбрасывается в нулевое состояние импульсом выхода элемента 60 задержки блока 45 управления. Единичный сигнал прямого выхода триггера 9 переключает коммутатор 15 на время п тактов в состояние, при котором выход элемента ИЛИ 53 блока 45 управ- ления подключается ко входу суммато- ра-вычитателя 22, через который в регистр 19 сдвига под действием тактовых импульсов генератора 49 импульсов блока 45 управления записывается

двоичный код величины U - U, , установленный на коммутаторе 51 блока 45 управления. Спустя п тактов коммутатор 15 подключает вход сум- матора-вычитателя 22 к выходу регистра 19 сдвига, в котором запоминается динамическим способом двоичньгй код,

После установки триггера 6 в единичное состояние за каждые п тактов

работы устройства, где п - количество разрядов регистров 18-20 сдвига, выполняется один цикл суммирования сумматором-вычитателем 21 двоичных кодов регистров 18 и 20 сдвига, так как коммутатор 14 при единичном состоянии триггера 6 подключает выход регистра 20 сдвига ко второму входу сумматора-вычитателя 21, пер- вьй вход которого подключен к выходу регистра 18 сдвига. Поскольку выход сумматора-вычитателя 21 соединен с информационным входом регистра 18 сдвига, то в нем накапливается двоичный код, равный произведению количества циклов суммирования на величину двоичного кода регистра 20 сдвига. В это время счетчик 23 выполняет подсчет количества циклов суммирования двоичных кодов сумма- тором-в ычитателем 21, так как через каждые п тактов на его счетном входе действуют импульсы последовательности первого выхода распределителя 50 импульсов блока 45 управления, поступающие через элемент И 32, открытый единичным сигналом прямого выхода триггера 6.

Так будет продолжаться до тех пор, пока двоичный код, накапливаемый в регистре 18 сдвига, не достигнет или превысит двоичного кода величины и U( , хранящегося в регистре 19 сдвига. Если двоичный код в регистре 18 сдвига достигнет или првысит двоичный код регистра 19 сдвига, то на одном из йыходов равенства или превышения узла 52 сравнения блока 45 управления сформируется единичный сигнал, который откроет один из элементов И 55 или 56 блока 45 .управления. Импульс последовательности п-го разряда распределителя 50 импульсов блока 45 управления через один из элементов И 55 или 56, элемент ИЛИ 54 блока 45 управления поступит на R-вход триггера 6 и установит его в нулевое состояние, при котором блокируется элем ент И 32,

В счетчике 23 зафиксируется з-на- чение показателя убывающей экспоненциальной функции, которое индицируется группой элементов 24 индикации

Показатель убывающей экспоненциальной функции определяется на основании соотношения

dt l об

(e

oit.

е-° Ъ -55

и,

ot

которое преобразуется н условие:

feftUex; MU (и, - UJ, (6) t L,.i J

по достижении которого узел 52 сравнения блока 45 управления останавливает процесс вычисления показателя

oi экспоненциальной функции в счетчике 23.

Масштабный коэффициент М выбирается из соотношения (3) и учитывается при установке двоичного кода величины U, - U, на коммутаторе 51 блока 45 управления путем сдвига кода на m - 1 разряд в сторону старших разрядов, где т 1, 2, 3,... Узел 52 сравнения (фиг.З) блока

45 управления работает следующим образом.

В исходном состоянии триггеры 83 и 84 находятся в нулевом состоянии, в которое их устанавливает через каждые п тактов последовательность импульсов выхода элемента 60 задержки блока 45 управления, поступающая на вход 93 сброса. На синхронизирующие входы триггеров 83 и 84 по щине

92 поступает последовательность тактовых импульсов генератора 49 импульсов блока 45 управления.

Каждые п тактов узел 52 сравнения осуществляет поразрядное сравнение

двух последовательных двоичных кодов, поступающих, начиная с младшего разряда, на информационные входы 90 и 91.

Если на входе 91 действует сиг- нал логической единицы, на входе 90 сигнал логического нуля, то на выходе элемента И 85 формируется сигнал логической единицы, устанавливающий триггер 83 в единичное состояние и сбрасывающий триггер 84 в нулевое состояние.

50

-55

Если на входе 91 действует сигнал логического нуля, а на входе 90 - сигнал логической единицы, то на выходе элемента И 86 формируется сигнал логической единицы, устанавливающий триггер 84 в единичное состояние и сбрасывающий триггер 83 в нулевое состояние.

В случае комбинаций кодов 00 и 11 на входах 90 и 91 на выходах элементов И 85 и И 86 действуют сигналы логического нуля, а триггеры 83 и 84 сохраняют предшествующее состояние.

2113

Если двоичный код, поступающий по входу 91, превышает двоичный код, действующий на входе 90, то спустя п тактов триггер 83 находится в единичном состоянии и на выходе 94 действует сигнал логической едини.

В случае равенства двоичных кодов триггеры 83 и 84 сохраняют нулевое состояние и на выходе 95 элемента ИЯИ-НЕ 87 формируется сигнал логиче- 5СКОЙ единицы.

Если двоичный код на входе 91 меньше двоичного кода на входе 90, то спустя п тактов триггер 84 находится в единичном состоянии и на выходе 96 действует сигнал логической единицы.

Формула изобретения

Устройство для вычисления показателя экспоненциальной функции, содержащее первый и второй пороговые элементы, первый и второй генераторы одиночных импульсов, делитель частоты, преобразователь аналог - длительность импульса, первый и второй RS- триггеры, S-триггер, первый, второй, третий и четвертый коммутаторы,первый и второй регистры сдвига, первый сумматор-вычитатель,счетчик,блок элементов индикации, первый, второй, третий, четвертый и пятый элементы И, первый элемент ИЛИ, первый и второй элементы НЕ, элемент задержки и блок управления, содержащий генератор импульсов, распределитель импульсов, коммутатор, узел сравнения, первый и второй элементы ИЛИ, первый и второй элементы И, первый элемент задержки, первьй элемент НЕ, первый, второй и третий ключи, выход генератора импульсов соединен с входом распределителя импульсов, с так- товым входом узла сравнения и с входами синхронизации первого и второго регистров сдвига, установочные входы которых соединены с входом логического нуля устройства, п выходов распределителя импульсов (где п - количество разрядов регистров сдвига) соединены с соответствующими информационными входами коммутатора, управляющий вход которого соединен с входом задания начального кода устройства, п выходов коммутатора сое-- динены с соответствующими входами превого элемента ИЛИ, первый выход

990

распределителя импульсов блока управления соединен с пергзыми ь ходлми первого и второго элементов И, п-й выход распределителя импульсов подключен к первым входам первого и второго элементов И блока управления и через первый элемент задержки блока управления подсоединен к перQ вому информационному входу второго ключа и к входу сброса узла сравнения, выход равенства и выход пре- вьшения которого соединены соответственно с вторыми входами первого и

5 второго элементов И блока управления, выходы которых соединены соответственно с первым и вторым входами второго элемент а ИЛИ блока управления, выход которого соединен с R0 входом второго RS-триггера, выход

первого ключа соединен с третьим входом второго элемента ИЛИ блока управления и установочными входами счетчика и делителя частоты, управля5 ющие входы первого и второго ключей соединены с входом задания режима работы устройства, управляющий вход третьего ключа соединен с входом задания вида экспоненциальной функции

0 устройства, первый информационный вход третьего ключа соединен с выходом первого элемента -НЕ блока управления, вход которого подключен к входу логического нуля устройства, вторые информационные входы ключей блока управления соединены с входом логического нуля устройства, выход второго ключа блока управления со- единен с тактовыми входами первого и

д второго генераторов одиночных импульсов и первьпч входом .третьего элемента И, выход третьего ключа блока управления соединен с управляющими входами первого и второго коммутато5 ров, информационный вход устройства соединен с первыми входами первого и второго пороговых элементов и с информационным входом преобразователя аналог - длительность импульса,

0 второй вход первого порогового элемента соединен с входом задания первого эталонного напряжения устройства, вход задания второго эталонного напряжения устройства соединен с вто5 рым входом второго порогового элемента, выход которого соединен с первым информационным входом второго коммутатора и через первый элемент НЕ с первым информационным входом пер5

первого коммутатора, выход первог о порогового элемента соединен с вторым информационным входом первого коммутатора и через второй элемент НЕ с вторым информационным входом второго коммутатора, выходы первого и второго коммутаторов подсоединены соответственно к входам запуска первого и второго генераторов одиночных импульсов, выход первого из которых подсоединен к первому входу первого элемента ИЛИ и к S-входу первого RS-триггера, прямой выход которого соединен с вторым входом первого элемента И и через элемент задержки с вторым входом третьего элемента И, выход которого подключен к информационному входу делителя частоты, выход которого соединен с вто рым входом первого элемента ИЛИ, выход которого подключен к входу запуска преобразователя аналог - длительность импульса, выход которого соединен с третьим входом первого элемента И, прямой выход второго RS- триггера соединен с управляющим входом третьего коммутатора и с вторым входом второго элемента И, выход которого соединен со счетным входом счетчика, выходы разрядов которого соединены с соответствующими входами блока элементов индикации, выход третьего коммутатора соединен с первым информационным входом первого сумматора-вычитателя, выход которого соединен с информационным входом первого регистра сдвига, выход которого соединен с вторым информационным входом первого сумматора-вычитателя, прямой выход S-триггера соединен с управляющим входом четвертого коммутатора, отличаюп ее ся тем, что, с целью расширения области применения за счет вычисления показателя для убывающей или возрастающей экспоненциальной функции с произвольным установившимся значением, в него введены второй сумматор-вы- читатель, третий регистр сдвига, пятый и шестой коммутаторы, третий и четвертый RS-триггеры, второй, третий, четвертый, пятый и шестой элементы ИЛИ, шестой, седьмой,, восьмой, девятый и десятый элементы И, третий элемент НЕ, а в блок управления введены второй и третий элементы НЕ и второй элемент задержки, .подключенный входом к прямому выхо

0

5

5

0

0

ду второго RS-трнггера, а выходом - к третьим входам первого и второго эле - ментов И блока управления ,п-й выход распределителя импульсов соединен с первым входом девятого элемента И и через второй элемент НЕ блока управления соединен с первыми входами шестого и седьмого элементов И, выход третьего ключа соединен с первым входом четвертого элемента ИЛИ и с управляющими входами пятого и шестого коммутаторов и через третий элемент НЕ блока управления соединен с вторым входом седьмого и первым входом восьмого элементов И, т-й выход распределителя импульсов блока управления соединен с вторым входом восьмого элемента И, выход генератора импульсов блока управления соединен с входом синхронизации третьего регистра сдвига, выход второго ключа блока управления под- соединен к первому входу десятого элемента И, выход первого элемента НЕ блока управления соединен с первым информационным входом первого ключа, выход которого соединен с управляющими входами первого и второго регистров сдвига и с первыми входами второго и третьего элементов ИЛИ, выходы которых соединены соответственно с R-входами первого и третьего RS-триггеров, выход первого элеg мента задержки блока управления соединен с R-входом S-триггера, вьпсод второго элемента ИЛИ блока управле ния соединен с R-входом четвертого RS-триггера, выход первого элемента

0 ИЛИ блока управления соединен с первым информационным входом четвертого коммутатора, выход которого соединен с первым информацио нным входом второго сумматора-вычитателя,первый вы5 ход которого соединен с первым информационным входом узла сравнения блока управления и с информационным входом второго регистра сдвига, выход которого соединен с вторым информационным входом четвертого коммутатора, второй выход второго сумматора- вычитателя подключен к второму входу девятого элемента И, выход которого подсоединен к S-входу четвертого RSg триггера, прямой выход которого соединен с вторым входом десятого элемента И и с первым входом четвертого элемента И, второй вход которого подсоединен к выходу делителя частоты.

0

а выход четвертого элемента И соединен с nepniiiM информлциониым пходом пятого коммутатора, )д К(1торого соединен с S-пходом Я-тригтерл и г вторым входом пторого элемента ИЛИ, выход пторого генератора одрпкпгных импульсов coeдннefI с BTopiiFM нходом третьего элемента ИЛИ, с вторым информациокным входом пятого коммутато- ю ходом Пятого и вторым входом шесра и с первым информяционным входом шестого коммутатора, выход которог-о

соединен с S-входом второго RS-трнггера, инверсный выход которого соединен с управляющим входом трет1,сго регистра сдвига, выход которого соединен со своим информацис)нным входом и с первым информациоирп гм входом третьего коммутатора, второй информационный вход которого подсоединен

к выходу первого элемента И, выход первого сумматора-вьшитателя соединен с установочным входом третьего регистра сдвига, выход первого стра сдвига соединен с вторым информационным входом узла сравнения блока управления, выход первого генератора одиночных импульсов соединен с S-входом третьего RS-триггера, прямой выход которого соединен с третьим входом седьмого элемента И, выход которого соединен с первым входо управления режимом первого сумматорл-яь чит,-1Т(чи 1 пергилм их(1дом пятого гкчрмелта ИЛИ. HTopofi ход которого 1юдго(диири к. HHiicpcKoMy выходу пер- ног о КЯ-триг1 (ра, л В1.1ход пятого элемента ИЛИ с-оеднпен с первым входом У11рпвле 1ия режимом зторого суммато- ра-вычитателя, инверсньи выход третьего RS-тригг ера соединен с первым

того элементов И, гилход последнего in которых соединен с вторым входом четвертого элемента ИЛИ, выход которого соединен с вторым входом управления режимом первого сумматора-вы- читателя, выход первого RS- триггера подсоединен к первому входу шестого элемента ИЛИ и к второму входу пятого, элемента И, выход которого соединен с Вторым входом угтравления режимом второго суммато- ра-вычитателя, выход преобразователя аналог - длительность импульса соединен с вторым входом шестого

элемента И.Г1И, выход которого соединен с входом третьего элемента НЕ и с третьим входом восьмого элемента И, выход которого соединен с вторым информационным входом второго

сумматора-вьгчитателя, выход третьего элемента НЕ соединен с третьим входом десятого элемента И, выход которого соединен с вторым информационным входом шестого коммутатора.

(8},

- °,oi

0 fOS

Ч OJS

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

| Устройство для контроля экспоненциальных процессов | 1986 |

|

SU1310781A1 |

| Устройство для контроля экспоненциальных процессов | 1990 |

|

SU1732331A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1335989A1 |

| Квадратор | 1987 |

|

SU1501049A1 |

| Устройство для контроля экспоненциальных процессов | 1984 |

|

SU1282087A1 |

| Устройство для контроля экспоненциальных процессов | 1987 |

|

SU1500997A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1982 |

|

SU1043677A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1983 |

|

SU1129611A1 |

| Устройство для моделирования графов | 1989 |

|

SU1709346A2 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при исследовании процессов различной физической природы описывакнцихся экспоненциальной функцией. Цель изобретения - расширение области применения за счет обеспечения вычисления показателя убывающей или возрастающей экспоненциальной функции с произвольным установившимся значением. Устройство содержит два пороговых- элемента, преобразователь аналог-длительность импульса, два генератора одиночных импульсов, четыре RS-триггера, S-триг- гер, два сумматора-вычитателя, шесть коммутаторов, три регистра сдвига,, счетчик, группу элементов индикации, делитель частоты, десять элементов И, шесть элементов ИЛИ, три элемента НЕ, элемент задержки, блок управления. Устройство работает в двух режимах. В основе вычисления лежит сравнение интегрального значения от экспоненциальной временной функции на определенном интервале времени с . априорно-заданной константой, зависящей от значений функции на границах интервала, по достижении равенства этих двух величин в счетчике фиксируется показатель экспоненты. 4 ил. § (Л 00 САЭ СЛ СО ф

Редактор Н.Егорова

Составитель Е.Телешинин

Техред М.Ходанич Корректор А.Зимокосов

Заказ 4048/43 Тираж 672Подписное

ВНИИ1Ш Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

| Устройство для вычисления показа-ТЕля эКСпОНЕНциАльНОй фуНКции | 1979 |

|

SU824230A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1983 |

|

SU1129611A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-09-07—Публикация

1986-04-29—Подача