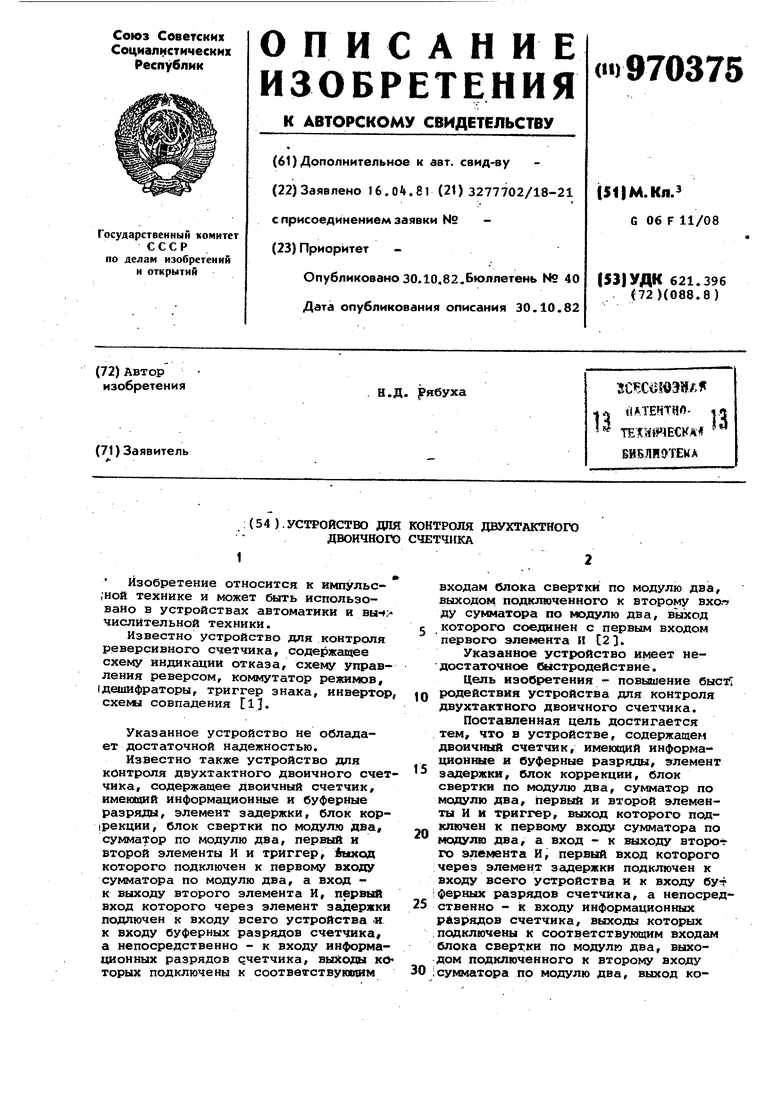

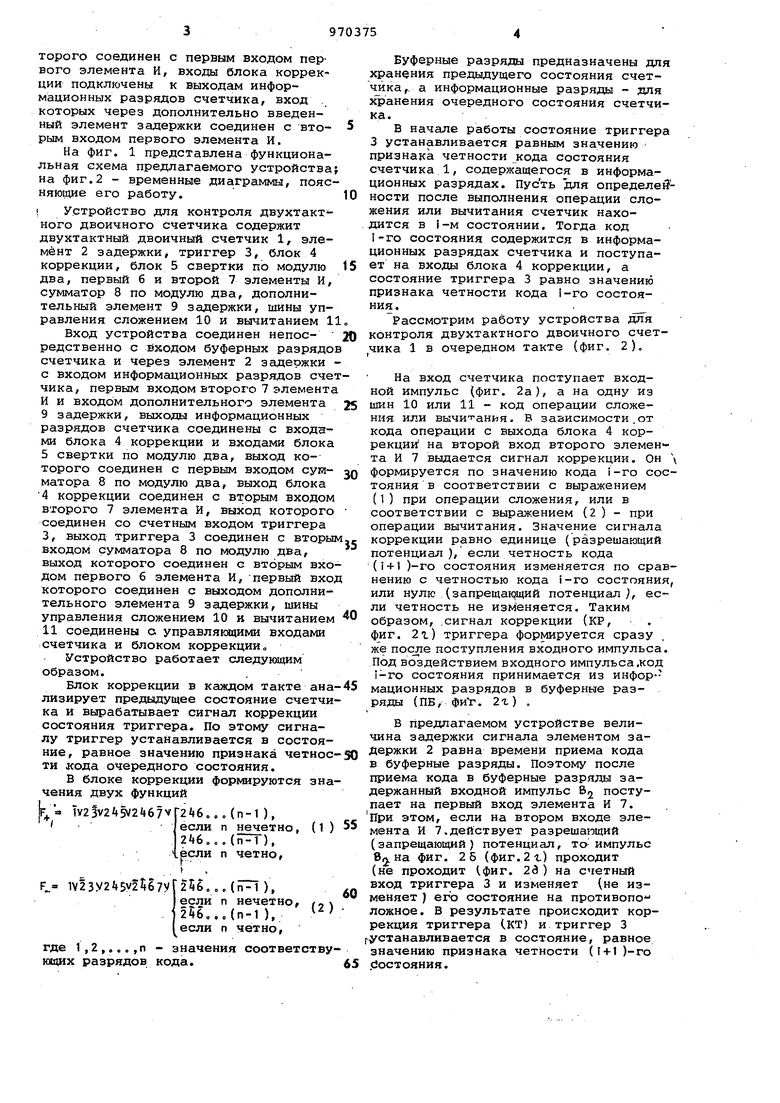

торого соединен с первым входом первого элемента И, входы блока коррекции подключены к выходам информационных разрядов счетчика, вход .. которых через дополнительно введенный элемент задержки соединен с вторым входом первого элемента И. На фиг. 1 представлена функциональная схема предлагаемого устройства на фиг.2 - временные диаграммы, пояс няющие его работу. Устройство для контроля двухтактного двоичного счетчика содержит двухтактный двоичный счетчик 1, элемент 2 задержки, триггер 3, блок 4 коррекции, блок 5 свертки по модулю два, первый 6 и второй 7 элементы И, сумматор 8 по модулю два, дополнительный элемент 9 задержки, шины управления сложением 10 и вычитанием 1 Вход устройства соединен непосредственно с входом буферных разрядо счетчика и через элемент 2 за,цержки с входом информационных разрядов сче чика, первым входом второго 7 элемент И и входом дополнительного элемента 9 задержки, выходы информационных разрядов счетчика соединены с входами блока 4 коррекции и входами блока 5 свертки по модулю два, выход которого соединен с первым входом суйматора 8 по модулю два, выход блока 4 коррекции соединея с вторым входом второго 7 элемента И, выход которого соединен со счетным входом триггера 3, выход триггера 3 соединен с вторы входом сумматора 8 по модулю два, выход которого соединен с вторым вхо дом первого 6 элемента И,первый вхо которого соединен с выходом дополнительного элемента 9 задержки, шины управления сложением 10 и вычитанием 11 соединены а управляющими входами счетчика и блоком коррекции Устройство работает следующим образом.. Блок коррекции в каждом такте ан лизирует предыдущее состояние счетчи ка и вырабатывает сигнал коррекции состояния триггера. По этому сигналу триггер устанавливается в состояние, равное значению признака четное ти кода очередного состояния. В блоке коррекции формируются зн чения двух функций Ty23V2i5V2i67V 246.,Лп-1), если п нечетно, (1 2.6.. Лп-1 ), если п четно. F 1у1зУ2 5У25б7У . Лп), если п нечетно, 25б,.,(п-1 ), если п четно. где 1,2,...,п - значения соответств Ю1цих разрядов кода. Буферные разряды предназначены для хранения предыдущего состояния счетчика,, а информационные разряды - для хранения очередного состояния счетчика. В начале работы состояние триггера 3 устанавливается равным значению признака четности кода состояния счетчика 1, содержащегося в информационных разрядах. Пусть для определейности после выполнения операции сложения или вычитания счетчик нахоится в i-M состоянии. Тогда код 1-го состояния содержится в информационных разрядах счетчика и поступает на входы блока 4 коррекции, а состояние триггера 3 равно значению признака четности кода 1-го состояния. Рассмотрим работу устройства для контроля двухтактного двоичного счетчика 1 в очередном такте (фиг. 2), На вход счетчика поступает входной импульс (фиг. 2а), а на одну из шин 10 или 11 - код операции сложения или вычитания, В зависимости.от кода операции с выхода блока 4 коррекции на второй вход второго элемента И 7 выдается сигнал коррекции. Он формируется по значению кода i-ro состояния в соответствии с выражением (1) при операции сложения, или в соответствии с выражением (2 ) - при операции вычитания. Значение сигнала коррекции равно единице (разрешающий потенциал), если четность кода (i + 1 )-го состояния изменяется по сравнению с четностью кода i-ro состояния, или нулю (запрещак)щий потенциал , если четность не изменяется. Таким образом, .сигнал коррекции (КР, . фиг. 2г) триггера формируется сразу . же nocje поступления входного импульса. Под воздействием входного импульса .код i-ro состояния принимается из инфор-мационных разрядов в буферные разряды (ПБ, фиг. 2 г ) о В Предлагаемом устройстве величина задержки сигнала элементом задержки 2 равна времени приема кода в буферные разряды. Поэтому после приема кода в буферные разряды задержанный входной импульс Bj поступает на первый вход элемента И 7. при этом, если на втором входе элемента И 7,действует разрешающий (запрещающий) потенциал, то- импульс 8, на фиг. 25 (фиг. 2 г) проходит (не проходит (фиг. 2д ) на счетный вход триггера 3 и изменяет (не изменяет ) его состояние на противопо ложное. В результате происходит коррекция триггера (КТ) и триггер 3 устанавливается в состояние, равное значению признака четности (1 + 1 )-го сЗостояния.

Подвоздействием этого же импульса бд выполняется операция. (Cf, заданная кодом операции. Результат операции (очередное (I+1 )-е состояние) принимается в информгщионные разряды (пи). Далее код (f + l)-ro состояния с выхода информационных разрядов поступает на входы блока 5 свертки по модулю два, где фиксируется значение признака четности этого кода (СВ).

При правильной работе счетчика значение признака четности совпадает с состоянием триггера 3, результат сложения (СЛ) в сумматоре 8 по модулю 2 равен нулю и на второй Bxog. элемента И 6 поступает запрещающий потенциал. Поэтому сигнал схиибки на выходе элемента И 6 отсутствует. При ошибке счетчк: а совпадение отсутствует и на второй вход элемента И б поступает запрещаюкщй потенциал. На первый вход элемента И 6 поступает задержанный элементами 2 и 9 задержки входной импульс вд и на выходе элемента И 6 формируется сигнал ошибки.

Задержка сигнала элементом 9 эа,держки равна сумме времен.выполнения операции в счетчике, приема код ( + )-го состояния в информационные разрядам, свертки информации в блоке 5 свертки по модулю два и сложения в cyNwaTope 8 по модулю два.

Введение дополнительного элемента 9 задержки и подключение входов бло,ка 4 коррекции к выходам информационных разрядов счетчика позволило

сократить длительность такта работы счетчика за счет совмещения во вреМени части операций предыдущего такта с операциями очередного такта.

Формула изобретения

Устройство для контроля двухтактного двоичного счетчика, содержащее двоичный счетчик, имекхций информационные и буферные разряды, элемент задержки, блок коррекции, блок свертки по модулю два, сумматор по модулю два, первый и второй элементы И и триггер, выход которого подключен:. к первому входу сумматора по модулю

два, а вход - к выходу второго элемента И, первый вход которого через элемент задержки подключен к входу всего устройства и к входу буферных разрядов счетчика, а иепосредственно - к входу информационных разря дов счетчика, выходы которых подключены к соответствующим входам блока свертки по модулю два, выход которого подключен к второму входу сумматора по модулю два, выход которого соединен с первым входом первого элемента И, о т л и ч а ю щ е е с я , тем, что, с целью повышения быстродействия, входы блока коррекции подключены к выходам информационных

разрядов счетчика, вход которых че- рез дополнительно введенный элемент задержки соединен с вторым входом первого элемента И.

Источники информации,

принятые во внимание при экспертизе

1.Авторское свидетельство СССР 444186, кл. 6 06 F 11/00, 1975.

2.Авторское свидетельство СССР 607221 кл. G 06 F 11/08, 1978

(прототип).

и

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля двухтактного двоичного счетчика | 1975 |

|

SU607221A1 |

| Счетчик с контролем на четность | 1981 |

|

SU1010728A1 |

| Устройство для вычисления синдромов кода Рида-Соломона | 1990 |

|

SU1751860A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Пересчетное устройство с контролем | 1986 |

|

SU1378050A1 |

| ВЫЧИСЛИТЕЛЬНЫЙ ЭЛЕМЕНТ ДЛЯ ОСУЩЕСТВЛЕНИЯ БЫСТРОЙ СВЕРТКИ | 1991 |

|

RU2028666C1 |

| Микропрограммное устройство управления с самоконтролем | 1985 |

|

SU1247871A1 |

| Арифметико-логическое устройство связного процессора | 1978 |

|

SU765808A1 |

| Устройство для контроля счетчика импульсов | 1985 |

|

SU1307580A1 |

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1129655A1 |

Авторы

Даты

1982-10-30—Публикация

1981-04-16—Подача