(54) АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО СВЯЗНОГО Изобретение относится к вычислительной технике, а более конкретно к арифметическим устройствам связных процессоров. Известны арифметические устройства, содержащие входные регистры, выходной регистр, блок адресуемых регистров, схемы, выполняющие логические и арифметические операции 2 . Этим устройствам свойственна низкая скорость обработки информации при использовании их в связном процессоре , Наиболее близким к изобретению по технической сущности является арифметическое устройство для чисел с переменной длиной,-содержащее вход ные регистры, двоичный сумматор, логические схемы, маску, вентильные схемы, схемы управления вводом и вы водом информации, переносом и заемом,шины данных, шины управления, выходной коммутатор З , Одной из основных задач,выполняемых связным процессором,является реа лизация кодозамиты информации,наиболее распространенными методами котоПРОЦЕССОРАрой являются контроль tio четности и использование кодов.Хэмминга. В случае использования метода контроля по четности при пригале с линии связи информации (символа) необходимо производить анализ тоящества mod 2(Ск) 0 БЧСк + ТИПЧ 0 (1) где mod 2(Ск) - сумма по модулю два разрядов информации Ск (к-го символа), принятой с линии; ВЧС - контрольный бит четности этой информации;ТИПЧ - тип четности, принятой на данной линии (четность или нечетность). Если тождество не выполняется, то информация принята с искажениями. При передаче в линию информации (символа) необходимо сформировать для нее контрольный бит в соответствии с заданным ТИПЧ. В случае использования кодозащиты по методу Хзмк4инга необходимо для передаваемого (принимаемого) информационного массива сформировать определенный контрольный код, каждый разряд которого есть суьвла по модулю два некоторых разрядов информационного массива. При посимвольной обработке в связном процессоре массив пе редается (принимается) символами, с каждым из которых проделывается подобная операция, т.е. при приеме(передаче очередного символа информационного массива необходимо для каждого -го бита контрольного кода проделать следующую операцию: bx.rbi©mod2(c,, (Z) i - О V N ; , -значение -го бита контрольного кода после обработки (к+1)-го -символа -значение 4-го бита контрольного кода после обработки к-го символа; -(к+1) символ; -маска (к+1)-го символа для 4 -го разряда контроль ного кода; число разрядов контрольно го кода; L - количество символов в мас сиве (BJ, 0). Применение данного устройства по влечет за собой программную реализа цию этих методов кодозаидиты с испол зованием большого количества логич ких операций выделения разрядов и сложения их по модулю два, что приведет к существенному снижению производительности связного процессора т.е. уменьшению количества обрабатываемых символов в -единицу времени Целью изобретения является повышение быстродействия связного процессора. Достигается это тем, что в арифметико-логическое устройство связного процессора, содержащее входной коммутатор, первый информационный вход которого является первым входом устройства, два регистра операн дов, вход первого из которых соединен с выходом входного коммутатора, вход второго является вторым входом .устройства,,а выходы регистров операндов соединены соответственно с первыми и вторыми входами сумматора вычитателя, блока логического сложе ния, сумматора по модулю два,блока логического умножения, выходы которых соединены с первыми четырьмя ин формационными входами выходного ком , пятый информационный вход которого соединен с выходом второго регистра операндов, а выход выходного коммутатора является выходом р зультата устройства и соединен с вт рым информационным входом входного коммутатора и с входом блока анализа на нуль, выход которого является выходом признака устройства, соединен с первым входом триггера нулевого результата и с входом признака местного устройства управления, первый информационный вход которого соеинен с выходом триггера переносазаема и является выходом переносазаема устройства, второй информационный вход местного устройства управления является третьим входом устрюйства, третий информационный вход соединен с первым выходом сумматоравычитателя, третий вход которого является четвертым входом устройства, а четвертый вход соединен с первым выходом управления местного устройства управления, второй выход управления которого соединен с управляющим входом триггера переноса-заема, третий выход, управления соединен с управляющим входом входного коммутатора, а четвертый выход управления соединен с управляющим входом выходного коммутатора, выход триггера результата является выходом нулевого результата устройства, введены блок свертки-контроля по модулю два входных операндов, блок контроля четности, триггер четности и блок свертки по модулю два результата, причем первый и второй входы блока свертки-контроля по модулю два входных операндов соединены соответственно с выходами первого и второго регистров операндов, первый выход этого блока является выходом ошибки устройства, а второй выход соединен с первым входом блока контроля-четности:,второй вход которого является пятым входом устройства, а третий вход блока контроля четности соединен с выходом триггера четности и является выходом устройства, первый вход триггера четности является шестьгм входом устройства, а второй вход триггера четности соединен с выходом генерации блока контроля-четности, выход контроля которого соединен с вторым входом триггера нулевого результата, вход блока свертки по модулю два результата соединен с выходом выходного коммутатора, а выход блока свертки по модулю два результата является выходом бита четности результата устройства и соединен с четвертым информационным входом местного устройства управления. Данное устройство позволяет реализовать оба метода кодозащиты без дополнительных программных затрат, возникающих при использовании устройства-прототипа в связном процессоре, и повысить производительность процессора. Кроме того, аппаратные затраты в данном/случае невелики, так как при выполнении операций (1) и (2) в значительной степени используется оборудование арифметическологического устройства-прототира.

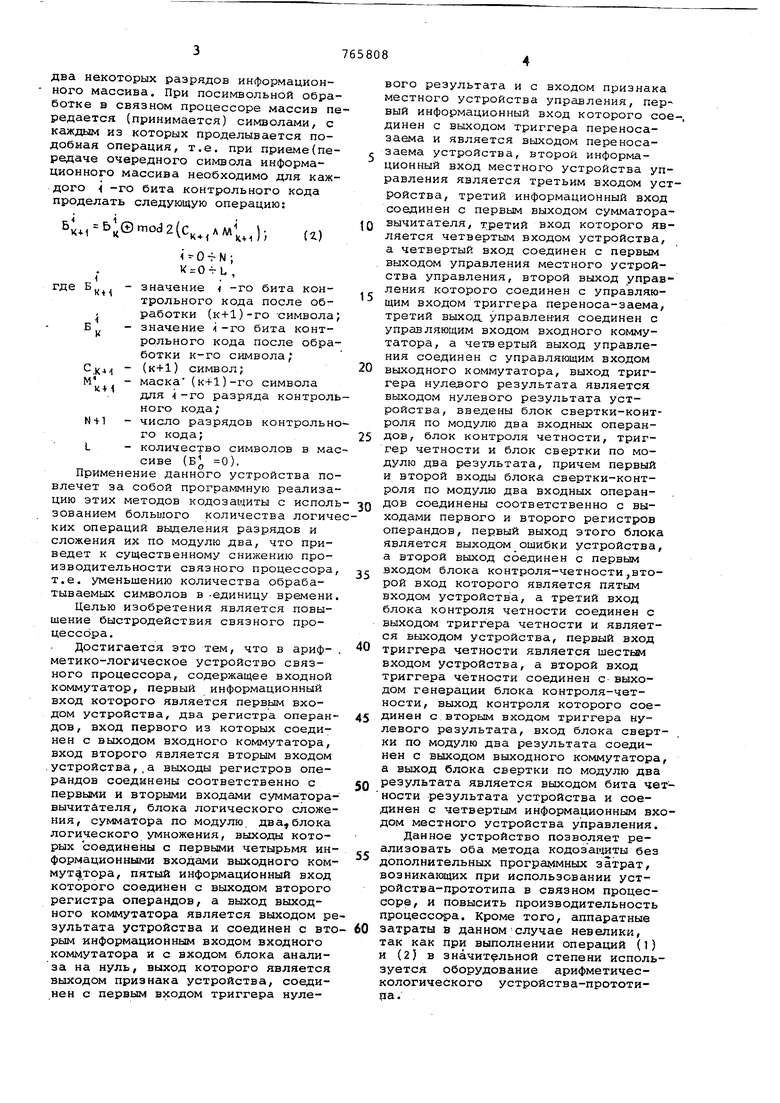

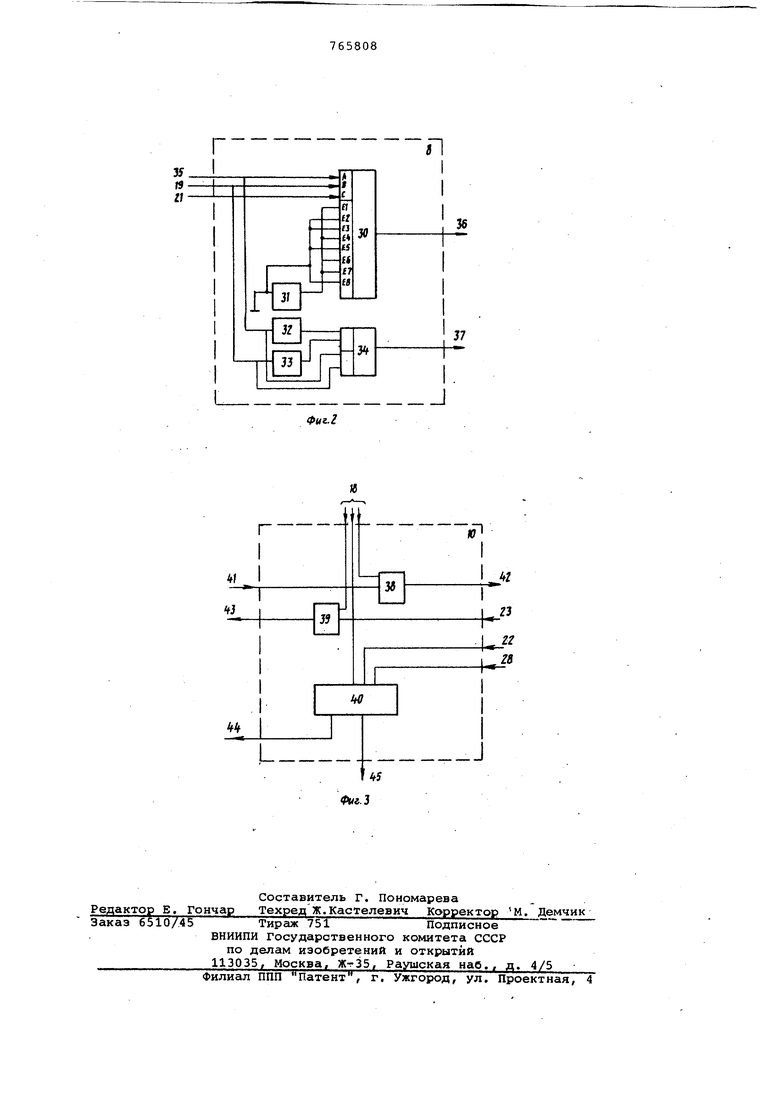

На фиг. 1 показана блок-схема фифметико-логического устройства ;;вязного процессора; на фиг,2 -блок контроля-четности; на фнг. 3 - блок местного устройства управления.

Устройство содержит регистры oneрандов 1 и 2, сумматор/вычитатель 3, блок 4 логического сложения, сумматор 5 по модулю два, блок 6 логичес.кого умножения, блок 7 свертки/контроля входных операндов по модулю два контролирующий входные операнды по четности и сворачивающий второй операнд (регистр 2) по модулю два, блок 8 контроля-четности, осуществляющий контроль или генерацию четности в соответствии с тождеством (1), вхоной коммутатор 9, местное устройство управления 10, выходной коммутатор 11, блок 12 анализа на нуль, триггер 13 четности, содержащий бит четности символа, принятый (передаваемый из) в лцнию связи, триггер 14 переноса/заема, триггер 15 нулевого результата, блок 16 свертки результата по модулю два, шины 17, 18 и 19 сигналов из центрального устройства управления процессором шины 20 и 21 сигналов из/в устройство сопряжения процессора с линиями связи, шину 22 сигнала признака нулевого операнда в централь нов устройство управления, шину сигнала переноса/зает4а 23 и нулевого результата 24 в центральное устройство управления, шины 25 и 26 входных операндов, шину 27 результата, шину 28 бита четноети результата, шину 29 сигнала оилибки приема входных операндов на входные регистры в устройство обработки прерываний. Блок 8 контроля четности, кроме того, содержит двоичный коммутатор 30, выбиракедий в зави- симости от кода на входах А,В,С один из восьми входов El + Е8 на инвертирующий выход, элементы НЕ 31, 32 и 33, элемент 2-2И-ИЛИ-НЕ 34, шину 35 сигнала свертки по модулю два операнда, шину контроля 36, шину генерации 37. Местное устройство управления, кроме того, содержит элементы 38 и 39, блок 40 сигналов управления ксялмутаторами, входную шину 41 переноса/заема, шину 42 управления триггером переноса/заема, выходную шину 43 переноса/раема, шины 44 и 45 управления входным и выходны коммутатором. Триггеры 13,14 и 15 являются программно доступньоми.

Устройство работает следующим образом. В первом такте происходит прием, входных операндов на регистры операндов 1 и 2 по шинам 25 и 26. В случае обнаружения ошибки njJkема блок 7 выдает сигнал ошибки 29 в устройство обработки прерываний процессора. Этот -контролБ.-. производится для всех операций, выполняемых устройством, и входные операнды

контролируются по постоянной внутренней четности процессора, отличающейся от четности на линии,где возможны различные типы четкостк. Во втором такте над входными операндами одновременно выполняются арифметические илогические действия и в зависимости от сигналов, поступающих по шинам 18, 22, 28, местное устройство управления 10, открывает соответствующий вход выходного коммутатора 11. Сигнал в шине 17 определяет реж1м работы сумматора-вычитателя 3 сложение или вычитанИе. Блок 16 вырабатывает бит четности результата,а блок 12 сравнивае результат с нулем.и по результату анпнза устанавливается триггер 15. Если выполняется арифметическая опера ция, то результат ее также отображается триггером 14. Устройство выполняет следугадие операции:

операция над операндами с разрядностью меньшей или равной разрядност входных шин. Эти операции заверииаются выдачей результата в выходную шину 27 с отображением его триггерами 14 и 15. Время выполнения - один так работы устройства;операции над операндами с разрядностью большей, чем разрядность входных шин, которые выполняются последовательно над 4acTHN3i операндов, причем такт выдачи промежуточного результата совмещен по вре.мени с приемом на входные регистры сле,цующей части входных олерандов, В случае возникновения переноса/заема в промежуточном результате (сигнал в ши-. не 41) местное устройство управления 10 по шине 42 устанавливает трйг гер 14, который затем участвует в последующей промежуточной операции .(сигнал в шине 43). Время выполнения тактов показывает во сколько раз длина операнда больше длины входного регистра;

операции, в которых промежуточный результат операции, полученный в i-м такте является входным операндом в (itO-OM такте операции. В этом случае прс 1ежуточный результат и его бит четности по ишнам 27 и 28 через ВХОДНОЙ коммутатор 9 .в 4-м такте пос:Тупает на регистр операндов 1;

условные операции/ результат которых зависит от анализа на нуль входного операнда или результата операции. В этом случав сигнал нуля поступает с выхода блока 12 в местное устройство управления 10, которое у31равляет вы :одным коммутатором 11 в последующих тактах работы (по шине 45); .

операция кодозащиты по методу контроля четности. При обработке символа, принятого из линии (контроль четности), данный символ поступает

из блока адресуемых регистров в первом такте работы устройства на регистр операндов 2 .ло шине 26. Во втором такте блок 7 сворачивает символ

по модулю два,а блок 8 в зависимости от результата свертки(шина 35), заданного -типа четности (шина 19) и значения триггера 13 (шина 21), содержащего принятый из линии бит четности да,нного символа, устанавливает в соответствии с тождеством (1) триггер 15 (шина 36). Программа, анализирующая триггер 15, делает заключение о правильности приема. При обработке символа, подлежащего передаче в линию, (генерация четности) во втором такте работы блок 8 в зависимости от результата свертки символа по модулю два (шина 35) и заданного типа четности (шина 19) устанавливает триггер 13 (шина 37)значение бита четности символа, подлежащего передаче в линию. В обоих случаях во втором такте работы содержимое регистра операндов 2, т.е.обрабатываемый символ, подается на выход устройства 27. Время выполнения и операции контроля, и операции генерации один такт работы устройства;

операция кодозащиты по методу Хэмминга.

Операция формирования одного разряда, контрольного кода выполняется в соответствии с выражением (2) следующим образом. В первом такте работ устройства на регистры операндов 1 и 2 поступают обрабатываемый символ и значение маски для данного разряда контрольного кода. Во втором такте работы устройства блок б выделяет разряды символа, которые складываются по модулю два блоком 16, и результат сложения подается в местное устройство управления 10 на блок 40. В том же такте на регистр операндов 2 поступает предыдущее значение накапливаемого контрольного кода, содержащего формируемый разряд, а на регистр операндов 1 - маска, содержащая единицу в разряде, соответствующем формируемому разряду в контрольном коде. Если текущее значение формируемого разряда контрольного кода, сформированного блоком 16 (шина 28), равно О, то необходимо составить контрольный код, без «зменений, и поэтому s третьем. такте блок 40 выбирает в шину результата 27 значение регистра операндов 2 i В противном случае производится сложение по модулю два содержимого регистров операндов 1 и 2 т.е. на выходную шину результата 27 выбирается выход сумматора 5 по модулю два. Для формирования всего контрольного кода необходимо зьшолнить набор подобных операций, количество которых равно количеству

разрядов коатрольного кода. Время выполнения операции формирования одного разряда контрольного кода равно двум тактам работы устройства.

Устройство позволяет эффективно реализовать в связном процессоре.оба метода кодозащиты. Поскольку задачи кодозащиты являются обязательными для связного процессора, то устройство позволяет существенно повысить производительность связного процессора, т.е. увеличить количество обрабатываемых символов в единицу времени, при небольших затратах оборудования - при выполнении операций кодозащить в значительной мере используется оборудование устройства-прототипа, а-введение схем свертки, т.е. средств аппаратного контроля, увеличивает надежность работы устройства и в конечном итоге также повышает производительность процессора.

Формула изобретения

Арифметико-логическое устройство связного процессора, содержащее входной коммутатор, первый информационный вход которого является первым входом устройства, два регистра операндов, вход первого из которых соединен с выходом входного коммутатора вход второго является вторым входом устройства, а выходы регистров операндов соединены соответственно с первыми и вторыми входами сумматоравычитателя, блока логического сложения, сумматора по модулю два, блока логического умножения, выходы которых соединены с первыми четырьмя информационными входами выходного ко1 мутатора,. пятый информационный вход которого соединен с выходом второго регистра операндов, а выход выходного коммутатора является выходсм результата устройства и соединен со вторым информационным входо входного коммутатора и со входом блока анализа на нуль, выход которого является выходом признака устройства, соединен с первым входом триггера нулевого результата и с входом признака местного устройства управления, первый информационный вход которого соединен с выходом триггера переноса-заема и является выходом переноса-заема устройства, второй информационный вход местного устройства управления является третьим входо устройства, третий информационный вход соединен с первым выходом сумматора-вычитателя, третий вход которого является четвертым входом устройства, а четвертый вход соединен с первым выходом управления (местного устройства управления, второй выход управления которого соединен с управ лякицйм входом три -ера переноса-заема, третий выход управления соединен с управляющим входом входного коммутатора, а четвертый выход управления соединен с управляющим входом выходного коммутатора, выход триггера нулевого результата является выходом нулевого результата устройства, отличающеес я тем, что/ с целью повышения быстродействия связного процессора, в него введены блок свертки-контроля по модулю два входных операндов, блок контроля-четности, триггер четности и блок свертки по модулю два результата, причем первый и второй входы блока свертки-контроля по модулю два входных операндов соединены соответственно с выходами первого и второго регистров операндов, первый выход этого блока является выходом ошибки устройства, а второй выход соединен с первым входом блока контроля-четности, второй вход которого является пятым входом устройства, а третий вход блока конт- роля четности соединен с выходом триггера четности и является выходом устройства, первый вход триггера четности является шестым входом устройства, второй вход триггера четности 5 соединен с выходом генерации блока контроля-четности, выход контроля которого соединен с вторым входом триггера нулевого результата, вход блока свертки по модулю два результата соединен с выходом выходного коммутатора, а выход блока свертки по модулю два результата является выходом бита четности результата устройства и соединен с четвертым информационным входом.местного устройства управления.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидет1вльство СССР 0 241108, кл. G Об F 7/38, .1968.

2.Патент США W 38110J9, кл. 235-175.

3. Патент США 3751650, ;кл. 235-175 (прототип).

Г

n

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Микропроцессор с контролем | 1981 |

|

SU1016788A1 |

| Ассоциативный матричный процессор | 1981 |

|

SU1005065A1 |

| Устройство для контроля двоичного кода на четность | 1981 |

|

SU989558A1 |

| Устройство для сдвига со встро-ЕННыМ КОНТРОлЕМ | 1979 |

|

SU809386A1 |

| РЕЗЕРВИРОВАННАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2039372C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ СОПРЯЖЕНИЕМ АБОНЕНТОВ | 1993 |

|

RU2037196C1 |

| Устройство для сдвига информации с контролем | 1983 |

|

SU1095184A1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| Устройство для контроля регистраСдВигА | 1979 |

|

SU842968A1 |

::I

Z

Авторы

Даты

1980-09-23—Публикация

1978-10-04—Подача