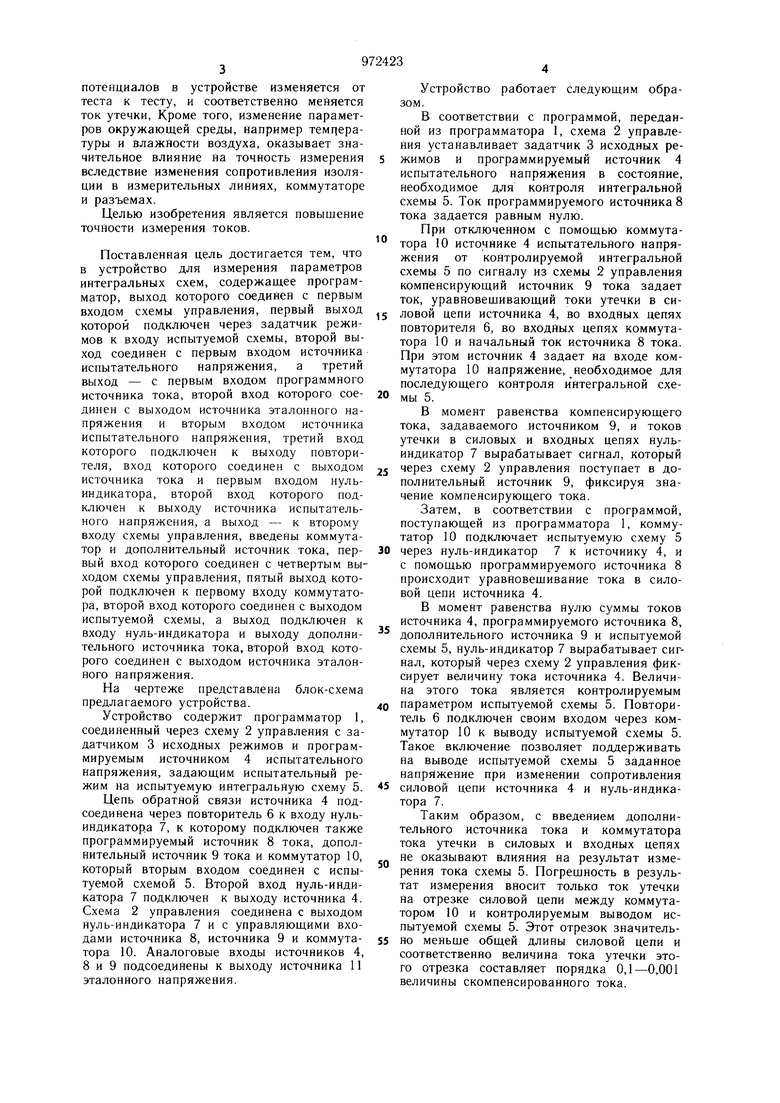

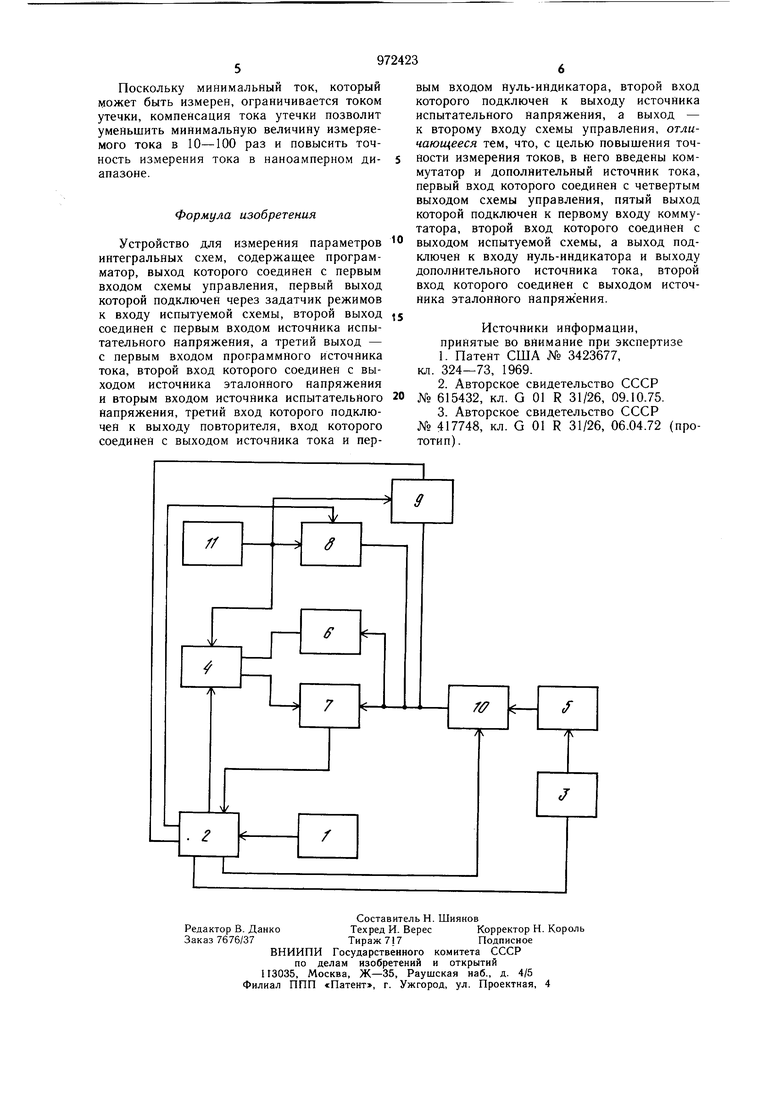

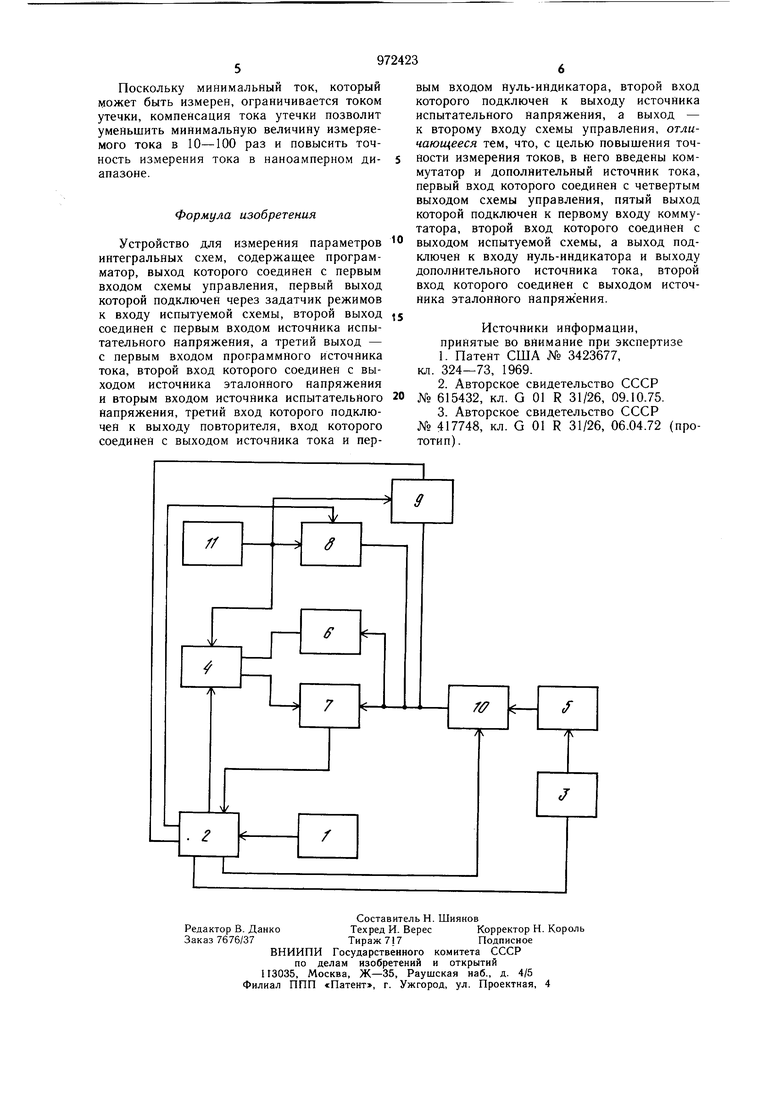

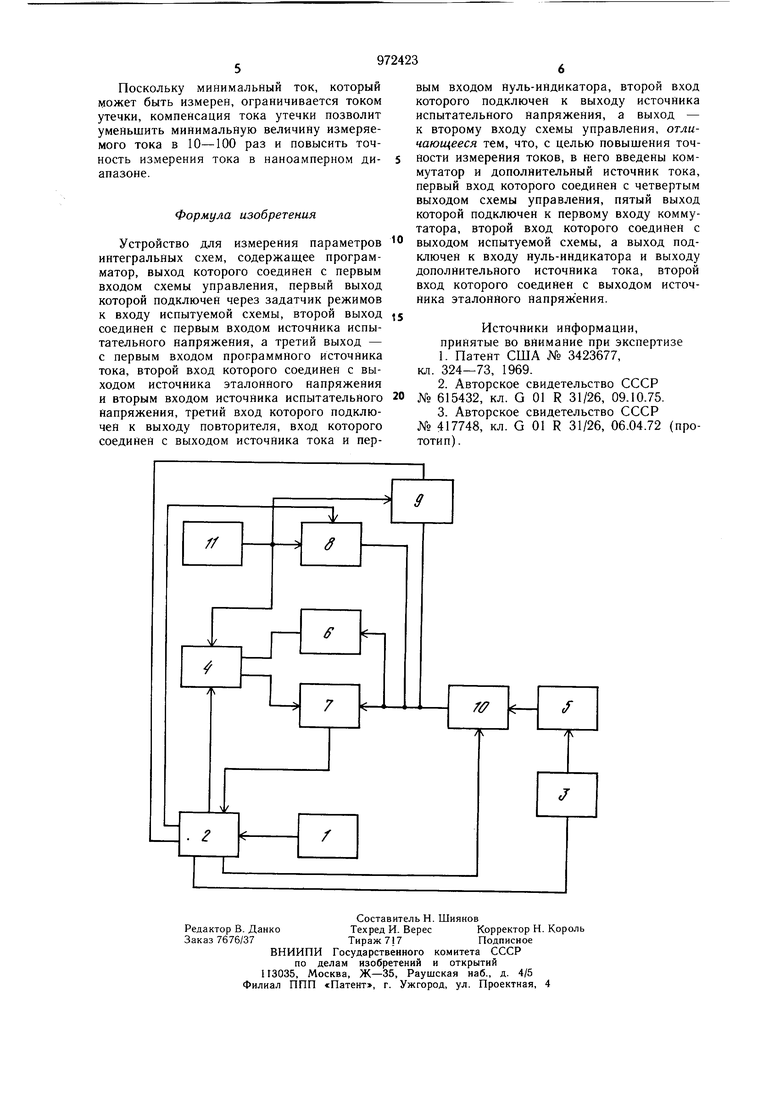

(54) УСТРОЙСТВО ДЛЯ ИЗМЕРЕР1ИЯ ПАРАМЕТРОВ ИНТЕГРАЛЬПЫХ СХЕМ Изобретение относится к электронной технике и может быть использовано для измерения параметров интегральных схем. Известно устройство для контроля параметров микросхем, содержащее программный источник напряжения, соединенный с генератором управляющего сигнала, регистратором, измерителем напряжения, коммутатором, а также через токосъемный резистор, снабженный схемой управления, с памятью и непосредственно с коммутатором, соединенным через измерительную линию с испытуемым прибором 1. Известно также устройство для контроля параметров микросхем, содержащее программный источник напряжения, соединенный с генератором управляющего сигнала, регистратором, измерителем напряжения, коммутатором, а также через токосъемный резистор, снабженный схемой управления, непосредственно с коммутатором, соединенным через измерительную линию с испытуемым прибором, последовательно соединенные генератор строб-сигнала, согласующий трансформатор и ключ, подключенные к генератору управляющих сигналов. а ключ подключен параллельно и к токосъемному резистору 2. Наиболее близким техническим рещением к изобретению является устройство для контроля параметров интегральных схем, содержащее программное устройство, схему управления, задатчик исходных режимов, источник напряжения с повторителем в цепи обратной связи, источник эталонного напряжения, программируемый источник тока, первый вход которого соединен со схемой управления, второй - с источником эталонного Напряжения, а выход через нульиндикатор связан с источником напряжения, входом подключенным к схеме управления, другой вход которой соединен с нуль-индикатором 3. Недостатком указанных устройств является неконтролируемость тока утечки в измерительных линиях и повторителе. Этот ток оказывает значительное влияние на точность измерения при использовании устройства в многопостовом комплексе контроля параметров интегральных схем. Учесть вклад тока утечки при начальной калиброке невозможно, поскольку распределение потенциалов в устройстве изменяется от теста к тесту, и соответственно меняется ток утечки, Кроме того, изменение параметров окружающей среды, например темцературы и влажности воздуха, оказывает значительное влияние на точность измерения вследствие изменения сопротивления изоляции в измерительных линиях, коммутаторе и разъемах. Целью изобретения является повышение точности измерения токов. Поставленная цель достигается тем, что в устройство для измерения параметров интегральных схем, содержащее программатор, выход которого соединен с первым входом схемы управления, первый выход которой подключен через задатчик режимов к входу испытуемой схемы, второй выход соединен с первым входом источника испытательного напряжения, а третий выход - с первым входом программного источника тока, второй вход которого соединен с выходом источника эталонного напряжения и вторым входом источника испытательного напряжения, третий вход которого подключен к выходу повторителя, вход которого соединен с выходом источника тока и первым входом нульиндикатора, второй вход которого подключен к выходу источника испытательного напряжения, а выход - к второму входу схемы управления, введены коммутатор и дополнительный источник тока, первый вход которого соединен с четвертым выходом схемы управления, пятый выход которой подключен к первому входу коммутатора, второй вход которого соединен с выходом испытуемой схемы, а выход подключен к входу нуль-индикатора и выходу дополнительного источника тока, второй вход которого соединен с выходом источника эталонного напряжения. На чертеже представлена блок-схема предлагаемого устройства. Устройство содержит программатор 1, соединенный через схему 2 управления с задатчиком 3 исходных режимов и программируемым источником 4 испытательного напряжения, задающим испытательный реЖИМ на испытуемую интегральную схему 5. Цепь обратной связи источника 4 подсоединена через повторитель 6 к входу нульиндикатора 7, к которому подключен также программируемый источник 8 тока, дополнительный источник 9 тока и коммутатор 10, который вторым входом соединен с испытуемой схемой 5. Второй вход нуль-индикатора 7 подключен к выходу источника 4. Схема 2 управления соединена с выходом нуль-индикатора 7 и с управляющими входами источника 8, источника 9 и коммутатора 10. Аналоговые входы источников 4, 8 и 9 подсоединены к выходу источника 11 эталонного напряжения. Устройство работает следующим образом. В соответствии с программой, переданной из программатора 1, схема 2 управления устанавливает задатчик 3 исходных режимов и программируемый источник 4 испытательного напряжения в состояние, необходимое для контроля интегральной схемы 5. Ток программируемого источника 8 тока задается равным нулю. При отключенном с помощью коммутатора 10 источнике 4 испытательного напряжения от контролируемой интегральной схемы 5 по сигналу из схемы 2 управления компенсирующий источник 9 тока задает ток, уравновещивающий токи утечки в силовой цепи источника 4, во входных цепях повторителя 6, во входных цепях коммутатора 10 и начальный ток источника 8 тока. При этом источник 4 задает на входе коммутатора 10 напряжение, необходимое для последующего контроля интегральной схемы 5. В момент равенства компенсирующего тока, задаваемого источником 9, и токов утечки в силовых и входных цепях нульиндикатор 7 вырабатывает сигнал, который через схему 2 управления поступает в дополнительный источник 9, фиксируя значение компенсирующего тока. Затем, в соответствии с программой, поступающей из программатора 1, коммутатор 10 подключает испытуемую схему 5 через нуль-индикатор 7 к источнику 4, и с помощью программируемого источника 8 происходит уравновешивание тока в силовой цепи источника 4. В момент равенства нулю суммы токов источника 4, программируемого источника 8, дополнительного источника 9 и испытуемой схемы 5, нуль-индикатор 7 вырабатывает сигнал, который через схему 2 управления фиксирует величину тока источника 4. Величина этого тока является контролируемым параметром испытуемой схемы 5. Повторитель 6 подключен своим входом через коммутатор 10 к выводу испытуемой схемы 5. Такое включение позволяет поддерживать на выводе испытуемой схемы 5 заданное напряжение при изменении сопротивления силовой цепи источника 4 и нуль-индикатора 7. Таким образом, с введением дополнительного источника тока и коммутатора тока утечки в силовых и входных цепях не оказывают влияния на результат измерения тока схемы 5. Погрешность в результат измерения вносит только ток утечки на отрезке силовой цепи между коммутатором 10 и контролируемым выводом испытуемой схемы 5. Этот отрезок значительно меньше общей длины силовой цепи и соответственно величина тока утечки этого отрезка составляет порядка 0,1-0,001 величины скомпенсированного тока. Поскольку минимальный ток, который может быть измерен, ограничивается током утечки, компенсация тока утечки позволит уменьшить минимальную величину измеряемого тока в 10-100 раз и повысить точность измерения тока в наноамперном диапазоне. Формула изобретения УСТРОЙСТВО для измерения параметров интегральных схем, содержащее программатор, выход которого соединен с первым входом схемы управления, первый выход которой подключен через задатчик режимов к входу испытуемой схемы, второй выход соединен с первым входом источника испытательного напряжения, а третий выход - с первым входом программного источника тока, второй вход которого соединен с выходом источника эталонного напряжения и вторым входом источника испытательного няппяжения третий вход которого подключен к выходу повторителя, вход которого соединен с выходом источника тока и первым входом нуль-индикатора, второй вход которого подключен к выходу источника испытательного напряжения, а выход - к второму входу схемы управления, отличающееся тем, что, с целью повышения точности измерения токов, в него введены коммутатор и дополнительный источник тока, первый вход которого соединен с четвертым выходом схемы управления, пятый выход которой подключен к первому входу коммутатора, второй вход которого соединен с выходом испытуемой схемы, а выход под- - ..тппя и выхолу ключен к входу нуль-индикатора и выходу дополнительного источника тока, второй вход которого соединен с выходом источника эталонного напряжения. Источники информации, принятые во внимание при экспертизе 1.Патент США № 3423677, кл. 324-73, 1969. 2.Авторское свидетельство СССР . ..„..----„ № 615432, кл. G 01 R 31/26, 09 Ш.75. 3. Авторское свидетельство СССР № 417748, кл. G 01 R 31/26, 06.04.72 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для автоматического контроля интегральных схем | 1983 |

|

SU1145311A1 |

| Устройство для автоматического контроля интегральных схем | 1986 |

|

SU1401418A2 |

| ПРЕОБРАЗОВАТЕЛЬ ТОК-КОД ДЛЯ КОНТРОЛЯ ИНТЕГРАЛЬНЫХ СХЕМ | 1972 |

|

SU420112A1 |

| Устройство для контроля параметров полупроводниковых приборов | 1978 |

|

SU781721A1 |

| Устройство для допускового контроля токов | 1983 |

|

SU1128224A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СОПРОТИВЛЕНИЯ ЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИИ | 2012 |

|

RU2501027C2 |

| Устройство для функционально-параметрического контроля логических элементов | 1982 |

|

SU1140065A1 |

| Устройство для контроля электрических параметров конденсаторов | 1989 |

|

SU1684729A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1987 |

|

SU1562864A1 |

| Устройство для контроля качества электрической изоляции | 2020 |

|

RU2730535C1 |

Авторы

Даты

1982-11-07—Публикация

1981-04-10—Подача