лируемого логического элемента, вторые входы коммутатора связаны через соответствующие первые и вторые формирователи логических уровней соответственно с выходами первого счетчика и дешифратора управляющие входы первых и вторых формирователей логических уровней соединены с соответствующими входными клеммами устройства.

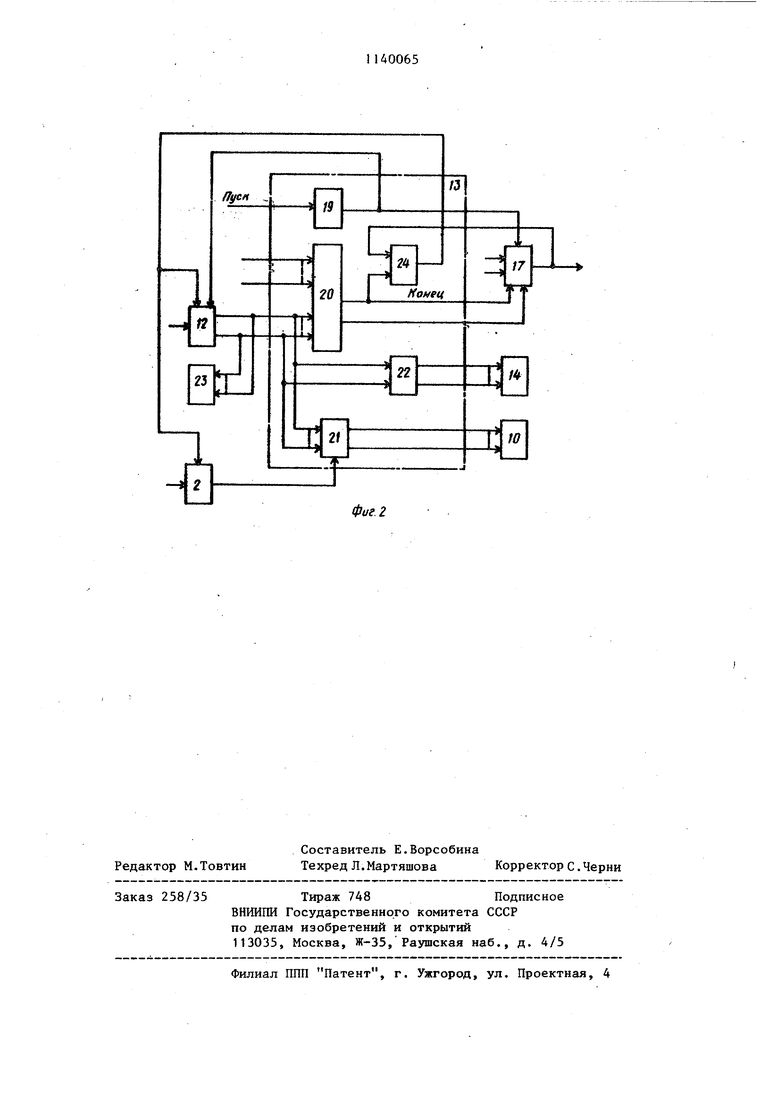

2. Устройство по П.1, отличающееся тем, что блок управ ления содержит формирователь сигнала сброса, формировлтель сигналов управления, формирователь импульсов записи, программатор источника питания, индикатор и элемент ИЛИ, выход которого соединен с одним из вторых выходов блока, первьй вход с пятым входом блока, второй вход с другим вторым выходом блока и первым вьгходом формирователя сигналов управления, второй выход которого соединен с четвертым выходом блока, первые входы - с четвертыми входами блока, а вторые входы с входамииндикатора и первыми входами блока, первая группа которых соединена с входами программатора источника питания, вторая группа - с информационными входами формирователя импульсов записи, синхровход которого соединен с вторым входом блока, а выходы - с третьим выходами блока, соединенного третьим входом с входом формирователя сигнала сброса, выход которого соединен с первым выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для функционально-параметрического контроля логических элементов | 1985 |

|

SU1302220A2 |

| Устройство для функционально-параметрического контроля логических элементов | 1982 |

|

SU1067453A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1987 |

|

SU1562864A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1332322A1 |

| Сигнатурный анализатор | 1987 |

|

SU1444776A1 |

| Устройство для обнаружения ошибок в блоке постоянной памяти | 1984 |

|

SU1246141A1 |

| Устройство для контроля цифровой аппаратуры | 1989 |

|

SU1735854A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1120338A1 |

| Система для контроля и диагностики цифровых узлов | 1988 |

|

SU1594544A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1539782A2 |

1. УСТРОЙСТВО ДЛЯ ФУНКЦИОНАЛЬНО-ПАРАМЕТРИЧЕСКОГО КОНТРОЛЯ ЛОГИЧЕСКИХ ЭЛЕМЕНТОВ, содержащее генератор импульсов, первьй счетчик, коммутатор, соединенный первыми входами с выходами первого счетчика, первыми выходами - с клеммами для подключения выводов контролируемого логического элемента, дешифратор, соединеиньй входами с вторыми выходами коммутатора, мультиплексор, соединенный информационными и адресныьш входами соответственно с третьими и четвертыми выходами коммутатора, и сигнатурньй анализатор, соединенный первым информационным входом с выходом мультиплексора, отличающееся тем, что, с целью повышения достоверности контроля, в устройство введены делитель частоты, второй и третий счетчики, первые и вторые формирователи логических уровней, RS -триггер, программируемый источник питания, датчик тока потребления, компаратор, анализатор неисправности, блок нагрузок и блок управления, соединенный первым выходом с установочными входами третьего счетчика и анализатора неисправности, вторыми выходами - с блокирующими входами делителя частоты, третьего счетчика и анализатора неисправности, третьими выходами - с информационными входами второго счетчика, четвертым выходом - со стробирующим входом анализатора неисправности, пятыми выходами - с управляющими входами программируемого источника питания, первыми входами - с выходами третьего счетчика, вторым входом с выходом -делителя частоты, счетным входом первого счетчика и S-входом RS-триггера, выход которого соединен с синхровходом сигнатурного анализатора н блокирующим входом второго счетчика, соединенсл ного выходом переполнения с R -входом RS-триггера, счетным входом с выходом генератора импульсов и счетным входом делителя частоты, пятые выходы коммутатора соединены с счетным входом третьего счетчика и старт-стопным входом сигнатурного и анализатора, выходы которого соединены с первыми информационными входами анализатора неисправности, вторые информационные входы - с шесо: тыми выходами коммутатора, соедисл ненного третьими выходами с входами блока нагрузок, седьмым выходом - с первым входом компаратора, . выход которого соединен с вторым информационным входом анализатора неисправности,а второй вход через датчик тока потребления - с общей шиной устройства и непосредственно - с одним выходом программируемого источника питания, соединенного вторым выходом с клеммой для подключения вывода питания контро

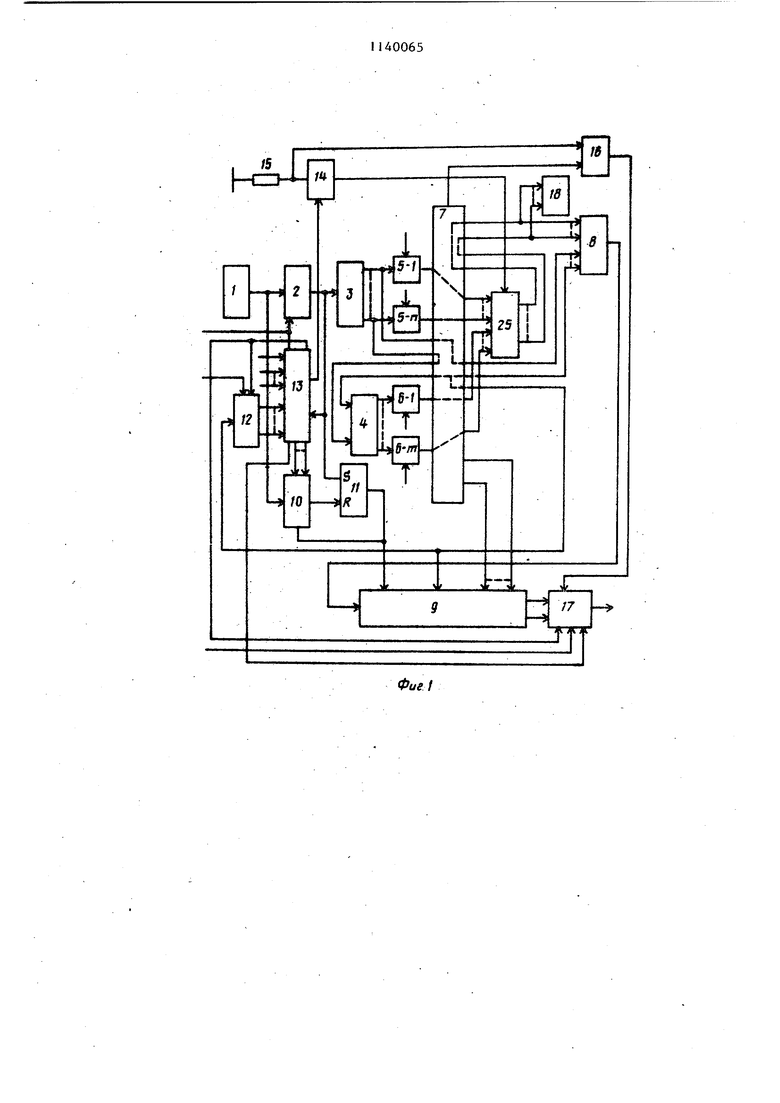

Изобретение относится к контрольно-измерительной технике и может быть использовано для контроля логических элементов, например, микросхем и плат с микросхемами. Известно устройство для контроля схем цифровых вычислительных .машин содержащее блок ввода, регистр задания и хранения информации, коммутатор, блок сравнения, компаратор, блок управления и блок эталонов О. Недостатки известного устройства его сложность и ограниченные функциональные возможности вследствие отсутствия динамического контроля. Наиболее близким техническим решением к изобретению является уст ройство для функционсшьно-параметри ческого контроля логических элементов, содержащее генератор импульсов первьй счетчик, коммутатор, соедине ньй первыми выводами с выходами пер вого счетчика, вторыми выводами с клеммг1ми для подключения выводов контролируемого логического элемента, дешифратор,, соединенньй входами с третьими выводами коммутатора, мультиплексор, соединенньй информационными и адресными входами соответственно с четвертыми и пятыми вывод ми коммутатора и сигнатурньй анализатор, соединенньй первым информационным входом с выходом мультиплексора 2 . Недостатком известного устройства является низкая достоверность контроля из-за невозможности контроля динамических параметров и тока потребления и невозможности автоматического изменения .напряжения питания в процессе -контроля. Цель изобретения - повышение до- стоверности контроля. Поставленная цель достигается тем, что в устройство для функционально-параметрического контроля логических элементов, содержащее генератор импульсов, первый счетчик, коммутатор, соединенньй первыми входами с выходами первого счетчика, первыми выходами - с клеммами для подключения выводов контролируемого логического элемента, дешифратор, соединенньй входами с вторыми выходами коммутатора, мультиплексор, соединенньй информационными и адресными входами соответственно с третьими и четвертыми выходами коммутатора, и сигнатурньй анализатор, соединенньй первым информационным входом с вьгходом мультиплексора, введены делитель частоты, второй И третий счетчики, первые и вторы формирователи логических уровней, RS-триггер, программируемый источни питания, датчик тока потребления, компаратор, анализатор неисправност блок нагрузок и блок управления, с диненный первым выходом с установоч ными входами третьего счетчика и анализатора неисправности, вторыми выходами. - с блокирующими входами делителя частоты, третьего счетчика и анали атора неисправности, третьими выходами - с информационными входами второго счетчика, чет вертым выходом - со стробирующим .входом анализатора неисправности, пятыми выходами - с управляющими входами программируемого источника питания, первь1ми входами - с выходами третьего счетчика, вторым входом - с выходом делителя частоты, счетным входом первого счетчика и S-входом RS-триггера, выход которого соединен с синхровходом сигнатурного анализатора и блокирующим входом второго счетчика, соединенного выходом переполнения с R-BXOдом RS-триггера, счетным входом с выходоч генератора импульсов и счетным входом делителя частоты, тые выходы коммутатора соединены с счётным входом третьего счетчика и старт-стопным входом сигнатурного анализатора, выходы которого соединены с первыми информационньти входами анализатора неисправности, вторые информационные входы - с шес тыми выходами коммутатора, соединенного третьими выходами с входами блока нагрузок, седьмым выходом - с первым входом компаратора, выход которого соединен с вторым информационным входом анализатора неисправ ности, а второй вход через датчик т ка потребления - с общей шиной устройства и непосредственно - с одним выходом программируемого источника питания, соединенного вторьм выходом с клеммой для. подключения в вода питания контролируемого логиче кого элемента, вторые входы коммутатора связаны через соотвётствукнци первые и вторые формирователи логических уровней соответственно с выходами первого счеучика и дешифратора, управляющие входы первых и вторых формирователей логических уровней соединены с соответствукнцими входными клеммами устройства. 65 Блок управления содержит формирователь сигнала сброса, формирователь сигналов управления, формирователь импульс.ов записи, программатор источника питания, индикатор и элемент ИЛИ, выход которого соединен с одним из вторых выходов блока, первый вход - с пятым входом блока, второй вход - с другим вторым выходом блока и первым выходом формирователя сигналов управления, второй выход которого соединен с четвертым выхо дом блока, первые входы - с четвертыми входами блока, а вторые входы с входами индикатора и первыми входами блока, первая группа которых соединена с входами программатора источника питания, вторая группа - с информационными входами формирователя импульсов записи, синхровход которого соединен с вторым входом блока, а выходы - с третьими выходами блока, соединенного третьим входом с входом формирователя сигнала сброса, выход которого соединен с первым выходом блока. На фиг.1 приведена структурная схема устройства5 на фиг.2 - структурная схема блока управления и связи его с другими блоками устройства. Устройство содержит генератор 1 импульсов, делитель частоты 2, первый счетчик 3, дешифратор 4, первые 5-1 - 5-п и вторые 6-1 - 6 - Нл формирователи логических уровней, коммутатор 7, мультиплексор 8, сигнатурный анализатор 9, второй счетчик 10, RS-триггер 11, третий счетчик 12, блок 13 управления, программируемый источник 14 питания, датчик 15 тока потребления, компаратор 16, анализатор 17 неисправности и блок нагрузок 18. Блок 13 управления содержит формирователь 19 сигналов сброса, формирователь 20 сигналов управления,формирователь 21 импульсов записи, программатор 22 источника питания, ивдикатор 23, элемент 24 ИЛИ и контролируемый логический элемент 25. Устройство работает следующим образом. Перед началом работы с помощью элементов коммутации, например перемьтек на сменном коммутаторе 7 и кнопочных переключателей, входящих в блок 13, задаются нeoбxoди в e для контроля данного типа логических элементов соединения блоков устройства, эталонная сигнатура, поступающая на вторые информационные входы анализатора 9, и граничное значение задержки распространения сигнала. Совместимые входы контролируемого логического .элемента 25 подключаются на коммутаторе 7 через формирователи 5 непосредственно к выходам счетчика 3, несовместимые входы (т.е такая группа входов, на которые, например, недопустимо подавать одновременно нуль), если они имеются, подключаются через формирователи 6 к выходам дешифратора 4. Если, например, количество информационных входов мультиплексора 8 2 (это значит, что количество адресных входов мультиплексора 2 и что количество выходов элемента 25 должно быть не более 2 ) и если кон кретный тип элемента 25 имеет i сов местимых входов, то при помощи коммутатора 7 входы элемента 25 через формирователи 5 можно подключить к первым i разрядам счетчика 3, адресные входы мультиплексора - к разрядам 1+1, i+2 - i + E, стартстопный вход сигнатурного анализатора 9 и счетный вход счетчика 12к одному и тому же разряду I + 8 + 1 того же счетчика. На коммутаторе 7 задается также граничное значение тока потребления элемента 25 по цепи питания, поступ ющее на первый вход коммутатора 16. Для пуска устройства на вход бло ка 13 подается сигнал, обеспечивающий через формирователь 19 сброс в исходное состояние анализатора 17 /неисправности и счетчика 12, в связ с чем С5 вторых выходов блока 13 (с выхода элемента 24 и второго выхода формирователя 20) на блокиру щие входы делителя частоты 2, счетчика 12 и анализатора 17 поступают си налы, разрешающие работу устройства После запуска по одному и тому же фронту каждого выходного импуль са делителя частоты 2 добавляется единица в счетчик 3, устанавливаетс в состояние 1 триггер 11 и строби руется формирователь 21, записывающий код, соответствуюЙ1Ий допустимому (граничному) значению задержки сигнала, в счетчик 10. 1 56 Изменением выходного кода счетчика 3 осуществляется полный перебор стимулирующих входных воздействий на входах элемента 25. Дешифратор 4 обеспечивает задание на несовместимые входы элемента 25 воздействий в необходимые по временной диаграмме моменты времени. Формирователи 5 и 6 формируют необходимые уровни входных сигналов для элемента 25 в зависимости от управляющих сигналов на их входах. Если ко входам логического элемента 25 подключены i младших разрядов счетчика 3, полньй цикл стимуляции элемента 25 составляет 2 различных воздействий. При этом в первом цикле стимуляции на выходах разрядов 1+1, i+2 - i + счетчика 3 поступает логический ноль, в связи с чем, на адресные входы мультиплексора 8 поступает код 00-0, что приводит к подключению первого выхода элемента 25 ко входу анализатора 9. При последующих циклах, стимуляции код, поступающий на адресные входы мультиплексора 8, возрастая каждый раз на единицу, принимает все значения от 00-01 до 11-1, что приводит к последовательному подключению всех выходов элемента 25 ко входу сигнатурного анализатора 9. Полученный таким образом на входе анализатора 9 последовательньй код по заднему фронту импульса, поступающего на синхровход с выхода триггера 11, преобразуется в анализатор 9 в шестнадцатиразрядную двоичную сигнатуру, характеризующую все выходы элемента 25 по всем входным воздействием. Количество циклов стимуляции элемента 25, определяемое продолжительностью окна (логического нуля) на старт-стопном входе анализатора 9, подключенном к разряду L+t+l счетчика 3, при этом, не меньше числа выходов элемента 25. Положение заднего фронта синхроимпульса определяется кодом, записываемым в счетчик 10, и задается при каждом очередном воздействии срабатыванием триггера 11 и счетчика 10. Этим обеспечивается контроль задержки распространения сигнала элемента 25 следующим образом, Одновременно с добавлением единицы в счетчик 3 дополнительный код допустимой задержки записывается в счетчик 10, а триггер 11 устанавливается в состояние 1. До тех пор. пока на блокирующий вход счетчика Ю 1, счетчик 10 счи поступает сигнал тает импульсы, поступающие на его вход от генератора 1, дополняя код, записанный в счетчик 10. По импульсу переполнения счетчика 10 триггер 11 переключается в состояние О, в связи с чем счетчик 10 останавливается. Перекодом выходного сиг нала триггера 11 из состояния 1 в состояние О разрешается (синхронизируется и стробируется) работа анализатора 9. Если за время дополнения счетчика 10 до максимального кода злемента 25 не успел сформировать на своем выходе соответствующий данному входному воздействию логический уровень, т.е. он не годен по быстродействию, то сигнатура, пол ченная в анализаторе 9, не совпадает с зталонной. Указанная последовательность работы обеспечивает функциональный контроль и контроль задержки распространения до заданному пределу допу тимых значений последовательно по каждому выходу элемента 25 для каждо го входного воздейсГтвия. . После получения первой суммарной сигнатуры элемента 25 по всем его выходам сигнал, поступающий с разряда i + Е + 1 счетчика 3 на старт стопный вход анализатора 9, изменяется с логического нуля на единицу. В результате формирователь сигнатур анализатора 9 останавливается, полученная сигнатура сравниваетс с эталонной и переписывается из формирователя сигнатур в регистр индикации, после чего автоматически формирователь сигнатур сбрасывается. Когда на старт-стопном входе анализатора 9.и счетном входе счетчика 12 появляется вновь логический нуль, в счетчик 12 добавляется единица h начинается новый дакл работы устройства формируется новая сигнатура, которая при состоянии t на старт-стопном входе, в анализаторе 9 сравнивается с зталонной сигнатурой. Результат сравнения поступает на первый информационный вход анализ.атора 17 неисправности, который, в случае нераренства указанных сигнатур, по стробирукнцему сигналу, поступакицему с четвертого выхода 1 58 блока 13, вьщает сигнал Брак на индикацию, на выход устройства и на элемент 24 блока 13. Сигнал Брак через элемент 24 передается на блокирующие входы делителя 2 и счетчика 12 останавливая дальнейшую работу устройства. После многократного повторения цикла получения сигнатуры элемента 25, которое производится для повыщения достоверности результата контроля, когда выходной код счетчика 12 будет равен заданному коду, на втором выходе формирователя 20, настроенном на этот код, появляется сигнал Конец, останавливающий через элемент 24 делитель 2 и счетчик 12 и разрешающий анализатору 17 выдать сигнал Годен на индикацию и выход устройства. Код допустимой задержки распространения сигнала в злементе 25, записываемый из формирователя 21 в счетчик 10, может быть сформирован, например кнопочным переключателем, входящим в состав формирователя 21, или формироваться (различной величины) в соответствии с выходным кодом счетчика 12. В последнем случае Тгмеется возможность измерения задержки распространения сигналов в элемен-. jre 25, так как величина этого кода может уменьшаться от одного цикла получения сигнатуры к другому до тех пор, пока анализатор 17 не даст ре- зультат Брак. При этом код измеренной величины задержки высвечивается .индикатором 23. Возможность записи кода допустимой задержки в счетчик 10 в зависимости от кода счетчика 12, при соответствующей коммутации старт-стопного входа;, анализатора 9 и счетного входа счетчика 12 к выходам счетчика 3, позволяет осуществить контроль задержки по каждому выходу элемента 25 в отдельности с заданием собственных допустимых значений задержки. Предлагаемое устройство обеспечивает в процессе получения каждой очередной сигнатуры в анализаторе 9 изменение напряжения питания элемента 25. Величина напряжения п1 тання задается в том или ином цикле в зависимости от выходного кода счетчика t2, в соответствии с которым программатор 22 задает соответствукяцие сигналы на управляюпще входы програ мируемого источника питания 14. При изменении напряжения питания контролируется ток потребления элемента 25. Для этого используется ко паратор 16, сравниваняций величину тока, поступающую с датчика 15, ..с граничным значением, заданным на ко мутаторе 7. Если ток, потребляемьй элементом 25, превысит заданньй уровень, компаратор 16 вьщает .сигна негодности на анализатор 17 формирующий сигнал Врак, останавливакмдий устройство и индицирующий признак негодности по току потребления. Так как входы программатора 22 подключены к группе выходов счетчика 12, индикатор 23 при этом показывает, при каком напряжении питания ток потребления превысил за данное граничное значение. Для повторного пуска устройства необходимо через формирователь 19 осуществить сброс анализатора 17 и счетчика 12. Блок нагрузок обеспечивает нагрузку выходов элемента 25 до номинальной величины. 510 Целесообразно для каждого типа контролируемых логических элементов изготовить сменный коммутатор. В качестве сменного коммутатора может быть применена ответная часть многоконтактного разъейа с перемычками. Для каяяой группы логических элементов, выходные параметры которых одинаковы (например серия микросхем) , целесообразно изготовить cMeHHi блок нагрузок. 1 Предлагаемое устройство позволяет одновременно с контролем функционирования осуществлять контроль задержки распространения сигналов и тока потребления логического элемента при различных нагрузках и уровнях входных сигналов и изменяющемся от цикла к циклу напряжении питания. Все это существенно повьшает достоверность контроля. При помощи предлагаемого устройства возможен также контроль задержки распространения сигналов при автоматически изменяющемся допуст 1мом (пороговом) значении задержки распространения сигнала, что позволяет не только контролировать, но и измерять задержку.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| УСТРОЙСТВО для КОНТРОЛЯ СХЕМ ЦИФРОВЫХ ВЫЧИСЛИТЕЛЬНЫХ МАШИН | 0 |

|

SU378852A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для функционально-парамет-РичЕСКОгО КОНТРОля лОгичЕСКиХэлЕМЕНТОВ | 1979 |

|

SU830391A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-02-15—Публикация

1982-07-19—Подача