которого соединен с общей шиной, первый ВЫТ5ОД запоминающего конденсатора соединен с входом второго повторителя, выход которого через четвертый ключ и суммирующий резистор соединен с третьим входом компаратора,ч а управляющие входы третьего и четвертого ключей подключены к седьмому и восьмому выходам задатчика кодов и команд.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для автоматического контроля интегральных схем | 1986 |

|

SU1401418A2 |

| Устройство для измерения параметров интегральных схем | 1981 |

|

SU972423A1 |

| Устройство для допускового контроля токов | 1983 |

|

SU1128224A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ЭЛЕКТРИЧЕСКОГО СОПРОТИВЛЕНИЯ ТОЧЕК АКУПУНКТУРЫ | 1992 |

|

RU2027403C1 |

| Устройство для контроля интегральных схем | 1985 |

|

SU1290522A1 |

| Устройство для автоматического контроля интегральных схем | 1987 |

|

SU1471155A2 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| Устройство автоматизированного контроля | 1987 |

|

SU1525680A2 |

| Устройство для измерения порогового напряжения полевых транзисторов | 1981 |

|

SU1064241A1 |

| Устройство для контроля параметров электронных схем | 1982 |

|

SU1112324A1 |

УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО КОНТРОЛЯ ИНТЕГРАЛЬНЫХ СХЕМ, содержащее программируемый источник напряжения, первый повторитель, измерительный резистор, инвертор, сумматор, источник граничных значений, источник опорного напряжения, компаратор, коммутатор, блок подключения, задатчик кодов и команд, при этом первый вход программируемого источника напряжения подключен к выходу источника опорного напряжения, а его выход - к первому вьтоду измерительного резистора, второй вьшод которого через последовательно соединенные первый ключ коммутатора и первый ключ блока подключения соединен с клеммой для подключения выводов контролируемой схемы, к которой через последовательно соединенные второй ключ блока подключения и второй ключ коммутатора подключен вход первого повторителя, выход которого соединен с вторым входом программируемого источника напряжения и с входом инвертора, выход которого подключен к первому входу сумматора, второй вход которого соединен.с выходом программируемого источника напряжения, а выход - с первым входом компаратора, второй вход которого соединен с выходом источника граничных значений, вход которого подключен к выходу источника опорного напряжения, а вьпсод компаратора соединг н с выходом устройства, первая группа выходов задатчика кодов и команд соединена с управляющими входами клю чей блока подключения, вторая группа выходов задатчика кодов и команд соединена с управляющими входами ключей коммутатора, третья группа выходов задатчика кодов и команд соединена с управлякяцим входом измерительного резистора, четвертая группа выходов задатчика кодов и команд соединена с управлянщими входами программируемого источника напряжения, пятый выход задатчика кодов и команд соединен с входом источника опорного напряжения,шестая группа выходов задатчика кодов и команд соединена 4 О1 с управляющими входами источника граничных значений, отличаюСО щееся тем, что, с целью повышения точности контроля параметров, в него введены инвертирующий усилитель, второй повторитель, входной резистор, резистор обратной связи, суммирующий,резистор третий и четвертый ключи, запоминающий конденсатор, причем вход инвертирующего усилителя через входной резистор соединен с выходо сумматора и через резистор обратной связи - с выходом второго повторителя, а,выход через третий ключ - с первьм выводом запоминающего конденсатора, второй вывод

Изобретение относится к электронной технике и может быть использовано для кс5нтроля параметров интегральных схем, в частности для контроля статических параметров КМОПгструктур

Известно устройство для контроля параметров микросхем, содержащее программный источник напряжения, соединенньй с генератором управляющего сигнала, регистратором, измерителем напряжения, коммутатором, а также через токосъемный резистор, снабженньШ схемой управления, с памятью и непосредственно с коммутатором, соединенным через измерителькую линию с испытуемым прибором, последовательно соединенные генератор строб-сигнала, согласующий трансформатор и ключ, подключенные к генератору управляющих сигналов LO .

Недостатком устройства является низкая точность контроля параметров интегральных схем.

Наиболее близким к предлагаемому по техническому решению является тестер статических параметров интегральных схем, содержащий программируемый источник напряжения, повторитель-, измерительный резистор, ин вертор, сумматор, источник граничных значений, источник опорного напряжения, компаратор, коммутатор, блок подключения, блок управления и контролируемую микросхему, причем первый вход программируемого источника напряжения подключен к выходу источника опорного напряжения, выход - к первому выводу измерительного резистора, второй вывод которого через последовательно соединенные первый ключ коммутатора и первый ключ блока подключения соединен с выводом контролируемой микросхемы, к которой чеРез последовательно соединенные второй ключ блока подключения и второй ключ коммутатора подключен вход повторителя, выход которого подключен к второму входу программируемого источника напряжения и к входу инвертора, выход которого подключен к первому входу сумматора, второй вход которого подключен к выходу программируемого источника напряжения, а выход к первому входу компаратора, второй вход которого подключен к выходу источника опорного напряжения, а выход компаратора является выходом устройства, при этом выходы блока управления подключены к соответствующим управляющим входам программируемого источника напряжения, измерительного резистора, коммутатора, блока подключения и источника граничных значений С2.

Недостатком устройства является значительная, не поддакмцаяся учёту, погрешность измерения токов в наноамперном диапазоне, определяемая токами утечки в. измерительных линиях и блоках устройств. Токи утечки и, соответственно, погрешности контроля и измерения токов изменяются при изменении параметров окружающей средЫ и режима устройства, что не позволяет учесть их при калибровке устройст

Целью изобретения является повышение точности контроля параметров.

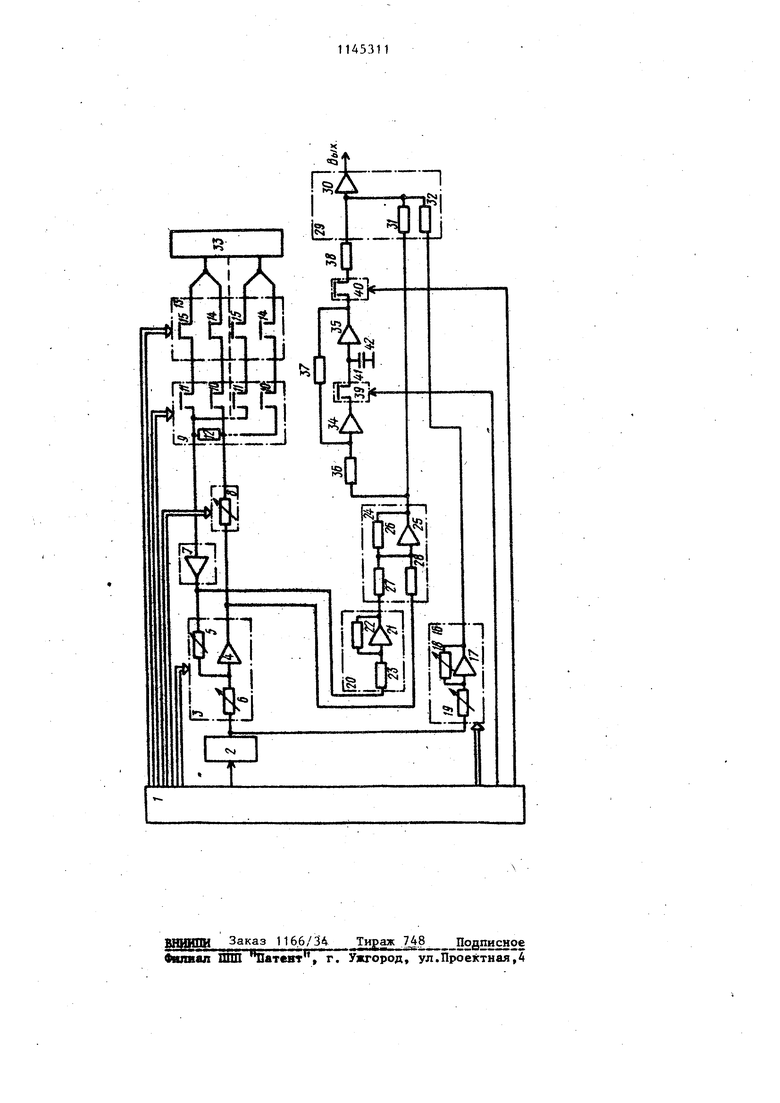

Поставленная цель достигается тем, что в устройство, содержащее программируемыйисточник напряжения, первый повторитель, измерительный резистор, инвертор, сумматор, источник граничных значений, источник опорного напряжения, компаратор, коммутатор, блок подключения, задатчик кодов и команд, при этом первый вход программируемого источника напря ения подключен к выходу источника опорного напряжения, а его выход к первому выводу измерительного резистора, второй вывод которого через последовательно соединенные первый ; ключ коммутатора и первый ключ блока подключения соединен с клеммой для подключения выводов контролируемой схемы, к которой через последователь но соединенные второй ключ блока подключения и второй ключ коммутатора подключен вход первого повторителя, выход которого соединен с вторым .входом программируемого источника напряжения и с входом инвертора, выход которого подключен к первому входу сумматора, второй вход которого соединен с выходом программируемого источника напряжения, а выход - с первым входом компаратора, второй вход которого соединен с выходом источника граничных значений, вход которого подключен к выходу источника опорного напряжения, а выход компаратора соединен с выходом устройства, первая группа выходов задатчика кодов и команд соединена с управляющими входами ключей блока подключения,вторая группа выходов задатчика кодов и команд соединена с управляющими входами ключей коммутатора, третья группа выходов задатчика кодов и команд соединена с уш равляющим входом измерительного резистора, четвертая группа выходов задатчика кодов и команд соединена с управляющими входами программируемого источника напряжения, пятый выход задатчика кодов и команд соединен с входом источника опорного напряжения, шестая группа выходов задатчика кодов и команд соединена с управляющими входами источника граничных значений, введены инвертирующий усилитель, второй повторитель входной резистор, резистор обратной ;связи, суммируюций резистор, третий и четверть ключи, запоминающий конденсатор, причем вход инвертирующего усилителя через входной резистор соединен с выходом сумматора и через резистор обратной связи - с выходом второго повторителя, а выход через третий ключ - с первым вьшодом запоминающего конденсатора, второй вывод которого соединен с общей,шиной первый вывод запоминающего .конденсатора соединен с входом второго повторителя, выход которого через чет 114 вертый ключ и суммирующий резистор соединен с третьим входом компаратора, а управляющие входы третьего и четвертого ключей подключены к седьмому и восьмому выходам задатчика кодов и команд. На чертеже представлена блок-схема устройства. Устройство содержит задатчик 1 кодов и команд, источник 2 опорного напряжения, подключенный к первому входу программируемого источника 3 напряжения, который предназначен для задания испытательного напряжения и содержит инвертирующий усилитель 4 и резисторы 5 и 6, определяющие коэффициент передачи, первый повторитель 7, подключенный к цепи обратной связи программируемого источника 3 напряжения, измерительный резистор 8, коммутатор 9, содержащий первые 10 и вторые 11 ключи и резистор 12. Коммутатор 9 предназначен для передачи испытательного напряжения на соответствующий вывод блока 13 подключения, содержащего первые 14 и вторые 15 ключи. Источник 16 граничных значений, вход которого соединен с выходом источника 2 опорного напряжения, вьфабатывает напряжение, соответствующее граничному значению поля допуска контролируемого тока, и включает в себя усилитель 17 и резисторы 18 и 19, определяющие коэффициент передачи. Инвертор 20, содержащий усилитель 21 и равные по величине резисторы 22 и 23, подключен к сумматору 24, содержащему усилитель 25, резистор 26 обратной связи и суммирукмцие резисторы 27 и 28. Компаратор 29, первый вход которого соединен с выходом сумматора 24, второй вход - с выходом источника 16 граничных значений, третий вход с суммирующю резистором 28, предназначен для сравнения поступающих на входы напряжений и содержит усилитель 30 и резисторы 31 и 32. К блоку 13 подключения подсоединена контролируемая микросхема 33. Устройство содержит также инвертирукндий усилитель 34, второй повторитель 35, входной резистор 36, резистор 37 обратной связи, суммирующий резистор 38, первый 39 и второй 40 ключи, запоминающий конденсатор 41, общую шину 42, причем запомина511

ющий конденсатор 41 подключен через i второй повторитель 35 и второй ключ 40 к суммирующему резистору 38 и через первый ключ 39 - к входу инвертирующего усилителя 34,

Задатчик 1 обеспечивает требуемые режимы работЫ устройства (выбор необ ходимого коэффициента передачи программируемого источника напряжения и необходимой величины измерительного резистора, включение необходимых ключей коммутатора и блока подключения), для чего вырабатьрает соответствующие коды. Кроме того, задатчик 1 обеспечивает необходимую последовательность включения источника опорного напряжения и источника граничных значений, для чего вырабатывает соответствующие команды.

Устройство работает следующим образом.

Процесс контроля состоит из двух этапов.

Первый этап. По команде из задатчика 1 кодов и команд программируемьй источник 3 напряжения устанавливает необходимое напряжение на выходе с помощью источника 2 опорного напряжения и резисторов 5 и 6. Полученное напряжение через измерительньй резистор 8 и замкнутые, контакты первого ключа 10 коммутатора 9 поступает в измерительную линию (на входе блока 13 подключения). Отрицательная обратная связь с вывода измерительного резистора 8 через резистор 12 коммутатора 9 и повторитель 7 на второй вход программируемого источника 3 напряжения (резистор 5) обеспечивает компенсацию падения напряжения на измерительном резисторе 8. Через измерительный резистор 8 при этом протекает ток утечки в измерительной линии, коммутаторе 9, цепях обратной связи (связь второго ключа 15 блока 13 подключения с входом повторителя 7 через второй ключ 11 коммутатора 9) и повторителе 7. Падение напряжения на измерительном резисторе 8, пропорциональное току утечки, вьщеляетсясумматором 24 с помощью инвертора 20, При этом на первьлй вход сумматора 24 (суммирующий резистор 27) поступает напряжение с выхода повторителя 7 через инвертор 20, выполненный на базе усилителя 21 с единичным коэффициентом усиления, определяемым резис116

торами 22 и 23, На второй вход сумматора 24 (суммирующий резистор 28) поступает напряжение с выхода программируемого источника 3 напряжения. Коэффициент передачи сумматора 24 определяется резистором 26 обратной связи. Вьщеленное напряжение с выхода сумматора 24 поступает на запоминающий конденсатор 41 через входной резистор 36, инвертирующий усилитель 34 и замкнутые контакты первого ключа 39. Запоминающий конденсатор 41 подключен к входу второго повторителя 35 с вЬюокоомным входом. Напряжение на запоминающем конденсаторе 41 под действием отрицательной обратной связи, образованной резистором 37 обратной связи, устанавливается таким, что на выходе второго повторителя 35 появляется напряжение, равное напряжению на выходе сумматора 24, но с противоположным, знаком. Равенство напряжений обеспечивается равенством величин сопротивлений резистора 37 обратной связи и -входного резистора 36 Таким образом, на выходе второго повторителя 35 присутствует напряжение, пропорциональное току утечки, Второй ключ 40 разомкнут, при этом на вход компаратора 29 (резистора 31) поступает напряжение с выхода сумматора 24, пропорциональное току утечки, а с выхода источника 16 граничных значений - напряжение, йоответствуняцее максимально допустимому току утечки. Необходимое напряжение на выходе источника 16 граничных значений устанавливается резисторами 18 и 19 по команде задатчика 1 кодов и команд спомощью источника 2 опорного напряжения.

Затем по команде из задатчика 1 кодов и команд первый ключ 39 размыкаетсй, а запоминающий конденсатор 4 поддерживает на выходе второго повторителя 35 напряжение, соответствующее току утечки,

Второй этап. По команде задатчика 1 кодов и команд замыкаются первый 14 и второй 15 ключи блока 13 подключения, и испытательное напряжение с выхода программируемого источника 3 напряжения через измерительный резистор 8, коммутатор 9 и блок 13 подключения поступает на вход контролируемой микросхемы 33, При этом через измерительный резистор 8

711

протекает сумма токаутечки и тока контролируемой микросхемы 33. Падение напряжения на измерительном резисторе 8 выделяется сумматором 24 с помощью инвертора 20 и поступает на второй вход компаратора 29 (резистор 31), а также на входной резистор 36 i При этом на первый вход компаратора 29 через суммирукиций резистор 38 и замкнутый по команде задатчика 1 кодов и команд второй ключ 40 поступает напряжение, соответствующее инвертированному току утечки, а на третий вход компаратора 29 (резистора 32) поступает напряжение с выхода источника 16 граничных значений, соответствующее граничному значению тока контролируемой микросхемы 33. В этом случае сумма сравниваемых на компараторе 29 напряжений равна сумме напряжений на входах

и и, Uj + Uj, - (1)

где Ui - напряжение на разисргоре38;

Uj - напряжение на резисторе31;

Uj - напряжение на резисторе32 граничных значений.

Уравнение (1) можно записать в виде i

и -1,К R е + (1,,+ I) KR-Uj (2)

где 1у - ток утечки;

R - сопротивление измерительного резистора 8;

t - длительность измерения;

f - постоянная времени разряда запоминающего коИденсатора 41;

К - коэффициент пропорциональности;

3 - контролируемый ток микросхемы 33.

Из (2) следует, что без учета погрешности коэффициента передачи с выхода сумматора 24 на выход второго повторителя 35 погрешность измерения, определяемая током утечки, определяется постоянной времени разряда запоминающего конденсатора 41 и составляет .

AI 7sj R К(1 (3)

)

J-А

Например, если Т, 10 нА, г 10с t 0,1 с, то из (3) следует

и 0,1 нА

т.е. погрешность измерения, определяемая током утечки, снизилась в 100 раз.

Предполагаем, что ток утечки на первом и втором этапах измерения одинаков. Такое предположение обосновано, поскольку второй этап измерения следует непосредственно за первым этапом, то тепловой режим и влажность, обусловленные окружающей средой и внутренним состоянием устройства, практически не изменяются. Неуча енный ток утечки в отрезке линии от блока 13 подключения до контролируемой микросхемы 33 на порядок меньше общего тока утечки и на погрешность измерения не влияет.

Таким образом, предлагаемое устройство позволяет на несколько порядков уменьшить погреЬгность измерения, вносимз ю токами утечки при изменяющихся внутреннем состоянии устройства и пдраметрах окружающей среды.

П

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля параметров микросхемы | 1975 |

|

SU615432A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| ЭЛЕКТРИЧЕСКАЯ ЛАМПА НАКАЛИВАНИЯ С РЕФЛЕКТОРОМ ВНУТРИ КОЛБЫ | 1926 |

|

SU4502A1 |

Авторы

Даты

1985-03-15—Публикация

1983-02-04—Подача