ES

розрешемае

{Детм

, WIMff

гг

OHffJita

00

гз

14)

Изобретение относится к электронной технике и может быть использовано для контроля параметров интегральных схем, в частности для допускового контроля статических параметров интегральных схем КМОП-структур,и является усовершенствованием устройства по авт. св. fP 1145311.

Цель изобретения - повышение быст- родействия допускного контроля входного тока КМОП-структур за счет проведения контрольных замеров при неуставившемся режиме работы измерительной цепи.

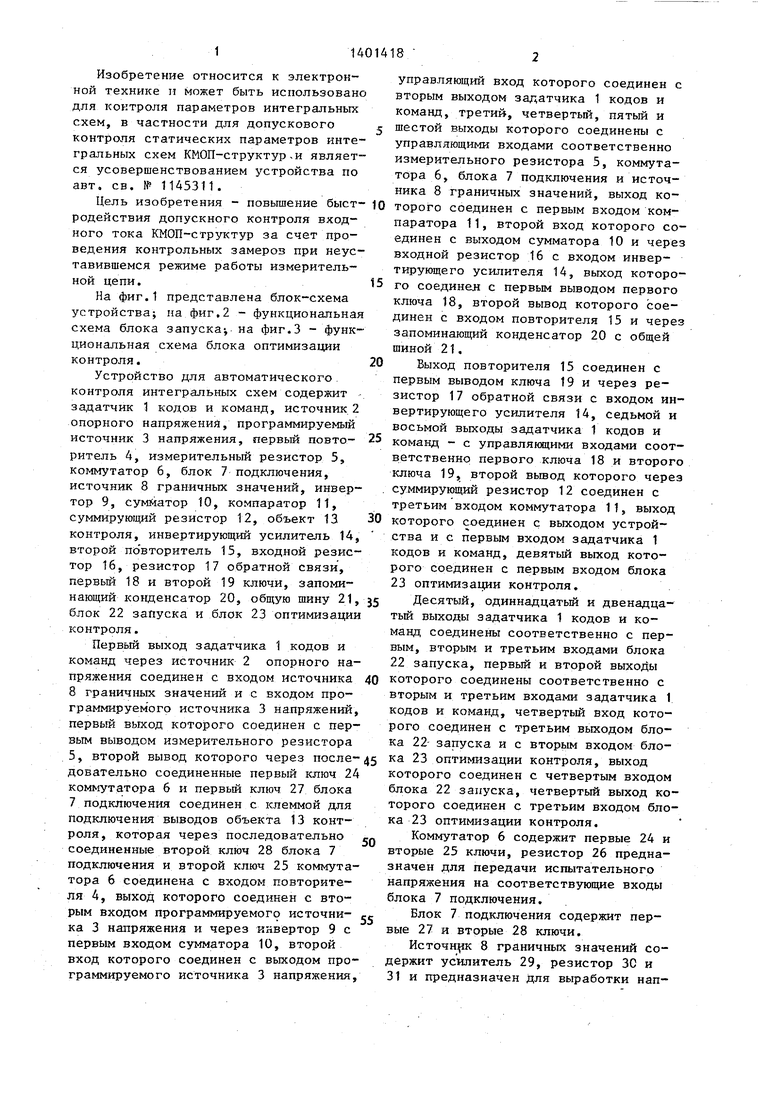

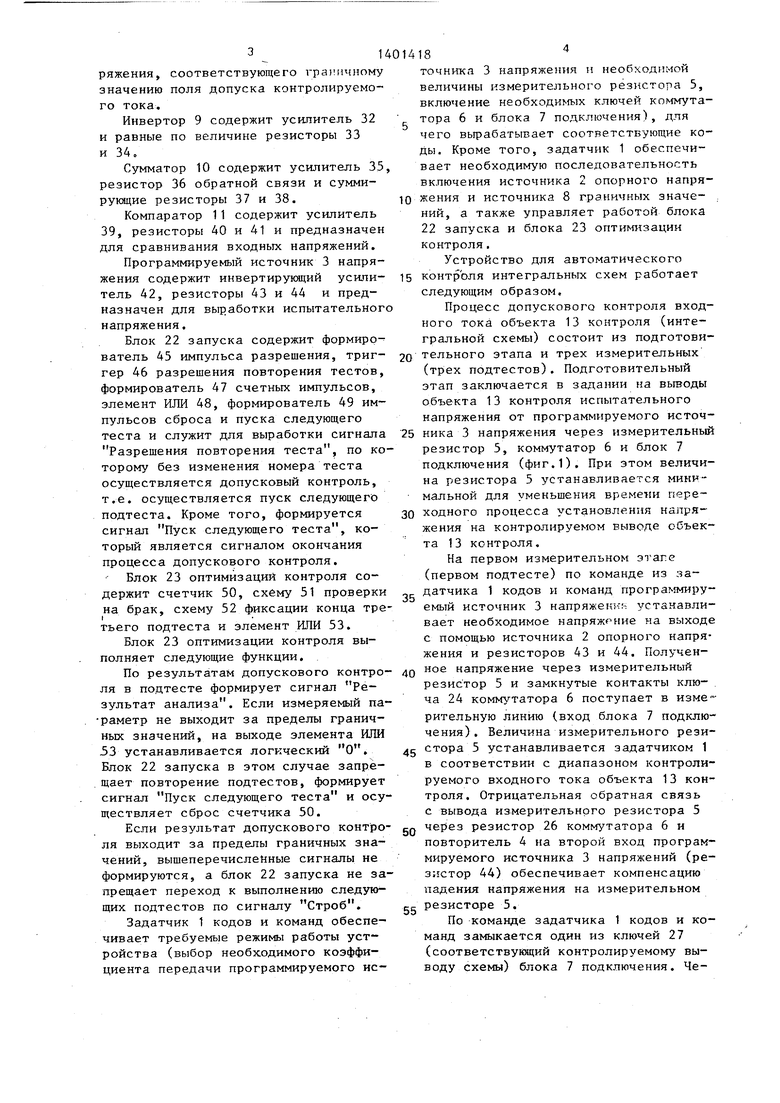

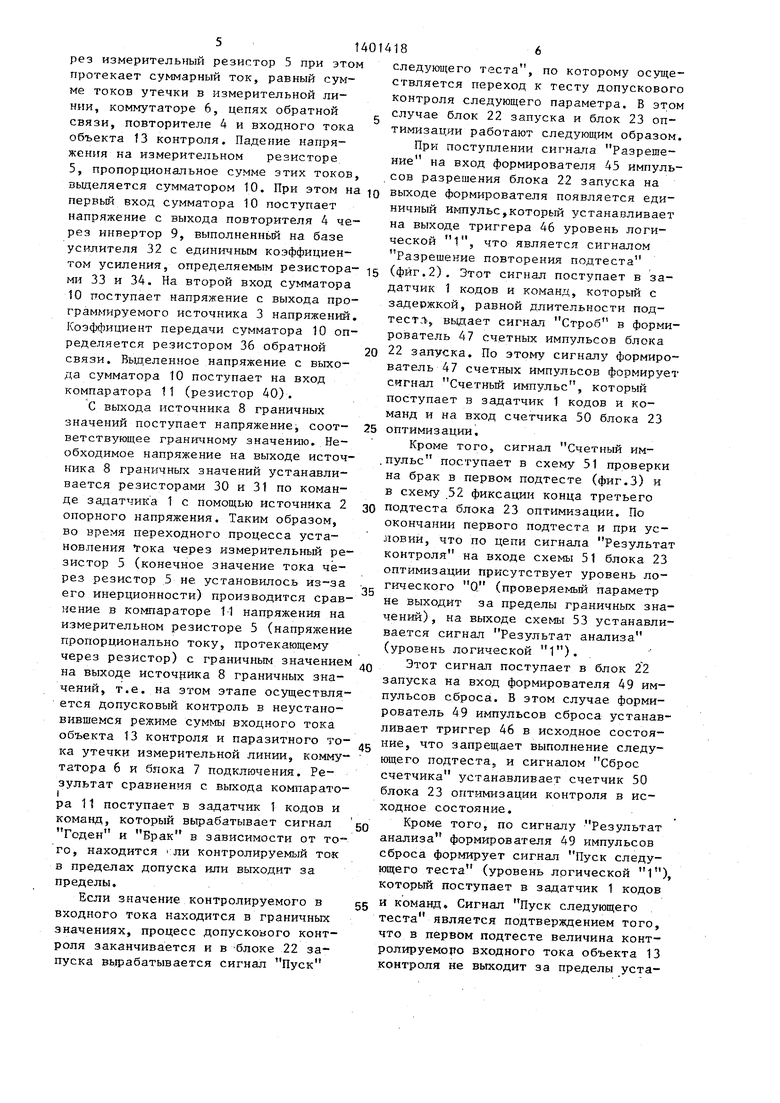

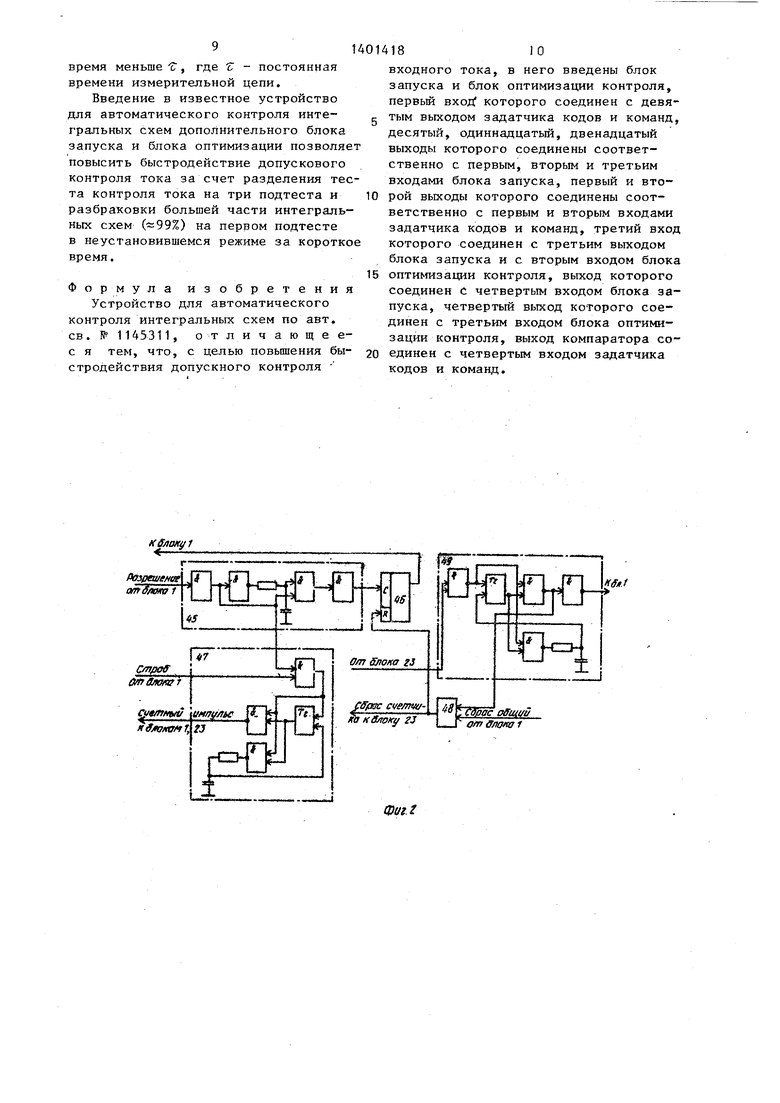

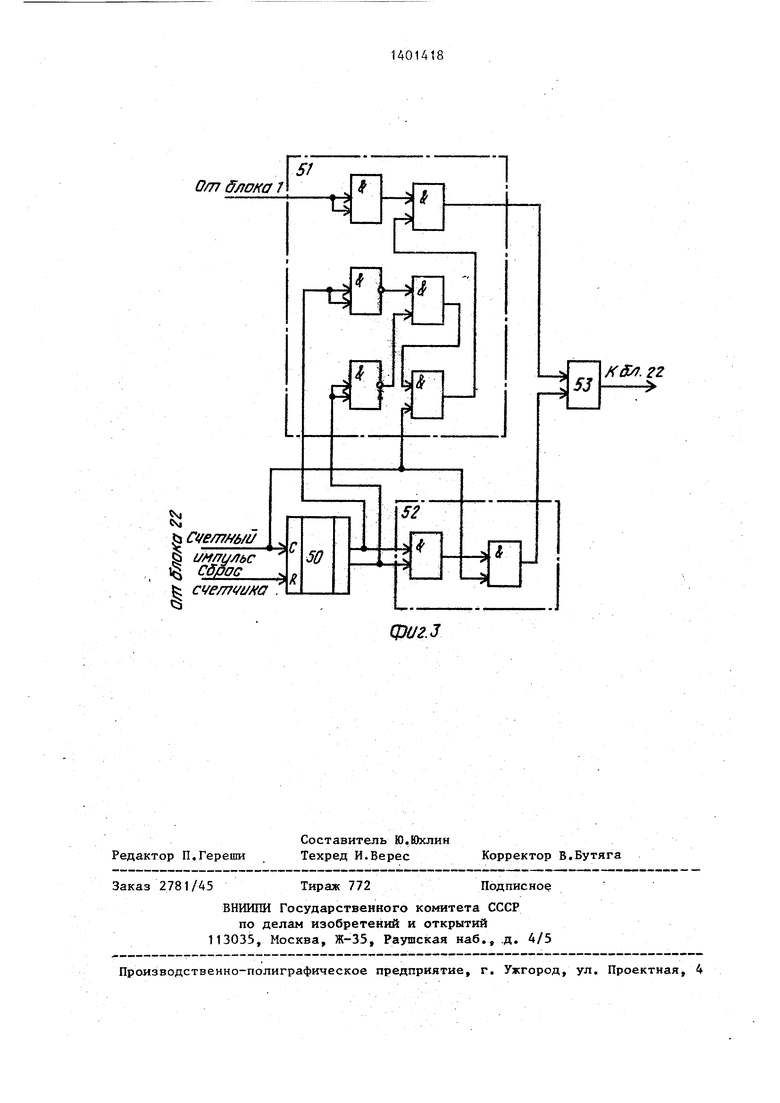

На фиг.1 представлена блок-схема устройства; на фиг.2 - функциональная схема блока запуска-, на фиг.З - функциональная схема блока оптимизации контроля.

Устройство для автоматического контроля интегральных схем содержит за,датчик 1 кодов и команд, источник 2 опорного напряжений, программируемый источник 3 напряжения, первый повто-

ритель 4, измерительный резистор 5, коммутатор 6, блок 7 подключения, источник 8 граничных значений, инвертор 9, сумйатор 10, компаратор 11, суммирующий резистор 12, объект 13 контроля, инвертирующий усилитель 14, второй по вторитель 15, входной резистор 16, резистор 17 обратной связи, первый 18 и второй 19 ключи, запоминающий ковденсатор 20, общую шину 21, блок 22 запуска и блок 23 оптимизации контроля.

Первый выход задатчика 1 кодов и команд через источник 2 опорного напряжения соединен с входом источника В граничных значений и с входом про- граммируем ого источника 3 напряжений, первый выход которого соединен с первым выводом измерительного резистора 5, второй вывод которого через последовательно соединенные первый ключ 24 коммутатора 6 и первый ключ 27 блока 7 подключения соединен с клеммой для подключения выводов объекта 13 контроля, которая через последовательно соединенные второй ключ 28 блока 7 подключения и второй ключ 25 коммутатора 6 соединена с входом повторителя 4, выход которого соединен с вторым входом программируемого ИСТОЧНИ-

ка 3 напряжения и через инвертор 9 с первым входом сумматора 10, второй вход которого соединен с выходом программируемого источника 3 напряжения.

управляющий вход которого соединен с вторым выходом задатчика 1 кодов и команд, третий, четвертьп4, пятый и шестой выходы которого соединены с управляющими входами соответственно измерительного резистора 5, коммута- TOipa 6, блока 7 подключения и источника 8 граничных значений, выход которого соединен с первым входом компаратора 11, второй вход которого соединен с выходом сумматора 10 и чере входной резистор 16 с входом инвертирующего усилителя 14, выход которого соединен с первым выводом первого ключа 18, второй вывод которого соединен с входом повторителя 15 и чере запоминающий конденсатор 20 с общей шиной 21.

Выход повторителя 15 соединен с первым выводом ключа 19 и через резистор 17 обратной связи с входом инвертирующего усилителя 14, седьмой и восьмой выходы задатчика 1 кодов и команд - с управляняцими входами соответственно первого ключа 18 и второг ключа 19, второй вьшод которого чере суммирующий резистор 12 соединен с третьим входом коммутатора 11, выход которого соединен с выходом устройства и с первым входом задатчика 1 кодов и команд, девятый выход которого соединен с первым входом блока 23 оптимизаи;ии контроля.

Десятый, одиннадцатый и двенадца- тьй выходы задатчика 1 кодов и команд соединены соответственно с первым, вторым и третьим входами блока 22 запуска, первый и второй выходы которого соединены соответственно с вторым и третьим входами задатчика 1 кодов и комавд, четвертый вход которого соединен с третьим выходом блока 22- запуска и с вторьм входом блока 23 оптимизации контроля, выход которого соединен с четвертым входом блока 22 запуска, четвертый выход которого соединен с третьим входом блока 23 оптимизации контроля.

Коммутатор 6 содержит первые 24 и вторые 25 ключи, резистор 26 предназначен для передачи испытательного напряжения на соответствующие входы блока 7 подключения.

Блок 7 подключения содержит первые 27 и вторые 28 ключи.

Источник 8 граничных значений содержит усилитель 29, резистор 30 и 31 и предназначен для выработки нап-

3 1

ряжения, соответствующего гра)ичному значению поля допуска контролируемого тока.

Инвертор 9 содержит усилитель 32

Т1 и равные по величине резисторы 33

и 34,

Сумматор 10 содержит усилитель 35 резистор 36 обратной связи и суммирующие резисторы 37 и 38.

Компаратор 11 содержит усилитель 39, резисторы 40 и 41 и предназначен для сравнивания входных напряжений.

Программируемый источник 3 напряжения содержит инвертирующий усили- тель 42, резисторы 43 и 44 и предназначен для выработки испытательног напряжения.

Блок 22 запуска содержит формирр ватель 45 импульса разрешения, триг- гер 46 разрешения повторения тестов, формирователь 47 счетных импульсов, элемент ИЛИ 48, формирователь 49 импульсов сброса и пуска следующего теста и служит для выработки сигнала Разрешения повторения теста, по которому без изменения номера теста осуществляется допусковый контроль, т.е. осуществляется пуск следующего подтеста. Кроме того, формируется сигнал Пуск следующего теста, который является сигналом окончания процесса допускового контроля.

Блок 23 оптимизаций контроля содержит счетчик 50, схему 51 проверки на брак, схему 52 фиксации конца третьего подтеста и элемент ИЛИ 53.

Блок 23 оптимизации контроля выполняет следующие функции.

По результатам допускового контро- ля в подтесте формирует сигнал Результат анализа. Если измеряемый па- раметр не выходит за пределы граничных значений, на выходе элемента ИЛИ 53 устанавливается логический О. Блок 22 запуска в этом случае запрещает повторение подтестов, формирует сигнал Луск следующего теста и осуществляет сброс счетчика 50.

Если результат допускового контро- ля выходит за пределы граничных значений, вышеперечисленные сигналы не формируются, а блок 22 запуска не запрещает переход к выполнению следующих подтестов по сигналу Строб.

Задатчик 1 кодов и команд обеспечивает требуемые режимы работы уст ройства (выбор необходимого коэффициента передачи программируемого ис

5

5

0 25 О

0 5

Q

5

18

точника 3 напряжения и необходимой величины измерительного резистора 5, включение необходимых ключей коммутатора 6 и блока 7 подключения), для чего вьфабатывает соответствующие коды. Кроме того, задатчик 1 обеспечивает необходимую последовательность включения источника 2 опорного напряжения и источника 8 граничных значений, а также управляет работой блока 22 запуска и блока 23 оптимизации контроля.

Устройство для автоматического контроля интегральных схем работает следующим образом.

Процесс допускового контроля входного тока объекта 13 контроля (интегральной схемы) состоит из подготовительного этапа и трех измерительных (трех подтестов). Подготовительный этап заключается в задании на выводы объекта 13 контроля испытательного напряжения от программируемого источника 3 напряжения через измерительный резистор 5, коммутатор 6 и блок 7 подключения (фиг.1). При этом величина резистора 5 устанавливается минимальной для уменьшения времени переходного процесса установления напряжения на контролируемом выводе объекта 13 контроля.

На первом измерительном этаге (первом подтесте) по команде из за датчика 1 кодов и команд программируемый источник 3 напряжент-гг-: устанавливает необходимое напряжение на выходе с помощью источника 2 опорного напряжения и резисторов 43 и 44. Полученное напряжение через измерительный резистор 5 и замкнутые контакты ключа 24 коммутатора 6 поступает в измерительную линию (вход блока 7 подключения) . Величина измерительного резистора 5 устанавливается задатчиком 1 в соответствии с диапазоном контролируемого входного тока объекта 13 контроля. Отрицательная обратная связь с вывода измерительного резистора 5 через резистор 26 коммутатора 6 и повторитель 4 на второй вход программируемого источника 3 напряжений (резистор 44) обеспечивает компенсацию падения напряжения на измерительном резисторе 5.

По команде задатчика 1 кодов и команд замыкается один из ключей 27 (соответствующий контролируемому выводу схемы) блока 7 подключения. Через измерительный резистор 5 при этом протекает суммарный ток, равный сумме токов утечки в измерительной линии, коммутаторе 6, цепях обратной связи, повторителе 4 и входного тока объекта 13 контроля. Падение напря- женггя на измерительном резисторе 5, пропорциональное сумме этих токов, выделяется сумматором 10. При этом на nepBbrff вход сумматора 10 поступает напряжение с выхода повторителя 4 через инвертор 9, выполненной на базе усилителя 32 с единичным коэффициентом усиления, определяемым резисторами 33 и 34. На второй вход сумматора 10 поступает напряжение с выхода программируемого источника 3 напряжений. Коэффициент передачи сумматора 10 определяется резистором 36 обратной связи. Выделенное напряжение с выхода сумматора 10 поступает на вход компаратора 11 (резистор 40).

С выхода источника 8 граничных значений поступает напряжение, соответствующее граничному значению. Необходимое напряжение на выходе источника 8 граничных значений устанавливается резисторами 30 и 31 по команде задатчика 1 с помощью источника 2 опорного напряжения. Таким образом, во время переходного процесса установления Тока через измерительный резистор 5 (конечное значение тока через резистор 5 не установилось из-за его инерционности) производится сравнение в компараторе 11 напряжения на измерительном резисторе 5 (напряжение пропорционально току, протекающему через резистор) с граничным значением на выходе источника 8 граничных значений, т.е. на этом этапе осуществляется допусковый контроль в неустановившемся режиме суммы входного тока объекта 13 контроля и паразитного тока утечки измерительной линии, комму татора 6 и блока 7 подключения. Результат сравнения с выхода компарато- I ра 11 поступает в задатчик 1 кодов и

команд, который вьграбатывает сигнал Годен и Брак в зависимости от то го, находится :ли контролируемый ток в пределах допуска или выходит за пределы.

Если значение контролируемого в входного тока находится в граничных значениях, процесс допускоыого контроля заканчивается и в -блоке 22 запуска вырабатывается сигнал Пуск

следующего теста, по которому осутце- ствляется переход к тесту допускового контроля следующего параметра. В этом случае блок 22 запуска и блок 23 оптимизации работают следующим образом. При поступлении сигнала Разрешение на вход формирователя 45 импуль- сов разрешения блока 22 запуска на

выходе формирователя появляется единичный импульс,который устанавливает на выходе триггера 46 уровень логической 1, что является сигналом Разрешение повторения подтеста

(фиг.2), Этот сигнал поступает в задатчик 1 кодов и команд, который с задержкой, равной длительности под- тестл, выдает сигнал Строб в формирователь 47 счетных импульсов блока

22 запуска. По этому сигнал формирователь 47 счетных импульсов формирует сигнал Счетный импульс, который поступает в задатчик 1 кодов и команд и на вход счетчика 50 блока 23

оптимизации.

Кроме того, сигнал Счетный им- .пульс поступает в схему 51 проверки на брак в первом подтесте (фиг.З) и в схему .52 фиксации конца третьего

подтеста блока 23 оптимизации. По окончании первого подтеста и при условии, что по цепи сигнала Результат контроля на входе схемы 51 блока 23 оптимизации присутствует уровень логического Q (проверяемый параметр не выходит за пределы граничных значений), на выходе схемы 53 устанавливается сигнал Результат анализа (уровень логической 1).

Этот сигнал поступает в блок 22 запуска на вход формирователя 49 импульсов сброса. В этом случае формирователь 49 импульсов сброса устанавливает триггер 46 в исходное состоя-

ние, что запрещает выполнение следующего подтеста, и сигналом Сброс счетчика устанавливает счетчик 50 блока 23 оптимизации контроля в исходное состояние.

Кроме того, по сигналу Результат

анализа формирователя 49 импульсов сброса формирует сигнал Пуск следующего TeiCTa (уровень логической 1), который поступает в задатчик 1 кодов и команд. Сигнал Пуск следующего теста является подтверждением того, что в первом подтесте величина конт- ролируеморо входного тока объекта 13 контроля не выходит за пределы уста71

новленных граничных значений. Процесс допускового контроля тока прекращается.

Если по окончании первого подтеста в цепи сигнала Результат контроля присутствует уровень логической 1 (контролируемый параметр выходит за пределы граничных значений), триггер 46 блока 22 запуска и счетчик 50 бло- ка 23 оптимизации не сбрасываются и в цепи сигнала Разрешение повторения подтестов сохраняется высокий уровень, что является разрешением к выполнению второго подтеста контроля,

На втором измерительном этапе (втором подтесте) по команде из за- датчика I кодов и команд на выходе программируемого источника 3 напряжений (фиг.1) устанавливается необходи- мое напряжение, вывод объекта 13 контроля отключен. Отрицательная обратная связь с вывода измерительного резистора 5 через резистор 26 коммутатора 6 и повторитель 4 обеспечивает компенсацию падения напряжения на измерительном резисторе 5. В этом случае через измерительный резистор 5 протекает ток, равный сумме токоа утечки в измерительной линии, комму- таторе 6, цепях обратной связи и повторителе 4. Падение напряжения на измерительном резисторе-5, пропорциональное этому току, наделяется сумматором 10 с помощью инвертора 9. Это

напряжение запомина.ется на запоминающем конденсаторе 20, подключенном к входу повторителя 15 с высокоомным входом.

Под действием отрицательной обратной связи, образованной резистором 17, напряжение на конденсаторе 20 устанавливается таким, что на выходе -повторителя 15 появляется напряжение равное напряжению на выходе сумматора 10, но с противоположным знаком. Равенство напряжений обеспечивается равенством величин сопротивлений резистора 17 обратной связи и входного резистора 16. Таким образом, на выходе повторителя 15 присутствует напря жение, пропорциональное току утечки. Ключ 19 разомкнут.

Затем по команде задатчика 1 ключ 18 размыкается, а запоминающий конденсатор 20 поддерживает на выходе повторителя 15 напряжение, соответствующее току утечки.

8

Таким образом, на втсром этапе производится выделение напряжения, соответствуюидего току утечки в измерительных цепях. На третьем измерительном этапе (третьем подтесте) по

команде за цатчика

кодов и команд

5

0 5 О

5

0

5

5

замьисаготся ключи 27 и 28, соответствующие контролируемому выводу объекта 13 контроля, блока 7 подключения (фиг.1). Напряжение с выхода программируемого источника 3 напряж- ний че- р,ез измерительный резистор 5, комму- татор; 6 и блок 7 подключения поступает на вывод испытуемой схемы. Падение напряжения на измерительном резисторе 5 вьщеляется сумматором 10 и поступает на второй вход компаратора 11 (резистор 40). При этом на первый вход компаратора 11 через суммируюпуй резистор 12 и замкнуты по команде задатчика 1 кодов и команд.ключ 19 поступает напряжение, соответствующее инвертированному току утечки. На третий вход компаратора 11 (резистор 41) поступает напряжение с выхода источника 8 граничных значений, соответствующее граничному значению входного тока объекта 13 контроля.,

В этом случае в компаратора 11 сравнивается напряжение с вяхода источника 8 граничных значений (соот-- ветствующее заданному гран ;чному значению тока в установившемся реллям -) с напряжением на измеритегьном резне™ торе 5 (соответствующем сумме входного тока объекта 13 контроля и токов утечки измерительных цепей в установившемся режиме) и с н пряжен;1ем ка выходе повторителя 15, которое измерено на втором подтЁсте и хранится на запоминающем конденсаторе 20. Величина этого напряжения соответствует току утечки в измерительных цепях с противоположным знаком. Ка выходе компаратора 11 появляется результат сравнения входного тока объекта 13 контроля с граничным значением с компенсацией токов утечки.

Больпшнство ИС КМОП-структур («99%) имеет входные токи в несколько раз меньше, чем предельно допустимые значения по техническим условиям.

Например, при допустимом значении тока 50нА 99% интегральных схем имеют входные токи менее ЮнА. Менее 1% интегральных схем контролируется в установившемся режиме за время значительно больше f, остальные 99% - за.

время меньше г, где гГ - постоянная времени измерительной цепи.

Введение в известное устройство для автоматического контроля инте- гральных схем дополнительного блока запуска и блока оптимизации позволяе повысить быстродействие допускового контроля тока за счет разделения теста контроля тока на три подтеста и разбраковки большей части интегральных схем (99%) на первом подтесте в неустановившемся режиме за коротко время.

Формула изобретения

Устройство для автоматического контроля интегральных схем по авт. ев. № 1145311, отличающее- с я тем, что, с целью повьшгения бы- стродействия допускного контроля

140141810

входного тока, в него введены блок

запуска и блок оптимизации контроля, первьй вход которого соединен с девятым выходом задатчика кодов и команд, десятый, одиннадцатый, двенадцатый выходы которого соединены соответственно с первым, вторым и третьим входами блока запуска, первый и второй выходы которого соединены соответственно с первым и вторым входами задатчика кодов и команд, третий вход которого соединен с третьим выходом блока запуска и с вторым входом блока оптимизации контроля, выход которого соединен с четвертым входом блока запуска, четвертый выход которого соединен с третьим входом блока оптимизации контроля, выход компаратора соединен с четвертым входом задатчика кодов и команд.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для автоматического контроля интегральных схем | 1983 |

|

SU1145311A1 |

| Устройство для допускового контроля токов | 1983 |

|

SU1128224A1 |

| Устройство для автоматического контроля параметров интегральных схем | 1988 |

|

SU1649474A1 |

| Устройство для контроля интегральных схем | 1985 |

|

SU1290522A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ЭЛЕКТРИЧЕСКОГО СОПРОТИВЛЕНИЯ ТОЧЕК АКУПУНКТУРЫ | 1992 |

|

RU2027403C1 |

| Устройство автоматизированного контроля | 1987 |

|

SU1525680A2 |

| УСТРОЙСТВО ПОЭЛЕМЕНТНОГО ДОПУСКОВОГО КОНТРОЛЯ/?„Ск или /?к/.к ЦЕПЕЙ | 1973 |

|

SU370557A1 |

| ВСГ-СОЮЗНАЯр'^-"Г-:-^--ла;Г!:ГНДЯв i J-tt S •' • •* -^ - ' • "^ьИЬЛИО^ьКА | 1971 |

|

SU298069A1 |

| Высоковольтная система электропитания с микропроцессорным управлением | 1991 |

|

SU1835541A1 |

| Устройство для измерения параметров интегральных схем | 1981 |

|

SU972423A1 |

Изобретение относится к электронной технике и служит для повьппе- ния быстродействия допускового контроля входного тока КМОП-структур. Устройство содержит задатчик 1 кодов и кома1Щ, источник 2.опорного напряжения, программируемьй источник 3 напряжения, повторители 4 и 15, измерительный резистор 5, коммутатор 6, блок 7 подключения и источник 8 граничных значений. Кроме того, устройство включает инвертор 9, сумматор 10, компаратор 11, суммирующий резистор 12, инвертирующий усилитель 14, резистор 17 обратной связи, ключи 18 и 19 и запоминающий конденсатор 20. Введение блока 22 запуска, блока 23 оптимизации контроля и образование новых функциональных связей обеспечивают возможность проведения контрольных замеров при неустановившемся режиме работы измерительной цепи, т.е. при разделении теста контроля тока на три подтеста и разбраковке большей части интегральных схем (99%) на первом подтесте. 3 ил. с (Л

Ajyxanf/

O/frexKOfT

Kff/i.t

Фиг

цзиг.з

| Устройство для автоматического контроля интегральных схем | 1983 |

|

SU1145311A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-06-07—Публикация

1986-09-04—Подача