(54) ЦИФРОВОЙ ЧАСТОТНЫЙ ДЕТЕКТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой частотный детектор | 1978 |

|

SU720779A1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОЙ БАЛАНСИРОВКИ РЕЗОНАТОРА ТВЕРДОТЕЛЬНОГО ВОЛНОВОГО ГИРОСКОПА ЛУЧОМ ЛАЗЕРА | 1993 |

|

RU2079107C1 |

| Одноканальное устройство для управления -фазным преобразователем | 1978 |

|

SU775855A1 |

| Устройство для анализа сигналов в реальном масштабе времени | 1990 |

|

SU1812518A1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ МНОГОЛУЧЕВЫХ РАДИОСИГНАЛОВ | 1992 |

|

RU2042195C1 |

| Преобразователь телевизионного стандарта | 1980 |

|

SU1238267A1 |

| Устройство для измерения частотных характеристик диэлектрических свойств веществ | 1982 |

|

SU1051455A1 |

| Устройство для цикловой синхронизации при двоичном сверточном кодировании | 1982 |

|

SU1062881A1 |

| Преобразователь отклонения частоты от номинального значения в аналоговый сигнал | 1990 |

|

SU1748082A1 |

| УСТРОЙСТВО РАСПОЗНАВАНИЯ ЛИНЕЙНО-ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 1983 |

|

SU1841012A1 |

1

Изобретение относится к технике связи и может нспопьзова гься в системах передачи данных.

По основному авт. св. № 72О779 известен цифровой частотный детектор, содержащий ограничитель, выход которого соединен с входами триггера, выход которого подключен к первому входу регистра, второй вход которого соединен с выходом генератора опорной частоты, при этом выходы регистра подключены к входаммажоритарного блока, выход инвертора подключен к первому дополнительному входу триггера, второй и тр&тий дополнительные входы которого со&динены с выходом nej®oro ждущего мультивибратора, вход которого соединен с входом инвертора, четвертым дополнательным входом триггера и выходом второго ждущего мультивибратор, к входу кйторюго подключен выход ограничите .

Однако в известном детекторе недоста точная помехоустойчивость.

Цель изобретения - повышение помехоустойчивости.

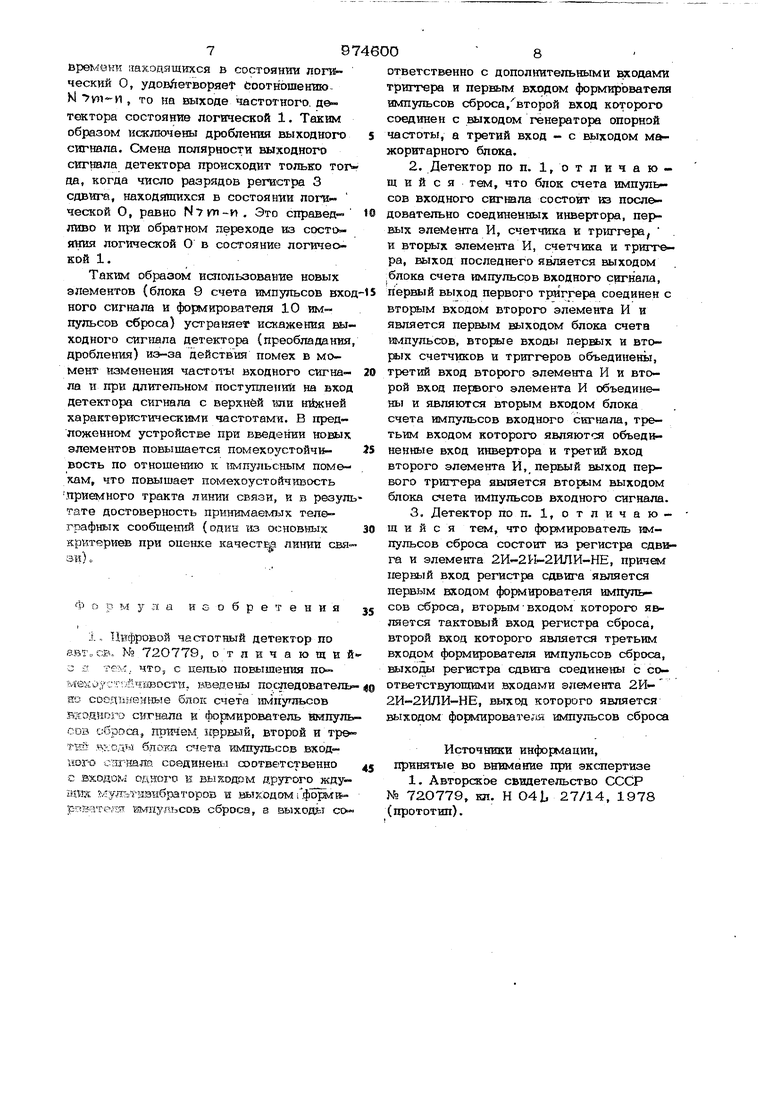

Для этого в цифровой частотный детектор введены последовательно соединенные блок счета импульсов входного сигнала и формирователь импульсов сброса, причем первый, второй и третий входы блока счета импульсов входного сиг нала соединены соответственно в входом одного и выходом другого ждущих мультИи вибраторов и выходом формирователя импульсов сброса, а выходы соответственно с дополнительными входами триггера, и первым входом формирователя импульсов сброса, второй вход которого соединен с выходом генератора опорной частоты, а третий вход - с выходом мажоритарного блока.

Блок счета импульсов входного сшгна ла состоит из последовательно соедине ных инвертора, первых элемента И, счегчика и| триггера и вгорьгк элемента И, счетчика и триггера, звь1ход последнего является выходом блока счета импульсов входного сигнала, первый №1ход первого триггера соединен с втор1лм входом второго элемента И и является первым выходом блока счета импульсов, BTOpbie входы первых и вторых счетчиков и трш героБ объединены, третий вход второхх элемента И и второй вход первого элемента И .объединены и являются вторым входом блока счёГаИмпульсов входного сигнала, третьим входом которого являются объединенные (ВХОД инвертора и третий вход второпэ элемента И, первый выход первого триггера является вторым выходом блока C4eta импульсов входного сигнала, формирователь импульсов сброса состоит вз регистра сдвига и элемента 2И-2И-2Ш1И НЕ, причем первый вход регистра сдвига является первым входом формирователя импульсов сброса, вторым входом которого является тактовый вход регистра сброса, второй вход которого является третьим-входом формирователя импульсов сброса, выходы регистра сдвига соединены с соответствующими входами элемента 2И-2И- 2ИЛИ-1-Ш, выход которого является выходом формирователя ; -и зщьсов сброса. rlfi чертеже изображена стр -ктурная сгшма предлагаемого детектора. Цифровой частотный детектор содер;, 01п:аннчите зь 1, триггер 2, .регистр 3, т-енератор 4 опорной частоты, мажоритар№ й блок 5, ждутциё мультивибрато 6 инвертор 8, блок 9 счета импул входного сигнада, формирователь 10 В сброса, блок 9 состоит из fiuр I 11,12, счетчиков 13,14, I 15,16 и инвертора 17, форг-т, 10 состоит из регистра 18 samii л 1 элемента 19 t оиство работает следующим об-разом. Вкодной сигнал поступает на ограничнте.ль if который формирует п эямоуголь аые- лщтъсы, следующие с частотой поjjTDpein-Я. равной частоте входного Сигнал ОЬТКОДЕОЙ сигнал ограничителя 1 посту1ше;г на .й вход триггера 2, на вхо шй5н, мупь тшнбратора 6, включая его и аа третьи входы элементов И 11,12. Длительность выходного импульса ждуще :го мупьттшибратора 6 пер ленная, ве личийа которая сиределяется частотой входнозго сщ-аала. При поступлеяии на BS-oa детектора стзгнала с нижней харак- тернсгйческой частотой j длительность t ВЫХОДНЫХ импульсов ждущего мультивибратора 6 равна TTj При поступлетш на вход детектора сагнала с верхней характеристической частотой {« длительность TX-t выходных импульсов ждущего мультивибратора 6 равна -беоконечности. Иыходньгё импульсы ждущего мультивибратора (5 задним фронтом включают ждущий мультивибратор 7, выходные импульсы тсоторого имеют отрицательную полярность и постоянную длительность равную t. Пусть на вход детектора поступает сшнал с верхней характеристической частотой Ер , тогда на выходе ждущего мультивибратора 6 поддерживается постоянный уровень выходного Напряжения (логическая 1), т.е. длительность выходного импульса равна бесконечности. При этом триггер2 находится в единичном состоянии, триггеры 15 и16внулевсм состоянии и на выходах жд5тцего мультивибратора 7 и мажоритарного блока 5 уровень логичеокой 1. Пусть частота сигнала на входе детектора изменяется от f g до { . В диапазоне изменения частоты сигнала от f g до f 2. триггеры 2,15,16, ждущие мультивибраторы 6, 7 сохраняют предыдущее состояние. На выхода мажоритарного блока 5 также сохраняется уровень логической 1. При достижении частотой сигнала величины f 2. выходе ждущего мультивибратора 6 сформируется импульс, который задшш фронтом ышючает ждущий мультивибратор 7, формирующий первый сигнал блокировки, который, формируется во время изменения частоты входного сигнала от до f . Таким образом на время изменения частоты входного сигнала от 2. до f -1 тркгтср 2 заблокирован и сохраняет предьщущее состояние. Кроме того, триггер 2 заблокирован Btoрым сигналом блокировки, формируемым триггером сигнала от J до . Длительность erot; определяется емкостью KI счетчика 13 импульсов, причем П K,j К, где П - порог срабатывания мажоритарного блока 5. Таким образом, второй блокировки блокирует триггер 2 до тех пор, пока во apsviH изменения частоты входного сиг нала от до 4; текущее значение частоты) на счетчик 13 импульсов не поступит К импульсов входного сигнала. Наличие второго сигнала блокировки позволяет уменьшить исзесажения вы- ходнопо.сигнала (преобпаданяя,дробления), что объясетется следующим образом. Пусть в момент времени t частота ,входногосигнала достигла значения д причем следутощее ее значение в момент времени -Ь должно быть f g т.е. находиться в диапазоне частот от -1 ii ( зоне действия первого сиг нала блокировки, формируемого ждутаим мультивибратором 7). Пусть при этом в момент времени b частота входного сигнала под действием помех приняла значение i , т.е. за зоной действия первого импульса блокировки. Однако триггер 2 не изменит своего состояния, так как он заблокирован вторым сигналом блокировки, который формирует ся триггером 15. После окончания Действия помехи частота входного сигнала в момент времени tjj примет значение f L чалее последовательно будет принимать значения, которые удовлетворя ют условию f -t 4 до момента времени -t когда значение fj. равно С-л., лидды значки ПК xj. f . В интервале времени от-Ь,, до -t первый сигнал блокировки, поступает через инвертор 17 на элементы И 11 и дает разрешение на прохождение импутшсов с выхода ограничителя 1 на счетчик 13импульсов. Импульс переполнения сче чика 13 импульсов включает триггер 15 При этом элемент И 11 закрыт и снят второй сигнал блокировки с триггера 2. и элемента И 12. В момент времени -fcg- , когда частота входного сигнала достигнет зшчения триггер 2 под действием выходных импульсов ограничителя 1 переключается в противоположное состояние. Таким образом, триггер 2 сработает только в момент времени, когда частота входного сигнала достигнет значения ХУ( При отсутствии второго сигнала блокировки триггер 2 изменит свое состо яние в момент. времени -Ь- действия помехи) и сохранит его до момента обратного перехода частоты входного сигнала от до ig , когда частота . входного сигнала достигнет значения f . Следовательно, в этом случае длительность телеграфной посылки увелвчится на величину приблизительно равную к Тер. При дальнейшем изменении частоты .входного сигнала от значения 1 f до значения -f (с момента времени bg ) импульсы с выхода ограничителя 1 через эл««1ент И 12 поступают на счеч чик 14 импульсов, емкость которого К П. Импульс переполнения счетчика 14импульсов включает триггер 16, выходной сигнал котпрьго поступает на второй информапионный вход регистра 18 сдвига, на парный информационный и гактовый входы которого поступают сигйаяы с выхода мажоритарного блока 5 и с дополнительного выхода генератора 4 частоты. Выходной сигнал триггера 16 дает разрешение на формирование импульса сброса, который вырабатывается формирователем 10 импульсов сброса в момент изменения полярности выходного напряжения мажоритарного блока 5. Импульс сброса устанавливает в нулевое (и ходное) положение счетчики. 13 и 14 импульсов и триггеры 15 и 16. Выходкой сигнал триггера 15 блокирует триггер 2 и закрывает элемент И 12. Таким образом, триггер 2 сохраняет свое состояние до момента обратного перехода частоты входного сигнала от .,, когда частота входного сит f И ° € нала достигнет значения ± 7 -f/. Р этом исключаются искажения выходного . сигнала частотного детектора, которые возникают из-за воздействия помех на входной сигнал. В момент времени, когда с триггера 2сняты сигналы блокировок, под воздействием на входной сигнал импульсных и других видов помех, нарушающих рабюту детектора, в выходном сигнале триггера 2,1 поступающем в регистр 3 (сдвига), могут появиться дробления. Исключение дроблений п юисходит следующим образом. Выходной сигнал триггера 2 поступает на информапионный вход регистра 3 сдвига и каждым импульсом генератора 4 опорной частоты продвигается иа один . разряд. Выход каждого разряда регистра 3сдвига подключен к соответствующему; входу мажоритарного блока 5. Пусть регистр 3 сдвига имеет п разрядов, тогда база анализа равна Vyi , а решение о значении выходного детектора принимается по Vi разрядам (где tri и t - целые чт/к па, УУ - нечетное и И7 -я ) Если выходной сигнал триггера 2 имеет уровень логической 1, но иэ-за воздействия помех появляются дробления (логические О), а выходной сигнал триггера 2 непрерывно записывается и продвигается по разрядам в регистре 3 сдвига, то в данный момент времени каждый разряд регистра 3 сдвига примет какое-либо определенное значение (логический О или логическая 1). Если число разрядов регистра 3 сдв1, в данный момент 79746 времени находящихся в состоянии лоп ческий О, yflOBfteTBOpHet соогтошениюЫ , то на выходе частотного, деTQiTopa состояние погичесжой 1. Таким образом исключены дробления выходного сигнала. Смена полярности выходного сигнала детектора происходит только тогда, когда число разрядов регистра 3 сдвига, находящихся в состоянии логической О, равно , Это справед- б ливо и при обратном переходе из состояния логической О в состояние; логической 1. Таким образом использование новых элементов (блока 9 счета импульсов вход-15 ного сигнала и формирователя 10 импульсов сброса) устраняет искажения выходного сигнала детектора (преобладания, дробления) из-за действия помех в момент изменения часто1Ъ1 входного сигна- 20 ла и при длительном пост yime НИИ на вход детектора сигнала с верхней vaivi нижней характеристическими частотами. В прюд- ложенном устройстве при введении новых элементов повышается помехоустойчивость по отношению к импульсным помехам, что повышает помехоустойчивость Приемного тракта линии связи, и в резуль тате достоверность принимаемых телеграфных сообшений (один из основных KpvsTepHSB при оцешсе качеству линии связи) о Формула обретения i „ Цифровой частотный детектор по 8Вг„св„ № 72О779, отличающий с 3. тем, что, с целью поЕРЫшешш по мекоуст.1Йт0вости. введены последователь шз coofVUHSHF&m блок счета имИутоьсов входмг: го стсгнала и форлирователь Шйпуль CDB сброса, причем зфрвьзй, второй и трутни .«.оды блокл счета импульсов входН г-о сагиалв. соедикежд соотве Тственно с BxoROfA одного К ВЫХОДОМ другого жду- а0гл л:улотавнбрз1оров и выходом Гфорлир : ввте,Ш fjMJLyribcoB, сброса, з выходы со 5 0 ответственно с дополнительными Еосодами триггера и первым втищом формирователя импульсов сброса/Второй вход которого соединен с выходом генератора опорной частоты, а третий вход - с выходом мажоритарного блока. 2. Детектор по п. 1, о т л и ч а ю щ и и с я тем, что блок счета импульсов входного сигнала состоит кз последовательно соединенных инвертора, первых элемента И, счетчика и триггера, . и вторых элемента И, счетчика и триггера, выход последнего является выходом Jблока счета импульсов входного сигнала, первый выход первого триггера соединен с вторым входом второго элемента И и является первым йз1ходом блока счета Шv пyльcoв, вторые входы перных и вторшх счетчиков и триггеров объединены, третий вход второго элемента И и второй вход первого элемента И объединены и являются вторым входом блока счета импульсов входного сигнала, третьим входом которого являются обьедйненные вход инвертора и трютий вход второго элемента И, первый выход первого триппера является вторым выходом блока счета импульсов входного сигнала. 3, Детектор по п. 1, отличаюш и и с я тем, что форж ирюватель импульсов сброса состоит из регистра сдвига и элемента 2И-2И-2ИЛИ-НЕ, причем первый вход регистра сдвига является первым входом формирователя импуль сов сброса, вторым входом которогп является тактовый вход регистра сброса, второй вход которого является третьим входом формирователя импульсов сброса, выхода регистра сдвига соединены с соответствуюпшми входами элемента 2И2И-2ИЛИ-НЕ, выход которого является выходом форв1гаровате/ Я импульсов сброса Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 720779, кл. Н О4Ь 27/14, 1978 (прототип).

Авторы

Даты

1982-11-15—Публикация

1981-03-31—Подача