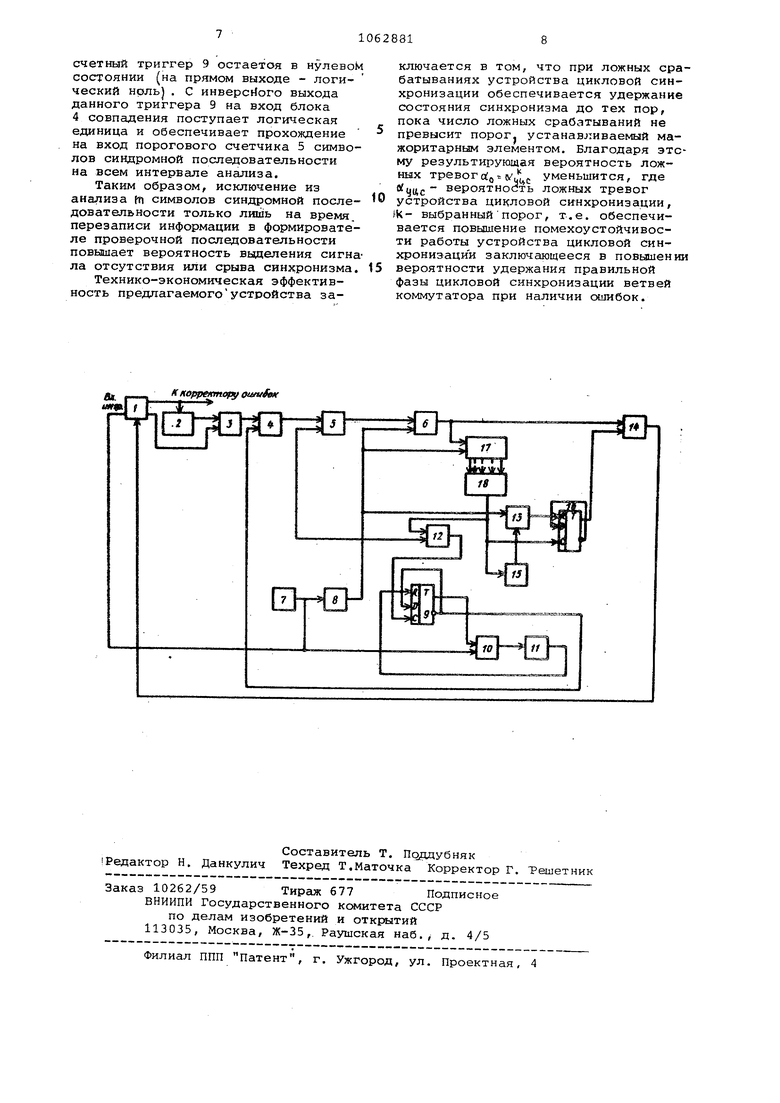

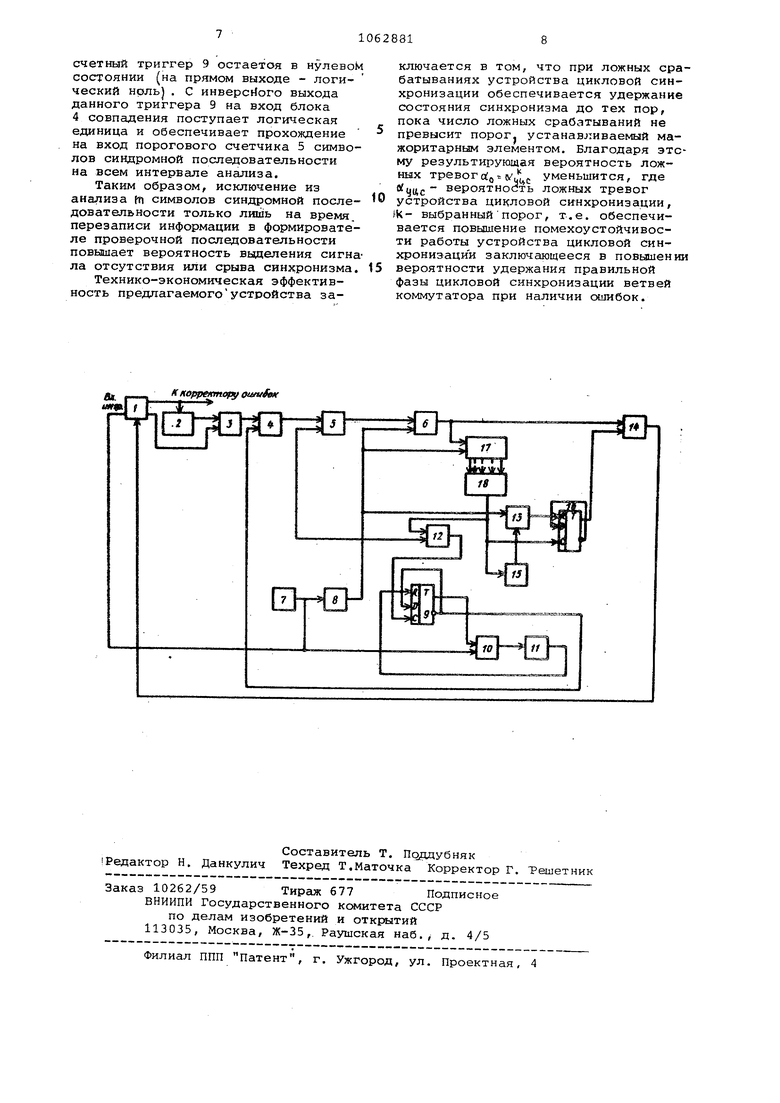

Изобретение относится к электро связи и может использоваться для цикловой синхронизации в аппаратуре повышения достоверности передачи данных в системах сбора и обработки дискретной информации, сигн.элов цифрового радио и телевизион ноге вещания при кoдиpoвaEiии их сверточнь№Ш колами с порогонькл блоком декодирования. Известно устройство для циклово синхронизации при двоичном сверточ ком кодировании, содержащее последовательно соединенные запрещающий блок, KObJMyTaTop, ключи, блок обна ружения ошибок, блок исправления ошибок, а также последовательно соединенные блок формирования такт вых импульсов, счетчик объема, выборки, формирователь импульсов уст новки нуля, элемент ИЛИ, пороговый счетчик, триггер и формирователь запрещающих импульсов, выход которого подсоединен к второмувходу запрещающего блока, выход блока формирования тактовых импульсов подсоединен к входу запрещающего блока, а второй вход порогового счетчика подключен к выходу блока обнаружения ошибок. Недостатками данного устройства являются сравнительно большое времй вхождения в синхронизм и невысокая кздежность работы устройст ва, 1ак как при переключении ключей первоначальными. т,е, принятыми проверочным символами будут зг1полнены блок обнаружения ошибок и блок исправления ошибок, и в течение Гп TciKTOB (где Yn - максимальная степень поролсдающего полинома) будут ошибочно формироваться символы сикдромной последовательности, которые фиксируются пороговым счетчиком и тем caMHivi увеличиваетcfi вероятность лохсного срабатывания устройства цикловой синхро-н зaции, следовательно, увеличив,иется время вхождения в синхронизм. Наиболее близким техническим решением к изобретению является У(::тройство для цикловой синхрониЗс ции при двоичном сверточном кодировании, содержащее последоватешьно соединенные коммутатор, фор м - рователь проверочной последов;; тельности, формирователь синдромной последовательности, первый 6j-toK совпадения, пороговый счетчик и формирователь запрещающих сигналов , к второму входу которого ПОД кх;ючен формирователь тактовых им-п льсов через счетчик объема выбор ки, выход которого подсоединен к второму входу порогового счетчиKi:i, последовательно соединенные счетный триггер, второй блок совпадения и формирователь временного интервала перезаписи, при этом второй вход второго блока совпадения объединен с входом счетчика объема выборки и подключен к информационному входу коммутатора, второй вход которого является входом устройства, второй выход KOMiviyTaTopa подсоединен к второму входу формирователя синдромной последовательности, а к второму входу первого блока совпадения подключен инверсный выход счетного триггера, к счетному входу которого подключен выход форгчирователя временного интервала перезаписи, а к установочному входу подключен выход счетчика объема выборки, причем выход формирователя запрещающих сигналов подсоединен к третьему входу кoм2 vтaтopa. Недостатками известного устройства для цикловой синхронизации при двоичном сверточном кодировании ЯВЛЯЮТСЯ недостаточная надежность (точность) достоверности выделения сигнала срыва синхронизма из-за исключения синдрома из ffi символов при анализе синдромной последовательности, когда не происходит перезапись информации в формирователе проверочной последовательности, а также низкая помехоустойчивость работы устройства цикловой синхронизации при двоичном сверточном кодировании при возникновении в канале связи пакетов ошибок. Цель изобретения - повышение помехоустойчивости при наличии пакетов ошибок. Поставленная цель достигается тем, что в устройство для цикловой синхронизации при двоичном сверточном кодировании, содержащее последовательно соединенные кo Фlyтaтop, формирователь проверочной последовательности, формирователь синдромной последовательности, первый блок совпадения, пороговый счетчик и формирователь запрещающих сигналов, к второ.гу входу которого подключен формирователь тактовых импульсов через счетчик объема выборки, выход которого подсоединен к второму входу порогового счетчика, последовательно соединенные счетньтй триггер, второй блок совпадения и формирователь временного интервала перезаписи, при этом второй вход второго блока совпадения объединен с входом счетчика объема выборки и подключен к информационному входу коммутатора, второй вход которого является входом устройства, второй выход коммутатора подсоединен к второму входу формирователя синдромной последовательнос ти, а к второму входу первого блок совпадения подключен инверсный выход счетного триггера, введены тре тий блок совпадения и последовател но соединенные регистр сдвига, маж ритарный элемент, инвертор, четвер тый блок совпадения, дополнительны счетный триггер и пятый блок совпа дения, выход которого подсоединен к дополнительному входу.коммутатора, а второй вход объединен с первы входом регистра сдвига и подключен к выходу формирователя запрещающег сигнала, второй вход регистра сдви объединен с вторым входом четверто го блока совпадения, первым входом третьего блока совпадения, и подключен к выходу счетчика объема выборки, при этом второй вход третьего блока совпадения объединен со счетным входом дополнительного счетного триггера и подключен к выходу мажоритарного элемента, а инверсный выход дополнительного счетного триггера подключен к своему инфopмaциoннo входу, причем выход формирователя временного интервала перезаписи подсоединен к установочному входу счетного триггера, счетный вход которого подключен к выходу третьего блока совпадения а инверсный выход подсоединен к своему информационному входу. На чертеже представлена блок-схе ма устройства для цикловой синхронизации при двоичном сверточном кодировании. Устройство для цикловой синхронизации при двоичном сверточном кодировании содержит коммутатор 1, формирователь 2 проверочной последовательности, формирователь 3 синд ромной последовательности, первый блок 4 совпадения, пороговый счетчик 5«, формирователь 6 запрещающих сигналов, формирователь 7 тактовых импульсов, счетчик 8 объема выборки счетный триггер 9, второй блок 10 совпадения, формирователь 11 времен ного интервала перезаписи третий, четвертый и пятый блоки совпадения 12-14, инвертор 15, дополнитель ный счетный триггер 16, регистр 17 .сдвига, и мажоритарный элемент 18, Устройство для цикловой синхронизации при двоичном сверточном кодировании работает следующим образом. Принятая кодовая последовательность в коммутаторе 1 разделяется на информационную (или информацион ные) и на проверочную (или проверо ные последовательности. Символы информационной последовательности -поступают на вход формирователя 2 проверочной последовательности, где из принятых информационных символов формируется проверочная последовательность, которая поступает на один из входов формирователя 3 синдромной последовательности, на второй вход которого с коммутатора 1 поступает принятая проверочная последовательность; производится формирование синдромной последовательности. При наличии цикловой синхронизации ветвей коммутатора 1 и отсутствии ошибок в информационной последовательности формируется нулевая синдромная последовательность; при наличии ошибок в информационной последовательности формируется ненулевая синдромная последовательность. Число ненулевых символов определяется видами порождающих полиномов и характером ошибок в канале связи. При отсутствии цикловой синхронизации ветвей коммутатора 1 формирователь 2 проверочной последовательности образует проверочную последовательность, отличную от переданной, и в формирователе 3 синдромной последовательности формируется ненулевая синдромная последовательность; в этом случае число ненулевых символов в синдромной последовательности больше. Сформированная синдромная последовательность через первый блок 4 совпадения поступает на вход порогового счетчика 5. Если же по окончании времени анализа число ненулевых символов синдромной последовательности превысит выбранный порог, то на выходе порогового счетчика 5 появится импульс, свидетельствующий об отсутствии цикловой синхронизации или ложном срабатывании цикловой синхронизации. Иг-шульсы с выхода порогового счетчика 5 поступают на вход формирователя б запрещающих сигналов, который вырабатывает импульсы сдвига, запрещающие прохождение импульсов тактовой частоты в коммутаторе 1, что соответствует перераспределению (сдвигу) ветвей инфор- . мации в коммутаторе 1. Формирователь временного интервала анализа, определяющий число ненулв. вых символов в синдромной последовательности, выпстчен в виде счетчика 8 объема выборки. Импульсы сдвига с выхода формирователя 6 запрещающих сигналов поступают одновременно .на вход блока 14 совпадения и на вход регистра 17 сдвига, тактирование которого производится импульсами с выхода счетчика 8 объема выборки. По заполнении импульсами регистра 17 сдвига мажоритарный элемент 18 производит анализ содержимого регистра 17 сдвига. Если число ненулевых символов, записанных в pe-i. гистре 17 сдвига превысит порог,- то на выходе мажоритарного элемента 18 появляется логическая единица Логическая единица высокий уро вень) с выхода мажоритарного элеме та 18 поступает одновременно на счетный вход второго счетного триггера 16, на вход инвертора 15 и на первый вход блока 12 совпадения, При этом второй счетЕГый триггер 16 устанавливается в состояние Единица (логическая единица или высокий уровень на прямом выходе) , обе печивая тем самым прохо удение импул са сдвига через блок 14 совпадения на коммутатор 1 и перераспредале ние fсдвиг) ветвей инаюрмации в ком мутаторе 1. Выходной сигнал с инвертора 15 (логический ноль или низкий уровень), поступешщий на вх блока 13 совпаденияJблокирует (запрещает) прохождение импульсов сбр са со счетчика 8 объема выборки из. установочный вход второго счетного триггера 16, Одновременно выходной сигнал ма жоритарного элемента 18 (логическа единица или высокий уровень) откры вает блок 12 совпадения и обеспечи вает прохождение импульсов сброса от счетчика 8 объема выборки на счетный вход первого счетного триг гера 9, устанавливая eio в сосгояца или высокий уровень i-iai прямом выходе триггера). Сигналом с инверсного выхода первого счетного триггера 9 запирается 4 совпадения прекращая тем caMbiivi поступление синдромной послетдовательности на вход порогового счетчика 5, а сигналом с прямого выходгь первого счетного триггера 9 отпарывается блок 10 совпадения и импульсы тактовой частоты от формирователя 7 тактовых импульсов поступают ка вход формирователя 11 временного интервала перезаписи и регистр фор мирователя 2 проверочной последовательности. Производится перезапись информации формирователя 2 проверочной последовательности от ранее .принятой информации перед началом следующего этапа поиска цикловой синхронизации. По заполнении формирователя 11 временнного интерва-ла перезаписи сигналом с его выхода первый счетный триггер 9 устанавливается в нулевое состояние (логический ноль или низкий уровень на прямом выходе , ьтульсом с прямого выхода запирается блок 10 совпадения, а сигналом с инверсного выхода открывается блок 4 совдадения, обеспечивая поступление импульсов синдромнсй последовательности на вход порогового счетчи-к а 5 о Рассмотренной алгоритм поиска повторяется при отсутствии цикловой синхронизации до установления циклового синхронизма. Таким образом, в предлагаемом устройстве цикловой синхронизации исключение синдрома из ;,- СИМЕЮЛОВ (где Wi - длина регистра сдвига формирователя 2 проверочной последовательности) из анализа синдромной последовательности происходит только лишь при наличии импульса (логической единицы) с выхода мажоритарного элемента 1В, свидетельствукнцего об отсутствии или срыве цикловой синхронизации. Следова- тельНо. исключение из анализа синдромной последовательности - символов только лишь на время перезаписи информации в формирователе 2 проверочной последовательности повыи-iaeT точность и достоверность выделения сигнала отсутствия или срыва синхронизме. При установлении цикловогсз синхронизма с выхода мажоритарного элемента 1В логический ноль (низкий уровень) поступает одновременно на счетный вход счетного триггера 16, на вход инвертора 15 и на первый вход, блока. 12 совп;хцения. Инвертированный сигнал (логическая единица или высокий уровень , поступающий на вход сброса блока 13 совпаа ения . разрешает прохождение иг-лтульсоБ сброса от счетчика В объема выборки на установочный вход счетного триггера 16, счетньл триггер IS устанавливается в нулевое состояние. Выходным сигналом (логический ноль или низкий уровень) с прямого выхода счетного триггера 16 производится блокировка прохождеьиЕ И.-,пульсов сдвига с выхода формирователя 6 запрещающих сигналов через блок 14 совпадения на управляюгдий вход коммутатора 1 . Таким образом, производится блокировка импульсов сдвига, возникающих в результате ложных сраба.тываний устройства цикловой синхронизации и обеспечивается тем самым повышение помехоустойчивости работы устройства цикловой синхронизации или удержание правильной фазы цикловой синхронизации ветвей коммутатора 1 при наличии ошибок. Одновременно выходным сигналом мажоритарного элемента 18 обеспечивается блокировка прохождения импульсов сброса от счетчика 8 объема выборки через блок 14 совпадения на счетный вход первого счетного триггера 9„ В результате этого первый

счетный триггер 9 остается в нулевом состоянии (на прямом выходе - логический ноль}. С инверсного выхода данного триггера 9 на вход блока 4 совпадения поступает логическая единица и обеспечивает прохождение на вход порогового счетчика 5 символов синдромной последовательности на всем интервале анализа.

Таким образом, исключение из анализа ft символов синдромной последовательности только лишь на время, перезаписи информации в формирователе проверочной последовательности повышает вероятность вьшеления сигнала отсутствия или срыва синхронизма.

Технико-экономическая эффективность предлагаемогоустройства заключается в том, что при ложных срабатываниях устройства цикловой синхронизации обеспечивается удержание состояния синхронизма до тех пор, пока число ложных срабатываний не превысит порог, устанавливаемый мажоритарным элементом. Благодаря этому результирующая вероятность ложных тревогйд (, уменьшится, где чис вероятность ложных тревог устройства цикловой синхронизации, tk- выбранныйпорог, т.е. обеспечивается повышение помехоустойчивости работы устройства цикловой синхрониэации заключающееся в повышении вероятности удержания правильной фазы цикловой синхронизации ветвей коммутатора при наличии ошибок.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цикловой синхронизации при двоичном сверточном кодировании | 1981 |

|

SU1008921A1 |

| Устройство для цикловой синхронизации порогового декодера | 1983 |

|

SU1124441A1 |

| Устройство цикловой синхронизации порогового декодера | 1987 |

|

SU1483661A2 |

| Устройство цикловой синхронизации | 1984 |

|

SU1197122A1 |

| Сверточный кодек с алгоритмом порогового декодирования | 1985 |

|

SU1327296A1 |

| Устройство для устранения неопределенности дискретнофазовой модуляции | 1983 |

|

SU1095428A1 |

| Устройство для декодирования сверточного кода | 1984 |

|

SU1213491A1 |

| Кодек несистематического сверточного кода | 1990 |

|

SU1714812A1 |

| Пороговый декодер сверточного кода | 1986 |

|

SU1443180A1 |

| Пороговый декодер сверточного кода | 1982 |

|

SU1078654A1 |

УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИН.ХРОНИЗАЦИИ ПРИ ДВОИЧНОМ СВЕРТОЧНОМ КОДИРОВАНИИ, содержащее последовательно соединенные коммутатор, формирователь проверочной последовательности, формирователь синдромной последовательности, первый блок совпадения, пороговый счетчик и формирователь запрещающих сигналов, к второму входу которого подключен формирователь тактовых имрьульсов через счетчик объема выборки, выход которого подсоединен к второму входу порогового счетчика, последовательно соединенные счетный триггер, второй блок совпадения и формирователь временного интервала перезаписи, при этом второй вход второго блока совпадения обьединен с входом счетчика объема выборки и подключен к информационному входу коммутатора, второй вход которого является входсм устройства, второй выход коммутатора подсоединен к второму входу формирователя синдромной последовательности. а к второму входу первого блока совпадения подключен инверсный выход счетного триггера, отличающееся тем, что, с целью повышения помехоустойчивости при наличии пакетов сшибок, введены третий блок совпадения и последовательно соединенные регистр сдвига, мажоритарный элемент, инвертор, четвертый блок совпадения, дополнительный счетный триггер и пятый блок.совпадения, выход которого подсоединен к дополнительному входу к оммутатора, а второй вход объединен с первым входом регистра сдвига и подключен к выходу формирователя запрещающего сигнала, второй вход регистра сдвига объединен с вторым входом четвертого (Л блока совпадения, первым входом третьего блока совпадения, и подключен к выходу счетчика объема вы-борки, при этом второй вход третьего блока совпадения объединен со счетным входом дополнительного счетного триггера и подключен к выходу мажоритарного элемента, а инверсный выход дополнительного счетного триггера подключен к своему информационному входу, .причем выход формирователя временного интервала перезаписи подсоединен к установочному входу счетного триггера, счетный вход которого подключен к выходу третьего блока совпадения, а инверсный выходу подсоединен к своему информационному входу.

f( корректору ountiw

| ,1 | |||

| Устройство для цикловой синхронизации при двоичном сверточном кодировании | 1974 |

|

SU496690A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке № 3277516/18-09, .кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1983-12-23—Публикация

1982-10-25—Подача