() УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СМЕЩЕНИЯ КАДРОВ В ТЕЛЕВИЗИОННОМ СИГНАЛЕ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство компенсации сигнала дефектов киноленты | 1987 |

|

SU1494247A1 |

| Устройство компенсации сигнала царапин кинопленки | 1988 |

|

SU1536521A2 |

| Устройство компенсации сигнала царапин кинопленки | 1986 |

|

SU1392635A1 |

| Система передачи телевизионногоСигНАлА | 1979 |

|

SU794774A1 |

| Устройство компенсации сигнала дефектов киноленты | 1985 |

|

SU1322503A2 |

| Телевизионный координатор | 1983 |

|

SU1109956A1 |

| Устройство для бинарного квантования телевизионного видеосигнала | 1983 |

|

SU1129745A1 |

| Формирователь сигнала оценки дефектных элементов изображения в телекинопроекционной системе | 1984 |

|

SU1233300A1 |

| СПОСОБ ПРЕОБРАЗОВАНИЯ ЦИФРОВОГО СИГНАЛА ИЗОБРАЖЕНИЯ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2004 |

|

RU2287909C2 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

1

Изобретение относится к телевидению и может использоваться в автоматических телевизионных системах распознавания образов.

Известно устройство измерения смещения кадров в телевизионном сигнале, содержащее первый блок задержки, второй блок задержки, первый выход которого через последовательно соединенные первый умножитель, первый блок запрета и первый интегратор подключен к первому входу блока определения максимума сигнала, а второй выход второго блока задержки через последовательно соединенные второй умножитель, второй блок запрета и второй интегратор соединен с вторым входом блока определения максимума сигнала, а также компаратор, первый вход которого подключен к первому входу второго блока задержки, а второй вход компаратрра соеди.нен с первым входом третьего блока задержки, причем выход компаратора

подключен к вторым входам первого и второго блока запрета, а также элемент ИЛИ, первый и второй входы которого подключены соответственно к первому и второму входам блока определения максимума сигнала, а выход элемента ИЛИ соединен с вторыми входами первого и второго интеграторов, причем вход первого блока задержки предназначен для подачи телевизионно10го сигнала 1 Д.

Однако устройство имеет сравнительно невысокое быстродействие.

Цель изобретения - повышение быстродействия .

15

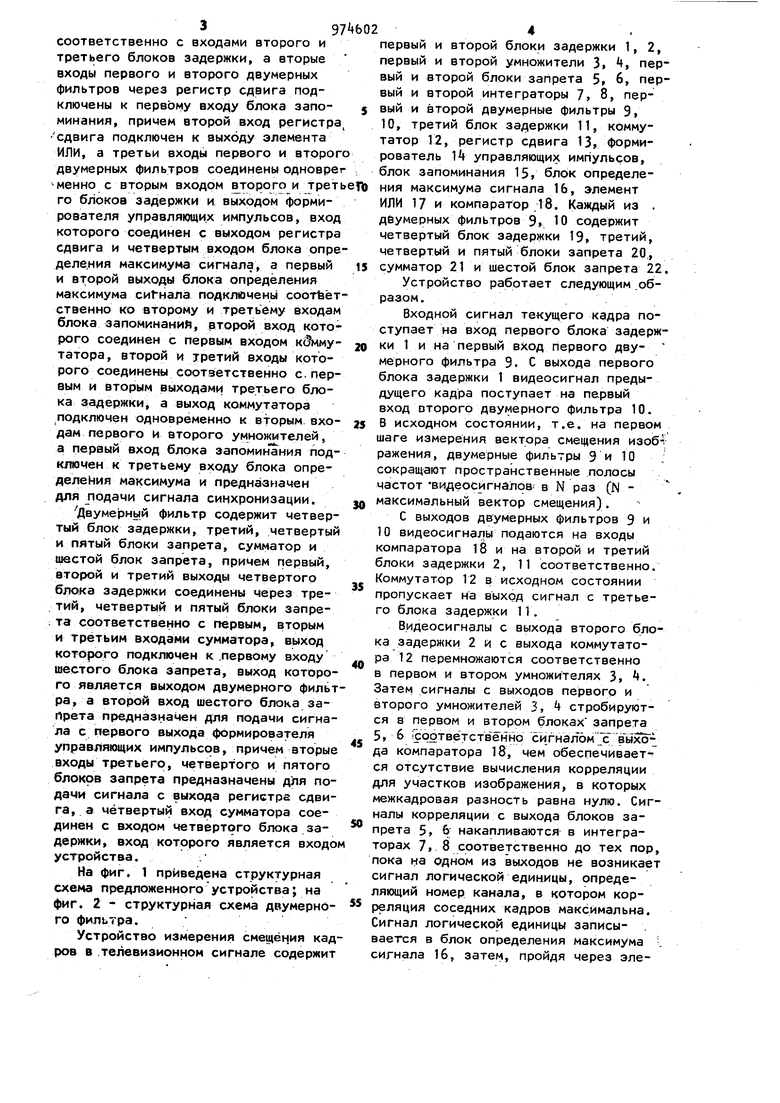

Для этого в устройство введены первый и второй двумерные фильтры, регистр сдвига, формирователь управляющих импульсов, коммутатор и блок запоминания, причем первые входы

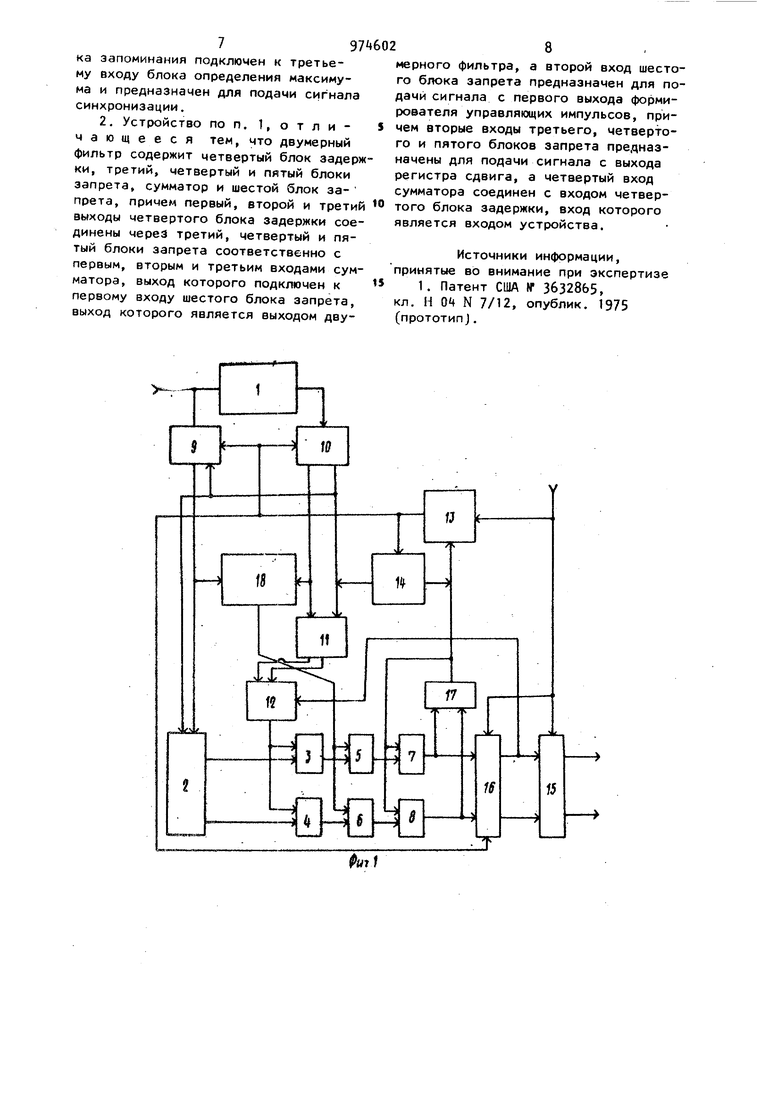

20 первого и второго двумерных фильтров соединены соответственно с входом и выходом первого блока задержки, а выходы двумерных фильтров соединены 397 соответственно с входами второго и третьего блоков задержки, а вторые входы первого и второго двумерных фильтров через регистр сдвига подключены к первому входу блока запоминания, причем второй вход регистра сдвига подключен к выходу элемента ИЛИ, а третьи входы первого и второго двумерных фильтров соединены одноврег -менно с вторым входом второго и треть го блоков задержки и выходом формирователя управляющих импульсов, вход которого соединен с выходом регистра сдвига и четвертым входом блока опре деле.ния максимума сигнала, а первый и второй выходы блока определения максимума сигнала подключены соотЬёт ственно ко второму и третьему входам блока запоминаний, второй вход которого соединен с первым входом кЗммутатора, второй и третий входы которого соединены соотзетственно с.первым и вторым выходами третьего блока задержки а выход коммутатора подключен одновременно к вторым входам первого и второго умножителей, а первый вход блока запомина ния подключен к третьему входу блока определения максимума и предназначен для подачи сигнала синхронизации. Двуме1эный фильтр содержит четвертый блок задержки, третий, четвертый и пятый блоки запрета, сумматор и 111естой блок запрета, причем первый, второй и третий выходы четвертого блока задержки соединены через третий, четвертый и пятый блоки запрета соответственно с первым, вторым и третьим входами сумматора, выход которого подключен к .первому входу шестого блока , выход которого является выходом двумерного фильт ра, а второй вход шестого блока запрета предназначен для подачи сигнала с первого выхода формирователя управляющих импульсов, причем вторые входы третьего, четвертого и пятого блоков запрета предназначены для подачи сигнала с выхода регистра сдвига, а четвертый вход сумматора соединен с входом четвертого задержки, вход которого является входо устройства. : На фиг, 1 приведена структурная схема предложенного устройства; на фиг. 2 - структурная схема двумерного фильтра. Устройство измерения смеи|ёния кад в .телевизионном сигнале содержит первый и второй блоки задержки 1, 2, первый и второй умножители 3 , первый и второй блоки запрета 5, 6, первый и второй интеграторы 7, 8, первый и второй двумерные фильтры 9, 10, третий блок задержки 11, коммутатор 12, регистр сдвига 13, формирователь Т управляющих импульсов, блок запоминания 15, блЬк определения максимума сигнала 16, элемент ИЛИ 17 и компаратор 18, Каждый из . дбумерных фильтров 9 Ю содержит четвертый блок задержки 19, третий, четвертый и пятый блоки запрета 20, сумматор 21 и шестой блок запрета 22, Устройство работает следующим образом. Входной сигнал текущего кадра поступает на вход первого блока задержки 1 и на первый вход первого двумерного фильтра 9. С выхода первого блока задержки 1 видеосигнал предыдущего кадра поступает на первый вход DTOporo двумерного фильтра 10, В исходном состоянии, т,е. на первом шаге измерения вектора смещения изоб-i ражения, двумерные фильтры 9 и 10 сокращают пространственные .полосы частот видеосигналов в N раз (N максимальный вектор смещения). С выходов двумерных фильтров 9 и 10 видеосигналы подаются на входы компаратора 18 и на второй и третий блоки задержки 2, 11 соответственно. Коммутатор 12 в исходном состоянии пропускает на выход сигнал с третьего блока задержки 11. Видеосигналы с выхода второго блока задержки 2 и с выхода коммутатора 12 перемножаются соответственно в первом и втором умножителях 3, , Затем сигналы с выходов первого и второго умножителей 3, стробируются в первом и втором блоках запрета 5, 6 соответствё ннр сигналом сГвыхода компаратора 18, чем обеспечивает ся отсутствие вычисления корреляции для участков изображения, в которых межкадровая разность равна нулю. Сигналы корреляции с выхода блоков запрета 5, 6 накапливаются в интеграторах 7, 8 соотвеуственно до тех пор, пока на одном из выходов не возникает сигнал логической единицы, определяющий номер канала, в котором корреляция соседних кадров максимальна. Сигнал логической единицы записы- . вается в блок определения максимума . сигнала 16, затем, пройдя через элемент ИЛИ 17i устанавливает в нулевое состояние интеграторы 7, 8 и сдвигает единицу Hf один разряд в регистре сдвига 13. Регистр сдвига 13 переклю чает формирователь 14, генерировавший импульсы со скважностью N, на более высокую частоту следования. Вместе с тем сигналами с выхода регистра сдвига 13 переключаются двумерные фильтры 9 и 10, полоса пропус кания которых соответственно увеличи вается. На первом выходе блока 16 формиру ется позиционный(КОД, соответствующий первой грубой оценке вектора сме щения изображения. Этот сигнал поступает на коммутатор 12, который обеспечивает прохождение с третьего блока задержки 11 видеосипнала; с соответственно более длительной задерж кой. Этим заканчивается переход устройства к второму этапу измерения вектора смещения. Работа части уст ройства, включающая компаратор 1, . второй и третий блоки задержки 2, 11 первый и второй умножители 3, , пер вый и второй блоки запрета 5, 6 интеграторы 7. 8 элемент ИЛИ 17, на всех этапах измерения вектора смещения одинакова. После окончания последнего .этапа измерения значение вектора смещения кадровым синхронизирующим импульсом переписывается из блока определения максимума сигнала 16 в блок 15, в ко тором хранится в течение следующего кадра для использования при компенсации смещения изображения.. Предложенное устройство позволяет в широком диапазоне векторов смещени изображений производить автоматичес-. кое измерение смещения рекурсивным методом, основанным на принципе полихотомии, и обеспечивает уменьшение затрат на производство и эксплуатацию автоматических телевизионных сис тем широкого класса. Формула изобретения . 1. Устройство для измерения смещения кадров в телевизионном сигнале соде|эжащее первый блок задержки, вто рой блок задержки, первый выход которого через последовательно соединенные первый умножитель, первый блок запрета и первый интегратор под ключен к первому входу блока определения максимума сигнала, а второй выход второго блока задержки через последовательно соединенные второй умножитель, второй блок запрета и второй интегратор соединен с вторым входом блока определения максимума сигнала, а также компаратор, первый вход которого подключен.к первому входу второго блока задержки, а второй вход компаратора соединен с первым входом третьего блока задержки, причем выход компаратора подключен к вторым входам первого и второго блока запрета, а также элемент ИЛИ, первый и второй входы которого подключены соответственно к первому и второму входам блока определения максимума сигнала, а выход элемента ИЛИ соединен с вторыми входами первого и второго интеграторов, причем вход первого блока задержки предназначен для подачи телевизионного сигнала, отличающееся тем, что,с целью повышения быстродействия, введены первый и второй двумерные фильтры, регистр сДвкга, формирователь управляющих импульсов, коммутатор и блок запоминания, причем первые входы первого и второго двумерных фильтров соединены соответственно с входом и выходом первого блока задержки, а выходы двумерных фильтров соединены соответственно с входами второго и третьего блоков задержки, а вторые входы первого и второго двумерных фильтров через регистр сдвига подключены к первому входу блока запоминания, причем второй вход регистра сдвига подключен к выходу элемента ИЛИ, а третьи входы первого и второго двумерных фильтров соединены одновременно с вторым входом второго и третьего блоков задержки и выходом формирователя управляющих импульсов, вход которого соединен с выходом регистра сдвига и четвертым входом блока определения максимума сигнала, а первый и второй выходы блока определения максимума сигнала подключены соответственно к второму и третьему входам блока запоминания , второй вход которого соеинен с первым входом коммутатора, второй и третий входы которого соединены соответственно с первым и вторым выходами третьего блока задержки, а ыход коммутатора подключен одновреенно к вторым входам первого и втоoro умножителей, а первый вход блока запоминания подключен к третьему входу блока определения максимума и предназначен для подачи сигнала синхронизации. 2. Устройство по п. 1, о т л и чающееся тем, что двумерный фильтр содержит четвертый блок задержки, третий, четвертый и пятый блоки запрета, сумматор и шестой блок запрета, причем первый, второй и третий выходы четвертого блока задержки соединены через третий, четвертый и пятый блоки запрета соответственно с вторым и третьим входами сумпервым, выход которого подключен к матера, первому входу шестого блока запрета, выход которого является выходом двуЭ7( 8 мерного фильтра, а второй вход шестого блока запрета предназначен для подачи сигнала с первого выхода формирователя управляющих импульсов, причем вторые входы третьего, четвертого и пятого блоков запрета предназначены для подачи сигнала с выхода регистра сдвига, а четвертый вход сумматора соединен с входом четвертого блока задержки, вход которого является входом устройства, Источники информации, принятые во внимание при экспертизе 1. Патент США № 3632865, кл. Н Oi N 7/12, опублик. 1975 (прототип.

20

Jsk.

f

f f

20

20

f

fN /

Фиг.2

Авторы

Даты

1982-11-15—Публикация

1979-09-17—Подача