(5) РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распределения импульсов | 1984 |

|

SU1205135A1 |

| Счетное устройство | 1985 |

|

SU1256195A1 |

| Распределитель импульсов | 1986 |

|

SU1309297A1 |

| Устройство для защиты и автоматического отключения потребителя | 1985 |

|

SU1339722A1 |

| Устройство для распределения импульсов | 1980 |

|

SU903846A1 |

| Счетное устройство | 1986 |

|

SU1368981A1 |

| Многопрограмный распределитель импульсов | 1987 |

|

SU1443163A1 |

| Распределитель импульсов | 1979 |

|

SU809137A1 |

| Устройство разделения и синхронизации сигналов | 1984 |

|

SU1211863A1 |

| Устройство для измерения периода | 1987 |

|

SU1465872A1 |

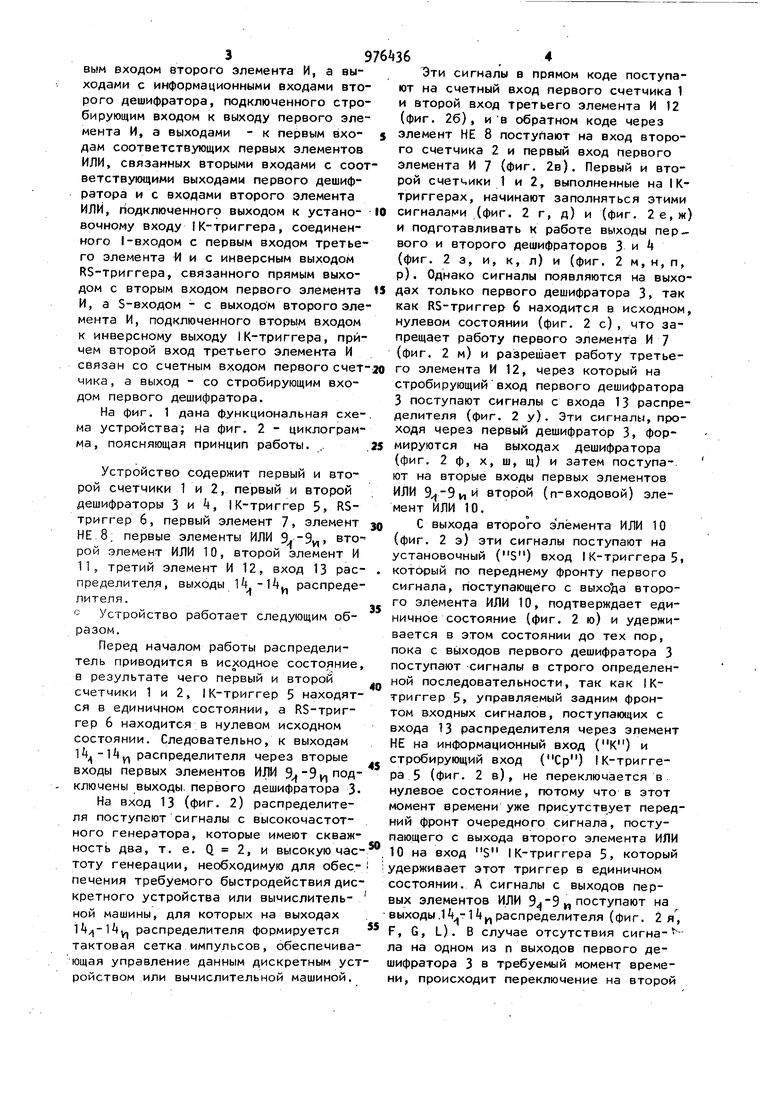

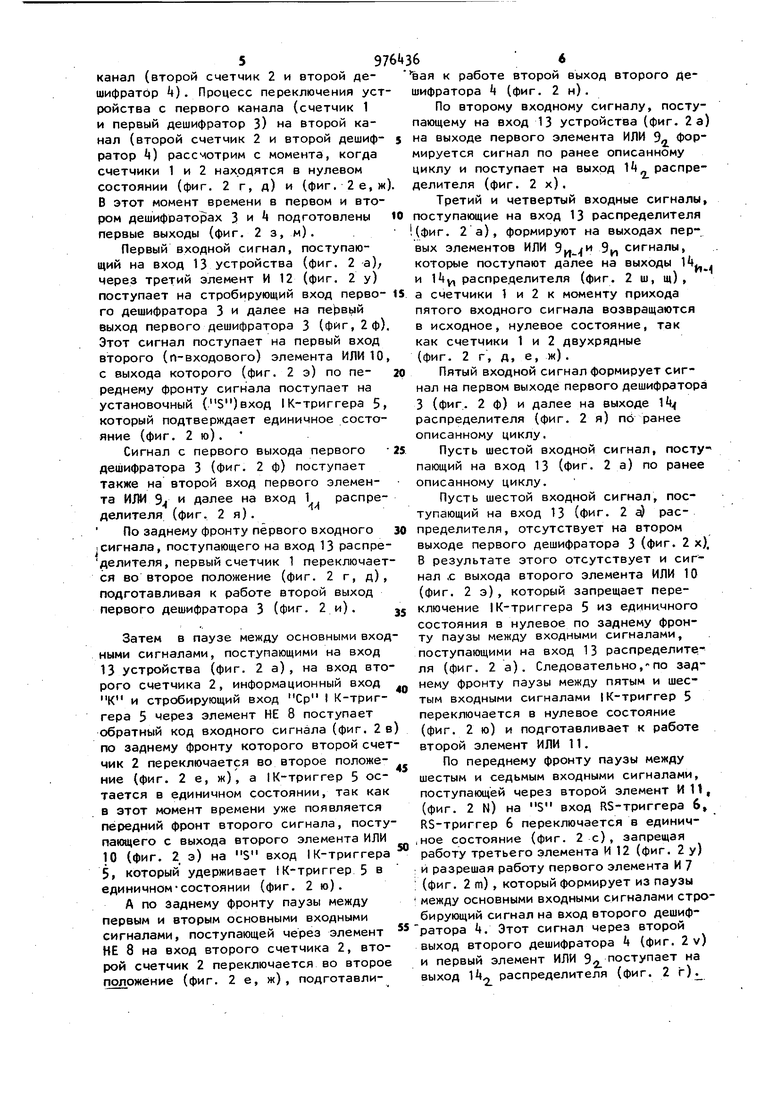

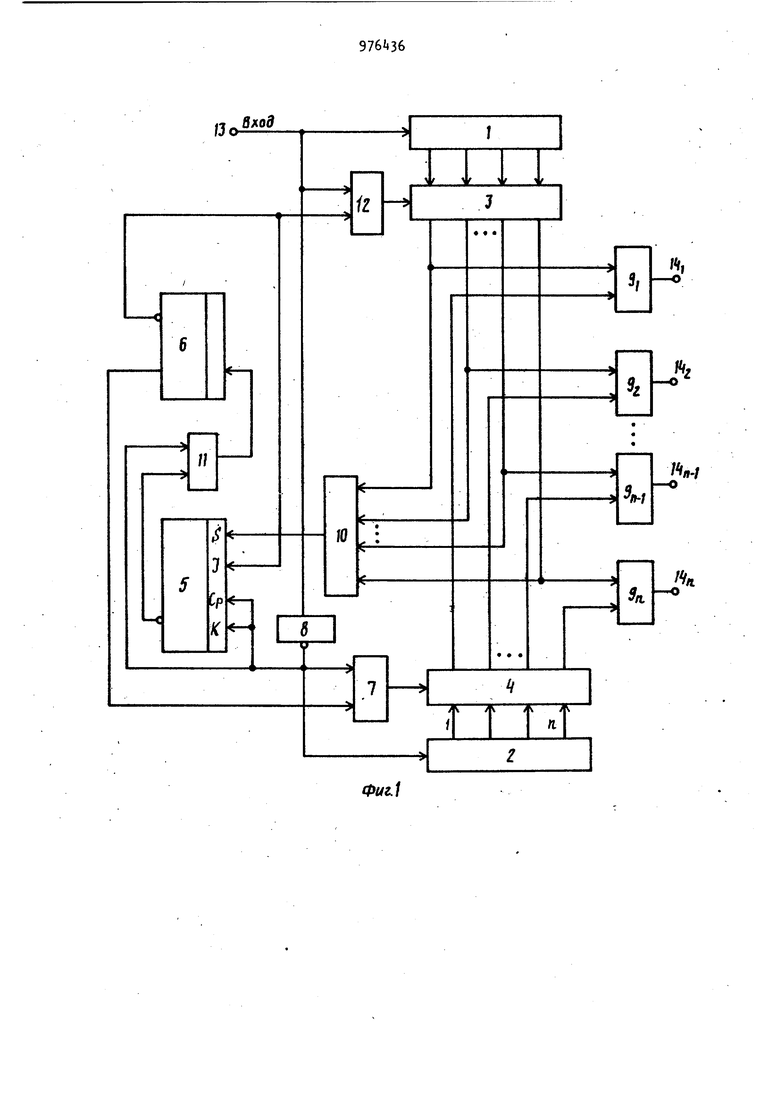

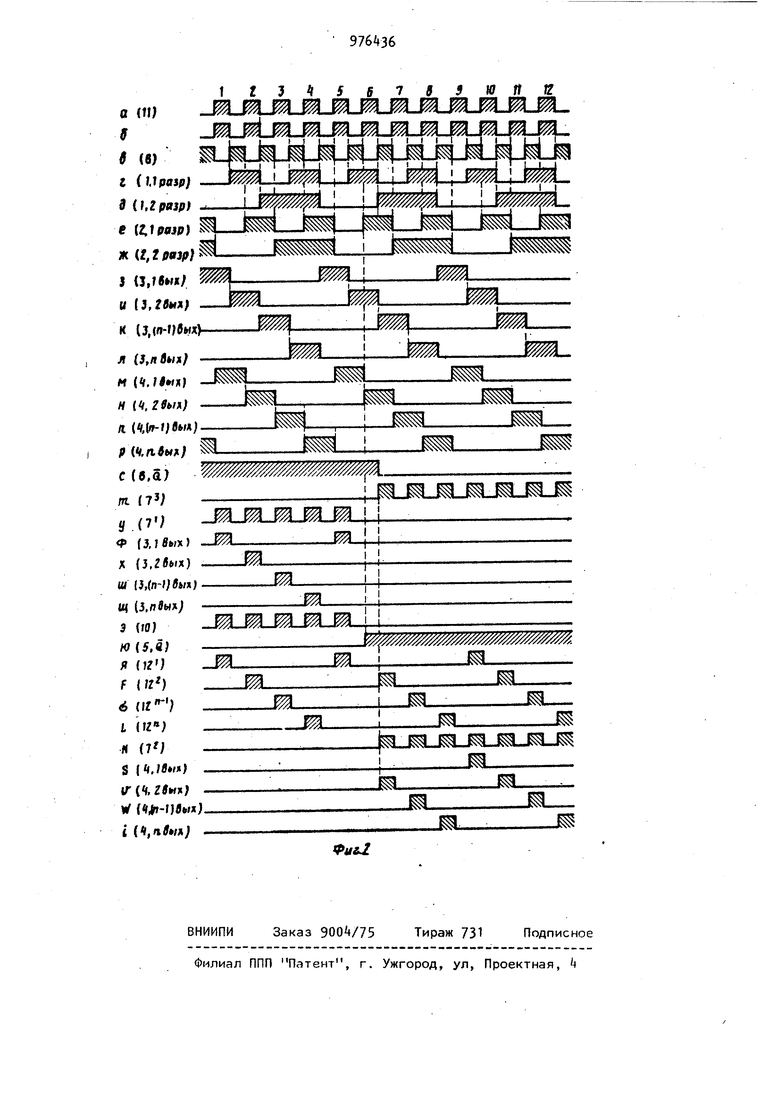

Изобретение относится к вычислительной технике и телемеханике и может быть использовано при построении распределителя тактовых импульсов для дискретных устройств и вычислительных машин. Известен многоканальный распределитель импульсов, содержащий триггеры и элемент И 1 }. Недостатком известного устройства является наличие двухтактной системы управления, что усложняет устройство так как требует наличия двойного количества триггеров и сложного генератора импульсов, обеспечивающего двухтактную последовательность импульсов. Наиболее близким техническим решением к изобретению является распределитель импульсов, содержащий первый счетный блок, вход которого соединен с входом элемента НЕ и подключен к входу устройства, а выходы первого счетного блока подключены к информационным входам первого дешифратора, второй дешифратор j 2Т. Распределитель не обеспечивает нормальную работу распределителя импульсов при выходе из строя элементов в счетном блоке или дешифраторе, что снижает надежность работы распределителя импульсов. Целью изобретения является повышение надежности устройства. Поставленная цель достигается тем, что в распределитель импульсов, содержащий первый и второй дешифраторы, первый счетчик, подключенный выходами к информационным входам первого дешифратора, а счетным входом - к входу элемента НЕ, введены RS-триггер, IКтриггер, три элемента И, по числу выходов распределителя - первые элементы ИЛИ, второй элемент ИЛИ и второй счетчик, соединенный счетным входом с входом элемента НЕ, с первым входом первого элемента И, со стробирующим входом и К-входом 1К-триггера и спер39вым входом второго элемента И, а выходами с информационными входами второго дешифратора, подключенного стробирующим входом к выходу первого элемента И, а выходами - к первым входам соответствующих первых элементов ИЛИ, связанных вторыми входами с соот ветствующими выходами первого дешифратора и с входами второго элемента ИЛИ, подключенного выходом к установочному входу 1К-триггера, соединенного I-входом с первым входом третьего элемента И и с инверсным выходом RS-триггера, связанного прямым выходом с вторым входом первого элемента И, а S-входом - с выходом второго элемента И, подключенного вторым входом к инверсному выходу 1К-триггера, причем второй вход третьего элемента И связан со счетным входом первого счетмика, а выход - со стробирующим входом первого дешифратора. На фиг. 1 дана функциональная схема устройства; На фиг, 2 - циклограмма, поясняющая принцип работы. .. Устройство содержит первый и второй счетчики 1 и 2, первый и второй дешифраторы 3 и i, 1К-триггер 5, RSтриггер 6, первый элемент 7, элемент НЕ 8, первые элементы ИЛИ Э.-Эу,, второй элемент ИЛИ 10, второй элемент И 11, третий элемент И 12, вход 13 распределителя, выходы 1.( распределителя. - Устройство работает следующим образом. Перед началом работы распределитель приводится в исходное состояние, в результате чего первый и второй счетчики 1 и 2, 1К-триггер 5 находятся в единичном состоянии, а RS-триггер 6 находится в нулевом исходном состоянии. Следовательно, к выходам 1 - И у распределителя через вторые входы первых элементов ИЛИ подключены ВЫХОДЫ- первого дешифратора 3На вход 13 (фиг, 2) распределителя поступают сигналы с высокочастотного генератора, которые имеют скважность два, т. е. Q 2, и высокую частоту генерации, необходимую для обеспечения требуемого быстродействия дискретного устройства или вычислительной машины, для которых на выходах распределителя формируется тактовая сетка импульсов, обеспечивающая управление данным дискретным уст ройством или вычислительной машиной. 36 . 4 Эти сигналы в прямом коде поступают на счетный вход первого счетчика 1 и второй вход третьего элемента И 12 (фиг. 26), ив обратном коде через элемент НЕ 8 постуЛают на вход второго счетчика 2 и первый вход первого элемента И 7 (фиг. 2в), Первый и второй счетчики 1 и 2, выполненные на IКтриггерах, начинают заполняться этими сигналами (фиг. 2 г, д) и (фиг, 2е,ж) и подготавливать к работе выходы первого и второго дешифраторов 3 и (фиг, 2 3, и, к, л) и (фиг. 2 м,н,п, р). Однако сигналы появляются на выходах только первого дешифратора 3, так как RS-триггер 6 находится в исходном, нулевом состоянии (фиг. 2 с) , что запрещает работу первого элемента И 7 (фиг. 2 м) и разрешает работу третьего элемента И 12, через который на стробирующийвход первого дешифратора 3 поступают сигналы с входа 13 распределителя (фиг. 2 у). Эти сигналы, проходя через первый дешифратор 3, формируются на выходах дешифратора (фиг. 2 ф, X, ш, щ) и затем поступа-. ют на вторые входы первых элементов ИЛИ sтopioй (п-входовой) элемент ИЛИ 10. С выхода второго элемента ИЛИ 10 (фиг. 2 э) эти сигналы поступают на установочный (S) вход IК-триггера 5 который по переднему фронту первого сигнала, поступающего с выхода второго элемента ИЛИ 10, подтверждает единичное состояние (фиг. 2 ю) и удерживается в этом состоянии до тех пор, пока с выходов первого дешифратора 3 поступают сигналы в строго определенной последовательности, так как 1Ктриггер 5, управляемый задним фронтом входных сигналов, поступающих с входа 13 распределителя через элемент НЕ на информационный вход (К) и стробирующий вход (Ср) IК-триггера 5 (фиг, 2 в), не переключается в нулевое состояние, потому что в этот момент времени уже присутствует передний фронт очередного сигнала, поступающего с выхода второго элемента ИЛИ ,-. - - 10 на вход S 1К-триггера 5, который удерживает этот триггер в единичном состоянии. А сигналы с выходов первых элементов ИЛИ выходы.Т+ -Н распределителя (фиг. 2 я , F, G, L). В случае отсутствия сигна- ла на одном из п выходов первого дешифратора 3 в требуемый момент времени, происходит переключение на второй 597 канал (второй счетчик 2 и второй дешифратор 4) , Процесс переключения уст ройства с первого канала (счетчик 1 и первый дешифратор 3) на второй канал (второй счетчик 2 и второй дешифратор Ц) рассмотрим с момента, когда счетчики 1 и 2 находятся в нулевом состоянии (фиг. 2 г, д) и (фиг. 2 е, ж В этот момент времени в первом и втором дешифраторах 3 и А подготовлены первые выходы (фиг, 2 з, м). Первый входной сигнал, поступающий на вход 13 устройства (фиг. 2 а); через третий элемент И 12 (фиг. 2 у) поступает на стробирующий вход первого дешифратора 3 и далее на первый выход первого дешифратора 3 (фиг, 2ф) Этот сигнал поступает на первый вход второго (п-входового) элемента ИЛИЮ с выхода которого (фиг. 2 э) по переднему фронту сигнала поступает на установочный (5)вход 1К-триггера 5, который подтверждает единичное состояние (фиг. 2 ю). Сигнал с первого выхода первого дешифратора 3 (фиг. 2 ф) поступает также на второй вход первого элемента ИШ 9 и далее на вход 1 распределителя (фиг. 2 я). По заднему фронту первого входного (Сигнала, поступающего на вход 13 распределителя, первый счетчик 1 переключает ся во второе положение (фиг. 2 г, д), подготавливая к работе второй выход первого дешифратора 3 (фиг. 2 и). Затем в паузе между основными вход ными сигналами, поступающими на вход 13 устройства (фиг. 2 а), на вход вто рого счетчика 2, информационный вход К и стробирующий вход Ср I К-триггера 5 через элемент НЕ 8 поступает обратный код входного сигнала (фиг. 2 в по заднему фронту которого второй счет чик 2 переключается во второе положение (фиг. 2 е, ж), а |К-триггер 5 остается в единичном состоянии, так как в этот момент времени уже появляется передний фронт второго сигнала, посту пающего с выхода второго элемента ИЛИ 10 (фиг. 2 э) на S вход 1К-триггера 5, который удерживает 1К-триггер 5 в единичномСОСТОЯНИИ (фиг. 2 ю). А по заднему фронту паузы между первым и вторым основными входными сигналами, поступающей через элемент НЕ 8 на вход второго счетчика 2, второй счетчик 2 переключается во второе положение (фиг. 2 е, ж), подготавли6 6 вая к работе второй выход второго дешифратора 4 (фиг. 2 н) . По второму входному сигналу, поступающему на вход 13 устройства (фиг. 2 а) на выходе первого элемента ИЛИ Э формируется сигнал по ранее описанному циклу и поступает на выход Т распределителя (фиг. 2 х). Третий и четвертый входные сигналы, поступающие на вход 13 распределителя (фиг. 2 а), формируют на выходах первых элементов ИЛИ 9j сигналы, которые поступают далее на выходы 14 и , распределителя (фиг. 2 ш, щ) , а счетчики 1 и 2 к моменту прихода пятого входного сигнала возвращаются в исходное, нулевое состояние, так как счетчики 1 и 2 двухрядные (фиг. 2 г, д, е, ж). Пятый входной сигнал формирует сигнал на первом выходе первого дешифратора 3 (фиг. 2 ф) и далее на выходе 14 распределителя (фиг. 2 я) по ранее описанному циклу. Пусть шестой входной сигнал, посту пающий на вход 13 (фиг. 2 а) по ранее описанному циклу. Пусть шестой входной сигнал, поступающий на вход 13 (фиг. 2 д) распределителя, отсутствует на втором выходе первого дешифратора 3 (фиг. 2 х), В результате этого отсутствует и сигнал .с выхода второго элемента ИЛИ 10 (фиг. 2 э), который запрещает переключение |К-триггера 5 из единичного состояния в нулевое по заднему фронту паузы между входными сигналами, поступающими на вход 13 распределителя (фиг. 2 а). Следовательно,ПО заднему фронту паузы между пятым и шестым входными сигналами |К-триггер 5 переключается в нулевое состояние (фиг. 2 ю) и подготавливает к работе второй элемент ИЛИ 11. По переднему фронту паузы между шестым и седьмым входными сигналами, поступающей через второй элемент ИИ, (фиг. 2 N) на S вход RS-триггера 6, RS-триггер 6 переключается в единичное состояние (фиг. 2с), запрещая работу третьего элемента И 12 (фиг. 2 у) и разрешая работу первого элемента И 7 (фиг. 2 т) , который формирует из паузы между основными входными сигналами стробирующий сигнал на вход второго дешифратора 4. Этот сигнал через второй выход второго дешифратора k (фиг. 2v) и первый элемент ИЛИ 9. о упает на выход распределителя (фиг. 2 г)

С этого момента основными сигналами, поступающими на выходы распределителя, нвляются паузы (фиг. 26) между сигналами, поступающими на вход 13 распределителя (фиг. 2 а). По переднему фронту этих сигналов подтверждается единичное состояние RS-триггера 6 (фиг. 2 с), а ло заднему фронту - нулевое состояние 1К-триггера 5Последующие выходные сигналы формируются на соответствующих выходах l --lt (фиг. 2 я,Р, G, L) устройства по ранее описанному циклу.

Предложенное техническое решение также может быть использовано и при построении распределителя импульсов с любым количеством разрядов в счетчиках 1 и 2,и, следовательно, ,с любым количеством выходов в каждом дешифраторе, обеспечивая требуемое количество выходов устройства.

Использование предлагаемого устройства по сравнению с известными повышает надежность работы устройства, так как обеспечивает нормальную, работу устройства при выходе из строя первого канала (первый счетчик и первый дешифратор), потому что осуществляется переключение на второй канал (второй счетчик и второй дешифратор).

Формула изобретения

Распределитель импульсов, содержащий первый и второй дешифраторы, первый счетчик, подключенный выходами к информационным входам первого дешифратора, а счетным входом - к входу

элемента НЕ, отличающийся тем, что, с целью повышения надежности, в него введены RS-триггер, 1Ктрйггер, три элемента И, по числу выходов распределителя - первые элементы ИЛИ, второй элемент ИЛИ и второй счетчик, соединенный счетным входом с входом элемента НЕ, с первым входом первого элемента И, со стробирующим входом и К-входом I К-триггера и с первым входом второго элемента И, а выходами - с информационными входами второго дешифратора , подключенного стробируюМим входом к выходу пер.вого элемента И, а выходами - к первым входам соответствующих первых элементов ИЛИ, связанных вторыми входами с соответствующими выходами первого дешифратора и с входами второго элемента ИЛИ, подключенного выходом к установочному входу 1К-триггера, соединенного I-входом с первым входом третьего элемента И и с инверсным выходом RS-триггера, связанного прямым выходом с вторым входом первого элемента И, а S-входом - с выходом второго элемента И, подключенного вторым входом к инверсному выходу К-триггера, причем второй вход третьего элемента И связан со счетным входом первого счетчика, а выход - со стробирующим входом первого дешифратора.

Источники информации, принятые во внимание при экспертизе

1, Авторское свидетельство СССР № 38735, кл. G 06 F 1/0, 1970.

2i Авторское свидетельство СССР по заявке (Р 277 678/2, кл. G Об F 1/0, 1979 (прототип).

вход

13 О

/

ГО

f W W

/V/

-г f i t i

fл

t 45ST89lOtt1Z

...Ж

-NJ

ттЫ

Ш

.Ж.

.

Ж

ж.

-Ш-Ш-ШJ

.

Ш.

§si

.Lto I1 ILI

A%$y gjite

Р-Ш-ЖЖ-ЖЖ

%

p.

-Ш

J

.«.-Ш- Ж-Ш-Щ

ж.

.

m

Авторы

Даты

1982-11-23—Публикация

1981-05-11—Подача