(54) УСТРОЙСТВО ДЛЯ РАСПРЕДЕЛЕНИЯ ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Распределитель импульсов | 1979 |

|

SU809137A1 |

| Устройство для распределения импульсов | 1984 |

|

SU1205135A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1188736A1 |

| Распределитель импульсов | 1981 |

|

SU976436A1 |

| Устройство для синхронизации вычислительной системы | 1982 |

|

SU1068921A1 |

| Устройство для приема последовательного кода | 1986 |

|

SU1390625A2 |

| Устройство для контроля многоканального аппарата магнитной записи | 1986 |

|

SU1420615A1 |

| Устройство защиты от дребезга | 1978 |

|

SU813727A1 |

| Устройство для синхронизации блоков памяти | 1986 |

|

SU1439566A1 |

| Устройство для контроля профессиональных навыков оператора автоматизированных систем управления | 1984 |

|

SU1201864A1 |

1

Изобретение относится к вычислительной технике и телемеханике и может быть применено при построении распределителей тактовых импульсов для дискретных устройств и вычислительных машин.

Известно распределительное устройство, содержащее генератор импульсов, триггеры, импульсные делители частоты, матричный диодный дешифратор 1.

Недостатком известного устройства является сложная схема и большое количество элементов.

Наиболее близким к предлагаемому техническим решением является многоканальный распределитель импульсов, содержащий счетчик, вход.которого соединен со входом устройства, а выходы подключены к информационным входам дешифратора 2.

Данное устройство обладает простотой схемного решения и малым количеством элементов.

Однако оно не обеспечивает нормальную работу распределителя импульсов при выходе из строя элементов в счетчике, блоке или дешифраторе, что снижает надежность работы распределителя импульсов.

Цель изобретения - повышение надежности работы устройства.

Указанная цель достигается тем, что устройство для распределения импульсов, содержащее первый счетчик и первый дешифратор, причем выходы разрядов первого счетчика соединены с информационными входами первого дешифратора, содержит второй счетчик, второй дешифратор, триггер, элементы И, И-НЕ, многовходовой элемент ИЛИ, группу двувходовых элементов 14ЛИ,

10 элемент задержки, причелГ выходы разрядов второго счетчика соединены с информационными входами второго дешифратора, первые входы п двувходовых элементов ИЛИ группы соединены соответственно с выходами первого дешифратора (п - количество выходов первого и второго дешифраторов), вторые входы двувходовых элементов ИЛИ группы с первого по (п-1)-й соединены с выходами второго дешифратора со второго по п-й соответственно, первый выход второго

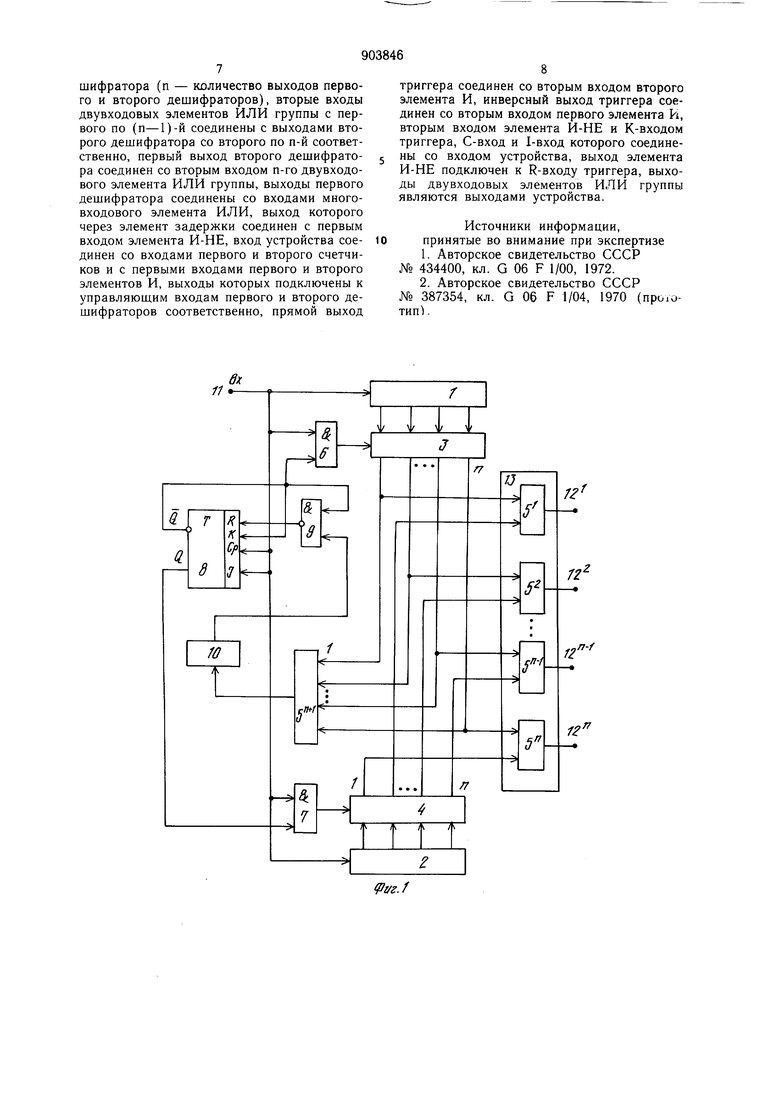

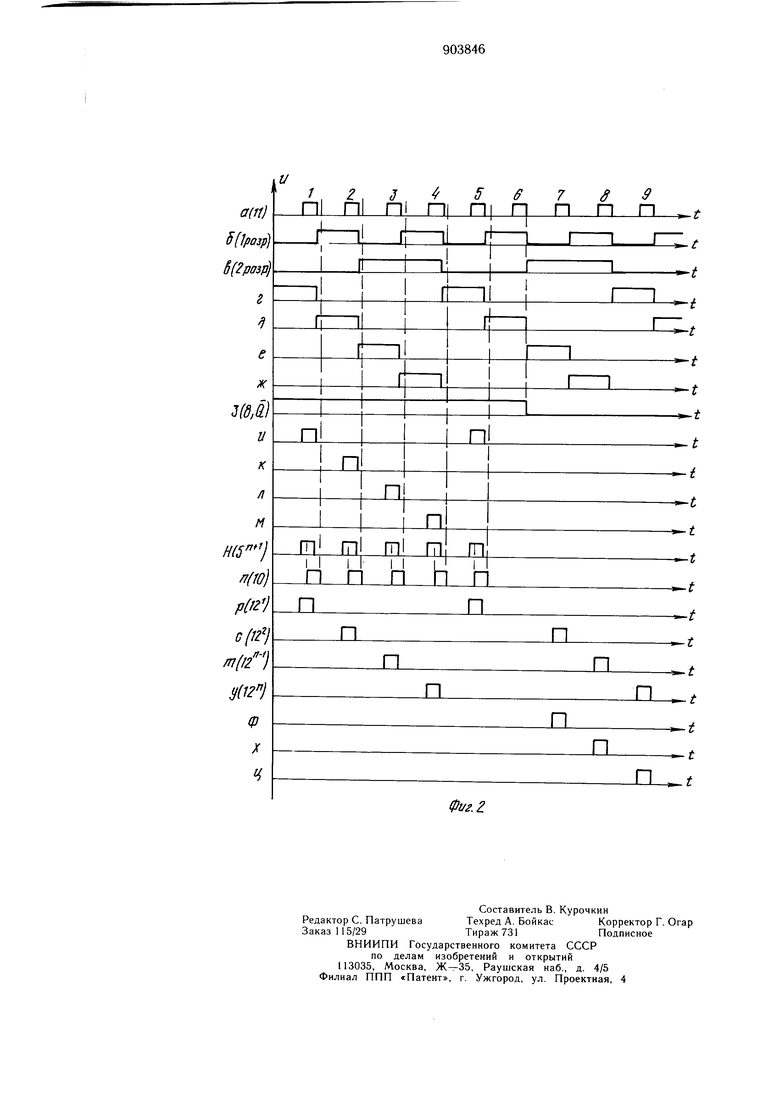

20 дешифратора соединен со вторым входом п-го двувходового элемента ИЛИ группы, выходы первого дешифратора соединены со входами многовходового элемента ИЛИ, выход которого через элементы задержки соединен с первым входом элемента И-НЕ, вход устройства соединен со входами первого и второго счетчиков и с первыми входами первого и второго элементов И, выходы которых подключены к управляющим входам первого и второго дешифраторов соответственно, прямой выход триггера соединен со вторым входом второго элемента И, инверсный выход триггера соединен со вторы входом первого элемента И, вторым входом элемента И-НЕ и К-входом триггера, С-вход и 1-вход которого соединены со входом устройства, выход элемента И-НЕ подключен к R-входу триггера выходы двувходовых элементов ИЛИ группы являются выходами устройства. На фиг. 1 показана структурная схема устройства, на фиг. 2 - временная диаграмма, поясняющая работу устройства для распределения импульсов. Устройство для распределения импульсов содержит счетчики и 2, выполненные на 1К-триггерах, дешифраторы 3 и 4, группу двувходовых элементов ИЛИ 5, элементы И 6 и 7, триггер 8, элемент И-НЕ 9, элемент 10 задержки, вход 11 устройства, выход 12 устройства, многовходовой элемент ИЛИ 13. Устройство работает следующим образом. На вход 11 по диаграмме (фиг. 2) в устройство для распределения импульсов поступают сигналы с генератора импульсов, частота которого определяется требуемым быстродействием дискретного устройства или вычислительной машины, для которых формируется на выходах 12 устройства тактовая сетка импульсов, обеспечивающая управление данным дискретным устройством или вычислительной машиной. Эти сигналы поступают на входы счетчиков 1 и 2, которые начинают заполняться (фиг. 2) и подготавливать к работе выходы первого и второго дещифраторов 3 и 4 по диаграмме (фиг. 2 г, д, е, ж). Однако сигналы появляются на выходах только первого дешифратора 3, так как триггер 8 находится в нулевом состоянии, и сигнал, поступающий с нулевого выхода триггера 8 по диаграмме (фиг. 2з) подготавливает к работе элемент И-НЕ 9 и первый элемент И 6, через который на стробирующий вход первого дешифратора 3 поступают сигналы со входа 11 устройства. Эти сигналы, проходя через первый дешифратор 3, формируются на входах дешифратора 3 по диаграмме (фиг. 2 и, к, л, м) и затем поступают на первые входы п элементов ИЛИ группы элементов ИЛИ 5 и входы многовходового элемента или 13. С выхода которого по диаграмме (фиг. 2 н) эти сигналы через элемент 10 задержки, который обеспечивает задержку выходного сигнала многовходового элемента ИЛИ 13 на 1/2 длительности импульса генератора (фиг. 2 п) и поступают через элемент И-НЕ 9 на R-вход триггера 8, на стробирующий Ср и информационный 1-входы которого поступают сигналы со входа 11 устройства. Однако триггер 8 по заднему фронту входных сигналов, поступающих на стробирующий вход Ср и информационный вход I, не переключается в единичное состояние, так как в этот момент на входе R присутствует сигнал, поступающий с выхода элемента И-НЕ 9, блокирующий работу триггера 8 по стробирующему входу Ср. Следовательно, триггер 8 будет оставаться в нулевом состоянии до тех пор, пока с п выходов первого дешифратора 3 в строго очередной последовательности будут поступать сигналы, которые затем через п элементов ИЛИ 5 поступают на выходы п устройства 12 по диаграмме (фиг. 2 р, с, т, д). В случае отсутствия сигнала на одном из п выходов первого дещифратора 3 в требуемый момент времени происходит аереключение на второй канал второй счетчик 2 и второй дещифратор 4). Нроцесс переключения распределителя импульсов с первого канала (первый счетчик 1 и первый дещифратор 3) на второй канал (второй счетчик 2 и второй дещифратор 4) рассматривается с момента, когда счетчики 1 и 2 находятся в нулевом состоянии (фиг. 2 б, в). В этот момент времени в первом и втором дешифраторах 3 и 4 подготовлены первые выходы по диаграмме (фиг. 2 г). Первый входной сигнал, поступающий на вход 11 устройства по диаграмме (фиг. 2 а) через первый элемент И 6 поступает на стробирующий вход первого дешифратора 3 и далее на первый выход первого дещифратора 3 (фиг. 2 и). Этот сигнал поступает на первый вход элемента ИЛИ 13, с выхода которого (фиг. 2 н) задержанный на 1/2 длительности импульса элемента 10 задержки по диаграмме (фиг. 2 п) через элемент И-НЕ 9 он поступает на R-вход триггера 8, блокируя работу стробирующего входа Ср на момент действия первого сигнала, поступающего на вход 11 по диаграмме (фиг. 2 а) устройства. Триггер 8 остается в нулевом состоянии. Сигнал с первого выхода первого дещифратора 3 (фиг. 2 и) поступает также на первый вход первого элемента ИЛИ группы элементов ИЛИ 5 и далее на первый выход устройства 12 (фиг. 2 р). По заднему фронту первого сигнала, поступающего на вход по диаграмме (фиг. 2 а) устройства- 11, счетчики 1 и 2 переходят во второе положение по диаграмме (фиг. 2 б), а дешифраторы 3 и 4 подготавливают к работе вторые выходы по диаграмме (фиг. 2 д). По второму входному сигналу, поступающему на вход 11 устройства по диаграмме (фиг. 2 а)., на выходе второго элемента ИЛИ группы элементов ИЛИ 5 формируется сигнал по ранее описанному циклу и поступает на второй выход группы выходов 12 формирователя импульсов.

Третий и четвертые входные сигналы, поступающие на вход 11 по диаграмме (фиг. 2 а) устройства, формируют на выходах элементов ИЛИ п-1 группы и п элементов ИЛИ сигналы, которые поступают далее на п-1 и п выходы группы выходов 12 устройства, а счетчики 1 и 2 возвращаются в исходное, нулевое состояние.

Пятый входной сигнал, поступающий на вход И по диаграмме (фиг. 2 а) устройства, формирует сигнал на первом выходе первого дешифратора 3 по диаграмме (фиг. 2 и) и далее на первом выходе группы выходов 12 (фиг. 2 р) устройства по ранее описанному циклу.

Пусть шестой входной сигнал, поступающий на вход 11 по диаграмме (фиг. 2 а) устройства, отсутствует на втором выходе первого дешифратора 3 по диаграмме (фиг. 2 к). В результате этого будет отсутствовать и сигнал, поступающий с выхода многовходового элемента ИЛИ 13 (фиг. 2 н) через элемент 10 задержки по диграмме (фиг. 2 п) и элемент И-НЕ 9, на входе R триггера 8. Следовательно, стробирующий вход Ср триггера 8 не будет блокироваться по входу R, и по заднему фронту шестого входного сигнала, поступающего на стробирующий вход Ср и информационный вход I, триггер 8 по диаграмме (фиг. 2 з) переключается в единичное состояние, запрещая работу первого элемента И 6, элемента И-НЕ 9, собственно информационного входа К и подготавливая к работе второй элемент И 7, т. е. осуществилось переключение на второй канал (второй счетчик 2 и второй дешифратор 4). Если п выходов первого дешифратора 3 соединены с первыми входами п элементов ИЛИ группы элементов ИЛИ 5 соответственно первый выход дешифратора - с первым элементом ИЛИ группы элементов ИЛИ 5, второй выход - со вторым элементом ИЛИ группы элементов ИЛИ 5 и т. д. п-ый выход - с п-ым элементом ИЛИ группы элементов ИЛИ 5, то выходы второго дешифратора 4 подключены ко вторым входам п элементов ИЛИ группы элементов ИЛИ 5 так, что второй вь1ход дешифратора соединен с первым элементом ИЛИ группы элементов ИЛИ 5, третий выход - со вторым элементом ИЛИ группы элементов ИЛИ 5 и т. д. п-ый выход с (п-1)-ым элементом иЛИ группы элементов ИЛИ 5, а первый выход - с п-ым элементом ИЛИ группы элементов ИЛИ 5. Это обеспечивает нормальную работу распределителя импульсов при выходе из строя первого канала.

Седьмой входной сигнал, поступающий по входу 11 по диаграмме (фиг. 2 а) формирует сигнал на третьем выходе второго дешифратора 4 по диаграмме (фиг. 2 ф), который поступает на второй элемент ИЛИ группы элементов ИЛИ 5 и далее на второй выход группы выходов 12 по диаграмме

(фиг. 2с) устройства, с задержкой на один период следования входных сигналов,поступающих на вход И по диаграмме (фиг. 2 а), так как щестой входной сигнал не был выдан на второй выход группы выходов 12 устройства из-за неисправности первого канала. А это не отразится на работе дискретного устройства, на которое работает данное устройство для распределения импульсов. Следовательно, обеспечивается нормальная работа устройства при выходе первого канала из

строя.

По заднему фронту седьмого входного сигнала, поступающего на стробирующий Ср и информационный 1-входы триггера 8, триггер 8 подтверждает единичное состояние, обеспечивая работу второго дешифратора 4 на п выходов группы выходов 12 устройства. Последующие входные сигналы, поступающие на вход 11 устройства, будут формироваться на соответствующих п выходах группы выходов 12 устройства по ранее описанному циклу.

Аналогично предложенное техническое решение может быть использовано при построении распределителя импульсов с любым количеством разрядов в счетчиках 1 и 2 и, следовательно, с любым количеством выходов в каждом дешифраторе, обеспечивая нужное количество выходов устройства. Использование предлагаемого устройства обеспечивает по сравнению с известными

0 устройствами следующие положительные эффекты: повышает надежность работы распределителя, так как обеспечивает нормальную работу распределителя импульсов при выходе из строя первого канала (первый счетчик и первый дешифратор), переключением на второй канал (второй счетчик и второй дешифратор), это достигается введением в распределитель импульсов второго счетчика, второго дещифратора, триггера, элементов И, И-НЕ, многовходового элемента ИЛИ, а также элементов ИЛИ и элемента

задержки, и соответствующих связей.

Формула изобретения

Устройство для распределения импульсов содержащее первый счетчик и первый дешифратор, причем выходы разрядов первого счетчика соединены с информационными входами первого дешифратора, отличающееся тем, что, с целью повышения надежности работы устройства, оно содержит второй счетчик, второй дешифратор, триггер, элементы И, И-НЕ, многовходовой элемент ИЛИ, группу двувходовых элементов ИЛИ, элемент .задержки, причем выходы разрядов второго

счетчика соединены с информационными входами второго дещифратора, первые входы п двувходовых элементов ИЛИ группы соединены соответственно с выходами первого дешифратора (n - количество выходов первого и второго дешифраторов), вторые входы двувходовых элементов ИЛИ группы с первого по (п-1)-й соединены с выходами второго дешифратора со второго по п-й соответственно, первый выход второго дешифратора соединен со вторым входом п-го двувходового элемента ИЛИ группы, выходы первого дешифратора соединены со входами многовходового элемента ИЛИ, выход которого через элемент задержки соединен с первым входом элемента И-НЕ, вход устройства соединен со входами первого и второго счетчиков и с первыми входами первого и второго элементов И, выходы которых подключены к управляюш,им входам первого и второго дешифраторов соответственно, прямой выход

триггера соединен со вторым входом второго элемента И, инверсный выход триггера соединен со вторым входом первого элемента И, вторым входом элемента И-НЕ и К-входом триггера, С-вход и 1-вход которого соединены со входом устройства, выход элемента И-НЕ подключен к R-входу триггера, выходы двувходовых элементов ИЛИ группы являются выходами устройства.

Источники информации, принятые во внимание при экспертизе

№ 387354, кл. G 06 F 1/04, 1970 (проютипЬ

Авторы

Даты

1982-02-07—Публикация

1980-04-23—Подача